### UC Riverside UC Riverside Electronic Theses and Dissertations

#### Title

Modeling and Simulation Methods for VLSI Interconnect Reliability Focusing on Time Dependent Dielectric Breakdown

**Permalink** https://escholarship.org/uc/item/966241xk

**Author** Peng, Shaoyi

Publication Date 2021

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Modeling and Simulation Methods for VLSI Interconnect Reliability Focusing on Time Dependent Dielectric Breakdown

> A Dissertation submitted in partial satisfaction of the requirements for the degree of

> > Doctor of Philosophy

in

**Electrical Engineering**

by

Shaoyi Peng

March 2021

Dissertation Committee:

Dr. Sheldon Tan, Chairperson Dr. Hyoseung Kim Dr. Daniel Wong

Copyright by Shaoyi Peng 2021 The Dissertation of Shaoyi Peng is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

I wish to thank many people who gave me the support and help through the journey of my PhD studies.

First and foremost, I want to express my gratitude to my knowledgeable advisor, Dr. Sheldon Tan, without whose help, I would not have been here. His experience and mentorship is beyond helpful while I was carrying out my research, and also while publishing my research. Our discussions about work and career are invaluable to me.

I would also like to thank my committee members Dr. Hyoseung Kim and Dr. Daniel Wong for their guide to my research, especially during my first year when I started to explore the areas of research.

I am also grateful to all my fellow labmates. Especially, I want to thank Taeyoung Kim, Hengyang Zhao, Chase Cook, Zeyu Sun, Han Zhou, Sheriff Sadiqbatcha, Wentian Jin, Jinwei Zhang, Shuyuan Yu and Yibo Liu. The mentorship and discussions we had are treasurous during these years of study. Furthermore, I cannot imagine going through these years without your company. You are the family of mine in this country.

The content of this thesis is reprinted or rewritten from these published materials:

• Shaoyi Peng, Han Zhou, Taeyoung Kim, Hai-Bao Chen, and Sheldon X-D Tan. "Physics-based compact TDDB models for low-k beol copper interconnects with timevarying voltage stressing". IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2017 (Chapter 2)

- Shaoyi Peng, Ertugrul Demircan, Mehul D. Shroff, and Sheldon X-D. Tan. "Fullchip wire-oriented back-end-of-line TDDB hotspot detection and lifetime analysis". Integration, 2020 (Chapter 3)

- Shaoyi Peng, Wentian Jin, Liang Chen, and Sheldon X-D Tan. "Data-Driven Fast Electrostatics and TDDB Aging Analysis". Proceedings of the 2020 ACM/IEEE Workshop on Machine Learning for CAD (Chapter 4)

- Shaoyi Peng, and Sheldon X-D. Tan. "GLU3.0: Fast GPU-based Parallel Sparse LU Factorization for Circuit Simulation". IEEE Design & Test, 2020 (Chapter 5)

To my parents for all the love and support.

#### ABSTRACT OF THE DISSERTATION

#### Modeling and Simulation Methods for VLSI Interconnect Reliability Focusing on Time Dependent Dielectric Breakdown

by

Shaoyi Peng

#### Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, March 2021 Dr. Sheldon Tan, Chairperson

Time dependent dielectric breakdown (TDDB) is one of the important failure mechanisms for Copper (Cu) interconnects that are used in VLSI circuits. This reliability effect becomes more severe as the space between wires is shrinking and low-k dielectric materials (low electrical and mechanical strength) are used. There are many studies and theories focusing on the physics of it. However, there is limited research from the electronics design automation (EDA) perspective on this topic, aiming to evaluate, or alleviate it from the perspective of designing a VLSI chip. This thesis compiles several studies into evaluating TDDB on the circuit level, and engineering methods that help the evaluation. The first work extends the study of a published physics model on simplified yet practical cases. It simplifies the calculation of lifetime by deriving an analytic solution and applying fitting methods. The second study proposes a new way to evaluate lifetime of a chip by extending the models of simple interconnect structures to the complete chip. This method is more robust as it focuses more on a complete chip. However, heavy dependence of finite element method (FEM) makes the flow very slow. The third study adopts machine learning methods to accelerate this slow evaluation process. The proposed method is also applicable to other similar electrostatics applications. Last but not least, the fourth study focuses on a GPU based LU factorization algorithm, which, on a broader aspect, is a universal numerical algorithm used in many different simulation applications, which can be helpful to TDDB evaluations as it can be used in FEM.

## Contents

| Lis | st of                                          | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | x                                                                                                                                                         |

|-----|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lis | st of                                          | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xi                                                                                                                                                        |

| 1   | <b>Intr</b><br>1.1<br>1.2<br>1.3               | oduction         Time Dependent Dielectric Breakdown for VLSI Interconnect         Sparse LU factorization         Related works                                                                                                                                                                                                                                                                                                                                                                                                      | <b>1</b><br>1<br>3<br>4                                                                                                                                   |

|     | $1.4 \\ 1.5$                                   | 1.3.1       TDDB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $     4 \\     5 \\     6 \\     8 $                                                                                                                      |

| 2   | Fast<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | <b>TDDB analysis with EPG model</b> Review of physics-based TDDB EPG model for low-k BEOL interconnectsFaster TDDB analysis flow with the EPG model2.2.1Analytic solution of ion concentration in the IMD2.2.2TDDB time to failure estimation2.2.3Study of the relationship between TTF and electric fieldEquivalent DC stressing voltage analysis of EPG modelExperimental results and discussionsSummary2.6.1Derivation of the analytic solution for the ion diffusion equation2.6.2Derivation of analytic form for time to failure | <ul> <li>9</li> <li>10</li> <li>13</li> <li>17</li> <li>18</li> <li>20</li> <li>23</li> <li>25</li> <li>29</li> <li>29</li> <li>29</li> <li>32</li> </ul> |

| 3   | Full-<br>3.1<br>3.2                            | -Chip Wire-Oriented TDDB AnalysisOverviewLength-aware TDDB model $3.2.1$ Review of $\sqrt{E}$ and other TDDB models $3.2.2$ TDDB damage model of interconnect wires $3.2.3$ Lifetime of chip                                                                                                                                                                                                                                                                                                                                          | <b>34</b><br>35<br>37<br>37<br>38<br>41                                                                                                                   |

|   | 3.3 | Layout partition-based TDDB wire damage analysis                        | 42        |

|---|-----|-------------------------------------------------------------------------|-----------|

|   |     | 3.3.1 Layout partition                                                  | 43        |

|   |     | 3.3.2 Solving $E$ and TDDB damage in each tile $\ldots$                 | 45        |

|   |     | 3.3.3 Integral of long wires for final results                          | 46        |

|   | 3.4 | Numerical results                                                       | 49        |

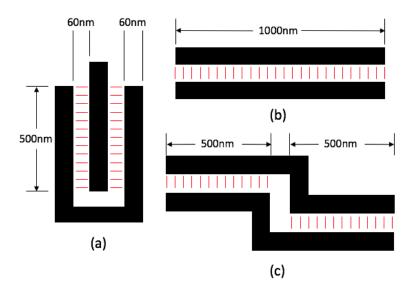

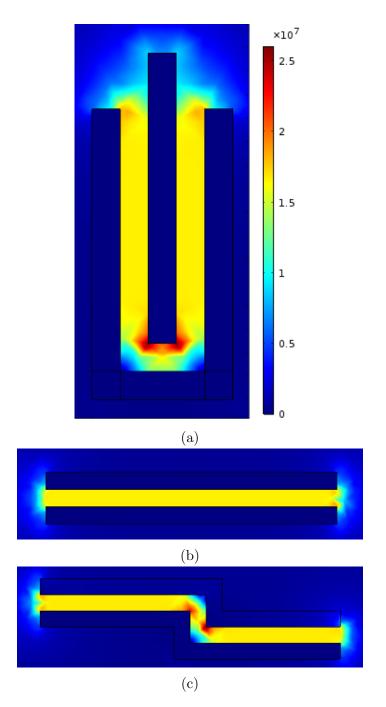

|   |     | 3.4.1 Comparison on three structures                                    | 49        |

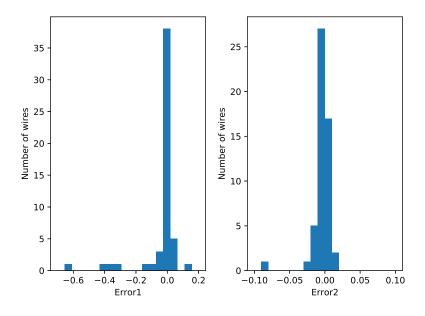

|   |     | 3.4.2 Validation of the partition-based method                          | 51        |

|   |     | 3.4.3 Analysis of an example layout                                     | 58        |

|   | 3.5 | Summary                                                                 | 61        |

| 4 | Dat | ta-Driven Fast Electrostatics and TDDB Aging Analysis                   | 62        |

|   | 4.1 | Overview                                                                | 63        |

|   | 4.2 | Related works                                                           | 64        |

|   | 4.3 | Preliminaries of Electrostatics and TDDB                                | 65        |

|   | 4.4 | The proposed data-driven electrostatic analysis                         | 67        |

|   |     | 4.4.1 Problem formulation                                               | 67        |

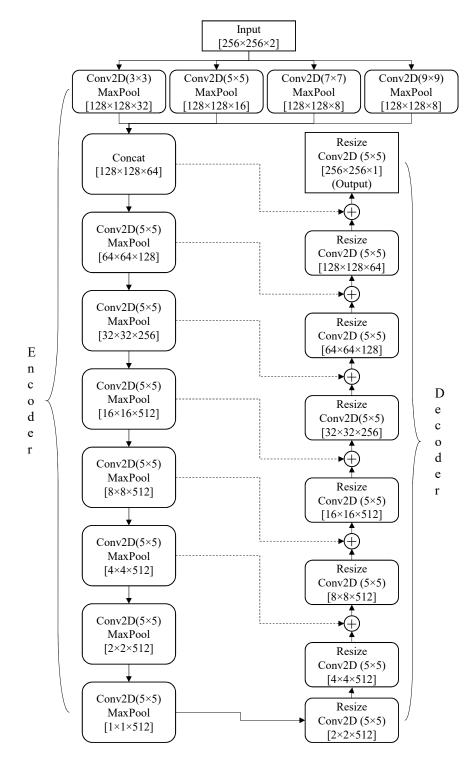

|   |     | 4.4.2 Structure of the neural network                                   | 70        |

|   | 4.5 | Numerical results and discussions                                       | 71        |

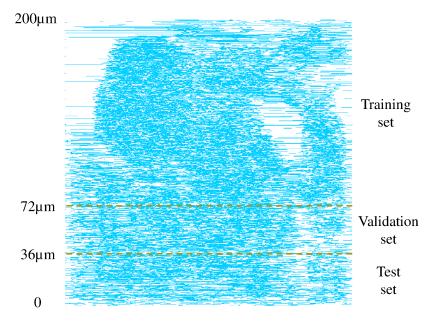

|   | 1.0 | 4.5.1 Data preparation and training                                     | 73        |

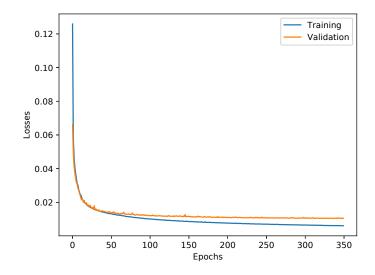

|   |     | 4.5.2 Results of electric potential analysis                            | 76        |

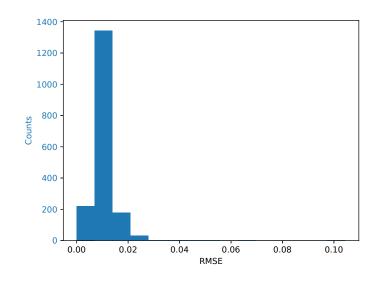

|   |     | 4.5.3 Results of electric field analysis                                | 77        |

|   |     | 4.5.4 Results of TDDB aging analysis                                    | 77        |

|   |     | 4.5.5 Simulation efficiency study                                       | 81        |

|   |     | 4.5.6       Discussion of network structure                             | 82        |

|   | 4.6 | Summary                                                                 | 83        |

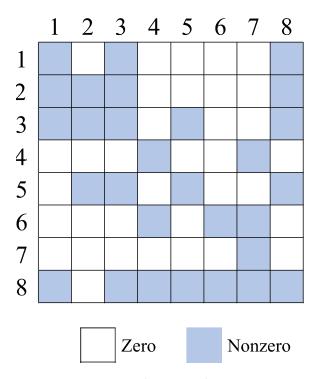

| 5 | GU  | U3.0: Fast GPU-based Parallel Sparse LU Factorization Solver            | 84        |

| 0 | 5.1 | Overview and related works                                              | 85        |

|   | 5.2 | Review of LU factorization and CUDA                                     | 86        |

|   | 0.2 | 5.2.1 The left-looking method                                           | 87        |

|   |     | 5.2.2 The column-based right-looking method used in GLU                 | 90        |

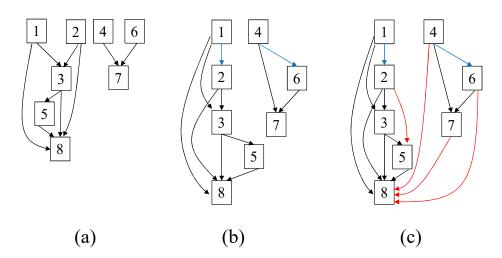

|   |     | 5.2.3 Additional data dependency in GLU: the fix in GLU2.0              | 93        |

|   |     | 5.2.4 Enhancements to GLU2.0                                            | 93<br>97  |

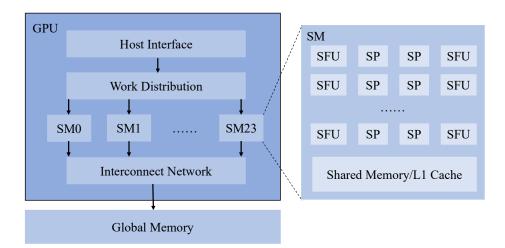

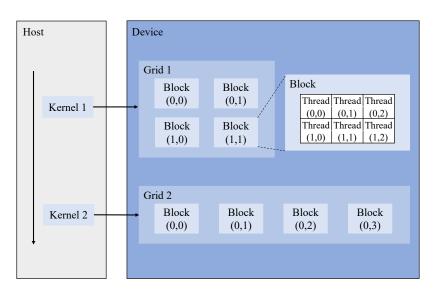

|   |     | 5.2.5 Review of GPU Architecture and CUDA programming                   | 97<br>97  |

|   | 5.3 | New GPU based sparse LU solver: GLU 3.0                                 | 99        |

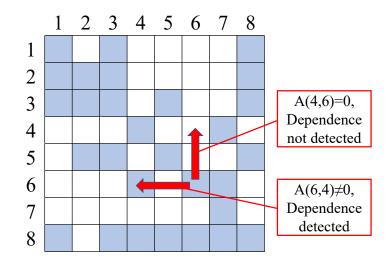

|   | 0.0 | 5.3.1 Relaxed data dependency detection method for GLU                  | 99<br>99  |

|   |     |                                                                         | 99<br>103 |

|   | 5.4 |                                                                         | 1103      |

|   |     |                                                                         | 110       |

|   | 5.5 | Summary                                                                 | 110       |

| 6 | Cor | nclusions                                                               | 118       |

|   | 6.1 | Fast TDDB analysis with EPG model                                       | 118       |

|   | 6.2 | Full-Chip Wire-Oriented TDDB Analysis                                   | 119       |

|   | 6.3 |                                                                         | 120       |

|   | 6.4 | GLU3.0: Fast GPU-based Parallel Sparse LU Factorization Solver $\ldots$ | 121       |

|   |     |                                                                         |           |

#### Bibliography

122

## List of Figures

| 1.1          | Structure of two copper interconnect wires and the IMD, where TDDB occurs                                                                                   | 2               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $2.1 \\ 2.2$ | Dielectric modeled by resistor chain and the corresponding ion concentration<br>Distribution of ion concentrations in one pattern.                          | $\frac{11}{12}$ |

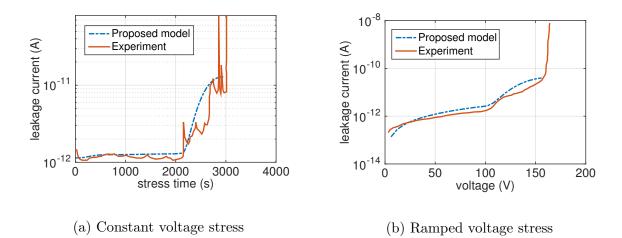

| 2.3          | Current-voltage leakage changes for different voltage (TDDB) stresses mod-<br>eled by EPG model, compared with experimental data from [61], courtesy of     |                 |

| 2.4          | [33]                                                                                                                                                        | 14              |

|              | FEM analysis using COMSOL.                                                                                                                                  | 14              |

| $2.5 \\ 2.6$ | TTF against different stressing voltages $(V_{DD})$ under different temperatures.<br>Comparison between RSM results with COMSOL results on different param- | 22              |

|              | eters                                                                                                                                                       | 28              |

| 3.1          | FEM analysis result showing higher electric field around tips                                                                                               | 36              |

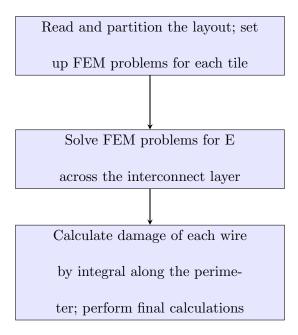

| 3.2          | The three key steps of the analysis flow                                                                                                                    | 42              |

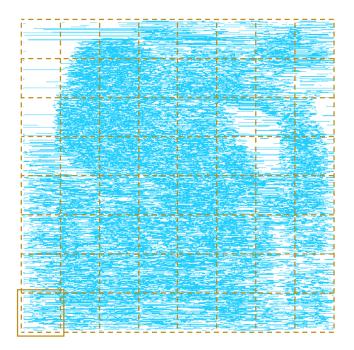

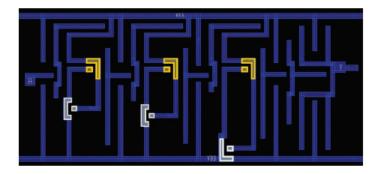

| 3.3          | Full layout of M3 and the partition scheme                                                                                                                  | 44              |

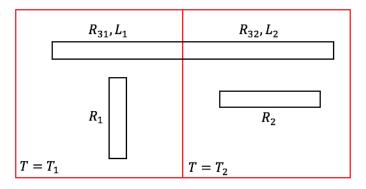

| 3.4          | An example of a wire crossing a tile boundary, with two tiles and three wires                                                                               |                 |

|              | in total                                                                                                                                                    | 47              |

| 3.5          | Comb structures in designs                                                                                                                                  | 50              |

| 3.6          | Three structures analyzed: (a) comb (b) parallel line (c)twisted line                                                                                       | 52              |

| 3.7          | Electric field distribution of the three structures analyzed                                                                                                | 53              |

| 3.8          | The layout tile used to validate the partition-based approach                                                                                               | 54              |

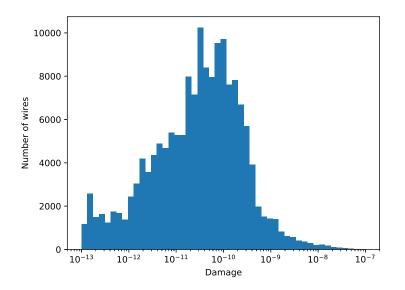

| 3.9          | Distribution of $Error1$ and $Error2$ of $R$ among all wires                                                                                                | 56              |

| 3.10         | Distribution of $R$ among all wires $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                 | 59              |

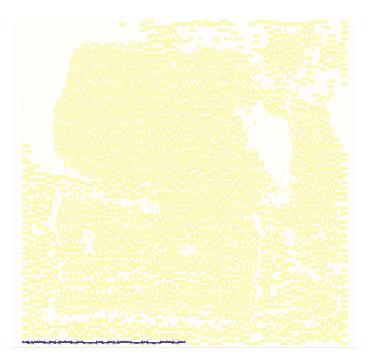

| 3.11         | Full M1 layer view with most vulnerable wire highlighted                                                                                                    | 60              |

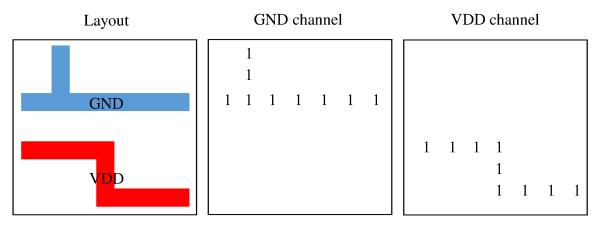

| 4.1          | Encoding a layout tile into image                                                                                                                           | 69              |

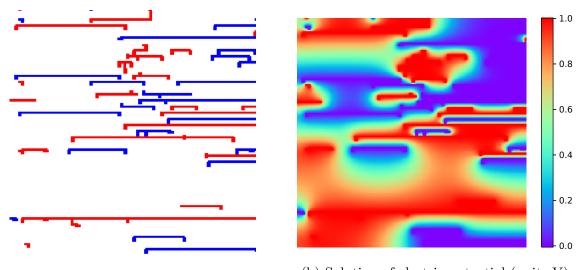

| 4.2          | An example of encoded tile image of and its corresponding solution of potential                                                                             | 69              |

| 4.3          | Structure of the used neural network                                                                                                                        | 72              |

| 4.4          | The split of the dataset from layout (M3 shown here)                                                                                                        | 74              |

| 4.5          | Training curves                                                                                                                                             | 75              |

| 4.6          | Distribution of RMSE over the test set                                                                                                                      | 75              |

| 4.7          | The test sample with the largest RMSE. The tile is shown using the same color convention as in Fig. 4.2a                                                                                         | 76       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

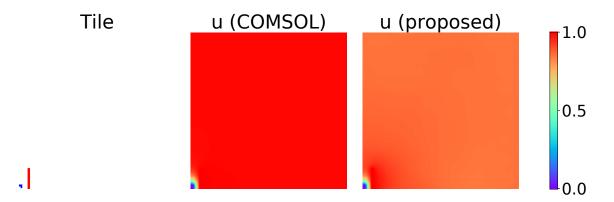

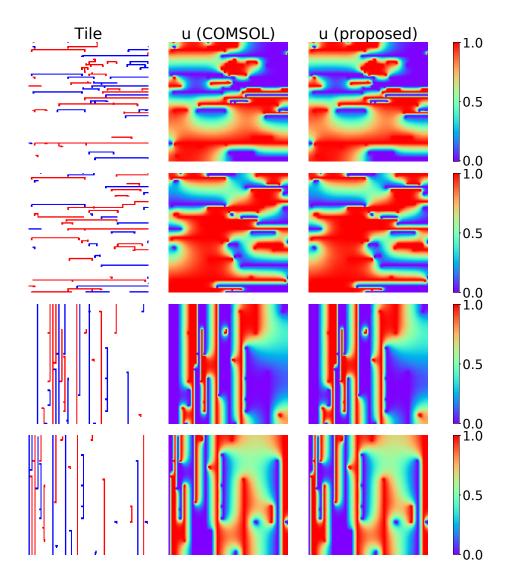

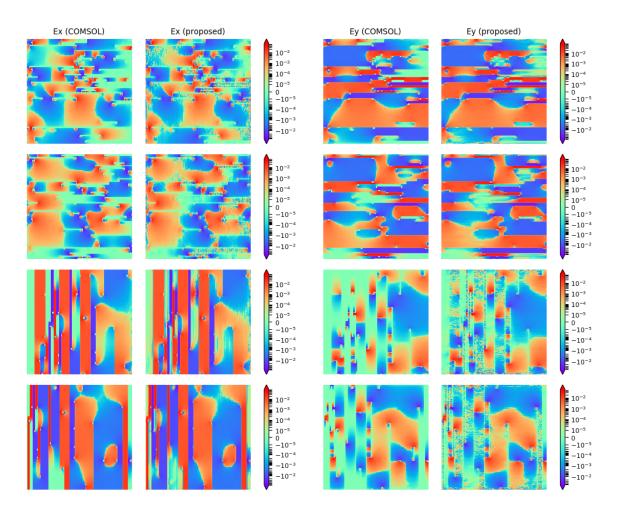

| 4.8          | Results of electric potential of sample tiles (left) from COMSOL (middle)<br>and the proposed method (right)                                                                                     | 78       |

| 4.9          | Results of electric field of sample tiles from COMSOL and the proposed method. The unit of electric field is $MV/cm$ .                                                                           | 79       |

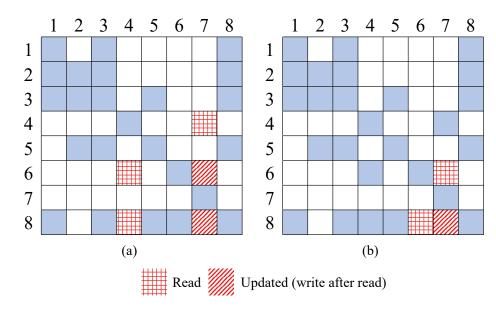

| $5.1 \\ 5.2$ | The example matrix $\dots$ The two update iterations completing factorization of the 7th column $(j = 7)$<br>(a) update using the 4th column $(k = 4)$ (b) update using the 6th column $(k = 6)$ | 87<br>90 |

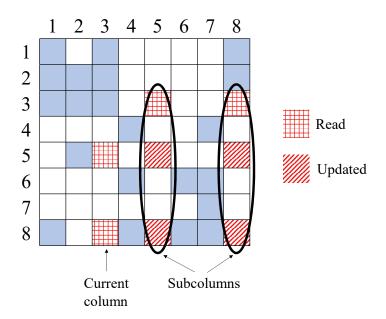

| 5.3          | Subcolumns and submatrix column 3. All highlighted elements compose the submatrix, which include elements being read and elements being updated.                                                 | 91       |

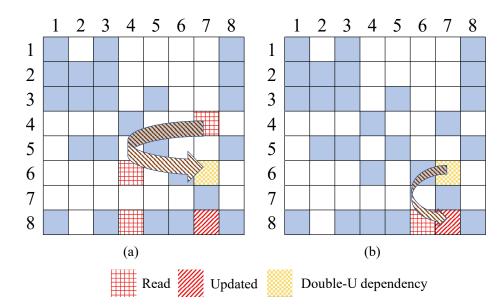

| 5.4          | An example of double-U dependency originated from element $(6,7)$                                                                                                                                | 95       |

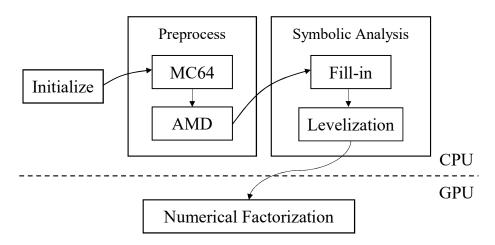

| 5.5          | Complete flow of GLU2.0                                                                                                                                                                          | 96       |

| 5.6          | Diagram of NVIDIA TITAN X and the streaming multiprocessor. (SP is<br>short for streaming processor, L/S for load/store unit, and SFU for Special                                                |          |

|              | Function Unit.)                                                                                                                                                                                  | 98       |

| 5.7          | The programming model of CUDA                                                                                                                                                                    | 99       |

| 5.8          | Comparison of left looking and up looking, left looking is able to detect                                                                                                                        |          |

|              | double-U dependency.                                                                                                                                                                             | 101      |

| 5.9          | Dependency graph generated from 3 methods: (a) GLU1.0: incorrect result                                                                                                                          |          |

|              | (b) GLU2.0: correct result (c) This work: the relaxed data dependency                                                                                                                            | 102      |

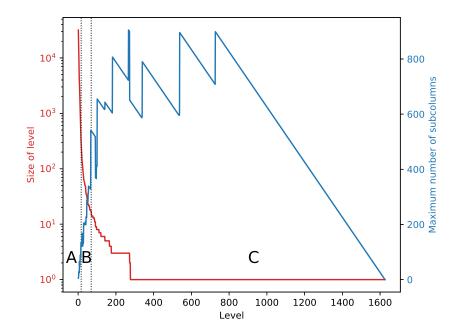

| 5.10         | Number of columns and subcolumns of different levels                                                                                                                                             | 107      |

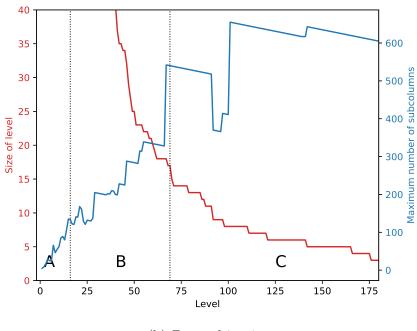

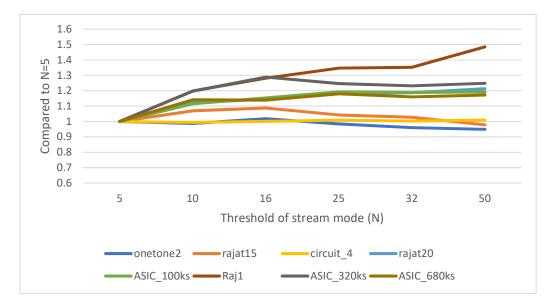

| 5.11         | Comparison of the concurrency layout for one column in different kernels:                                                                                                                        |          |

|              | (a) Small block mode (b) Large block mode (c) Stream mode                                                                                                                                        | 110      |

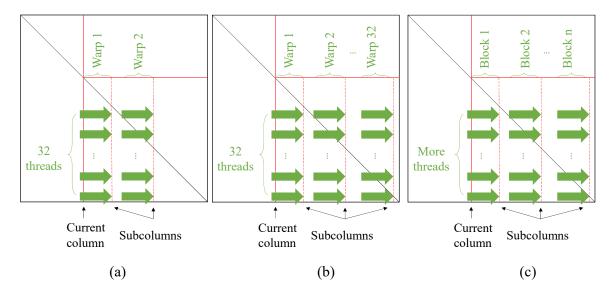

| 5.12         | Performance of GPU kernel with different stream mode threshold settings .                                                                                                                        | 116      |

|              |                                                                                                                                                                                                  |          |

## List of Tables

| 2.1 | Parameters and constants used                                                        | 14   |

|-----|--------------------------------------------------------------------------------------|------|

| 2.2 | Statistics of TTFs in different patterns with the same minimum distance              |      |

|     | (50nm)                                                                               | 15   |

| 2.3 | TTF results after changing $D_0$ or $E_a$                                            | 15   |

| 2.4 | Statistics of TTFs in different patterns with the same minimum distance              |      |

|     | (20 nm)                                                                              | 16   |

| 2.5 | Fitted coefficients of the power law model                                           | 20   |

| 2.6 | Results of ion concentration derived from two methods                                | 26   |

| 2.7 | TTF from different methods, the calculation times and speedup over FEM .             | 26   |

| 2.8 | Parameters for 3 tests                                                               | 28   |

| 3.1 | Results of E at points marked " $\times$ " under different setups. Unit is $V/m$ .   |      |

|     | Error is defined as $(E - E0)/E0$                                                    | 56   |

| 3.2 | Results of $R$ of marked wires marked " $\bigcirc$ " under different problem setups. |      |

|     | Error is defined as $(R - R0)/R0$                                                    | 56   |

| 3.3 | Analysis results of all layers                                                       | 58   |

| 4.1 | Integral results in capacitance and aging analysis of sample wires, calculated       |      |

|     | using the proposed method and COMSOL                                                 | 81   |

| 4.2 | Result discrepancy achieved with different network structures                        | 83   |

| 5.1 | Solver runtimes of GLU3.0 vs previous works, where $nz$ stands for number            |      |

|     | of nonzeros before fill-in, and $nnz$ stands for number of nonzeros after fill-in    | 112  |

| 5.2 | Levelization runtimes                                                                | 113  |

| 5.3 | GPU kernel runtimes without enabling all 3 kernel modes, compared to case            |      |

|     | 1 where small block mode is disabled, and case 2 where stream mode is disabled       | .114 |

## Chapter 1

## Introduction

## 1.1 Time Dependent Dielectric Breakdown for VLSI Interconnect

Time Dependent Dielectric Breakdown (TDDB) is the physical phenomenon that dielectric breaks down with time when the dielectric deposited under a field becomes weaker than the material breakdown strength. It creates a short circuit and is thus fatal to the VLSI circuit. TDDB has become a serious dielectric reliability concern and failure mechanism for back end of line (BEOL) interconnects, so accurate and fast modeling and estimation of TDDB failure become important.

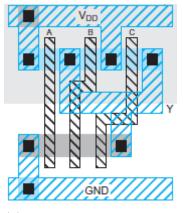

Traditionally, TDDB is a major concern only for the gate oxide of CMOS devices. With the advances of technology scaling, middle-of-line (MOL) TDDB and BEOL TDDB have also become important reliability mechanisms. MOL TDDB is breakdown between the gate and contact and is often modeled together with gate oxide TDDB as they can be

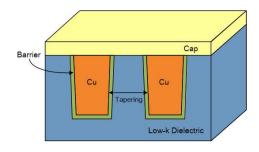

(a) The cross-section of copper/low-k dielectric structure

(b) The cross-section SEM image after TDDB failure, courtesy of [60]

Figure 1.1: Structure of two copper interconnect wires and the IMD, where TDDB occurs

modeled by extra resistors connecting transistor nodes [70, 8]. However, with aggressive technology scaling accompanied by the employment of new low-k and even porous materials [17], TDDB becomes a serious reliability concern and failure mechanism for BEOL interconnects [47, 34, 5, 67]. The dielectric breakdown is caused by the conducting path formation through the inter-metal dielectric (IMD) oxide between metal wires from electron tunneling current. Finally, a significant large leakage current occurs and results in the chip operation failure. This is shown in the SEM image in Fig. 1.1, along with a descriptive figure showing the structure of the two metal wires and the IMD in between. For BEOL, TDDB effects can be seen at the inter-layer dielectric (ILD) between two metal layers and also IMD between metal wires in the same layer of the low-k dielectrics. In general, due to the fact that ILD space is larger than that of IMD, TDDB in IMD is more likely to occur so more research focus is put on it.

Many researches have been done about the physics of TDDB, and thus many TDDB models have been proposed based on different proposed breakdown mechanisms, the most well known ones being E, 1/E, and  $E^{1/2}$  models. The E-model models TDDB as a weak bond breakage due to thermochemical heating [44]. The 1/E-model models it as high energy hole injection induced failure [9]. These models were initially introduced for gate oxides and later examined for the extension to the copper/low-k interconnects. The difference between gate oxides model and low-k BEOL dielectrics is the existence of metal ions in the former's interior. The  $E^{1/2}$ -model has been firstly proposed for metal-SiN-metal capacitors [2] and later examined in the low-k TDDB by assuming that the copper ion plays an important role in the dielectric breakdown [6, 60]. These studies use simple interconnect structures such as serpentine-comb or comb-comb to test the life time of test structures [67].

Recently some studies show that the migration of copper ions is not significant due to the existence of copper barrier (i.e. Ta). Instead, the barrier ions play an important role in ion migration [37, 43, 33]. Moreover, the breakdown depends on the conducting path formation between the two metal wires. This leads to the development of the electric path generation (EPG) model [33].

#### 1.2 Sparse LU factorization

LU factorization represents the routine to factorize a full-rank square matrix A into the product of two triangular matrices: the lower triangular matrix L and upper triangular matrix U such that A = LU.

Sparse matrix is a special type of matrix, in which most of the elements are zero. Sparse matrices appear in many engineering and scientific computing applications, such as circuit simulation and finite element method (FEM), which itself is an important method in TDDB analysis. The core of the computing or dominant computing of these applications is to solve the linear algebraic system, Ax = b, where matrix A and vector b are given and x is a vector to be solved. LU factorization is an important way to solve such problem. After finding the triangular matrices L and U through LU factorization, the solution x is then obtained by solving the two triangular matrices sequentially, which only has linear time complexity and is much cheaper than LU factorization.

#### 1.3 Related works

#### 1.3.1 TDDB

Besides the works on the physics of TDDB mentioned above, there also exists some other works focusing on evaluating the BEOL TDDB lifetime of a chip, which is the time a chip can function before a TDDB failure. They are more related to the studies conducted in this thesis.

A chip-scale TDDB lifetime simulator is proposed in [3]. In this work, interconnect geometries are grouped by spacing between wires and the total run length of each group is extracted. Next, lifetime of each group is scaled by total length based on experimental data of dielectrics of the same spacing. Furthermore, practical considerations such as variation in spacing and different temperature across the chip are also done. [4] extends this work to include other reliability effects such as electromigration (EM) and stress-induced voiding (SIV).

Besides proposing the EPG model, [33] also introduces a method based on a lookup table of high-risk interconnect shape patterns. The look-up table is built by simulating the TDDB failures on the patterns. Also, fitting methods are used to cover different kinds of wires such as power, ground and signal.

The work presented in [35] models BEOL TDDB as additional resistors across dielectrics. The device level model is then used for the higher circuit and system level modeling and simulations.

#### 1.3.2 Sparse LU factorization

There exists many earlier researches targeting sparse LU factorization. For instance, SuperLU\_MT [22] is the multi-threaded parallel version of SuperLU for multi-core architectures. However, it is not easy to form super-node in some sparse matrix such as circuit matrix. KLU [20], which is specially optimized for circuit simulation, adopts Block Triangular Form based on Gilbert-Peierls (G/P) left-looking algorithm [27] and has become one of the standard algorithms in circuit simulation applications. The original KLU runs on single CPU core only. NICSLU [12, 13, 11] implements its parallel version on multi-core architecture by exploiting the column-level parallelism. UMFPACK [64] is implemented based on a multifrontal algorithm. PARDISO [57] is developed based on a left-right-looking algorithm.

Existing GPU based parallel LU factorization solvers mainly focus on dense matrices including [25]. There also exists a few sparse matrix LU factorization methods on GPU [14, 26]. But these works mainly convert the sparse matrices into many dense submatrices (blocks) and then solve them by dense matrix LU factorizations. However, such strategy may not work well for circuit matrices, which hardly have dense submatrices. Parallel G/P left-looking algorithm on GPU has been explored first in [54, 10]. It exploits the column-level (called task-level) parallelism due to sparse nature of the matrix and vector-level parallelism in the sparser triangular matrix solving in the G/P method. However, the two loops in triangular matrix solving can't be completely parallelized (from line 4-8 in Algorithm 3) thus the G/P method is difficult for fine grain parallelization.

To mitigate this problem, He *et. al* proposed a hybrid right-looking sparse LU factorization on GPU, called GLU (GLU1.0) [30]. GLU keeps the benefits of the left-looking method for column-based parallelism and uses the same symbolic analysis routine. The difference is that it performs the submatrix update once one column is factorized, which is similar to the traditional right-looking LU method. However, GLU1.0 used a fixed scheme to allocate the GPU threads and memory, which limits its parallelism. Furthermore, the right-looking feature of GLU actually introduces new data dependency (called double-U dependency in this paper), which has been reported in GLU2.0 and [39]. Double-U dependency can lead to inaccurate results for some test cases. Detection of double-U dependency was added into GLU2.0 to fix this issue, which, however, incurred some performance degradation compared to GLU1.0. Recently, Lee *et al.* proposed an enhanced GLU2.0 solver [39], which considers the column count difference in different level, and exploits some advanced GPU features such as dynamic parallelism to further improve the GLU kernel efficiency. However, the fixed GPU threads and memory allocation method from GLU2.0 for each kernel launch is still used and limiting performance.

#### 1.4 Contributions

The work presented in this thesis presents several contributions in the area of TDDB analysis for VLSI interconnect, and GPU based sparse LU factorization:

- The recently proposed physics based EPG model for interconnect TDDB is further studied. It is shown that the simplified 1D case can represent most cases pretty well. The analytic solution of the PDE of the model is derived. Then it is shown that the location of the minimum concentration, which is a key factor in this TDDB model, can be determined by the dominant terms and the TTF can be computed by using a few dominant terms. Furthermore, fitting methods are adopted to extend the proposed method to time-varying DC stressing voltages.

- A full chip TDDB lifetime and hotspot evaluation flow is proposed based on a new concept called TDDB Damage. It takes into account the layout effect brought by complex wire geometries and the length of the wires and dielectric. By partitioning the chip into smaller tiles, FEM can be used to calculate the strength of electric field under stressing conditions, and the electric field is used to further calculate TDDB Damage and the lifetime of wires and the chip.

- A machine learning based method is proposed to speed up the electrostatics solving process, which aims to solve the electric field in TDDB analysis. After layout partition, each layout tile can be encoded as an image and thus an encoder-decoder network is employed to mimic the FEM solving process. High accuracy along with speedup of two orders are achieved.

• GLU3.0 introduces two main improvements to the previously developed GPU based sparse LU factorization solver GLU. First, a new leveling algorithm is developed, which brings the complexity of the preprocessing stage back to normal. Second, three new modes of GPU kernels are developed, which takes advantage of the data pattern in typical sparse LU factorization and helps better utilize the computing resources of GPU.

#### 1.5 Organization of this thesis

The rest of this thesis is organized as follows. Chapters 2, 3 and 4 introduce the three TDDB analysis works. Chapter 5 introduces GLU3.0. Each chapter begins with an overview, and the related published paper is listed, followed by details of the work and results. Finally, chapter 6 summarizes the thesis.

## Chapter 2

# Fast TDDB analysis with EPG model

The work presented in this chapter focuses on the EPG model [33], which is based on the breakdown concept of electric path generation. However, determination of the timeto-failure from this model includes time-consuming finite element method (FEM). The work presented in this chapter tries to mitigate this problem by developing fast time to failure (TTF) evaluation method based on the analytic solution of the ion diffusion partial differential equations. It is shown that the location of the minimum concentration can be determined by the dominant terms with sufficient accuracy and the TTF can also be computed with a few dominant terms. On top of this, time-varying stressing voltages are also considered, which are commonly seen in practical VLSI chips. An equivalent DC stressing voltage is computed for given time-varying stressing voltages such that both voltages will lead to the same TTF for the same wire structure. The developed equivalent DC stressing voltage is parameterized in terms of amplitude, duty cycle, and period for periodic stressing voltage waveforms using regression-based method. The proposed analytic TDDB concentration and TTF formula, and the equivalent DC stressing voltage compact model are all validated against the results of FEM analysis using COMSOL. Numerical results further show the new compact TDDB model can lead to three orders of magnitude speedup with less than 1% error against the existing FEM results. This work is published in [53]

## 2.1 Review of physics-based TDDB EPG model for low-k BEOL interconnects

The EPG model views dielectric breakdown as a complementary combination of electric current path generation by means of diffusing metal ions and field-based hopping conductivity of the current carriers. Different from the more widely accepted across-layout electrostatic field based TDDB models (i.e. E, 1/E, and  $E^{1/2}$  models), TTF in the EPG model is determined by the kinetics of the electric current path generation, which is controlled by a time-dependent minimum metal ion concentration in IMD. Also, in this model, it is assumed that the barrier metal ions are injected into the dielectrics based on the recent observation [37].

Specifically, 2D diffusion of the metal ions along the cap/IMD interface between the oppositely charged metal wires (as shown in Fig. 1.1a) is considered because experiments demonstrate that TDDB failures take place mostly at this interface [71, 24].

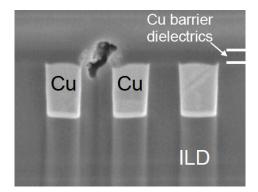

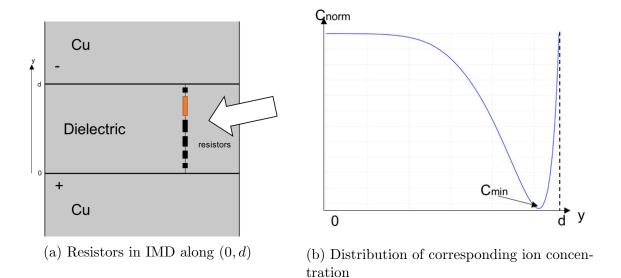

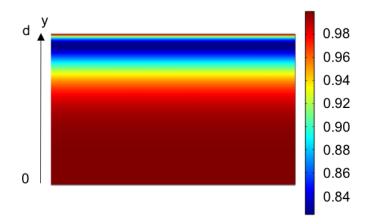

Figure 2.1: Dielectric modeled by resistor chain and the corresponding ion concentration

As stated, electric conductivity is represented by electron jumps between neighboring centers (hoping conductivity). The local conductivity is proportional to the probability of the electron jumping between the neighbor centers, which exponentially depends on the distance between the centers [58]:

$$\sigma_{ij} \sim \Gamma_{ij} = \gamma_{ij}^0 exp \left\{ -\frac{2r_{ij}}{a} - \frac{\varepsilon_{ij}}{k_B T} \right\}$$

(2.1)

where  $r_{ij}$  is the distance between centers marked *i* and *j*, *a* is the radius of electron localization at this type of centers (analog of the Bohr's radius), which can reach 100Å,  $\varepsilon_{ij}$  is the energy barrier between centers, and  $k_BT$  is the thermal energy. All connected centers form a resistor network, with the resistor between *i* and *j* centers being

$$R_{ij} = R_{ij}^0 exp\left\{\frac{2r_{ij}}{a} + \frac{\varepsilon_{ij}}{k_B T}\right\}$$

(2.2)

In a 2D system, the distance  $r_{ij}$  is determined by:  $r_{ij} = C(x, y, t)^{-\frac{1}{2}}$ , where C(x, y, t) is the ion concentration at the considered interface. Fig. 2.1 shows the schematic of the distri-

Figure 2.2: Distribution of ion concentrations in one pattern.

bution of ion concentration and corresponding resistor network at an arbitrary instance in time in IMD along a path (0, d) connecting metal electrodes. It is clear that electrons moving from the cathode to anode will meet the biggest resistor at the locations characterized by the largest distance between centers. Since the resistance grows exponentially with the distance, it is reasonable to conclude that the total resistance of the path (0, d) depends on the largest resistor, and its corresponding minimum ion concentration. Fig. 2.2 shows the COMSOL [1] FEM analysis result of the distribution of ion concentration for the pattern in Fig.2.1a under some time of stressing, which is a 2D version of Fig. 2.1b.

The distribution of the normalized ion concentration  $C_{\text{norm}}(x, y, t) = C(x, y, t)/C_0$ is governed by the diffusion of ions in an electric field [29]:

$$\frac{\partial C_{\text{norm}}}{\partial t} = -\nabla J, \text{ where } J = -D\nabla C_{\text{norm}} + v_d C_{\text{norm}}$$

(2.3)

subject to the following boundary conditions:

$$C_{\text{norm}}(x=0) = C_{\text{norm}}(x=d) = 1$$

where J is the metal flux,  $D = D_0 exp(-Ea/k_BT)$  is the diffusion coefficient,  $v_d = E \frac{Dq}{k_BT}$ is the metal ion drifting velocity, Ea is the activation energy for metal ion diffusion,  $k_B$  is the Boltzmann constant, T is the temperature, q is the electric charge and E is the electric field.

The developed model of the electric path generation and evolution allows derivation of the formalism of the leakage current evolution. As mentioned above, the neighboring ions characterized by the largest separation provides the largest "resistance" for the electrons hopping between metal ions. Assuming that the potential barriers between neighboring centers do not depend on the distance between them ( $\varepsilon_{ij} = \varepsilon$ ), and adopting the Poole-Frenkel mechanism of the field-induced barrier lowering, the expression for the current density evolution can be derived:

$$j(t) = j_0 Eexp \left\{ -\frac{2}{a\sqrt{C_{\text{norm}}^{\min}(t) \cdot C_0}} - \frac{\varepsilon - q\sqrt{qE/(\pi\varepsilon_{\text{perm}})}}{k_B T} \right\}$$

(2.4)

where  $\varepsilon_{\text{perm}}$  is the dielectric dynamic permittivity. The total leakage current can be obtained by integral of leakage current density over the whole shape contour. It was shown in [33] that the EPG model agrees with some observed experimental results in terms of breakdown leakage currents over time as shown in Fig. 2.3.

#### 2.2 Faster TDDB analysis flow with the EPG model

This section presents a faster way to analyze ion concentration and TTF in EPG model based on the solution of the ion diffusion equation (2.3). Before proceeding, we show

Figure 2.3: Current-voltage leakage changes for different voltage (TDDB) stresses modeled by EPG model, compared with experimental data from [61], courtesy of [33].

Figure 2.4: Two example patterns with the same minimum distance (50nm) studied in FEM analysis using COMSOL.

| Paras                    | Value                                          | Paras    | Value                            |

|--------------------------|------------------------------------------------|----------|----------------------------------|

| $D_0$                    | $2.24 \times 10^{-11} \mathrm{m}^2/\mathrm{s}$ | $E_a$    | $0.8\mathrm{eV}$                 |

| $\varepsilon_{\rm perm}$ | 2.9                                            | $k_B$    | $1.38\times10^{-23}\mathrm{J/K}$ |

| Т                        | 370K                                           | $V_{DD}$ | 1V                               |

Table 2.1: Parameters and constants used

Table 2.2: Statistics of TTFs in different patterns with the same minimum distance (50nm)

| TTF(s) | Count | Percentage |

|--------|-------|------------|

| 360000 | 42    | 7.61%      |

| 370000 | 269   | 48.73%     |

| 380000 | 194   | 35.14%     |

| 390000 | 34    | 6.16%      |

| 400000 | 11    | 1.99%      |

| 410000 | 2     | 0.04%      |

Table 2.3: TTF results after changing  $D_0$  or  $E_a$

| Test cases             | TTF(s)  |

|------------------------|---------|

| Original case          | 363426  |

| $D_0$ increased by 10% | 327083  |

| $D_0$ decreased by 10% | 399767  |

| $E_a$ increased by 10% | 6113735 |

| $E_a$ decreased by 10% | 21604   |

that the minimum distance between metal wires is the dominant factor in determining the TTF as this is the starting point of this work.

FEM analysis of equation (2.3) using COMSOL has been done to simulate TTFs of 552 different patterns. In all these patterns, there are two metal wires and the minimum distance between them are the same. Two example patterns are shown in Fig. 2.4, where the two gray lines represent metal wires, one connected to VDD (supply voltage), and the other connected to GND (ground), and the white area is the dielectric in between.  $C_x = 0.95$ is employed as the threshold normalized minimum concentration leading to failure. The parameters and constants used in the FEM analysis are shown in Table 2.1. The diffusion coefficient  $D_0$  and activation energy  $E_a$  are obtained from fitting the experimental results in [61] as shown in Fig. 2.3.

| TTF(s) | Count | Percentage |

|--------|-------|------------|

| 58000  | 23    | 4.17%      |

| 59000  | 159   | 28.80%     |

| 60000  | 219   | 39.67%     |

| 61000  | 78    | 14.13%     |

| 62000  | 30    | 5.43%      |

| 63000  | 12    | 2.17%      |

| 64000  | 18    | 3.26%      |

| 65000  | 13    | 2.36%      |

Table 2.4: Statistics of TTFs in different patterns with the same minimum distance (20nm)

First, a test is done with patterns with minimum distance of 50nm. The results are listed in Table 2.2, where *Count* means the number of patterns with the corresponding TTF value. It is shown that the TTFs for most cases are in the range between 360000s and 41000s for the minimum spacing of 50nm. Note that  $D_0$  and  $E_a$  have huge impacts on the TTFs of TDDB as they determine the diffusion speeds of the barrier metal ions. We changed the two parameters and the results are shown in Table 2.3.

Table 2.4 shows the TTF range is between 58000s and 65000s for a second test with the minimum spacing of 20nm. The precision of this range is limited by the timestep set in COMSOL. It shows that the layer pattern has some impact on the TTF values, and this impact gets more significant for smaller minimum spacing. However, for both 50nm and 20nm minimum spacings, the impact on TTF is quite small for the majority of the patterns. It is also observed that the minimum spacing dominant effect becomes more obvious when the length of the wires is sufficiently long (compared to the spacing between them). Based on this observation, as a first-order approximation, the original problem can still be simplified to the one-dimensional problem with two parallel metal wires separated by the minimum distance like the one shown in Fig. 2.1a, which is the starting point of this work.

#### 2.2.1 Analytic solution of ion concentration in the IMD

The normalized concentration  $C_{norm}(x,t)$  is simplified as C(x,t) for the sake of better presentation. Then equation (2.3) can be rewritten as

$$D\nabla^2 C = \frac{qD}{k_B T} \nabla (C \cdot E) + \frac{\partial C}{\partial t}$$

(2.5)

with boundary condition:

$$C(\text{at the edge of dielectric}) = 1$$

(2.6)

and initial condition:

$$C(t = 0, \text{ within the dielectric}) = 0$$

(2.7)

Equation (2.5) can be further simplified to one-dimensional form given the previous discussion as follows:

$$D\frac{\partial^2 C}{\partial x^2} = \frac{qDE}{k_B T} \cdot \frac{\partial C}{\partial x} + \frac{\partial C}{\partial t}$$

(2.8)

with boundary condition:

$$C(x=0) = C(x=L) = 1$$

(2.9)

and initial condition:

$$C(x,t) = 0, 0 < x < L, t = 0$$

(2.10)

Further define  $X, T', \lambda$ , and L as

$$X = \frac{x}{L}, \quad T' = \frac{Dt}{L^2}, \quad \lambda = \frac{P_e}{2} = \frac{qE}{2k_BT}L = \frac{qV_{DD}}{2k_BT}$$

(2.11)

Equation (2.8) can be written as

$$\frac{\partial^2 C}{\partial X^2} = P_e \frac{\partial C}{\partial X} + \frac{\partial C}{\partial T'}$$

(2.12)

The solution of (2.12) can be found by using Laplace transformation based method as shown below. The detailed derivation of the solution can be found at the Appendix section.

$$C(X,T') = 1 - 2\pi \sum_{n=1}^{\infty} \frac{n \sin(n\pi X)}{(n^2 \pi^2 + \lambda^2)} e^{-(n^2 \pi^2 + \lambda^2)T'} \cdot \left[ e^{\lambda X} - (-1)^n e^{\lambda X - \lambda} \right]$$

(2.13)

Note that equation (2.13) is an exact analytic solution without any approximation.

#### 2.2.2 TDDB time to failure estimation

This section introduces three different methods to estimate TTF based on different approximation of equation (2.13). An easy yet inaccurate method is first introduced, followed by an accurate but inefficient version. Finally, a combined method of these two that is both accurate enough and efficient is introduced.

Before proceeding, it is worthwhile to note that the goal here is to find TTF, which is the time when min [C(X, TTF)] reaches the threshold normalized minimum concentration  $C_X$  for 0 < X < 1.

As equation (2.13) contains an infinite series, it is not possible to get an analytical result of TTF. However, numerical methods are still feasible. First, it is natural to consider using first term approximation because of its simplicity. The first term approximation of equation (2.13) is:

$$C_1(X,T') = 1 - \frac{2\pi \sin(\pi X)}{\lambda^2 + \pi^2} e^{-(\lambda^2 + \pi^2)T'} \left( e^{\lambda X} + e^{\lambda X - \lambda} \right)$$

(2.14)

This equation can be used to derive where the minimum concentration locates (labeled by  $X_{fail}$ ) by calculating the partial derivative of concentration with respect to Xand solve for the zero points. Then, a fixed  $X_{fail}$  which does not change with T' can be derived:

$$X_{fail} = 1 - \frac{1}{\pi} \arctan\left(\frac{\pi}{\lambda}\right) \tag{2.15}$$

This  $X_{fail}$  can be used back in equation (2.14) to solve for TTF, which gives the result:

$$TTF = \frac{L^2}{D(\lambda^2 + \pi^2)} \ln \frac{2\pi^2 \left( e^{\lambda - (\lambda/\pi) \arctan(\pi/\lambda)} + e^{-(\lambda/\pi) \arctan(\pi/\lambda)} \right)}{(1 - C_X) \left( \lambda^2 + \pi^2 \right)^{3/2}}$$

(2.16)

The details of this derivation can be found at the Appendix section. This is the first method to evaluate TTF. However, the results from above equation (2.16) are not accurate as shown in Section 2.4.

The second method which is quite accurate contains two iterative phases, namely X and T' phases. First, in order to conduct sufficiently accurate approximation of equation (2.13), it is preferred to use a large number of terms (10000 terms are used in experiments) of the infinite series. Then, because the concentration is monotonically increasing with respect to T', so the bisection method can be used to numerically find TTF efficiently on condition that X is fixed. This is the T' phase, which is named because it solves T' with X fixed. Issues about  $X_{fail}$  can be tackled by the fact that there exists only one minimum value of concentration with respect to X. Therefore in X phase  $X_{fail}$  can be searched step by step with a fixed T' from the previous T' phase. In detail, X is adjusted with a small enough  $X_{step}$  in each searching step until the minimum concentration at  $X_{fail}$  is found. Then, a new T' phase may be started for more accurate TTF. The final result can be found by performing two phases iteratively for only a few times.

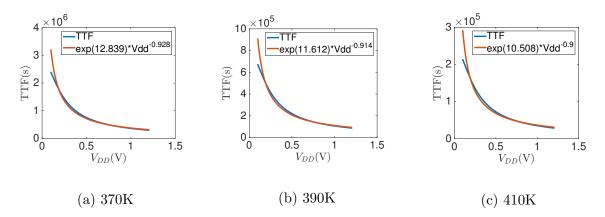

| Temperature(K) | B(T)           | N      |

|----------------|----------------|--------|

| 370            | $\exp(12.839)$ | -0.928 |

| 390            | $\exp(11.612)$ | -0.914 |

| 410            | $\exp(10.508)$ | -0.9   |

Table 2.5: Fitted coefficients of the power law model

This is the most accurate yet most complicated method. In fact, the previous two methods can be combined together to get an accurate and simple method.

As discussed above, the bisection method can be used to numerically find TTF if we use 3 or 5 terms for approximation. Note that an odd number of terms is used because the function of concentration has to be monotonic. At the same time,  $X_{fail}$  given by equation (2.15) can be directly used so the X phase can be skipped. The latter Section 2.4 shows that results derived from this simple method are quite accurate. In short, the X\_min in equation (2.15) can be used and then the 3 terms approximation based bisection method can be employed to numerically derive an accurate enough TTF.

A pseudocode describing this evaluation flow through bisection method is listed in Algorithm 1.  $C_{min}(T')$  stands for the ion concentration calculated through a certain approximation of equation (2.13) (for example, 3-terms approximation), with  $X = X_{fail}$ from equation (2.15).

#### 2.2.3 Study of the relationship between TTF and electric field

This section focuses on the relationship between the TTF and stressing electric filed or voltage for the EPG TDDB model. It is shown that EPG model shows similar

#### Algorithm 1 Evaluation of TTF

- 1: Set parameters such as spacing L, stressing voltage  $V_{DD}$

- 2: Calculate  $X_{fail}$  from equation (2.15)

- 3: Set initial T' = 1, result error tolerance eps

- 4: while  $C_{min}(T') < C_X$  do

- 5: T' = T' \* 2

- 6: end while

- 7: a = 0, b = T', c = (a + b)/2

- 8: while b a < eps do

- 9: **if**  $(C_{min}(a) C_X) * (C_{min}(c) C_X) < 0$  **then**

- 10: b = c, c = (a + b)/2

- 11: else if  $(C_{min}(b) C_X) * (C_{min}(c) C_X) < 0$  then

- 12: a = c, c = (a + b)/2

- 13: **else**

- 14: break

- 15: **end if**

- 16: end while

- 17:  $T'_{fail} = c$

Figure 2.5: TTF against different stressing voltages  $(V_{DD})$  under different temperatures.

relationship between TTF and electric field of the power law model [43, 68]:

$$TTF = B(T)V^{N} \tag{2.17}$$

To illustrate this, TTF is calculated with the most accurate method introduced in Section 2.2.2 over different electric fields. The pattern studied is still the same pattern used above. Only supply voltage  $V_{DD}$  is sweeped so that electric field can be changed. Fitted coefficients of the power-law model under different temperatures are shown in Table 2.5. Furthermore, Fig. 2.5 show the TTF predicted by the fitting power law models against our EPG models under different temperatures.

The fitted voltage exponent N is around 0.9 for different temperature, which is quite smaller than other power law models with N ranging from 40 to 48 [43] or even 24-36 [68]. In addition, the recent experimental data from the published BEOL TDDB power law models show that the exponent N is around 20-24 [16, 46]. However, in the EPG model, the material (Ta) and structure (confined copper with Ta as the barrier layer and low-k dielectrics) are totally different with those experiment settings. The underlying breakdown physics is also different. As a result, the fitted exponent, N, can be significant different than the existing power law models.

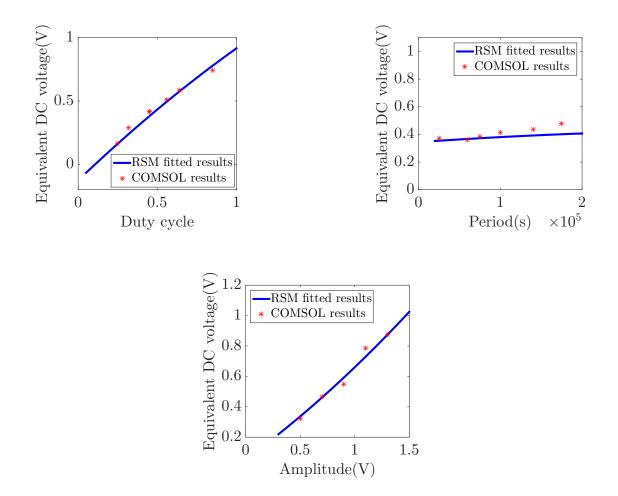

#### 2.3 Equivalent DC stressing voltage analysis of EPG model

In the previous discussion, it is assumed that two metal wires in the pattern are connected to VDD and GND respectively. In real digital ICs, this scenario does not apply to every two neighboring wires, as there are other kinds of wires such as clock net and signal net. However, it is still feasible to assume that the voltages on both wires can be modeled as DC or a square wave. With this being said, it is obvious that the electric field within the IMD can be modeled as a square wave. For simplicity, it is assumed to be unipolar and it covers the cases where voltage of one metal wire is constant. Three parameters can be used to define this unipolar square wave: amplitude, period, and duty cycle. With them, a function can be fitted to convert any unipolar square wave to the equivalent DC stressing voltage provided that they result in the same TTF. Other cases resulting in bipolar square wave can be treated with the same method, but with one more parameter.

Before moving on, we first review the response surface method (RSM), which is used in this study. RSM, consisting of a group of mathematical and statistical techniques, explores the relationships between several input variables and one or more responses. Based on a set of designed experiments, an optimal response can be obtained [48]. Specifically in RSM, input parameters are called independent variables and performance measure is considered as a response. Response y depends on input independent variables  $(\xi_1, \xi_2, \ldots, \xi_k)$

$$y = f(\xi_1, \xi_2, \dots, \xi_k) + \varepsilon \tag{2.18}$$

where f is the true response function which is unknown and could be very complicated and  $\varepsilon$  is an error of the model. Usually, a low-order polynomial in some relatively small region of the independent variable space is appropriate. First order model or second order model are the most commonly used models in RSM. In this article, second order model with relatively good accuracy is employed. A second-order response y depending on variables  $(x_1, x_2, \ldots, x_k)$  can be written as:

$$y = \beta_0 + \sum_{j=1}^k \beta_j x_j + \sum_{j=1}^k \sum_{i \le j} \beta_{ij} x_i x_j + \varepsilon$$

(2.19)

Let  $x_{k+1} = x_1 x_1, x_{k+2} = x_1 x_2, \dots, x_{k(k+3)/2-1} = x_{k-1} x_k, x_{k(k+3)/2} = x_k x_k$  and  $\beta_{k+1} = \beta_{11}, \beta_{k+2} = \beta_{12}, \dots$  then equation (2.19) can be expressed as

$$y = \beta_0 + \sum_{j=1}^q \beta_j x_j + \varepsilon \tag{2.20}$$

which is a linear regression model for coefficients  $(\beta_0, \beta_1, \ldots, \beta_q)$ , where q = k(k+3). With equation (2.20), least square method is employed to estimate the regression coefficients in the multiple linear regression model.

We assume that there are *n* observed responses  $y = (y_1, y_2, \ldots, y_n)$  and for each  $y_i$ , there are corresponding parameters  $x_i = (x_{i1}, x_{i2}, \ldots, x_{iq})$ . So equation (2.20) can be written in matrix notation as follow:

$$y = X\beta + \varepsilon \tag{2.21}$$

To solve  $\beta$  in a least square minimization sense, QR decomposition on X is applied. It is shown that  $R\beta = Q^T y$ . After solving the linear equations, estimated coefficient vector  $\hat{\beta}$  can be calculated. In this work, the input variables  $x_i$  are normalized parameters, which include amplitude, period, and duty cycle. The TTFs for DC stressing voltage are calculated using methods introduced in Section 2.2.2. A formula has been fitted to quickly find the equivalent DC voltage with the given TTF. TTFs for different square wave stressing voltage are derived using COMSOL.

Because of the limitation of timestep in FEM analysis, the period of square wave must be very long compared to practical cases.

## 2.4 Experimental results and discussions

This section shows the numerical results and comparisons for the new TDDB analysis flow. All programs run on a workstation with Xeon E5-2698 CPU and 128GB memory.

The first experiment is to test the accuracy of the derived analytic solution in equation (2.13) by comparing it with the results from COMSOL FEM analysis. The results are shown in Table 2.6. The data is based on the pattern shown in Fig. 2.1a, in which the distance between two metal wires is 50nm, and temperature is 370K. The metal wire at x = 0 is connected to VDD and the wire at x = 50 is connected to GND. As shown in the table, the proposed closed form expression give very accurate results compared to COMSOL simulations.

The second experiment is about the accuracy and calculation CPU time of different methods for TTF based on the same pattern above.  $C_x = 0.95$  as the threshold normalized minimum concentration leading to failure in the experiment. For the comparison, the result using 10000 terms and the resulting changes in  $X_{fail}$  is used as the golden results. The comparison results are shown in Table 2.7. In the last four rows,  $X_{fail}$  from equation (2.15)

| Time(s)           | x(nm) | FEM     | Results       | Error (%) |

|-------------------|-------|---------|---------------|-----------|

|                   |       |         | from $(2.13)$ |           |

| $1 \times 10^{5}$ | 35.97 | 0.01377 | 0.01363       | 1.03%     |

| $1 \times 10^{5}$ | 46.56 | 0.11680 | 0.11485       | 1.68%     |

| $2 \times 10^{5}$ | 11.67 | 0.99512 | 0.99527       | 0.01%     |

| $2 \times 10^{5}$ | 33.62 | 0.66238 | 0.66012       | 0.34%     |

| $3 \times 10^{5}$ | 20.49 | 0.99691 | 0.99754       | 0.06%     |

| $3 \times 10^{5}$ | 42.83 | 0.85763 | 0.85553       | 0.24%     |

Table 2.6: Results of ion concentration derived from two methods

Table 2.7: TTF from different methods, the calculation times and speedup over FEM

| Method               | TTF(s) | Error (%) | Time(s) | Speed-up |

|----------------------|--------|-----------|---------|----------|

| 10000 terms w-       | 363426 | -         | 8.702   | 4.94     |

| ith exact $X_{fail}$ |        |           |         |          |

| FEM                  | 370000 | 1.81%     | 43.000  | —        |

| 10000 terms          | 363221 | 0.06%     | 3.468   | 12.40    |

| 5 terms              | 363221 | 0.06%     | 0.013   | 3.31E3   |

| 3 terms              | 366562 | 0.86%     | 0.009   | 4.78E3   |

| 1 term               | 412568 | 13.52%    | 0.004   | 1.08E4   |

is used instead of more accurate  $X_{fail}$  for the sake of simplicity. Column **Error(%)** is the relative error compared to the golden. **Times(s)** is the CPU times and column **Speed-up** is the speedup against FEM.

The table shows that if 5 terms are used, the result is sufficiently accurate compared to 10000 terms as they can give almost the same results. If only 3 terms are used, the results can be very accurate as well. In terms of CPU time and speedup, the speedup ranges from  $15 \text{ to } 1.08 \times 10^4$ . Results from 3-terms show a good compromise between accuracy and speed, which gives about 0.86% accuracy, and the speedup more than three order of magnitude  $(4.78 \times 10^3)$ .

The same experiment with the spacing of 20nm is also done using 3-terms method. The result of TTF is 58650s. Basically, the analytic solution (2.13) shows that if only spacing changes, then it holds that  $TTF \propto L^{-2}$ .

Last but not least, the RSM fitted results are tested by calculating the equivalent DC stressing voltage for different stressing voltages and comparing the results of TTF from COMSOL. The fitted function to calculate equivalent voltage when T = 370K is:

$$V_{eq} = 0.4794 + 0.1606X_1 + 0.4675X_2 + 0.0185X_3$$

+ 0.0075X\_1^2 + 0.1563X\_1X\_2 + 0.0133X\_1X\_3 (2.22)

- 0.0323X^2 - 0.0252X\_2X\_3 - 0.0031X\_3^2

where

$$X_1 = \frac{\text{Amplitude(V)} - 0.9}{0.3} \quad X_2 = \frac{\text{Duty cycle} - 0.54}{0.46} \quad X_3 = \frac{\text{Period(s)}/1000 - 120}{80}$$

Some tests with parameters given in Table 2.8 have been done to test the correctness of this function. All these test cases are not used in building the RMS function. Each time only one of the three parameters is changed so a graph showing the impact of this variable can be drawn. The graphs are shown in Fig. 2.6. In the graphs, the COMSOL results are derived by searching for equivalent DC voltages based on TTF results from COMSOL. It can be seen that these graphs prove that RMS gives a good result for evaluating equivalent DC voltage.

It is worth mentioning that in the cases with the changeable distance between two metal wires, this result can still be used in that the distance L does not appear in equation (2.13). The only thing it can affect is the relationship between T' and t, as is

Table 2.8: Parameters for 3 tests

| Amplitude(V) | Duty cycle       | Period(s)           |

|--------------|------------------|---------------------|

| 0.9          | $0.25 \sim 0.85$ | 100000              |

| 0.9          | 0.45             | $25000 \sim 175000$ |

| 0.5~1.3      | 0.65             | 140000              |

Figure 2.6: Comparison between RSM results with COMSOL results on different parameters.

introduced in equation (2.11). So distance does not change the function of equivalent DC voltage at all.

## 2.5 Summary

The work presented in this chapter introduces a fast way to evaluate TDDB life time based on the EPG TDDB model. It is based on the analytic solution of the ion diffusion partial differential equation. It is shown that the location of the minimum concentration can be determined by the dominant terms and the TTF can be computed by using a few dominant terms. On top of this, the method is extended to cover time-varying stressing voltage, which is commonly seen in practical VLSI chips. The equivalent DC stressing voltage, parameterized by amplitude, duty cycle, and period for periodic stressing voltage waveforms, is calculated using regression based method. Numerical experiments validate that the proposed analytic TDDB concentration and TTF formula and the equivalent DC stressing voltage compact model against the results from FEM analysis using COMSOL. It is further shown that the new compact TDDB model can lead to three orders of magnitude speedup with less than 1% error.

## 2.6 Appendix

#### 2.6.1 Derivation of the analytic solution for the ion diffusion equation

In this section, we give the detailed mathematical derivation of the formulas for the proposed TDDB compact model. For the completeness of this section, the metal ion diffusion equation (2.5) is rewritten as follows:

$$D\nabla^2 C = \frac{qDE}{k_B T} \nabla C + \frac{\partial C}{\partial t}$$

(2.23)

with the boundary conditions:

$$C(\text{at the edge of dielectric}) = 1$$

(2.24)

In the one dimensional case, (2.23) can be written as

$$D\frac{\partial^2 C}{\partial x^2} = \frac{qDE}{k_B T} \cdot \frac{\partial C}{\partial x} + \frac{\partial C}{\partial t}$$

(2.25)

subject to boundary conditions:

$$C(x=0) = C(x=L) = 1$$

(2.26)

$$C(x,t) = 0, 0 < x < L, t = 0$$

(2.27)

Define:

$$X = \frac{x}{L} \qquad T' = \frac{Dt}{L^2} \qquad P_e = \frac{qE}{k_B T} L = \frac{qV_{dd}}{k_B T}$$

(2.28)

It gives:

$$\frac{\partial^2 C}{\partial X^2} = P_e \frac{\partial C}{\partial X} + \frac{\partial C}{\partial T'}$$

(2.29)

After the Laplace transformation, it gives

$$\frac{d^2\hat{C}}{dX^2} = P_e \frac{d\hat{C}}{dX} + p\hat{C}$$

(2.30)

subject to boundary conditions:

$$\hat{C}(0,p) = \hat{C}(1,p) = \frac{1}{p}$$

(2.31)

where p is the Laplace domain variable. For the differential equation (2.30), its solution would appear in this following general form:

$$\hat{C} = r_1 e^{p_1 X} + r_2 e^{p_2 X} \tag{2.32}$$

where  $p_1$  and  $p_2$  are the roots for equation  $x^2 = P_e x + p$ . As a result, it gives  $p_{1,2} = \frac{P_e}{2} \pm a$ ,  $a = \sqrt{\frac{P_e^2}{4} + p}$  with the following boundary conditions

$$\begin{cases} r_1 + r_2 = \frac{1}{p} \\ r_1 e^{a + P_e/2} + r_2 e^{-a + P_e/2} = \frac{1}{p} \end{cases}$$

(2.33)

By solving for  $r_1$  and  $r_2$ , one can obtain the solution in Laplace domain as

$$\hat{C}(p) = \frac{e^{P_e X/2} \sinh\left[a(1-X)\right]}{p \sinh(a)} + \frac{e^{P_e (X-1)/2} \sinh(aX)}{p \sinh(a)}$$

(2.34)

Inverse Laplace transform on (2.34) is then done to obtain the solution in the time domain. First take a look at the first part of (2.34), which is

$$\hat{C}_1 = \frac{e^{P_e X/2} \sinh[a(1-X)]}{p \sinh(a)}$$

A property of Laplace transform as this is used here:

$$\mathcal{L}^{-1}\left\{\hat{C}(X,p+b)\right\} = e^{-bT'}\mathcal{L}^{-1}\left\{\hat{C}(X,p)\right\}$$

Then it gives

$$C_1 = e^{\lambda X - bT'} \cdot \mathcal{L}^{-1} \left\{ \frac{\sinh\left[p^{1/2}(1-X)\right]}{(p-b)\sinh(p^{1/2})} \right\}$$

(2.35)

where  $b = \frac{P_e^2}{4}$ . Assume  $\lambda = b^{1/2} = \frac{P_e}{2}$ . The inverse transform can be derived by adding residues at all poles, in this case there is a pole at p = b, and poles at  $p^{1/2} = n\pi i$ ,  $n = b^{1/2} = n\pi i$ .

$0, \pm 1, \pm 2...,$  or equally  $p = -n^2 \pi^2, n = 0, 1, 2...$

$$\mathcal{L}^{-1}\left\{\frac{\sinh\left[p^{1/2}(1-X)\right]}{(p-b)\sinh(p^{1/2})}\right\} = \int_{C} \frac{\sinh\left[p^{1/2}(1-X)\right]}{(p-b)\sinh(p^{1/2})} e^{pT'} dp$$

$$= \frac{\sinh\left[\lambda(1-X)\right]}{\sinh(\lambda)} e^{\lambda^{2}T'} - 2\pi \sum_{n=1}^{\infty} \frac{n\sin(n\pi X)}{(n^{2}\pi^{2}+\lambda^{2})} e^{-n^{2}\pi^{2}T'}$$

(2.36)

The second part can be treated in the same way. After the inverse transformation, two parts are combined. With some additional algebraic operations the final result is obtained:

$$C(X, T') = e^{\lambda X} \left\{ \frac{\sinh [\lambda(1-X)]}{\sinh(\lambda)} - 2\pi \sum_{n=1}^{\infty} \frac{n \sin(n\pi X)}{(n^2 \pi^2 + \lambda^2)} e^{-(n^2 \pi^2 + \lambda^2)T'} \right\} + e^{\lambda X - \lambda} \left\{ \frac{\sinh(\lambda X)}{\sinh(\lambda)} + 2\pi \sum_{n=1}^{\infty} \frac{(-1)^n n \sin(n\pi X)}{(n^2 \pi^2 + \lambda^2)} e^{-(n^2 \pi^2 + \lambda^2)T'} \right\} = \frac{e^{\lambda X} \sinh [\lambda(1-X)] + e^{\lambda X - \lambda} \sinh(\lambda X)}{\sinh(\lambda)}$$

(2.37)

$$- e^{\lambda X} 2\pi \sum_{n=1}^{\infty} \frac{n \sin(n\pi X)}{(n^2 \pi^2 + \lambda^2)} e^{-(n^2 \pi^2 + \lambda^2)T'} + e^{\lambda X - \lambda} 2\pi \sum_{n=1}^{\infty} \frac{(-1)^n n \sin(n\pi X)}{(n^2 \pi^2 + \lambda^2)} e^{-(n^2 \pi^2 + \lambda^2)T'} = 1 - 2\pi \sum_{n=1}^{\infty} \frac{n \sin(n\pi X)}{(n^2 \pi^2 + \lambda^2)} e^{-(n^2 \pi^2 + \lambda^2)T'} \left[ e^{\lambda X} - (-1)^n e^{\lambda X - \lambda} \right]$$

## 2.6.2 Derivation of analytic form for time to failure

As approximation, let's take the first term of the analytic solution  $C(X,T^\prime)$  as  $C_1(X,T^\prime) \text{:}$

$$C_1(X,T') = 1 - \frac{2\pi \sin(\pi X)}{\lambda^2 + \pi^2} e^{-(\lambda^2 + \pi^2)T'} \left( e^{\lambda X} + e^{\lambda X - \lambda} \right)$$

(2.38)

To get the minimum concentration, the derivative of  $C_1(X, T')$  is set to zero:

$$\frac{\partial C_1(X,T')}{\partial X} = 0$$

$$= \frac{2\pi e^{-(\lambda^2 + \pi^2)T'}}{\lambda^2 + \pi^2} e^{\lambda X} \left(1 + e^{-\lambda}\right) \left[\lambda \sin\left(\pi X\right) + \pi \cos\left(\pi X\right)\right]$$

(2.39)

The solution of this equation gives a fixed  $X_{fail}$  which does not change with T' as

$$X_{fail} = 1 - \frac{1}{\pi} \arctan\left(\frac{\pi}{\lambda}\right) \tag{2.40}$$

Then at  $X_{fail}$ , define  $C(X_{fail}, T') = C_{fail}$  as the minimum concentration that

triggers the dielectric failure

$$C_{fail} = 1 - \frac{2\pi e^{-(\lambda^2 + \pi^2)T'}}{\lambda^2 + \pi^2} \sin \left[\pi - \arctan(\pi/\lambda)\right] \cdot \left(e^{\lambda - (\lambda/\pi)\arctan(\pi/\lambda)} + e^{-(\lambda/\pi)\arctan(\pi/\lambda)}\right)$$

(2.41)

$$= 1 - \frac{2\pi^2 e^{-(\lambda^2 + \pi^2)T'}}{(\lambda^2 + \pi^2)^{3/2}} \cdot \left(e^{\lambda - (\lambda/\pi)\arctan(\pi/\lambda)} + e^{-(\lambda/\pi)\arctan(\pi/\lambda)}\right)$$

(2.42)

The resulting time to failure can be found by solving:

$$C_{fail} = C_X$$

$$T'_{fail} = \frac{1}{\lambda^2 + \pi^2} \ln \frac{2\pi^2 \left( e^{\lambda - (\lambda/\pi) \arctan(\pi/\lambda)} + e^{-(\lambda/\pi) \arctan(\pi/\lambda)} \right)}{(1 - C_X) \left( \lambda^2 + \pi^2 \right)^{3/2}}$$

(2.43)

$$t_{fail} = \frac{L^2}{D(\lambda^2 + \pi^2)} \ln \frac{2\pi^2 \left( e^{\lambda - (\lambda/\pi) \arctan(\pi/\lambda)} + e^{-(\lambda/\pi) \arctan(\pi/\lambda)} \right)}{\left(1 - C_X\right) \left(\lambda^2 + \pi^2\right)^{3/2}}$$

(2.44)

## Chapter 3

# Full-Chip Wire-Oriented TDDB Analysis

The simplified TDDB evaluation method introduced in chapter 2 focuses on the spacing of IMD. For simplicity, the method treats all interconnect structures with same distance as parallel structures. This, however, ignores the complicated geometries of all the layout patterns, which is related to TDDB lifetime. Also, the results of TTF in fact represent the probability of failure. The breakdown can happen anywhere in the IMD analyzed. As a result, for more practical and accurate results, the overall probability of failure of the given IMD should take in consideration the length and shape of it [3].

Based on this idea, the work presented in chapter proposes a full-chip TDDB failure analysis methodology to evaluate lifetime and identify TDDB hotspots in VLSI layouts, which are essentially interconnect wires that have high failure risk due to TDDB. The proposed method features three new techniques compared to existing methods. First, a partition based scheme is developed to deal with the vast scale of full-chip analysis by partitioning the full chip layout into smaller tiles. Second, for each tile, a newly-introduced TDDB failure metric called *TDDB Damage* is calculated for all wires. Such a wire-oriented TDDB analysis is the first of its kind and is very amenable for physical design as the wires can be easily adjusted or re-routed for TDDB-aware optimization. Third, the new method considers the impact of the non-uniform electric field calculated using the finite element method (FEM), which significantly improves the accuracy of TDDB risk evaluation. Experimental results show that the proposed new TDDB analysis method is more accurate than a recently proposed full-chip TDDB analysis method in which electrical field is treated as a constant value. Additionally, the proposed method can analyze a practical VLSI layout in a few hours. This work is published in [50].

## 3.1 Overview

As stated, simple interconnect leakage test structures such as serpentine-comb or comb-comb have been typically used in the studies of BEOL TDDB [67]. In contrast, very little work has been done to develop a framework for assessing BEOL TDDB risk in practical and actual circuit layout geometries, which this work focuses on. The difference between the two are two folds. First, the probability of failure of IMD grows with its length. Second, complicated layout geometries can also play an important role.

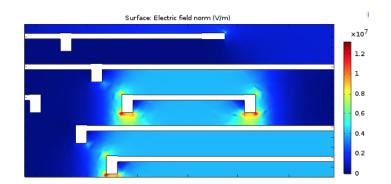

The effect of layout geometries can be seen in a simple simulation. The results through FEM analysis of electric field in a small piece of a synthesized layout shown in Fig. 3.1 reveals that with a voltage difference between neighboring wires, the electric field

Figure 3.1: FEM analysis result showing higher electric field around tips

at "corners" or "tips" of wires can actually differ greatly from that along longer, straightline segments, leading to the so called "layout effects' [32]. The higher electric field at tips can substantially reduce the lifetime of such wires, making the results scaled from test data optimistic and inaccurate. Thus, more applicable methods considering such layout effects are required if experimental data is to be used in practical lifetime analysis.

Because this method is based on solving electric field, unlike [3], it covers the non-uniform electrical field and cover local field enhancement effects, which leads to more accurate TDDB lifetime estimation. Additionally, the proposed methods can be applied to all the existing electric field-dependent TDDB models such as E, 1/E, power-law, and  $\sqrt{E}$ models. Numerical results show that the proposed method can identify the TDDB hotspots for a practical VLSI layout in a reasonable amount of time. It is further shown that M1 (Metal1) typically has the shortest lifetime because of the highest metal density.