# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

High Performance CMOS SOI Gbps Millimeter-Wave Transceivers, Phased-Arrays and Switching Networks

Permalink https://escholarship.org/uc/item/97s476fn

Author Yang, Yang

Publication Date 2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SAN DIEGO

### High Performance CMOS SOI Gbps Millimeter-Wave Transceivers, Phased-Arrays and Switching Networks

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Yang Yang

Committee in charge:

Professor Gabriel M. Rebeiz, Chair Professor James Buckwalter Professor William S. Hodgkiss Professor Brian G. Keating Professor Patrick Mercier

2018

Copyright Yang Yang, 2018 All rights reserved. The dissertation of Yang Yang is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California San Diego

2018

DEDICATION

To my wife, Mengfei Li.

To my parents, Nanzi Xie and Xun Yang.

To my Father in heaven.

## TABLE OF CONTENTS

| Signature Page  | е                                        |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             | •••                                                 |                                                        |                                     |                  | • •                             | •   |                         |                                       |                       | •                |                                           |                                 |                                       |                                           |                                           | iii                                                                  |

|-----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|-------------------------------------|------------------|---------------------------------|-----|-------------------------|---------------------------------------|-----------------------|------------------|-------------------------------------------|---------------------------------|---------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|

| Dedication .    |                                          |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 |     |                         |                                       |                       |                  |                                           |                                 |                                       |                                           | . <b>.</b>                                | iv                                                                   |

| Table of Conte  | ents .                                   |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 | •   |                         |                                       |                       |                  |                                           |                                 |                                       |                                           |                                           | v                                                                    |

| List of Figures | s                                        |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 |     |                         |                                       |                       |                  |                                           |                                 |                                       |                                           |                                           | vii                                                                  |

| List of Tables  |                                          |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 |     |                         |                                       |                       |                  |                                           | •                               |                                       |                                           | , <b>.</b>                                | Х                                                                    |

| Acknowledge     | ments                                    |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 | •   |                         |                                       |                       |                  |                                           |                                 |                                       |                                           |                                           | xi                                                                   |

| Vita            |                                          |                                                                                                                                   |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 | •   |                         |                                       |                       |                  |                                           |                                 |                                       | • •                                       |                                           | xiii                                                                 |

| Abstract of the | e Diss                                   | ertation                                                                                                                          |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 | •   |                         |                                       |                       |                  |                                           |                                 |                                       |                                           |                                           | xiv                                                                  |

| Chapter 1       | Intro                                    | duction                                                                                                                           |                                                                                       |                                                                                        |                                                                             |                                                     |                                                        |                                     |                  |                                 | •   |                         |                                       |                       |                  |                                           |                                 |                                       |                                           |                                           | . 1                                                                  |

| Chapter 2       | Milli<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | meter-W<br>Introdu<br>Design<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>Measu<br>Conclu<br>Acknoo | and S<br>Syste<br>Techi<br>Wilki<br>W-ba<br>Vecto<br>Quad<br>High-<br>Syste<br>rement | ingle<br>m Are<br>nolog<br>inson<br>nd Ar<br>or Moo<br>rupler<br>-Effici<br>m-Le<br>ts | Bloc<br>chited<br>y<br>and I<br>mplifi<br>dulate<br>r<br>iency<br>vel S<br> | k Mo<br>cture<br>Hybr<br>ier w<br>or<br>On-<br>imul | easu<br>easu<br>rid C<br>vith<br><br>-Chi<br>latic<br> | <br>Iren<br><br>Couj<br>Hig<br><br> | nent             | <br>s<br>s<br>AE<br><br>nna<br> |     | <br><br><br><br><br>    | · · · · · · · · · · · · · · · · · · · | ·<br>·<br>·<br>·<br>· | ·<br>·<br>·<br>· | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · · | ·<br>·<br>·<br>·<br>·<br>·<br>· | · · · · · · · · · · · · · · · · · · · | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · · | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · · | 4<br>5<br>5<br>7<br>9<br>9<br>14<br>17<br>17<br>20<br>22<br>29<br>29 |

| Chapter 3       | Gbps<br>3.1<br>3.2<br>3.3                | Millim<br>Introdu<br>Design<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>Measu                                                 | Trans<br>Oscil<br>I/Q M<br>I/Q M<br>Packa                                             | <br>sceive<br>lator,<br>lixer a<br>lodula                                              | · · · ·<br>r Top<br>Activ<br>and I<br>ator I                                | oolog<br>ve Sj<br>F Ai<br>Desig                     | <br>gy .<br>plitt<br>mpli<br>gn<br>                    | <br><br>er a<br>fier<br>            | <br><br>nd I<br> | <br><br>Dou<br>                 | ble | · · ·<br>· · ·<br>· · · | · · ·                                 |                       | •<br>•<br>•<br>• | · ·<br>· ·<br>· ·                         |                                 |                                       | · · ·                                     | · · ·                                     | 30<br>30<br>30<br>30<br>32<br>33<br>35<br>35<br>35<br>38             |

|              |       | 3.3.1   | Oscilla  | ator, 2 | Acti | ve S  | plit | ter | and | Re  | cei | ver |   |   | • |   |  |     | 38 |

|--------------|-------|---------|----------|---------|------|-------|------|-----|-----|-----|-----|-----|---|---|---|---|--|-----|----|

|              |       | 3.3.2   | Modul    | ator    | Mea  | isure | me   | nts |     |     |     |     |   |   | • |   |  |     | 43 |

|              |       | 3.3.3   | Transc   | eiver   | Me   | asur  | em   | ent | s.  |     |     |     |   |   | • |   |  |     | 48 |

|              | 3.4   | Conclu  | ision .  |         |      |       |      |     |     |     |     |     |   |   | • |   |  |     | 52 |

|              | 3.5   | Ackno   | wledgm   | ent     | •••  |       |      | •   | ••• | • • | • • | •   | • | • | • |   |  |     | 52 |

| Chapter 4    | Swite | ch Netw | vorks .  |         |      |       |      |     |     |     |     |     | • |   |   |   |  |     | 54 |

| -            | 4.1   | Introdu | iction . |         |      |       |      |     |     |     |     |     |   |   | • |   |  |     | 54 |

|              | 4.2   | Design  | ι        |         |      |       |      |     |     |     |     |     |   |   | • |   |  |     | 55 |

|              | 4.3   | Measu   | rements  |         |      |       |      |     |     |     |     |     |   |   | • |   |  |     | 67 |

|              | 4.4   | Conclu  | ision .  |         |      |       |      |     |     |     |     |     |   |   | • |   |  |     | 76 |

|              | 4.5   | Ackno   | wledgm   | ent     | •••  |       |      | •   | ••• | • • |     | •   | • | • | • | • |  | ••• | 76 |

| Chapter 5    | Conc  | lusion  |          |         |      |       |      |     |     |     |     |     | • |   |   |   |  |     | 83 |

| L            | 5.1   |         | Works    |         |      |       |      |     |     |     |     |     |   |   |   |   |  |     |    |

| Bibliography |       |         |          |         |      |       |      |     |     |     |     |     |   |   | • |   |  |     | 86 |

## LIST OF FIGURES

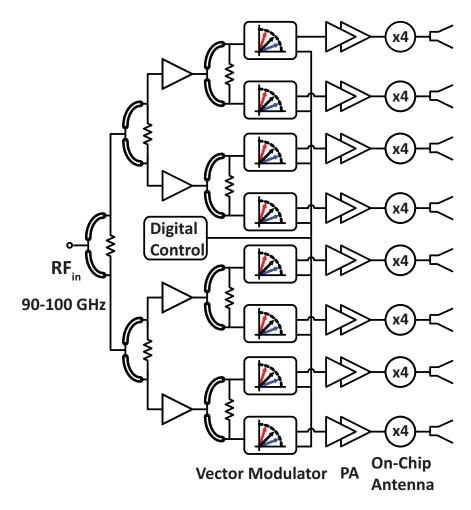

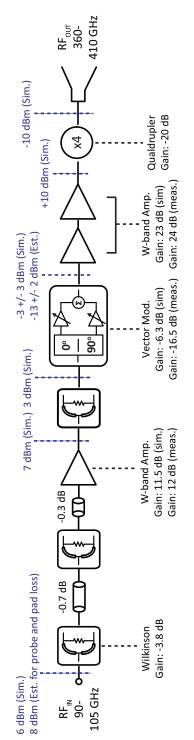

| Figure 2.1:   | Block diagram of the 400 GHz phased-array transmitter.                                                  | 6    |

|---------------|---------------------------------------------------------------------------------------------------------|------|

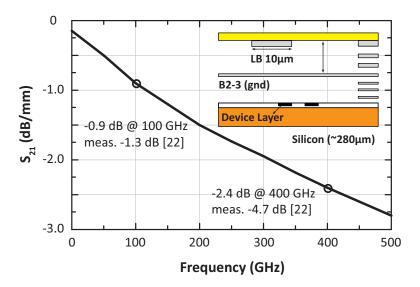

| Figure 2.2:   | GF 45 nm SOI process. and simulated loss of a 1 mm long 50 $\Omega$ microstrip                          |      |

| C             | line                                                                                                    | 8    |

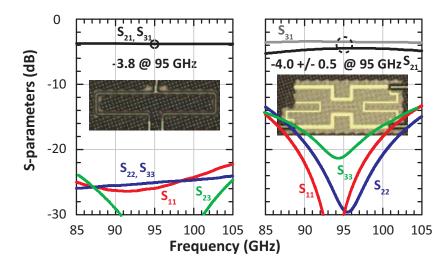

| Figure 2.3:   | Simulated S-parameters of W-band Wilkinson and hybrid couplers. The                                     |      |

| 8             | wilkinson coupler is 348 x 63 $\mu$ m <sup>2</sup> and hybrid coupler is 368 x 138 $\mu$ m <sup>2</sup> | 8    |

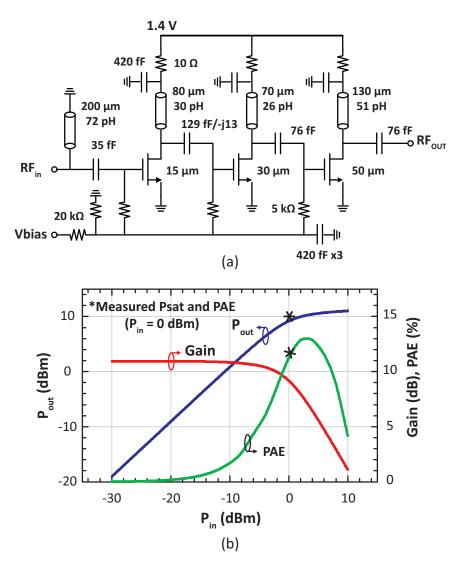

| Figure 2.4:   | W-band amplifier: (a) schematic and (b) simulated gain output power and                                 | -    |

|               | PAE at 95 GHz.                                                                                          | 10   |

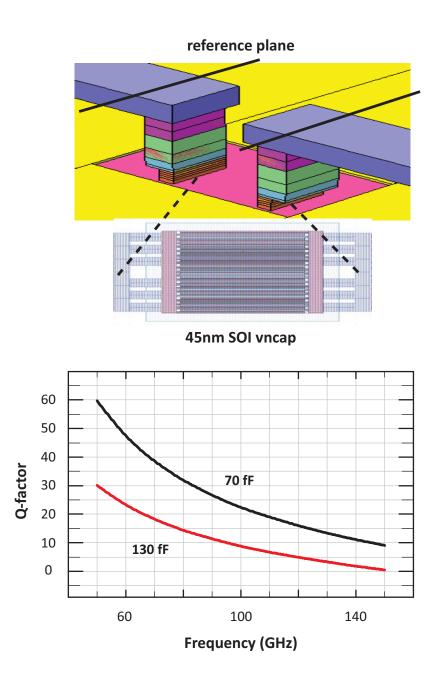

| Figure 2.5:   | Simulated Q-factor of 45nm SOI capacitors (vncap) versus frequency.                                     | 12   |

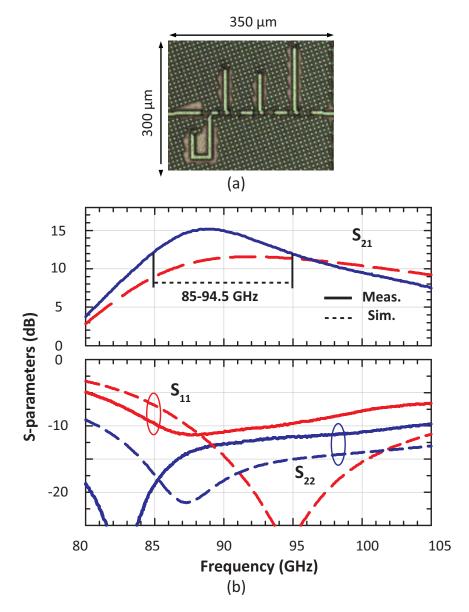

| Figure 2.6:   | (a) W-band amplifier microphotograph, and (b) measured S-parameters. The                                | 12   |

| 1 iguie 2.0.  | 3-dB bandwidth is 85-94.5 GHz.                                                                          | 13   |

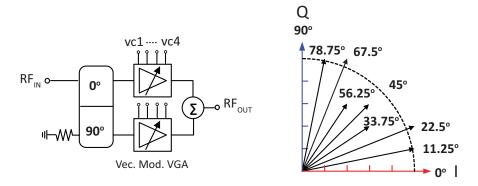

| Figure 2.7:   | Vector modulator VGA with discrete transistors for 3-bit control in the $0-90^{\circ}$                  | 10   |

| 1 iguie 2.7.  | quadrant.                                                                                               | 15   |

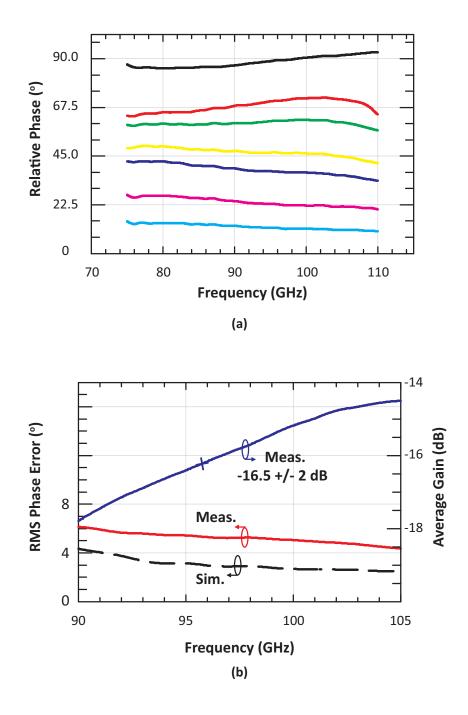

| Figure 2.8:   | Vector modulator measurements: (a) Relative phase, and (b) gain and RMS                                 | 10   |

| 115010 2.0.   | phase error.                                                                                            | 16   |

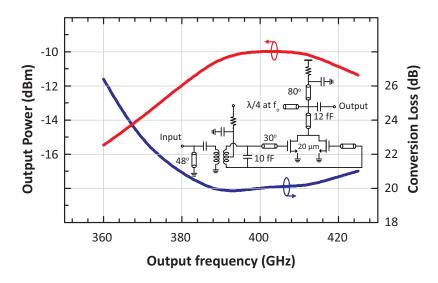

| Figure 2.9:   | Qualdrupler schematic and measured output power and conversion loss [13]                                | 10   |

| 115010 2.7.   | at an input power of +10 dBm ( $f_{in}$ = 90 - 105 GHz)                                                 | 18   |

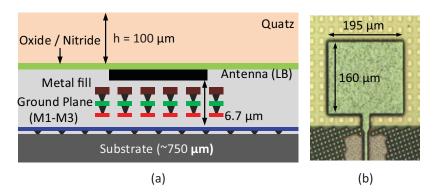

| Figure 2.10:  | High-efficiency microstrip antenna on 45nm SOI with quartz superstrate: (a)                             | 10   |

| 1 iguie 2.10. | cross-section view, (b) microphotograph of antenna showing metal fill.                                  | 18   |

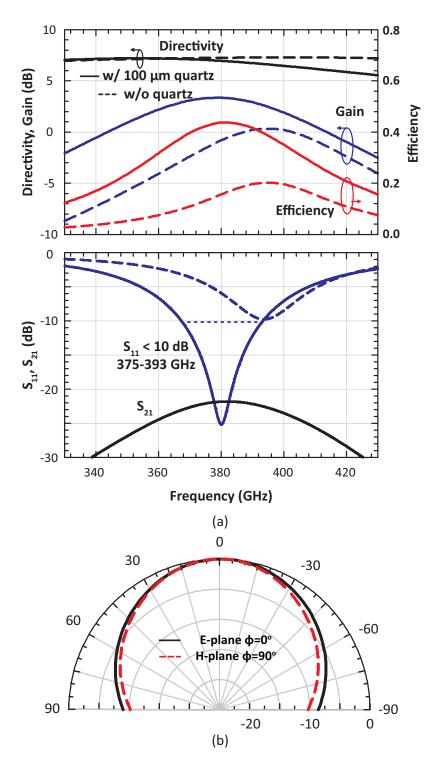

| Figure 2.11:  |                                                                                                         | 10   |

| 115010 2.111  | simulated pattern for single element at 380 GHz.                                                        | 19   |

| Figure 2.12:  | System-level simulations including estimated power levels at each block for                             |      |

|               | a single channel.                                                                                       | . 21 |

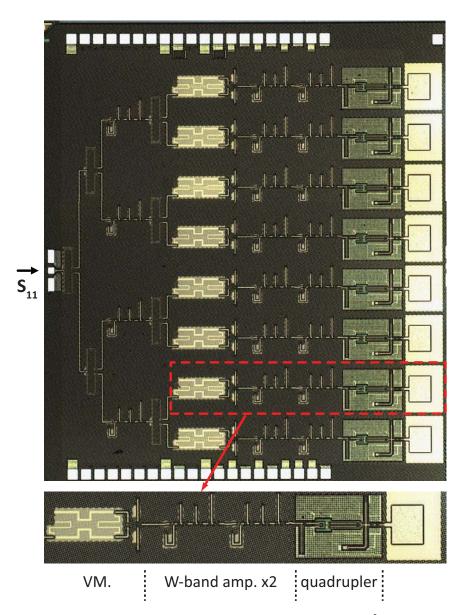

| Figure 2.13:  | Phased-array transmitter microphotograph (3 x $3.5 \text{ mm}^2$ ) with a blow up of a                  |      |

| 8             | single channel.                                                                                         | 23   |

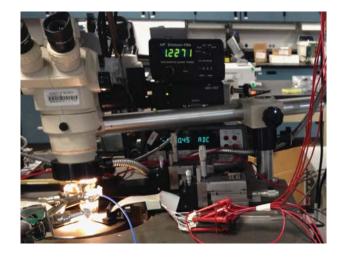

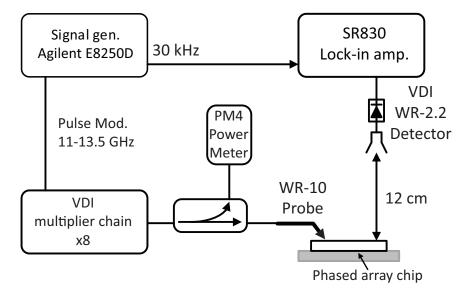

| Figure 2.14:  | -                                                                                                       |      |

| U             | the Cascade Microtech chuck (under the microscope) and a W-band GSG                                     |      |

|               | probe is used for the 90-100 GHz input.                                                                 | 24   |

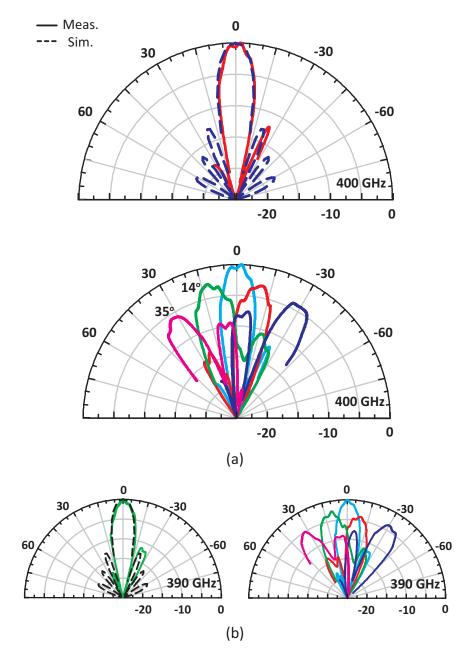

| Figure 2.15:  | Measured and simulated patterns: (a) 390 GHz no scanning and with scan-                                 |      |

| C             | ning, (b) 400 GHz no scanning and with scanning.                                                        | 25   |

| Figure 2.16:  | Measured EIRP: (a) versus frequency, and (b) versus input power at 97.5                                 |      |

| -             | GHz (fout=390 GHz)                                                                                      | 27   |

| E'            |                                                                                                         | 21   |

| Figure 3.1:   | QPSK transceiver block diagram with option for an external LO feed                                      |      |

| Figure 3.2:   | VCO schematic                                                                                           | 32   |

| Figure 3.3:   | Active splitter schematic.                                                                              | 33   |

| Figure 3.4:   | Doubler schematic.                                                                                      | 34   |

| Figure 3.5:   | Balanced mixer schematic schematic.                                                                     | 34   |

| Figure 3.6:   | wideband IF amplifier schematic.                                                                        | 35   |

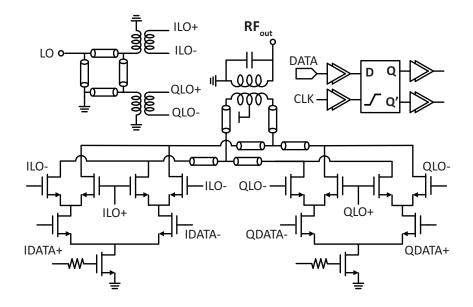

| Figure 3.7:   | I/Q modulator schematic.                                                                                | 36   |

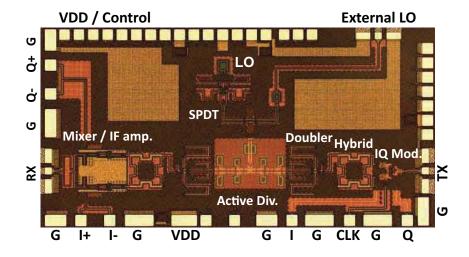

| Figure 3.8:   | Die micrograph.                                                                                         | 36   |

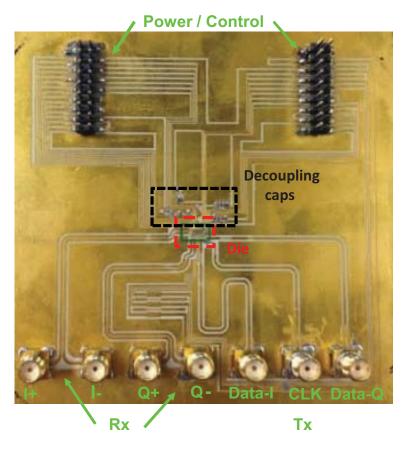

| Figure 3.9:   | PCB board                                                                                               | 37   |

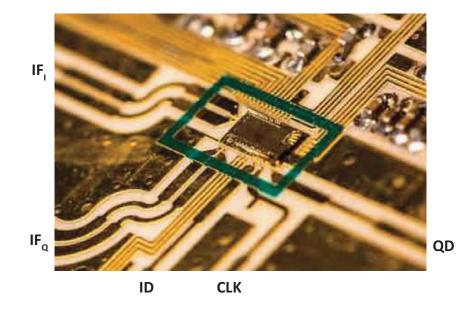

| Figure 3.10: | Die & bonding on PCB board.                                                 | 37   |

|--------------|-----------------------------------------------------------------------------|------|

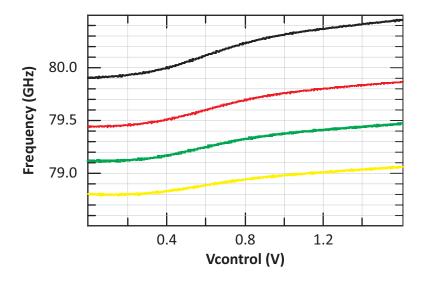

|              | Measured VCO tuning range.                                                  | 39   |

| Figure 3.12: | Measured VCO output power                                                   | 39   |

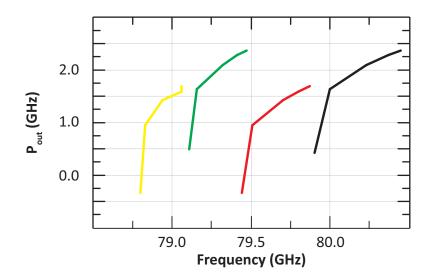

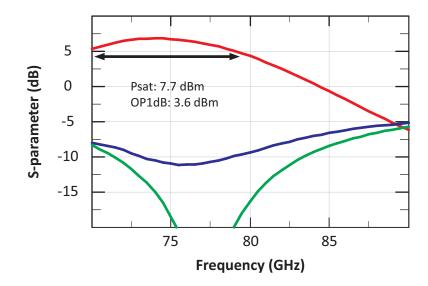

| Figure 3.13: | Measured VCO phase noise.                                                   | 40   |

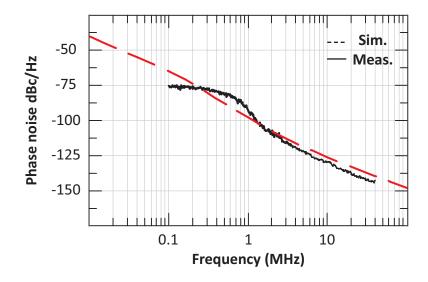

| Figure 3.14: | Active power splitter power measurement results                             | 40   |

| Figure 3.15: | Receiver power gain.                                                        | . 41 |

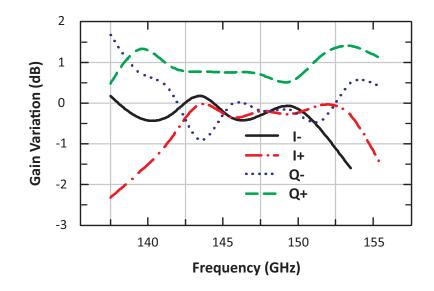

| Figure 3.16: | Receiver gain variation.                                                    | . 41 |

| Figure 3.17: | Receiver eye diagram measurement setup                                      | 42   |

| Figure 3.18: | Receiver spectrum and eye diagram measurement results                       | 42   |

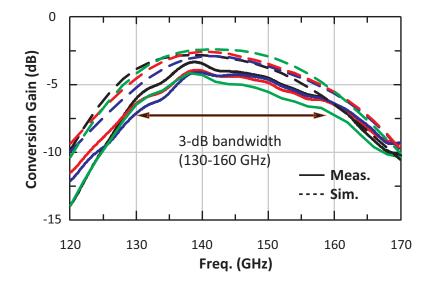

| Figure 3.19: | $S_{21}$ measurement results for (00), (01), (10), and (11) I/Q inputs      | 44   |

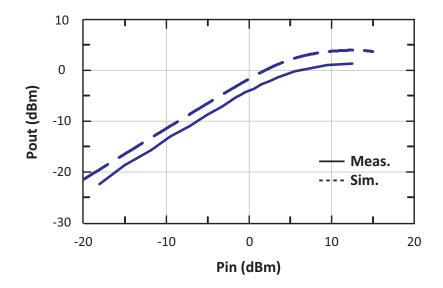

| Figure 3.20: | Modulator $P_{in}$ (LO power) versus $P_{out}$ measurement results          | 44   |

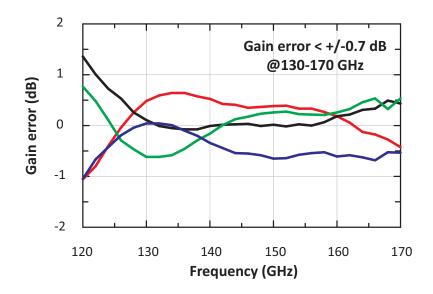

| Figure 3.21: | Modulator gain error for (00), (01), (10), and (11) I/Q inputs              | 45   |

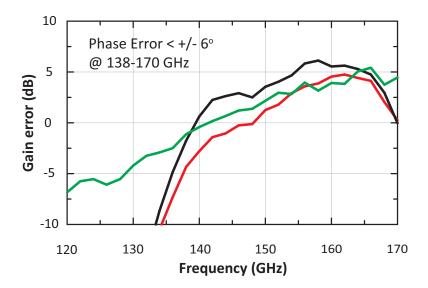

| Figure 3.22: | Modulator phase error for $(00)$ , $(01)$ , $(10)$ , and $(11)$ I/Q inputs  | 45   |

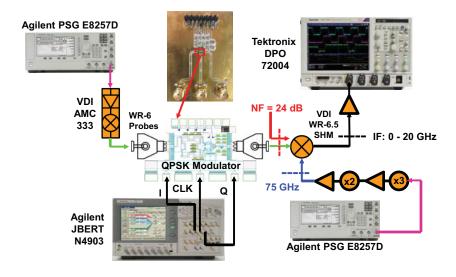

| Figure 3.23: | Modulator performance measurements setup                                    | 46   |

| Figure 3.24: | Measured modulator spectrum, eye diagram, and EVM at 150 GHz carrier        |      |

|              | frequency with 1 Gbit/s BPSK modulation                                     | 46   |

| Figure 3.25: | Measured modulator spectrum, eye diagram, and EVM at 150 GHz carrier        |      |

|              | frequency with 10 Gbit/s QPSK modulation                                    | 47   |

| Figure 3.26: | Measured modulator spectrum, eye diagram, and EVM at 150 GHz carrier        |      |

|              | frequency with 20 Gbit/s QPSK modulation                                    | 47   |

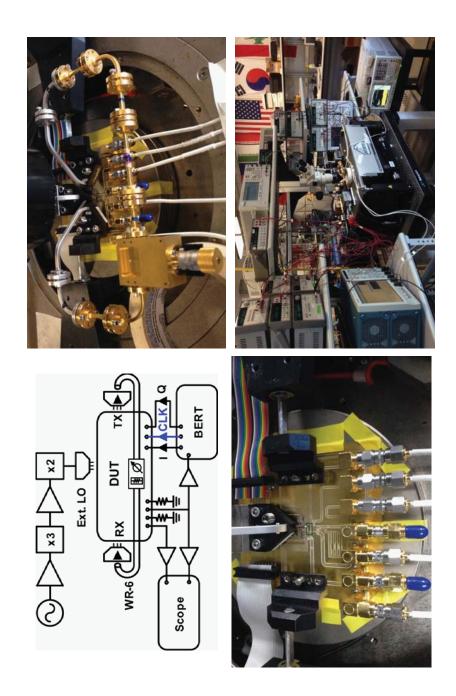

| Figure 3.27: | Loop-back transceiver measurement setup                                     | 49   |

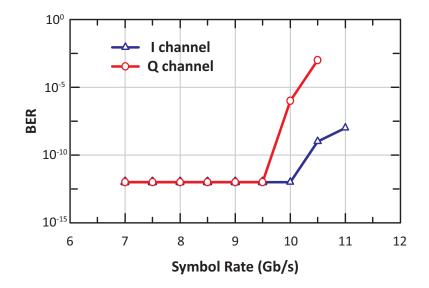

| Figure 3.28: | Measured Transceiver Bit-Error-Rate versus data rate with QPSK modulation   |      |

|              | at -20 dBm received power                                                   | 50   |

| Figure 3.29: |                                                                             |      |

|              | at -20 dBm received power                                                   | 50   |

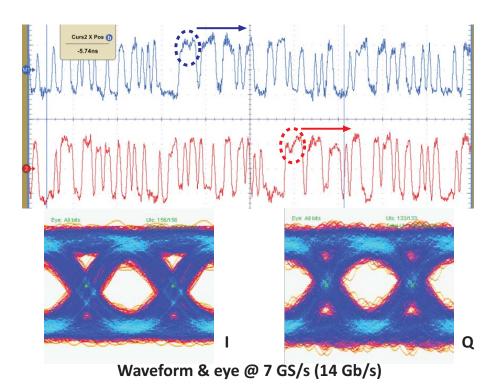

| Figure 3.30: | Measured waveform at 14 Gbit/s QPSK modulation with eye diagram for         |      |

|              | both I/Q channels.                                                          | . 51 |

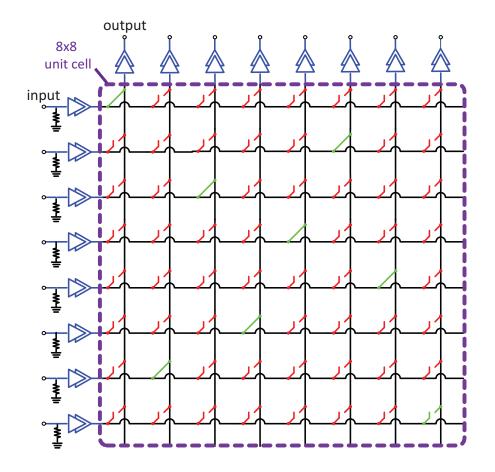

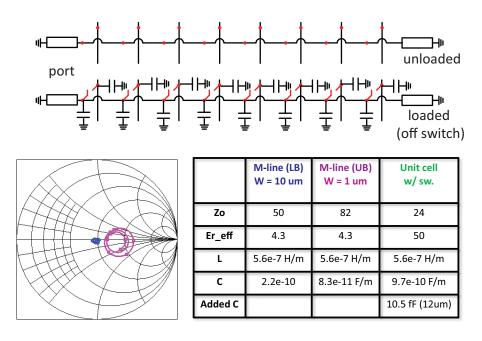

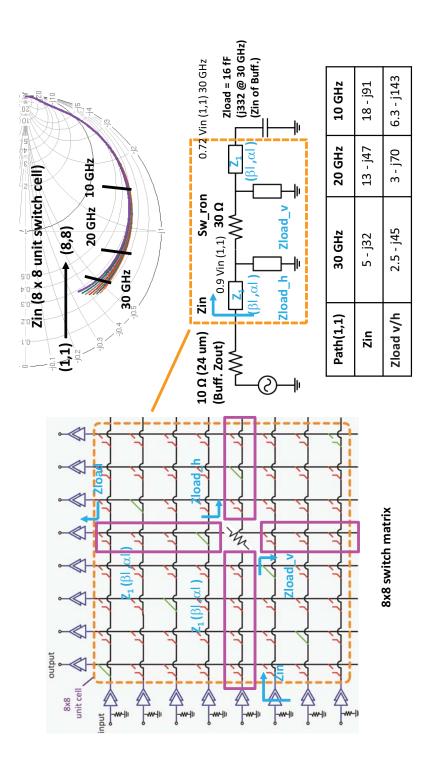

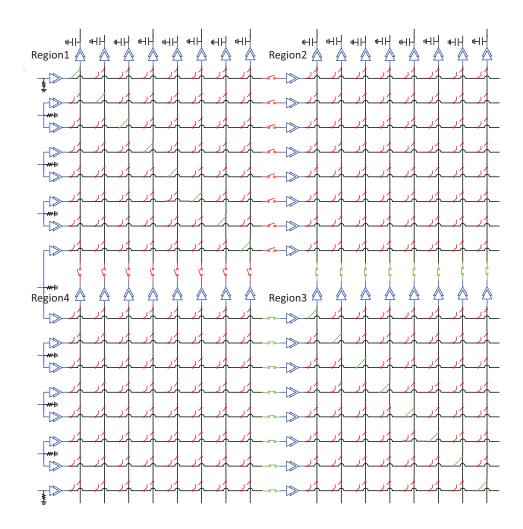

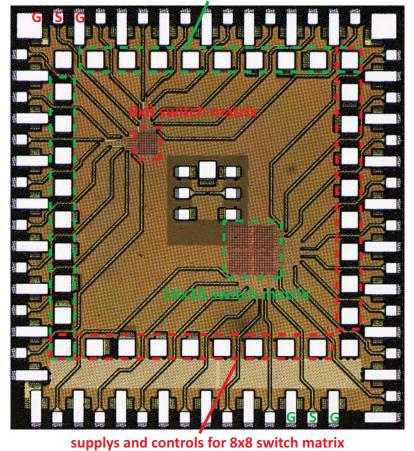

| Figure 4.1:  | Block diagram of 8x8 single ended switch matrix.                            | 56   |

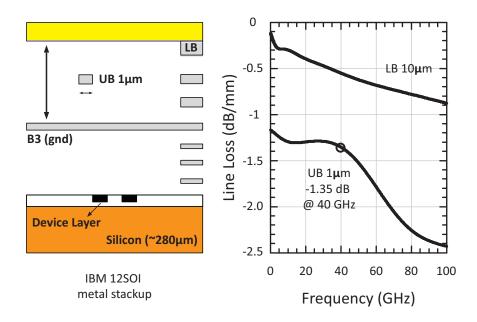

| Figure 4.2:  | IBM 12SOImetal stack-up and simulated T-line loss versus frequency          | 58   |

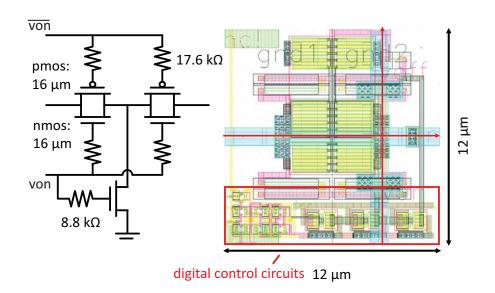

| Figure 4.3:  | Single shunt-series-shunt CMOS switch schematic and illustrated layout.     | 58   |

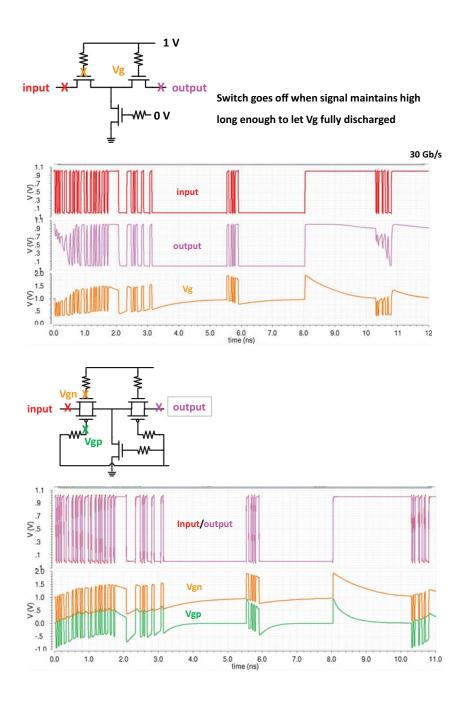

| Figure 4.4:  | Comparison of single transistor switch and transmission gate based one on   |      |

| -            | response of stimulation after long idle time pattern.                       | 59   |

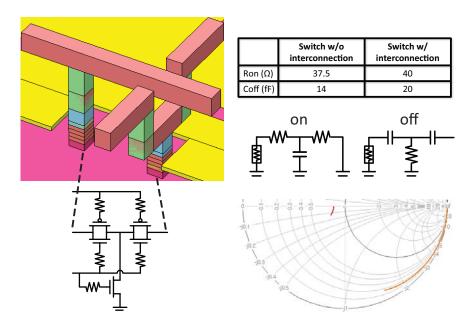

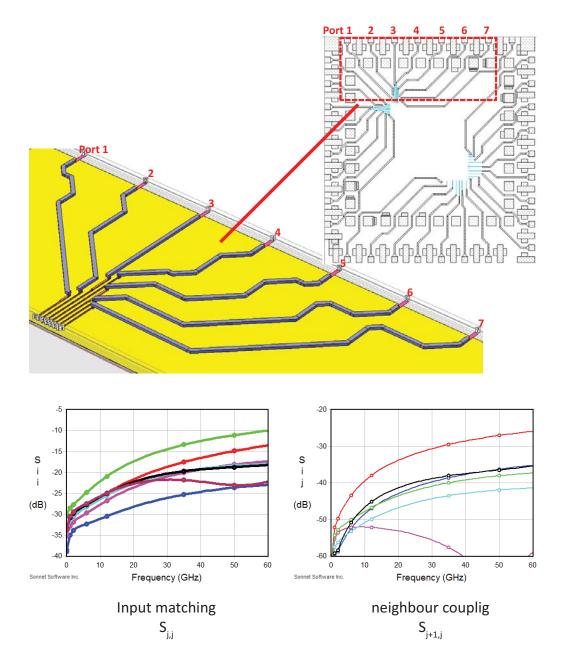

| Figure 4.5:  | Series-shunt-series switch illustrated 3-D interconnection model in Sonnet, |      |

| -            | equivalent lumped circuits model and S-parameter simulation results         | 60   |

| Figure 4.6:  | Stim of single transistor and                                               | 60   |

| Figure 4.7:  | Equivalent circuits model for the 8x8 matrix.                               | 62   |

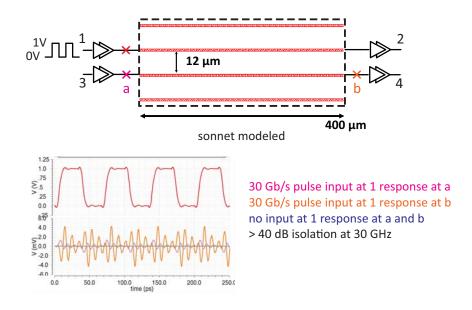

| Figure 4.8:  | Simulation of coupling between adjacent channels.                           | 63   |

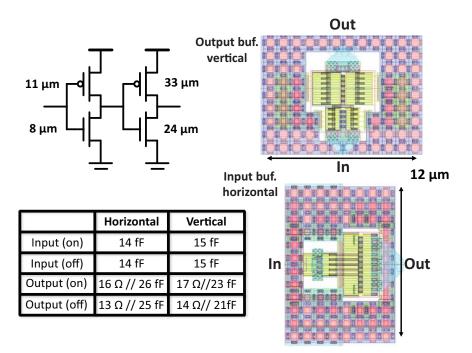

| Figure 4.9:  | Schematic and layouts of input/output buffer.                               | 63   |

| Figure 4.10: | Block diagram of 16x16 single ended switch matrix.                          | 64   |

| Figure 4.11: |                                                                             | 65   |

| Figure 4.12: | Input/output routing from pad to buffer.                                    | 66   |

| Figure 4.13: | Equivalent circuits model for the 8x8 matrix.                               | 68   |

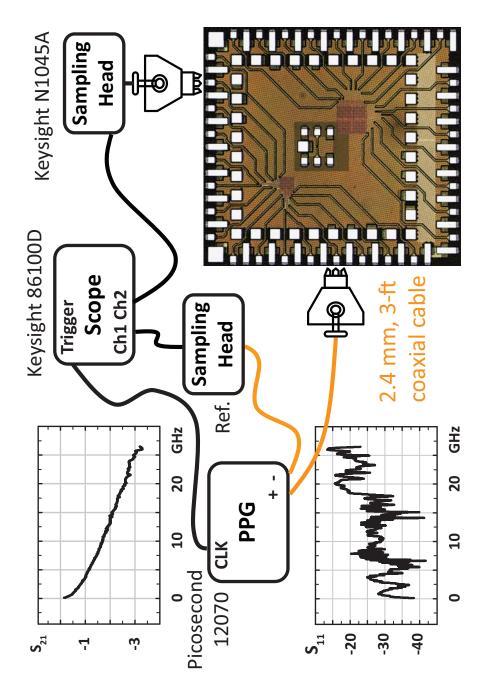

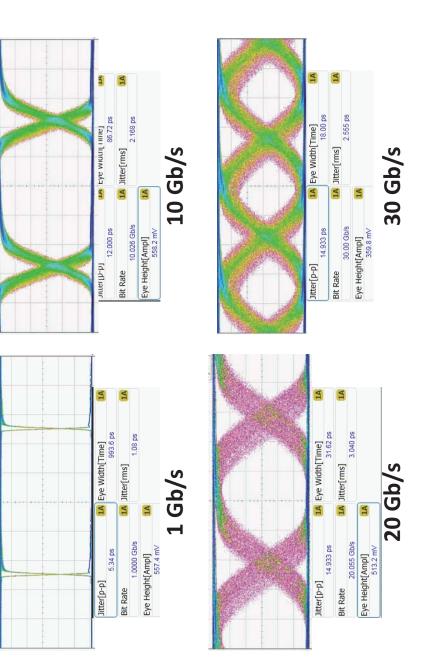

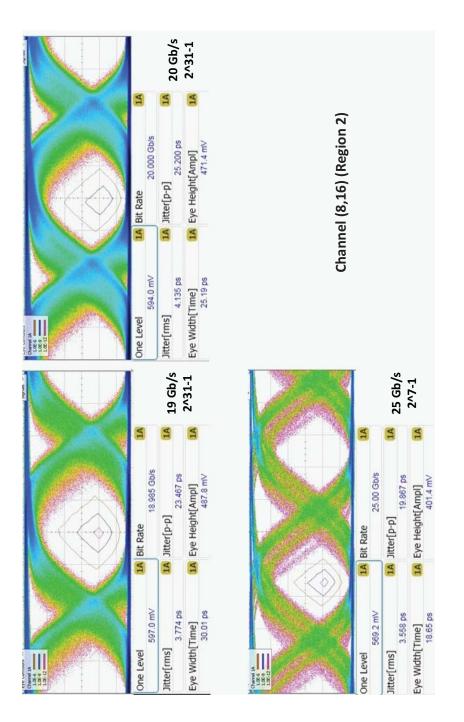

| Figure 4.14: | Eye diagram at 1, 10, 20, 30 Gb/s for channel(8,8)                           | 69 |

|--------------|------------------------------------------------------------------------------|----|

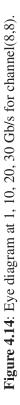

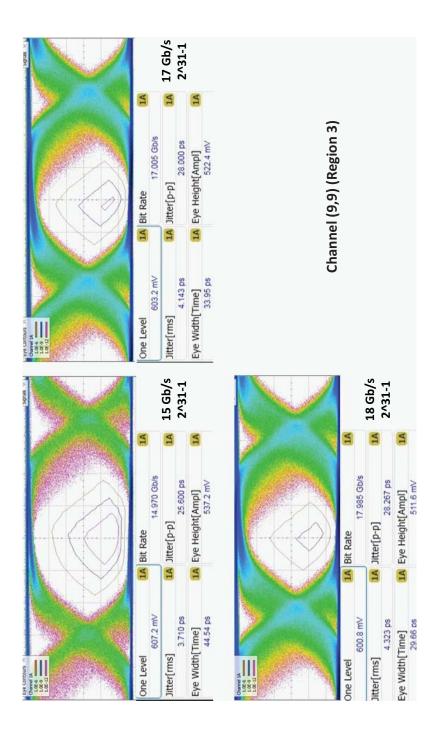

| Figure 4.15: | Eye diagram at 1, 10, 20, 30 Gb/s for diagonal channels                      | 70 |

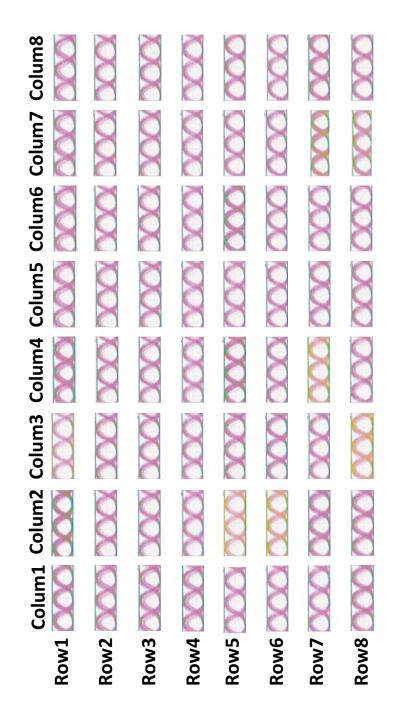

| Figure 4.16: | Eye diagrams at DUT(device under test) output(channel(1,1)) and 3-ft feeding |    |

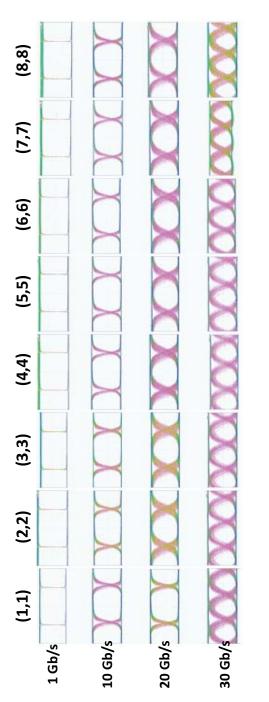

|              | cable output at 30 Gb/s                                                      | 71 |

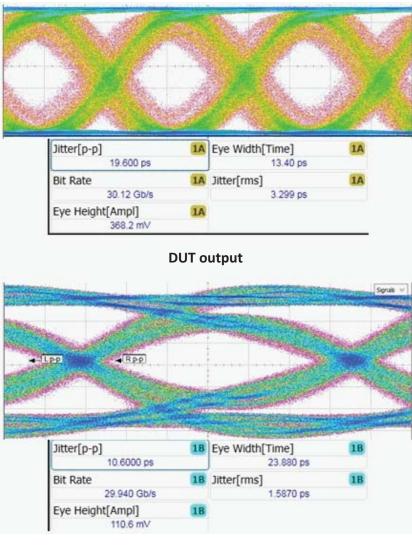

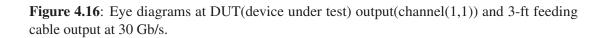

| Figure 4.17: | Eye diagram at 30 Gb/s for all channels                                      | 72 |

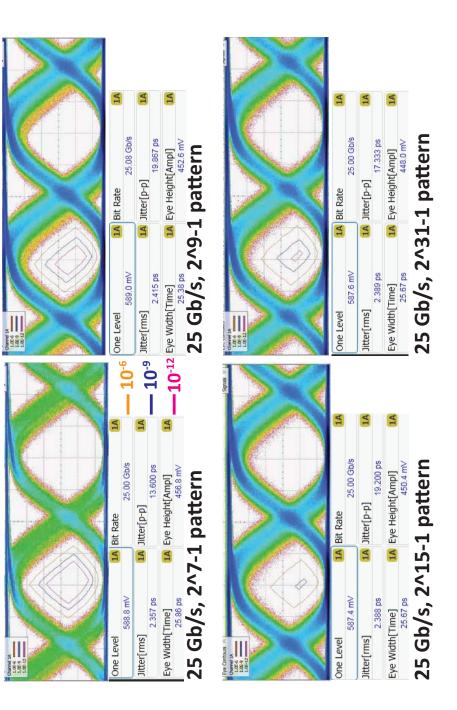

| Figure 4.18: | Eye diagrams and waveform for channel(5,4) at 30 Gb/s                        | 73 |

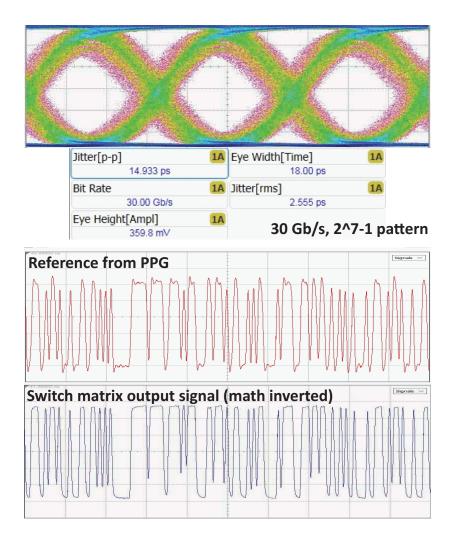

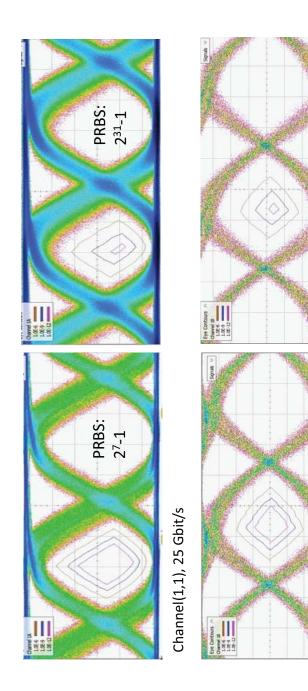

| Figure 4.19: | Channel(1,1) contour at 25 Gb/s for different patterns                       | 74 |

| Figure 4.20: | DUT output contour and reference output contour.                             | 75 |

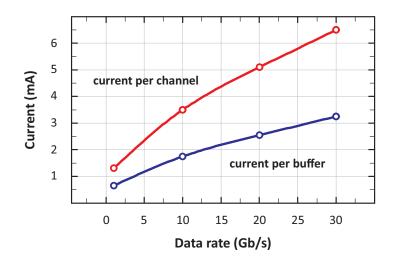

| Figure 4.21: | Measured current versus data rate.                                           | 78 |

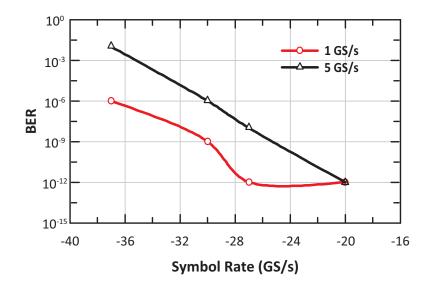

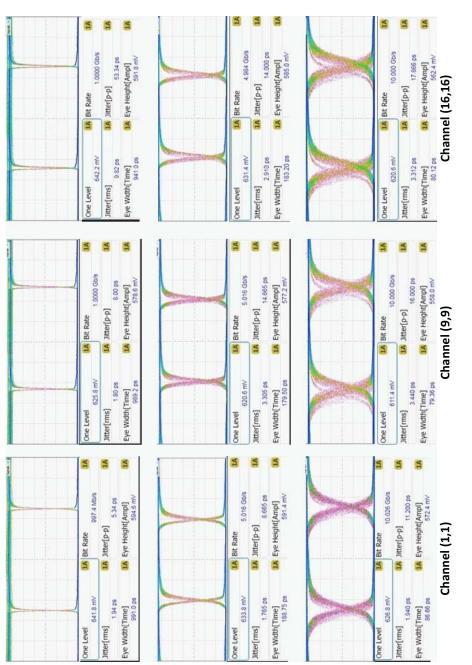

| Figure 4.22: | Channel (1,1)(9,9)(16,16) measured at 1, 5, 10 Gb/s                          | 79 |

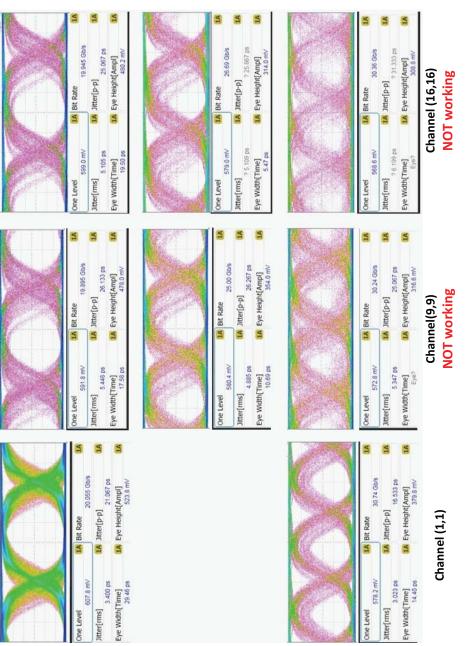

| Figure 4.23: | Channel (1,1)(9,9)(16,16) measured at 20, 25, 30 Gb/s                        | 80 |

| Figure 4.24: | Channel (8,16) measured contour.                                             | 81 |

| Figure 4.25: | Channel (9,9) measured contour                                               | 82 |

## LIST OF TABLES

| Table 2.1: | Summary and Comparison of Phased-Array above 300 GHz | 28 |

|------------|------------------------------------------------------|----|

| Table 3.1: | Performance Summary Table                            | 51 |

| Table 3.2: | Comparison Table with Transceivers above 100 GHz     | 52 |

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without help and support of many people. First I would like to thank my advisor Prof. Gabriel Rebeiz for his guidance and supports through my doctoral studies. In addition to the technical training, we learn everything about the life on his meeting table. The most important things I have learnt from him are how to shoot for the best, paying attention to extreme details while keeping the big picture. It has been a great pleasure and honor to work with him for the years.

Next, I would like to thank my dissertation committee members; Prof. James F. Buckwalter, Prof. Brian G. Keating, Prof. Patrick Mercier and Prof. William S. Hodgkiss for sharing their time, interest, and valuable comments about my research.

I want to give thanks to my co-authors: Dr. Ozan D. Gurbuz, Dr. Samet Zihir, Dr. Hsin-Chang Lin, Dr. Ozgur Inac and Dr. Fatih Golcuk. I used 400 GHz on-quartz antennas designed by Ozan D. Gurbuz in my 400 GHz 8x1 phased array designs, W-band quadrupler designed by Dr. Fatih Golcuk, D-band mixer designed by Dr. Ozgur Inac and D-band doubler designed by Dr. Hsin-Chang Lin. I would additionally thank Dr. Samet Zihir for great discussion on measurements and technical details.

Then thanks go to TICSG group members for their support and friendship: Abdullah Al-azemi, Hasan Al-Rubaye, Youngho Cho, Hyunchul Chung, Kerim Kibaroglu, Umut Kodak, Kevin Ming-Jiang Ho, Chih-Hsiang (Elmer) Ko, Bon-Hyun Ku, Timothy Lee, Chenhui Niu, Bhaskara Rupakula, Donghyup Shin, Woorim Shin, Eric Wagner, Hyun-Ho Yang, Tao Yang, Hosein Zareie, Zuwei Lin. It was a great pleasure for me to work with them all.

Special thanks to my lovely wife, Mengfei Li, my parents, Xun Yang and Nanzi Xie, my 'family member' here in San Diego, Uncle Xiyou Wang, Auntie Yifang Chen, Emilian, Changkun Chen, Jiaze Li, Xuan dai, Jun Li, Hao Wang, Zebin Wang. Without their support, encouragement, understanding, and most important accompany, nothing would ever happen. It is so lucky of me to meet all of you and go through the life together.

The six years journey is a witness for my Father in heaven. All is in his grace and promise. Will continue the race and fight in faith.

Chapter 2 is mainly a reprint of material published in *IEEE Transactions on Microwave Theory and Techniques*, 2016. Y. Yang, O. D. Gurbuz, G. M. Rebeiz. The dissertation author is the primary author of the source material.

Chapter 3 is mainly a reprint of material published in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, 2014. Y. Yang, S. Zihir, H. Lin, O. Inac, W. Shin, G. M. Reeiz. The dissertation author is the primary author of the source material.

Chapter 4 is mostly reprint of the materials as will be submitted to *IEEE Transactions on Microwave Theory and Techniques*, 2018. Y. Yang G. M. Rebeiz. The dissertation author is the primary author of the source material.

Yang Yang La Jolla, California July 2018

#### VITA

| 2010 | B. S. in Micro-Electronics, Shanghai Jiao Tong University, Shanghai, China                                           |

|------|----------------------------------------------------------------------------------------------------------------------|

| 2012 | M. S. in Electronics Engineering (Electronic Circuits and Systems), University of California San Diego, La Jolla, CA |

| 2016 | Ph. D. in Electrical Engineering (Electronic Circuits and Systems), University of California San Diego, La Jolla, CA |

#### PUBLICATIONS

Y. Yang, O. Gurbuz and G. M. Rebeiz, "A eight-element 370-210 GHz phaserd-array transmitter in 45-nm CMOS SOI with peak EIRP of 8-8.5 dBm," in *IEEE Transactions on Microwave Theory and Techniques*, December 2016.

Y. Yang, O. Gurbuz and G. M. Rebeiz, "A 8-element 400 GHz phased-array in 45 nm CMOS SOI," in *Microwave Symposium (IMS), 2015 IEEE MTT-S International*, May 2015.

Y. Yang, S. Zihir, H. Lin, O. Inac, W. Shin, G. M. Rebeiz, "A 155 GHz 20 Gbit/s QPSK transceiver in 45nm CMOS," in *Radio Frequency Integrated Circuits Symposium (RFIC)*, June 2014.

Y. Yang, S. Casina and G. M. Rebeiz, "A sige bicmos W-band LNA with 5,1 dB NF at 90 GHz," *IEEE Compound Semiconductor Integrated Circuit Symposium(CSICS)*, October 2013.

### ABSTRACT OF THE DISSERTATION

### High Performance CMOS SOI Gbps Millimeter-Wave Transceivers, Phased-Arrays and Switching Networks

by

#### Yang Yang

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2018

Professor Gabriel M. Rebeiz, Chair

With the CMOS process technology progress, transistor can achieve up to 260 GHz  $f_t$ and  $f_{max}$  referenced to the top metal, which makes it possible to develop lower cost circuits and blocks for THz high speed implementations such as active imagine system, short distance chip to chip communication systems, and large scale high speed ultra low power switch networks. The dissertation shows an 8x1 phased array transmitter working at 370-410 GHz with peak EIRP of 8.5 dBm, a QPSK modulated 20 Gbit/s transceiver front end (including modulator, voltage control oscillator, power splitter, doubler, mixer and wide-band baseband amplifier.) at 155 GHz and two cross connected high speed ultra low power switch matrices (an 8x8 matrix up to 25 Gbit/s matrix and a 16x16 matrix built using four 8x8 matrix). All circuits and blocks are built using the Global Foundries 45 nm CMOS SOI (silicon on insulator) process.

# Chapter 1

# Introduction

The potential of building large-scale imaging arrays and high data-rate communication links at relatively low cost makes designing transmitters and receivers using silicon SiGe and CMOS technologies in millimeter-wave (mm-wave) and terahertz (THz) an active area of research.

For imaging systems, silicon allows the construction of single chip focal-plane arrays with integrated antennas and detectors, together with all the multiplexing and readout electronics, thus reducing the system cost. Silicon also results in high yield and in uniformity from pixel-to-pixel, which is a prerequisite for fully integrated systems.

For communication systems, silicon offers acceptable performance up to 150-300 GHz for front end blocks such as mixers and modulators. The smaller device parasitics due to the technology progress also makes wideband IF circuits design possible. Those circuits and blocks are essential to be paired with the front end blocks for a whole system. Though SiGe and CMOS designs are still not as competitive as their GaAs counterparts, they are good enough for short distance communication systems and low power portable measurement equipments.

Meanwhile, in order to route the massive amounts of data for those new developed high speed circuits or to ease the increasing data traffic in current communication networks, switches are needed with the highest possible throughput. For the greatest versatility and performance it is critical that the switches also added little jitter to the signal and meet the reconfigurability requirements. Cross-point switches with both passive and active circuits used in combination to improve both fan-out capability and lower power consumption,

Accurate modeling of the interconnections and extraction of the parasitics are essential for high frequency circuits design. Careful system level budget and integration is required for a working system or sub-system.

Chapter 2 presents an 8-element 400 GHz phased-array in 45 nm CMOS SOI. The phasedarray transmitter delivers 8 dBm EIRP with a 3-dB bandwidth of 40 GHz and it is able to be scanned to +/- 35° in one plane. This multiple multipliers coupled with no-chip antenna elements and quasi-optical combining technique provide the solutions that silicon technologies is weak in power generation in the THz domain (>300 GHz). The design is also capable to be scaled up to larger sized phased-array. To our knowledge, this is one the first demonstrations of a phased array operating at 400 GHz using CMOS technology and with wide operating bandwidth.

Chapter 3 presents an 155 GHz 20 Gbit/s QPSK transceiver front-end includes modulator, demodulator, LO chain with an option for external LO feed. It is intended for short distance high speed wireless communication link and is the first demonstration of a single-chip QPSK transceiver in CMOS at frequencies above 100 GHz. To achieve higher speed with lower power consumption is always the goal for wireless technology. There are mainly two ways to increase the data-rate of a system. One is to increase the signal-to noise ratio and hence high order modulations can be implemented. However, the signal to noise ratio requirement drastically increases as the modulation order increases. The more straightforward way is to increase the bandwidth which becomes the motivation for this D-band transceiver design. The transceiver consumes 345 mW with on-chip LO (290 mW without LO) and is 2.8x1.4 mm<sup>2</sup> in size with pads.

Chapter 4 presents a 0.24 pJ/bit, 30 Gbit/s 8x8 single-ended cross connection switch matrix and a 16x16 matrix built using four of the 8x8 cells which can achieve 20 Gbit/s per channel. The motivation for the research is towards ultra low power consumption and scalable

unit cell for large scale matrix. The core circuits of the 8x8 matrix is only  $120x120 \mu m^2$  in size and consumes 7.2 mW per channel. In order to lower the power consumption, passive cross point switch core with input and output buffer structure is investigated. Loaded transmission line routing mode as well as tradeoff among speed, power consumption and size limitation of passive switches array are analyzed. Measurement results for different channels at different rates are showed and the limitation of the measurement setup is discussed.

The thesis concludes with a summary and future work suggestions in Chapter 5.

# Chapter 2

# **Millimeter-Wave Phased-Arrays**

# 2.1 Introduction

The use of silicon SiGe and CMOS technologies in millimeter-wave and terahertz (THz) transmitters and receivers has been an active area of research due to the potential of building large-scale imaging arrays and high data-rate communication links at relatively low cost [1–18]. For imaging systems, silicon allows the construction of single-chip focal-plane arrays with integrated antennas and detectors, together with all the multiplexing and readout electronics, thus reducing the system cost. Silicon also results in high yield and in uniformity from pixel-to-pixel, which is a pre-requisite for fully integrated systems. For communication systems, silicon offers acceptable performance for mixers and modulators up to 150-300 GHz [19–21], and while these are not as competitive as their GaAs counterparts, they are good enough for short distance communication systems.

A weak point of silicon technologies is the difficulty of generating of adequate transmit power and EIRP in the THz domain (> 300 GHz). SiGe and CMOS multipliers and oscillators have been successful at generating an output power of 20-21 dBm at 110-130 GHz and 2-8 dBm up to 250 GHz [22]- [23], but the transmit power quickly falls off above 250 GHz due to the transistor  $f_t$  and  $f_{max}$  (which is typically in the 250-300 GHz range). Therefore, in order to increase the radiated power, multiple oscillators or multipliers, coupled with on-chip antenna elements, have been used. The quasi-optical combining technique eliminates the lossy on-chip transmission-lone combiner, results in 100% combining in free space and increased the EIRP by a factor of N<sup>2</sup> [14], [24], [25]. It is also well suited for on-chip THz systems since the antenna spacing is 0.3-0.5 mm. The array approach also leads to a straightforward phased-array transmitter if the phase at each element is controlled independently, resulting in a wafer-scale phased array [25], [26].

This paper presents the first 360-410 GHz 8-element linear phased array transmitter in 45nm silicon SOI, and is an expanded version of [27]. The design is based on W-band phase shifters and amplifiers coupled with x4 multipliers for frequency up conversion, and with on-chip high-efficiency microstrip antennas. The transmitter is capable of operating over a 30 GHz bandwidth with an EIRP > 5 dBm a peak EIRP of 7-8 dBm at 380-400 GHz, and results in phased array patten scanning to +/- 35° in one plane.

# 2.2 Design and Single Block Measurements

## 2.2.1 System Architecture

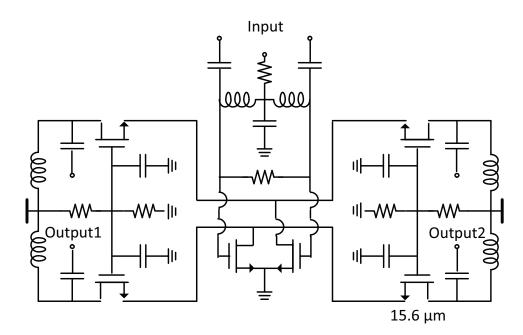

Fig. 2.1 presents the block diagram of the 8-element phased-array transmitter. The 90-105 GHz input signal is divided into 8 different paths using Wilkinson splitters and amplifiers and fed to vector modulators. The phased-shifted output then pass again by high-efficiency W-band amplifiers and is fed into a x4 quadruplers with an output at 360-420 GHz. The distance between the quadrupler and the antenna is kept very short so as to minimize the transmission-line loss.

This architecture results in two design criteria which are important for large-scale phased arrays: a) The entire chip is at W-band frequencies with high-gain amplifiers and relatively low transmission-line loss, making it scalable to 16 or 64 elements, b) the W-band signal needs to be

Figure 2.1: Block diagram of the 400 GHz phased-array transmitter.

controlled in a single quadrant only, that is 0-90°, since the x4 multiplication factor will expand the phase shift into 0-360°. Therefore, the phase shifter can be implemented as a single-ended vector modulator as opposed to the standard differential vector modulators used in mm-wave designs [28]. The entire chip is therefore designed in a single-ended configuration and this results in lower power consumption than differential designs. The use of a single-ended topology is also compatible with high-efficiency on-chip microstrip antennas.

For simplicity and ease of scalability, only four different components are used in the entire system: 1) Wilkinson combiner, 2) W-band amplifier, 3) W-band vector modulator and a 4) quadrupler. The components are all designed to be 50  $\Omega$  matched, and therefore are easily connected together without re-designing their input and output matching networks. This may not be as efficient as complex conjugate matching, but it results in wideband designs and is less sensitive to design error. Also, each component can be independently characterized using break-out circuits.

Note that the x4 architecture in the signal path does not allow for complex modulation signals such as 16QAM, and is more suited for continuous wave (CW), amplitude modulated (AM or OOK) or frequency shift systems (FSK, FMCW, etc.). However, if triplers are used instead of quadruplers, then a QPSK constellation can be supported as demonstrated in [19].

### 2.2.2 Technology

The Global Foundries (GF) 45nm CMOS SOI technology is used due to its high  $f_t$ ,  $f_{max}$  transistors, 11 metal layers with copper metals and tungsten vias, and with thick dielectrics and thick metals for the top layers (Fig. 2.2). The technology results in an  $f_t$  and  $f_{max}$  of 240-260 GHz referenced to the top metal and a maximum available gain (MAG) of 6.1 dB at 94 GHz [29]. In this design, the microstrip transmission line is built usinfg the LB metal for the signal line and B2/B3 metals tied for the ground plane.

Figure 2.2: GF 45 nm SOI process. and simulated loss of a 1 mm long 50  $\Omega$  microstrip line.

**Figure 2.3**: Simulated S-parameters of W-band Wilkinson and hybrid couplers. The wilkinson coupler is 348 x 63  $\mu$ m<sup>2</sup> and hybrid coupler is 368 x 138  $\mu$ m<sup>2</sup>.

A 50  $\Omega$  line is 10  $\mu$ m wide with a simulated loss of 0.9 dB/mm at 100 GHz (Q = 21) and 2.3 dB/mm at 400 GHz (Q = 7.5). Previous results found that the measured transmission line losses are 30-40% higher than simulations up to 110 GHz [29], [30]. However, measurements in [30] also show that the transmission line loss is 4.7 dB/mm at 400 GHz which is double the simulated values (investigations are currently under way to determine the mechanism for this additional loss, and it could be due to the thin high-resistivity adhesion layers used in advanced CMOS processes at every metal layer). This is the reason why the connection between the quadrupler and antenna is made as short as possible (< 30  $\mu$ m), and the high 400 GHz transmission-line loss has virtually no effect on the phased-array performance.

### 2.2.3 Wilkinson and Hybrid Couplers

Fig. 2.3 presents the Wilkinson power divider and the 90° hybrid coupler built using 35  $\Omega$ , 50  $\Omega$  and 70.7  $\Omega$  transmission lines, and simulated using Sonnet EM Suite (version 13.54). The hybrid coupler is required in the vector modulator for the 0-90° signal generation. The Wilkinson divider has excellent impedance match and isolation over a wide bandwidth and results in an insertion loss of 0.8 dB at 95 GHz (assuming 0.9 dB/mm loss at W-band). The hybrid coupler is also well matched with an insertion loss of 1.0 dB at 95 GHz and an amplitude and phase error of < +/-0.5 dB and 2°, respectively at 90-100 GHz. There is < 0.2 dB difference in the device insertion loss if a transmission line loss of 1.3 dB/mm is used due to the  $\lambda/4$  line lengths at 100 GHz is 375  $\mu$ m.

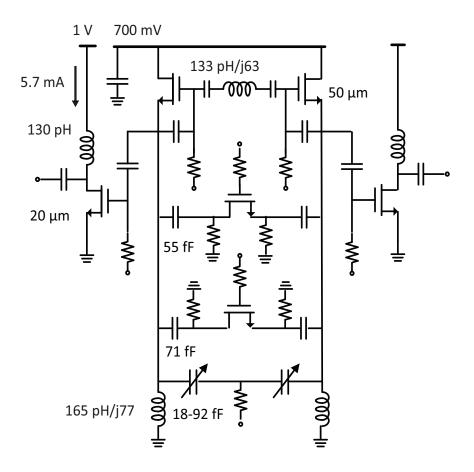

### 2.2.4 W-band Amplifier with High PAE

Fig. 2.4(a) presents the three-stage W-band amplifier used in the Wilkinson divider network and as a driver to the x4 quadrupler. The design is based on common source amplifiers with complex conjugate matching between the different stages. A single-contact finger length of 1

**Figure 2.4**: W-band amplifier: (a) schematic and (b) simulated gain output power and PAE at 95 GHz.

$\mu$ m is used in all designs which results in an f<sub>t</sub>/f<sub>max</sub> of 240/250 GHz for the 30  $\mu$ m transistor [29]. The stub loads are built using 50  $\Omega$  lines with a Q of ~12 (degraded from 21 due to the via interconnection to ground) at 95 GHz, and the interstage matching capacitors are multi-finger metal-oxide-metal designs with a Q of 20 and 10 for a capacitance of 70 fF and 130 fF, respectively, at 95 GHz (Fig. 2.5). The GF 45nm SOI technology does not offer MIM high-Q capacitors and the matching capacitors introduce 1-1.5 dB of additional loss. The output stage is 50  $\mu$ m wide for a saturated output power of 10 dBm and is biased at 19.6 mA. The simulated small-signal gain is 12 dB at 95 GHz with a 3-dB bandwidth of 85-107 GHz. The interstage conjugate match is staggered in frequency so as to result in a wideband design but at the expense of a slightly lower gain.

Note that 10  $\Omega$  resistors are present on the drain network and are mainly for stability since all the amplifiers employ the same V<sub>DD</sub> and ground planes. Also, two W-band amplifiers are used after the vector modulator with a small-signal gain of 23 dB.

Fig. 2.6 presents a stand-alone W-band amplifier and its measured S-parameters. Calibration is done using SOLT (short-open-load-through) to the probe tips and the gain includes the GSG (ground-signal-ground) to CPW (coplanar waveguide) transition loss of 0.5 dB. The measured peak gain is 15 dB at 87 GHz with a 3-dB bandwidth of 85-95 GHz. This was obtained on several samples and indicates that the staggered wideband matching was not well optimized (most probably due to the interdigital capacitor models), and thus the higher gain and narrower bandwidth. The measured P<sub>sat</sub> is ~10 dBm at 95 GHz and the associated PAE (power added efficiency) is ~12%. This was done at P<sub>in</sub> = 0 dBm using the vector network analyzer extender as a W-band source and is shown in Fig. 2.4(b). This PAE is competitive among medium power amplifier in CMOS at 10 dBm output power [31–33].

Figure 2.5: Simulated Q-factor of 45nm SOI capacitors (vncap) versus frequency.

**Figure 2.6**: (a) W-band amplifier microphotograph, and (b) measured S-parameters. The 3-dB bandwidth is 85-94.5 GHz.

### 2.2.5 Vector Modulator

The W-band vector modulator is implemented by summing the in phase (I) and quadrature (Q) signals from the hybrid coupler (Fig. 2.7). The lower transistors M1, M2, M3, M4 in the cascode vector modulator generate the required currents in four different magnitudes, and the upper transistors steer the current between the supply and the output node [34]. Compared to a VGA (variable gain amplifier) with tail current control, this topology handles a higher input power and results in a constant input  $P_{1dB}$  of +3 dBm. The 3-bit phase shifter requires current levels of 0 (all off), 1, 2, 3 and 5 mA and these are synthesized using M1-M4 with different sizes. Note that this simple vector modulator topology results in ~3 dB amplitude variation which can be compensated using a VGA stage. However, in this work, the driver amplifiers after the phase shifter operate in saturation mode and are not affected by this amplitude variation. The input and output of the vector modulator are matched to 50  $\Omega$  using a shunt stub and a series capacitor (LC network). The simulated S<sub>11</sub> is independent of the phase state and is < -10 dB at 75-110 GHz. The simulated gain is -6 +/- 3 dB for a power consumption of 31 mW and an output power of -3 +/- 3 dBm.

Fig. 2.8(b) presents the measured results of a stand-alone W-band vector modulator breakout. The conversion gain is  $-16 \pm 2 dB$  at 95 GHz which is 10 dB lower than simulated, and is due to a poorly defined ac ground at the upper transistor gates caused by a layout error. The measured 3-bit phase response is shown in Fig. 2.8. The phase shifter operates well with an RMS (root mean square) error of 5.4° with 0° being reference phase. The RMS phase error is calculated as:

$$\Phi_{rms} = \sqrt{\frac{\sum_{i=1}^{n} \left(\Phi_{measi} - \Phi_{ideali}\right)^2}{n}}$$

(2.1)

| θ      | <b>0</b> ° | 11.3° | 22.5° | 33.8° | 45.0° | 56.3° | 67.5° | 78.8° | 90° |

|--------|------------|-------|-------|-------|-------|-------|-------|-------|-----|

| tan⊖   | 0          | ~0.20 | ~0.41 | ~0.67 | 1     | ~1.5  | ~2.4  | ~5.0  | 8   |

| I (mA) | 5          | 5     | 5     | 3     | 3     | 2     | 2     | 1     | 0   |

| Q (mA) | 0          | 1     | 2     | 2     | 3     | 3     | 5     | 5     | 5   |

**Figure 2.7**: Vector modulator VGA with discrete transistors for 3-bit control in the  $0-90^{\circ}$  quadrant.

**Figure 2.8**: Vector modulator measurements: (a) Relative phase, and (b) gain and RMS phase error.

### 2.2.6 Quadrupler

The quadrupler is based on a balanced multiplier biased in a class C mode with a second harmonic choke, and results in a conversion gain of -20 dB at 390-410 GHz for an input power of 10 dBm (Fig. 2.9). Details of the design can be found in [14]. The quadrupler consumes 15.4 mW from a 1.4 V supply. The measured quadrupler output power is -10 dBm at 400 GHz when driven by a W-band amplifier with a  $P_{sat}$  of 10 dBm. Note that at 360 GHz, the conversion loss is 26 dB resulting in an output power of -16 dBm.

### 2.2.7 High-Efficiency On-Chip Antenna Array

For high transmit power and EIRP, it is essential that a on-chip high-efficiency antennas be used. A microstrip antenna directly integrated on the 45nm back-end with a 6.8  $\mu$ m of SiO<sub>2</sub> dielectric results in a simulated peak radiation efficiency of 20% and an antenna gain of -2 dB to 0 dB at 360-400 GHz (Ansoft HFSS v14 is used for simulations). In order to improve the radiation efficiency, a  $\lambda$ /4-thick quartz superstrate is used on top of the microstrip antenna (Fig. 2.10). Note that there is no metal defined on the quartz superstrate, and the superstrate is just placed on the top metal layer. This technique has been proposed in the 1980's and enhances the radiation of planar antennas, especially when the antennas are placed on thin or on high dielectric-constant substrates [35]. The quartz superstrate has also been used with on-chip slot-ring antennas at 95 GHz, 170 GHz, 300 GHz and 400 GHz [2], [14], [35].

The simulated microstrip antenna with a 100  $\mu$ m-thick quartz superstrate shows a peak efficiency of 45% and a gain of 2.8-3.5 dB at 360-400 GHz (Fig. 2.11). The antenna is centered at 380 GHz with a simulated directivity of ~ 7.3 dB and a -10 dB impedance bandwidth of 26 GHz. Note that the gain drops rapidly above 410 GHz due to the trigerring of higher order modes in the dielectric superstrate (TE10) [35]. The quartz superstrate increases the antenna peak gain by 3.1 dB (from 0.4 to 3.5 dB) and the peak efficiency by 3.5 dB (from 22% to 45%) as compared to the

**Figure 2.9**: Qualdrupler schematic and measured output power and conversion loss [13] at an input power of +10 dBm ( $f_{in} = 90 - 105$  GHz).

**Figure 2.10**: High-efficiency microstrip antenna on 45nm SOI with quartz superstrate: (a) cross-section view, (b) microphotograph of antenna showing metal fill.

**Figure 2.11**: (a) Simulated microstrip antenna with and without quartz superstrate, and (b) simulated pattern for single element at 380 GHz.

design without a quartz superstrate. Note that both antennas satisfy the stringent metal-density rules in 45nm SOI and a 30% fill factor of isolated islands on all metal layers underneath the antenna. These isolated islands are not connected to the ground plane or to the silicon substrate and are floating. Still, they do reduce the antenna efficiency from 65% to 45%.

The 8-element linear microstrip array are placed at an element spacing of  $0.5\lambda$  at 400 GHz (380  $\mu$ m spacing) for an H-plane pattern scan, and this results in a simulated mutual coupling of < -20 dB. The active antenna impedance is very similar to the single microstrip and is stable versus scan angle due to the H-plane scan. The simulated 3-dB beam-width of the 8-element array is 12° with a gain of 11-12 dB at 380-390 GHz (see Fig. 2.15 for comparison between measured and simulated beamwidth).

### 2.2.8 System-Level Simulations

The entire transmitter can be simulated using a block-diagram approach since all components are 50  $\Omega$  matched (Fig. 2.12). An input power of 6 dBm at W-band results in a power of +3 dBm and -3 dBm at the phase shifter input and output ports, repectively. This is then amplified by 23 dB to result in a P<sub>sat</sub> of 10 dBm before the quadrupler, which in turn generates a power of -10 dBm at the antenna port. Note that two amplifiers with a linear gain of 23 dB are used after the phase shifter to ensure full output saturation after the vector modulator. This was the correct design approach since a saturated power of 10 dBm is still achievable at 95-100 GHz at the multiplier input even with the additional 8-10 dB loss present in the vector modulator.

The output power from each quadrupler is -10 dBm, which results in a total power of -1 dBm from the 8 elements at the antenna input ports. This, together with an antenna array gain of 11-12 dB, results in an EIRP of 10-11 dBm at 380-390 GHz. The simulated radiated power is -4.5 dBm when an antenna efficiency of 45% is taken into account.

Figure 2.12: System-level simulations including estimated power levels at each block for a single channel.

## 2.3 Measurements

The 8-element phased array is fabricated on a 45 nm CMOS SOI chip with a size of 3 x 3.5 mm<sup>2</sup> (Fig. 2.13), and is biased at 1.4 V with a current of 1.1 A (1.5 W). The power consumption is divided into: a) W-band amplifiers: 1160 mW, b) W-band vector modulators: 246 mW and c) quadruplers: 123 mW. The CMOS chip is mounted on a Cascade Microtech measurement station and a 100  $\mu$ m quartz superstrate is glued on top. A W-band GSG probe is used at the RF port and the input power is calibrated to the probe tip. The measured S<sub>11</sub> is < -10 dB at 90-110 GHz.

The radiated power is measured in the far-field using a WR-2.2 horn and a VDI Schottky diode detector (Fig. 2.14). The far field for the 8-element array is 4 cm at 400 GHz, and a range of 12 cm is used. Amplitude modulation at 30 kHz is applied to the W-band source, and the received voltage from the diode detector is sent to a lock-in amplifier. The measured output voltage is in the mV range, resulting in a dynamic range > 25 dB.

The measured 8-element pattern in the H-plane at 390-400 GHz is shown in Fig. 2.15 when all the phase shifters are set to  $0^{\circ}$ . The pattern is the same at 390-400 GHz with a 3-dB beamwidth of  $12^{\circ}$  and agrees well with simulations. The cross-polarization component could not be measured and is < -25 dB relative to the main signal.

The phased-array transmitter scans to  $+/-35-40^{\circ}$  at 380-400 GHz in the H-plane as shown in Fig. 2.15. The measured relative peak power drop by 5 dB at 40° scan angle can be attributed to 3 dB due to the element factor and 1 dB due to the phased array discretization of 3-bit. At 35-40° scan angle, the sidelobe patterns are high, and this is not captured by simulations.

The measured EIRP  $(P_tG_t)$  is obtained using the Friis transmission formula:

$$P_r = P_t G_t G_r (\frac{\lambda}{4\pi R})^2 \tag{2.2}$$

**Figure 2.13**: Phased-array transmitter microphotograph  $(3 \times 3.5 \text{ mm}^2)$  with a blow up of a single channel.

**Figure 2.14**: Measurement setup and associated block diagram. The phased array is on the Cascade Microtech chuck (under the microscope) and a W-band GSG probe is used for the 90-100 GHz input.

**Figure 2.15**: Measured and simulated patterns: (a) 390 GHz no scanning and with scanning, (b) 400 GHz no scanning and with scanning.

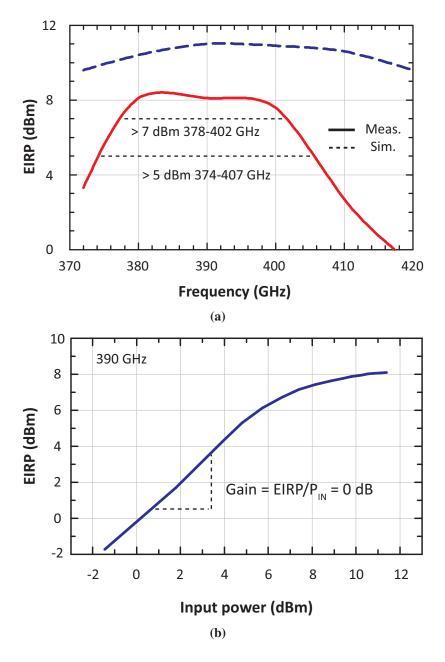

The receive antenna gain is calibrated using the two (identical) antenna method and is 22 +/- 0.5 dB at 390 GHz. The VDI diode detector is calibrated at the factory and also at UCSD, and its responsivity is ~1250 V/W. The difference in responsivity between the VDI and the UCSD calibration is < +/- 0.5 dB at 390 GHz as shown in [14]. The measured EIRP is then inferred from the received power and is plotted in Fig. 2.16(a). A peak EIRP of 8-8.5 dBm is obtained at 380-400 GHz, with a 3-dB bandwidth of 375-407 GHz. This is the highest EIRP obtained to-date at 400 GHz from a silicon-based phased-array, and without the use of a silicon lens. The total radiated power is 200  $\mu$ W (-7 dBm) at 380-400 GHz. There is a 3-dB difference between the simulated EIRP of 11 dBm and the measured value at 8 dBm. The bandwidth is also narrower than simulations. The difference is possibly due to antenna efficiency reduction if the quartz substrate is not well mounted on the wafer (air gaps) and additional impedance mismatch between the quadrupler and the antenna.

The measured EIRP at 400 GHz versus input power at 100 GHz is shown in Fig. 2.16(b). The small-signal transfer function, defined as EIRP/P<sub>in</sub> is 0 dB. The output power saturates at 8-10 dBm W-band input power (which is achievable using CMOS amplifiers). Table 2.1 summarises the array performance and presents a comparison with the state-of-the-art above 300 GHz using CMOS and SiGe technologies.

Note that the oscillator arrays summarized in [11,12,14] are narrowband, especially [12] with only 2 GHz of bandwidth. Also, silicon lenses are used in [11] and [12] which results in wider bandwidth and higher gain antennas. The work in this paper shows the widest 3-dB bandwidth (374-400 GHz) and also operation from 370-420 GHz with an EIRP > 0 dBm. Without doubt, THz sources based on multipliers result in much wider band operation than these based on harmonic or push-push oscillators.

**Figure 2.16**: Measured EIRP: (a) versus frequency, and (b) versus input power at 97.5 GHz (fout=390 GHz).

| Frequency      | Toohaoloon                       | Doctor                 | Antenna/               | Beam                  | Prad    | EIRP  | Pdc      | م<br>م     |

|----------------|----------------------------------|------------------------|------------------------|-----------------------|---------|-------|----------|------------|

| (GHz)          | recunology                       | Design                 | <b>Transition Type</b> | Steering <sup>1</sup> | (Mn)    | (dBm) | (mW)     | Kel.       |

| 374 4072       | 45 nm SOI CMOS                   | 8 x 1 active           | Micro-strip with       | 750                   | 000     | ×     | 1500     | This work  |

| 10+-+10        |                                  | quadrupler array       | quartz superstrate     | C 1                   | 7007    | 0     | nnci     | TIUN SIIIT |

| 330            | 130 nm CiCo                      | 4 x 1 acrive           | SIW cavity             | OVC                   | - 1000  | 10.6  | . 1000   | [11]       |

| 070            |                                  | quadrupler array       | backed patch           | +7                    |         | 0.01  |          | [11]       |

| 201 921        | 20MU 11119 29                    | 4 x 4 oscillator       | Diff. ring on          | 000                   | 100     | 7 0   | 017      | [15]       |

| C07-017        |                                  | injection-locked       | a thinned substrate    | 00                    | 170     | 7.4   | /10      | [61]       |

| 337 3302       | 65 nm hull CMOC                  | 4 x 4 oscillator       | Microetrin             | 050                   | 012     | 17    | 1540     | [13]       |

| 400-100        |                                  | 4th harmonic coupled   | INTICIOSUIP            | CK                    | C10     | 1/    | 1040     | [61]       |

| 300 440        | 15 m COLOMOC                     | 2 x 4 active           | Slot ring with         | Fixed                 | 100     | 6     | UUL      | [1]        |

| 044-060        |                                  | quadrupler array       | quartz superstrate     | pattern               | 100     | n     | 00/      | [14]       |

| 570 5262       | 120 mm CiCo                      | 4 x 4 oscillator array | Wire-ring with         | Fixed                 | 16 ע הי | 30    | 16 v 156 | [[1]]      |

| 000-070        |                                  | triple-push            | silicon lens           | pattern <sup>3</sup>  | 10 V 07 | C7    |          | [71]       |

| befined as ent | Defined as entire steering cone. |                        |                        |                       |         |       |          |            |

| ay above 300 GHz                                        |

|---------------------------------------------------------|

| 1: Summary and Comparison of Phased-Array above 300 GHz |

| able 2.1: Summary and C                                 |

| Table                                                   |

<sup>1</sup> Def

<sup>2</sup> 3-dB power bandwidth. <sup>3</sup> 16 incoherent patterns from 16 different transmitters.

# 2.4 Conclusion

This paper presented a 400 GHz phased-array transmitter with scalability being the prime design factor. This is achieved using W-band circuits for every component except the 100 to 400 GHz quadrupler placed before the antenna. This circumvents the high transmission-line loss at 400 GHz, and most of the phased-array is built at W-band which allows for scalability to large arrays. Also, 50  $\Omega$  blocks are used for all components, allowing straightforward connection of the transmitter array. The proposed topology also allows the W-band source to be phased-locked to a low frequency reference using standard frequency dividers, results in a wideband 400 GHz phased array, and can be used with any type of multipliers such as triplers, quadruplers and quintuplers.

## 2.5 Acknowledgment

The authors would like to thank Ozan Dogan Gurbuz and Michael Chang for technical discussions.

Chapter 2 is mostly a reprint of the materials from

• Y. Yang and O. D. Gurbuz and G. M. Rebeiz, "An eight-element 370-410GHz phasedarray transmitter in 45-nm CMOS SOI with peak EIRP of 8-8.5 dBm," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 12, pp. 4241-4249, Dec. 2016.

The dissertation author is the primary author of this material.

# Chapter 3

# **Gbps Millimeter-Wave Transceivers**

### 3.1 Introduction

THz systems at > 100 GHz have been successfully demonstrated for active imaging systems, general-purpose transmitters, and Gbit/s communication systems using CMOS and SiGe. Application areas such as chip-to-chip or 1-100 m communications require high-order modulation such as QPSK for better spectral density [36–39], and while this was achieved using GaAs-based systems [40,41], there has not been a QPSK transceiver demonstration using CMOS. This paper presents a 155 GHz transceiver with an I/Q modulator and demodulator capable of achieving > 20 Gbit/s QPSK data-rates.

## 3.2 Design

#### 3.2.1 Transceiver Topology

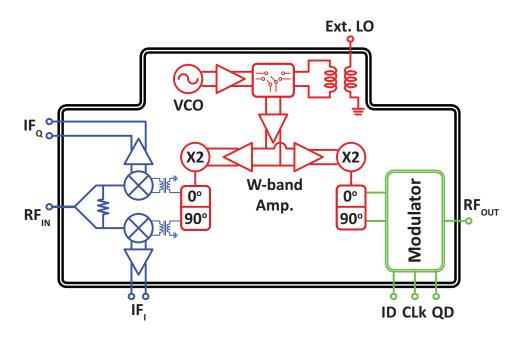

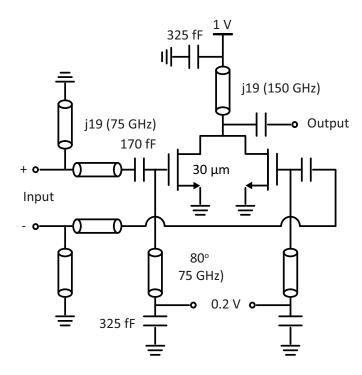

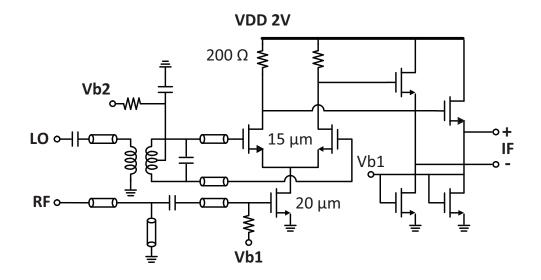

Fig. 3.1 presents the transceiver chip block diagram. A 74-77 GHz local oscillator is employed with an SPDT switch (2.2 dB loss) which allows an external LO feed. The LO signal passes by an active splitter and two balanced doublers with single-ended outputs. Two 150 GHz

0/90° quadrature hybrids are placed in the Tx and Rx paths (3 dB division loss + 0.8 dB ohmic loss) and 150 GHz passive baluns (1.5 dB loss) are used to drive the differential I/Q modulator and mixers. The system does not employ amplifiers at 150 GHz due to their power consumption and since the doublers can each generate 3 dBm which is enough to drive the 150 GHz circuitry. The I/Q mixers are directly attached to the input RF port using a Wilkinson splitter (3 dB division loss + 0.7 dB ohmic loss). The process is Global Foundries 45nm SOI CMOS, with ft/fmax of 250/240 GHz referenced to the top metal layer [42].

Figure 3.1: QPSK transceiver block diagram with option for an external LO feed.

#### 3.2.2 Oscillator, Active Splitter and Doubler

The Clapp oscillator (Fig. 3.2) is believed to have lower phase noise compared to other architectures, at the expense of limited tuning range. Two capacitors combined with a varactor are used to achieve a frequency tuning range of  $\sim$ 2 GHz. In order to save power consumption, the oscillator is working under 0.7 V supply domain. Common source amplifier based buffers which draw current from 1.0 V supply are used to deliver required power to saturate the followed by active power splitter.

Figure 3.2: VCO schematic

The differential cascode-based active power splitter (Fig. 3.3) drives the classical balanced doubler on both transmitter side and receiver side with a output saturated power of 7.7 dBm.

Quarter wavelength short stubs are used at both double input and output to eliminate harmonics. (Fig. 3.4).

#### 3.2.3 I/Q Mixer and IF Amplifier

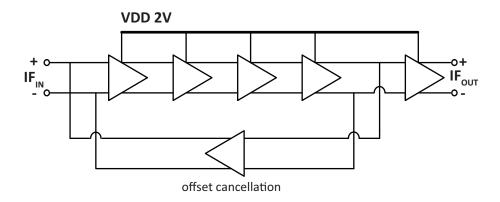

The I/Q balanced mixers (Fig. 3.5) have a simulated gain of 0 dB at 150 GHz at an LO power of -3 dBm (2 V, 13.5 mA) [43]. IF amplifier (Fig. 3.6) is built of four cascaded fixed gain stages with a feedback loop for DC offset cancellation. Output buffer is designed to drive 100  $\Omega$  differential load. The simulated 3-dB receiver bandwidth (mixer + IF amplifier) is ~140-152 GHz with an LO of 145 GHz, thus allowing for 20 Gbit/s data modulation. The simulated I/Q receiver gain and NF including the Wilkinson splitter loss for f<sub>RF</sub> = 150 GHz is 23 dB and 20 dB, respectively.

Figure 3.3: Active splitter schematic.

Figure 3.4: Doubler schematic.

Figure 3.5: Balanced mixer schematic schematic.

Figure 3.6: wideband IF amplifier schematic.

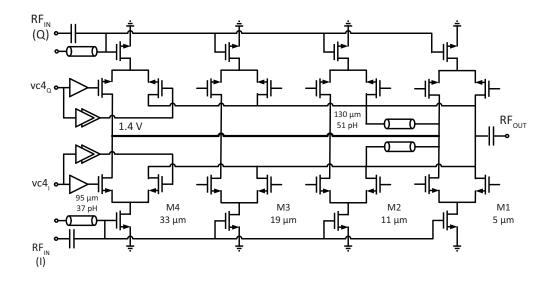

#### 3.2.4 I/Q Modulator Design

The I/Q modulator uses an LO switching transistor quad on the top level and I/Q data transistors on the bottom level (Fig. 3.7). A balun is used at the output port and provides a wideband conjugate impedance match between the modulator and the output 50  $\Omega$  port. The I/Q input data is retimed with the clock (CK) signal and turned differential using D-flip-flops with a rise/fall times of 14 ps, thus allowing > 20 Gbit/s per channel. The modulator interconnect parasitics are modeled from the top metal to C1 using Sonnet EM Suite and RC-extraction is done from M1 to C1.

#### 3.2.5 Packaging

Fig. 3.8 presents the chip micrograph with a size of 2.8x1.4 mm<sup>2</sup>. The chip consumes 345 mW with the on-chip LO (290 mW without the on-chip LO). The transceiver chip was placed on a Rogers-4003 board with  $\varepsilon_r$  = 3.5. The RF ports are probed using WR-6 GSG probes, and the off-chip LO is injected using a WR-10 GSG probe. (Fig. 3.9, Fig. 3.10)

Figure 3.7: I/Q modulator schematic.

Figure 3.8: Die micrograph.

Figure 3.9: PCB board.

Figure 3.10: Die & bonding on PCB board.

#### **3.3** Measurements

#### **3.3.1** Oscillator, Active Splitter and Receiver

The Clapp oscillator operated at 78.5-80.5 GHz from a 1/0.7 V supply (56 mW) with an output power of 0-3 dBm and a measured phase noise of < -92 dBc/Hz at 1 MHz. The oscillator shifted in frequency from a design of 74-76 GHz, but kept similar output power and phase noise values as simulated (Fig. 3.11, Fig. 3.12, Fig. 3.13)

The active splitter breakout has a measured gain of 6.8 dB at 75 GHz and an output  $P_{sat}$  of 8 dBm per channel (including GSG pads) from a 2 V supply (85 mW). The balanced doubler breakout results in a measured conversion loss of 3 dB and a peak output power of +3.5 dBm at 150 GHz, and with > 1.3 dBm from 140-160 GHz (includes GSG pads) from a 1 V supply. (Fig. 3.14)

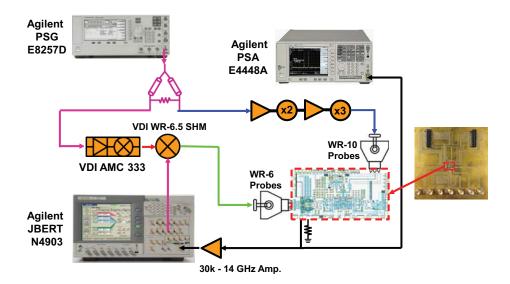

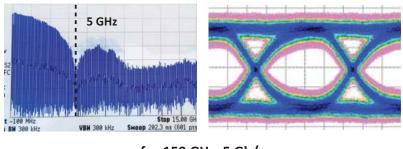

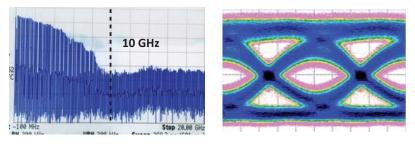

The measured conversion gain of the receiver is  $\sim$ 23 dB with a 3-dB bandwidth of 146-155 GHz for an LO of 150 GHz (Fig. 3.15). The I/Q channels were amplitude matched to +/-0.9 dB over the 3-dB bandwidth (Fig. 3.16). In general, the S-parameter measurement results agree well with simulations. Fig. 3.17 illustrates the setup for receiver eye diagram measurement. Carrier frequency is generated by the VDI AMC 333 multiplier chain, then it is mixed with the data from Keysight JBERT N4903 using VDI WR-6.5 sub-harmonic mixer for BPSK pattern. Spectrum and eye -diagram measured with 5 and 10 Gbit/s BPSK modulation at 150 GHz carrier frequency are showed on Fig. 3.18 as an evidence that the receiver can handle such data transition speed. Due to the VDI sub-harmonic mixer limitation, only BPSK modulation can be implemented. QPSK modulation will be tested with the transceiver loop back setup and measurement results will be presented in 'Transceiver Measurements' subsection.

Figure 3.11: Measured VCO tuning range.

Figure 3.12: Measured VCO output power.

Figure 3.13: Measured VCO phase noise.

Figure 3.14: Active power splitter power measurement results.

Figure 3.15: Receiver power gain.

Figure 3.16: Receiver gain variation.

Figure 3.17: Receiver eye diagram measurement setup.

f<sub>LO</sub>: 150 GHz, 5 Gb/s

f<sub>LO</sub>: 150 GHz, 10 Gb/s BPSK

Figure 3.18: Receiver spectrum and eye diagram measurement results.

#### **3.3.2** Modulator Measurements

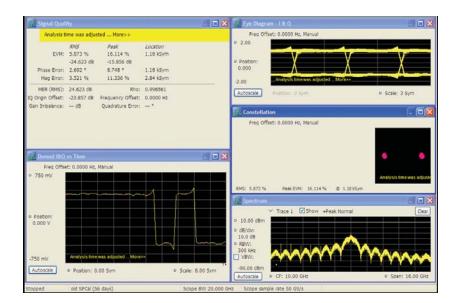

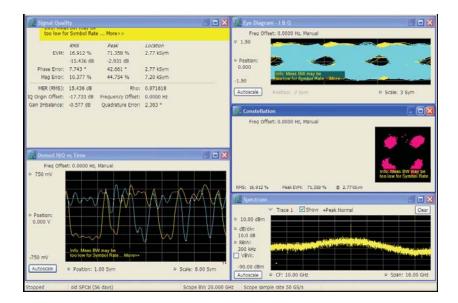

Measurements on a modulator breakout with LO and RF input/output baluns and a 0/90° hybrid show a peak gain of -4 dB at 140-145 GHz with a 3-dB bandwidth of 130-160 GHz, and a saturated output power of +1 dBm (Fig. 3.19, Fig. 3.20). The modulator results in < +/-0.7dB and  $\pm -6^{\circ}$  error with I/Q inputs of 00, 01, 10, 11 at 135-170 GHz (Fig. 3.21, Fig. 3.22). The modulator was also tested at an LO of 150-155 GHz, an output power of -10 dBm at the GSG pads, and with 0.1-12.6 Gbps I/Q data streams (Fig. 3.23). In this case, the output spectrum was down-converted to a center frequency of 10 GHz using a wideband subharmonic mixer followed by a 0.5-18 GHz amplifier with 26 dB gain (total receiver NF = 24 dB), and the OPSK signal fed into a Tektronics DPO scope. Fig. 3.24, Fig. 3.25, and Fig. 3.26 are screenshots of software evaluated spectrums, eye diagrams and EVM from the scope. A QPSK constellation is seen at 20 Gbit/s without any equalization and with an rms EVM of 16.9%. The measured LO leakage is -18 to -20 dBc at 150-155 GHz. The S/N ratio at the GSG pads is 40 dB in a 10 GHz bandwidth, resulting in an expected EVM of 1% (the modulator I/Q errors above add another  $\sim 1\%$ ). The increased EVM is due to impairments from the subharmonic mixer unequal upper side band/lower side band response, wideband external IF amplifier (+/-2dB ripple) and cable dispersion at DC-20 GHz. Measurements done at 2-20 Gbit/s show QPSK modulation EVM values of 6.6-16.9%.

**Figure 3.19**: *S*<sub>21</sub> measurement results for (00), (01), (10), and (11) I/Q inputs.

Figure 3.20: Modulator *P<sub>in</sub>* (LO power) versus *P<sub>out</sub>* measurement results.

Figure 3.21: Modulator gain error for (00), (01), (10), and (11) I/Q inputs.

**Figure 3.22**: Modulator phase error for (00), (01), (10), and (11) I/Q inputs.

Figure 3.23: Modulator performance measurements setup.

**Figure 3.24**: Measured modulator spectrum, eye diagram, and EVM at 150 GHz carrier frequency with 1 Gbit/s BPSK modulation

| Signal Quality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 🛐 Eye Diegram - I & Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |