## UC Davis UC Davis Previously Published Works

## Title

High-Mobility Hole Transport in Single-Grain PbSe Quantum Dot Superlattice Transistors

## Permalink

https://escholarship.org/uc/item/984395bb

## Journal

Nano Letters, 22(23)

## ISSN

1530-6984

## **Authors**

Abelson, Alex Qian, Caroline Crawford, Zachary <u>et al.</u>

Publication Date 2022-12-14

## DOI

10.1021/acs.nanolett.2c03657

Peer reviewed

# High-Mobility Hole Transport in Single-Grain PbSe Quantum Dot Superlattice Transistors

Alex Abelson, Caroline Qian, Zachary Crawford, Gergely T. Zimanyi, and Matt Law\*

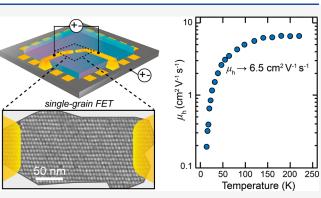

dots (QD epi-SLs) may exhibit electronic minibands and highmobility charge transport, but electrical measurements of epi-SLs have been limited to large-area, polycrystalline samples in which superlattice grain boundaries and intragrain defects suppress/ obscure miniband effects. Systematic measurements of charge transport in individual, highly-ordered epi-SL grains would facilitate the study of minibands in QD films. Here, we demonstrate the air-free fabrication of microscale field-effect transistors ( $\mu$ -FETs) with channels consisting of single PbSe QD epi-SL grains (2–7  $\mu$ m channel dimensions) and analyze charge transport in these single-grain devices. The eight devices studied show *p*-channel or ambipolar transport with a hole mobility as high

as  $3.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at 290 K and  $6.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at 170–220 K, one order of magnitude larger than that of previous QD solids. The mobility peaks at 150–220 K, but device hysteresis at higher temperatures makes the true mobility–temperature curve uncertain and evidence for miniband transport inconclusive.

**KEYWORDS:** colloidal quantum dots, superlattice, PbSe, single grain, field-effect transistor, charge transport

pitaxially-fused colloidal PbX (X = S, Se) quantum dot (OD)(QD) superlattices (epi-SLs)—arrays of QDs interconnected by homoepitaxial necks-combine extraordinary spatial order with strong inter-QD electronic coupling and are predicted to exhibit electronic minibands that enable highmobility, bandlike charge transport.<sup>1-12</sup> However, the epi-SLs studied thus far are too structurally defective (disordered) to support miniband formation, and electrical measurements of epi-SLs have demonstrated only localized carriers and hopping transport.<sup>7,8</sup> Ongoing efforts to eliminate intragrain defects are essential to trigger the emergence of minibands,<sup>12-14</sup> but it is also important to remove intergrain defects (grain boundaries and cracks) from the transport path in order to study the inherent properties of individual epi-SL grains (monocrystals).<sup>15</sup> A robust process for making measurements at the single-grain limit (monocrystalline devices) would enable systematic studies of miniband physics as a function of epi-SL structural order, surface chemistry, orientation, device size, and other parameters.

In this report, we describe the fabrication and electrical characterization of single-grain PbSe QD epi-SL field-effect transistors (FETs) made by multistep electron beam lithography (EBL). We infill and overcoat the epi-SLs with a thin layer of amorphous alumina by atomic layer deposition  $(ALD)^{16,11}$  to prevent their degradation by exposure to air, processing chemicals, mild heating, and the electron beam. We find that the mild heating needed to bake the electron-beam

resist for EBL processing (150 °C) also drastically lowers the doping of the ALD-infilled epi-SLs, without causing QD sintering. Variable-temperature electrical measurements of the resulting single-grain FETs (12–290 K) show a record-high hole mobility with a negative temperature dependence at higher temperatures that is suggestive of bandlike transport, but this antiactivated region is almost certainly an artifact of the bias-stress effect<sup>17</sup> rather than a signature of minibands. This paper introduces the single-grain FET fabrication process, details the structure and electrical properties of one device, briefly compares the behavior of an initial cohort of eight devices, and concludes with an analysis of the temperature dependence of the hole mobility in the four devices that were studied in detail.

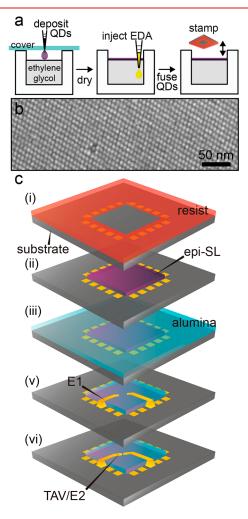

3D (multilayer) epi-SL films were fabricated by selfassembly of 6.9 nm diameter oleate-capped PbSe QDs (Figure S1) on the surface of liquid ethylene glycol (EG),<sup>18</sup> followed by injection of 1,2-ethylenediamine to trigger epitaxial fusion (necking) of the QDs via glycoxide-oleate ligand ex-

Received:September 22, 2022Revised:November 14, 2022Published:November 21, 2022

change<sup>11,12</sup> and stamp transfer of the resulting polycrystalline epi-SLs to custom-made device substrates (see Methods in the Supporting Information and Figure 1a). This procedure yields

Figure 1. Fabrication of single-grain epi-SL field-effect transistors. (a) Process for fabricating polycrystalline epi-SL films on the surface of ethylene glycol. (b) Post-mortem high-magnification SEM image of part of an epi-SL grain. The scale bar is 50 nm. (c) The single-grain FET fabrication process. (i) The Si/SiO<sub>2</sub> substrate (gray) was first patterned with photoresist (red) to expose a 550  $\times$  550  $\mu$ m square at the center of an array of prepatterned contact pads (gold). (ii) A polycrystalline epi-SL film was stamped onto the substrate and the resist was dissolved, leaving epi-SL film (purple) only in the central square. (iii) Alumina (blue) was deposited by ALD on the entire substrate, thereby infilling and overcoating the epi-SL. The substrate was then imaged by SEM to locate epi-SL grains of interest. (v) Coarse electrodes (E1) were written by EBL from the contact pads to within several micrometers of each selected epi-SL grain. (vi) Finally, through-alumina vias (TAVs) were patterned by EBL, wet-etched to expose the edges of each epi-SL grain and E1 electrode, and metalized (E2) to complete the single-grain epi-SL FETs. The image in (b) was acquired after FET fabrication and a post-mortem etch of the alumina to reveal the QDs.

epi-SLs with a rhombohedrally-distorted simple cubic unit cell  $(a \approx 6.9 \text{ nm}, \alpha \approx 99^{\circ})$  in which the QDs are necked across their {100} facets and the epi-SL grains are oriented predominantly with their  $(01\overline{1})_{\text{SL}}$  planes parallel to the substrate surface (Figure 1b).<sup>11</sup> Scanning electron microscopy (SEM) imaging showed that each epi-SL film consists of a

cracked, semicontinuous layer of equiaxed epi-SL grains (individual epi-SL crystallites) with a grain diameter as large as 10  $\mu$ m (Figure 2a). Film thicknesses of ~35 nm ("thin") and 60–85 nm ("thick") were studied. As discussed below, the thinner films show significantly higher hole mobility, probably because they are more fused and have thicker inter-QD necks.

Figure 1c depicts the air-free single-grain FET fabrication process that we developed to deterministically incorporate selected high-quality epi-SL grains into FETs to study charge transport at the single-grain limit. First, PbSe QD epi-SL films were stamped onto prepatterned substrates  $(p^{++})$  (100)oriented Si coated with a 200 nm thick SiO<sub>2</sub> layer and patterned with an array of metal contact pads and fiducial markers (5 nm Cr/45 nm Au)) and then infilled and overcoated with 11 nm of amorphous alumina using an inglovebox atomic layer deposition (ALD) system (see Methods) to prevent epi-SL oxidation/degradation.<sup>16</sup> Next, the films were imaged by SEM to identify individual highquality epi-SL grains for selective integration into FETs. The alumina layer thickness was optimized to balance film stability (as validated by FET measurements) and transparency to the electron beam (Figure S2). After imaging, an additional 22 nm of alumina was deposited to ensure indefinite environmental stability of the epi-SLs. We then used EBL to write "coarse" Cr/Au electrodes (labeled E1 in Figure 1c) from the prepatterned contact pads to within a few micrometers of each epi-SL grain of interest. These electrodes sit atop the 33 nm protective alumina layer and are therefore electrically isolated from the underlying film and produce negligible interelectrode leakage currents. Next, EBL-defined throughalumina vias (TAVs) were etched at a rate of ~0.6 nm/min using an aqueous sodium hydroxide solution (Figure S3) to expose the adjacent edges of the E1 electrodes and targeted grains. The TAVs were then metalized with "fine" Cr/Au electrodes (labeled E2) to connect the E1 electrodes selectively to each respective grain and define the FET channels. Finally, an additional 11 nm or more of alumina was deposited on the finished FETs to ensure their stability. This fabrication process prevents exposure of the QDs to air and lithographic processing chemicals and yields FETs with welldefined channels across single epi-SL grains in excellent electrical isolation from the rest of the film. A detailed description of the single-grain FET fabrication process is provided in Supporting Discussion 1.

Figure 2a shows a 35 nm thick single-grain FET with a channel length (L) and width (W) of 6.8 and 5.9  $\mu$ m, respectively. High-resolution SEM imaging (Figure 2b and Figure S4) shows that the channel contains two large  $(01\overline{1})_{SL}$ oriented epi-SL grains: a "major" grain that spans the electrodes, covers ~92% of the channel area, and contains 14 small, isolated twinned inclusions (blue lines in Figure 2b) and a "minor" grain that is adjacent to part of the source and does not span the electrodes. Based on this grain map, we expect that the source-drain current of this device will flow predominantly through the single-crystalline path provided by the major grain, and we therefore consider the device (Device 1) to be a single-grain FET. We used fast Fourier transform (FFT) images of the channel to determine epi-SL grain orientations and inter-QD distances. The FFT image of the entire channel yields a spot pattern that was indexed to the major (red) and minor (yellow) epi-SL grains (Figure 2c), while numerous FFTs of regions within the channel show an average inter-QD distance of 6.86 nm along  $[100]_{SL}$  and a

Figure 2. A single-grain epi-SL FET. (a) Perspective-view SEM image of a completed single-grain FET (Device 1, with channel dimensions of 6.8 × 5.9  $\mu$ m). E1 and E2 electrodes are colorized and labeled. (b) High-resolution plan-view SEM image of the FET channel after a post-mortem etch of the alumina coating. E2 source and drain electrodes are labeled. Blue lines denote SL twin planes. The [100]<sub>SL</sub> SL direction of the major epi-SL grain (red) and minor grain (yellow) are labeled. There are no additional planar or linear SL defects visible in the image. The faint vertical line near the center of the image is an image stitching artifact. (c) FFT of the entire channel with indexed SL spots for the major (red) and minor (yellow) epi-SL grains. (d) Room-temperature output characteristics ( $I_D-V_{SD}$ ) showing modulation of the drain current ( $I_D$ ) by the applied gate bias ( $V_G$ ) and *p*-channel behavior. The inset shows that the curves are nonlinear near  $V_{SD} = 0$  V. At each  $V_G$  (starting with  $V_G = 10$  V),  $V_{SD}$  was swept at a rate of 5 V/s from +10 to -50 V, then back to 10 V. (e) Room-temperature transfer characteristics ( $I_D-V_G$ ) for forward and reverse gate bias sweeps (sweep directions noted by black arrows). At each  $V_{SD}$  (starting with  $V_{SD} = 10$  V),  $V_G$  was swept at a rate of 200 V/s from +10 to -50 V, then back to 10 V. (f) Room-temperature  $I_D$  time trace upon stepping  $V_G$  from 0 to -50 V at t = 30 s ( $V_{SD} = -15$  V). The FET exhibits a significant bias-stress-effect transient at room temperature.

planar QD density of 17,390 QDs/ $\mu$ m<sup>2</sup> per QD monolayer, consistent with our previous reports.<sup>11,12</sup> Structural analysis of seven additional devices is provided in the Supporting Information, along with the corresponding charge transport data (Figures S5–S18). Devices 1–7 are single-grain FETs, while Device 8 is multicrystalline and serves as a control for the effect of grain boundaries on charge transport. Table S1 summarizes the microstructure and transport data for all eight devices. The seven single-grain FETs studied here are free of the SL grain boundaries and macroscopic cracks/voids that are common in polycrystalline epi-SL films made by ligand exchange and stamp transfer.

At room temperature, all but one of the FETs (Device 6, which is ambipolar) show *p*-channel conductance with moderate gate modulation of the drain current  $(I_D)$  and quasi-linear output curves  $(I_D-V_{SD})$  between 0 and -15 V (Figure 2d). Within  $V_{SD} = \pm 1$  V, the I-V curves are nonlinear (Figure 2c, inset), likely because of Schottky barriers at the QD/electrode interfaces. The nonlinearity also suggests that the contact resistance in these devices is significant and artificially lowers the values of the carrier mobility that are reported below. Contact resistance measurements and the associated correction of the mobility values will be performed with future batches of single-grain FETs. Transfer curves  $(I_D-V_G)$  exhibit hysteresis between forward and reverse  $V_G$  sweeps.

Reverse and forward sweeps for Device 1 yield a hole mobility of 4.3 and 6.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at  $V_{\rm G}$  = -45 V and  $V_{\rm SD}$  = -15 V (Figure 2e; see Methods). Hysteresis in the transfer curves is caused by the bias-stress effect (BSE), in which a buildup of a sheet of immobile charges near the gate/channel interface progressively screens the applied gate field and causes a timedependent (transient) reduction of the free carrier density and  $I_D$  in the FET channel.<sup>17</sup> Figure S19 provides graphical illustrations of the BSE and its electronic and ionic mechanisms. One consequence of the BSE is systematic underestimation of the carrier mobility derived from I-Vcurves. To approximately correct the mobility for the BSE, we measured the kinetics of  $I_{\rm D}$  decay after stepping  $V_{\rm G}$  from 0 to -50 V at the measurement temperature (Figure 2f and Figure S20) and used the fractional  $I_D$  decay at the mobility measurement time to determine a multiplicative correction factor, yielding a "transient-corrected" reverse and forward sweep mobility of 5.6 and 9.1  $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , respectively, for this device. We note that the true transient-free mobility is probably modestly higher than these imperfectly-corrected values. It is also important to point out that Device 1 consists of an isolated epi-SL flake that barely extends outside of the channel (Figure 2a); thus, fringing electric fields (spreading currents), which can cause mobility overestimation by up to a factor of ~2 for FETs with  $W/L \approx 1$  and semiconductor layers

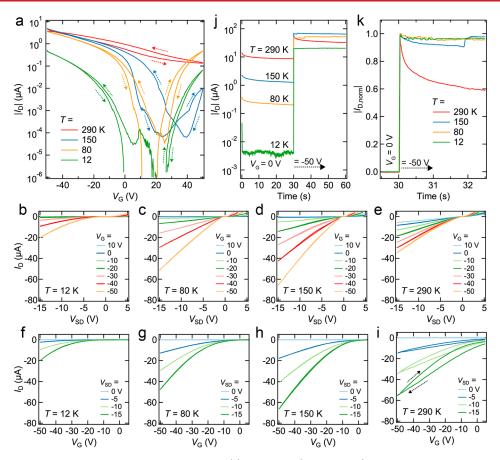

**Figure 3.** Temperature dependence of the FET *I*–*V* characteristics. (a) Full-sweep ( $V_G = \pm 50$  V) transfer curves for Device 1 acquired at T = 12, 80, 150, and 290 K at  $V_{SD} = 2$  V and a sweep rate of 5 V/s. The device is a *p*-channel at room temperature and becomes increasingly ambipolar at lower temperature.  $I_{OFF}$  drops dramatically with decreasing temperature. (b–e) Output curves acquired at T = 12, 80, 150, and 290 K, respectively, at a series of  $V_G$  values and a  $V_{SD}$  sweep rate of 5 V/s.  $V_{SD}$  was swept from +5 V to -15 V and then back to +5 V. (f–i) Corresponding transfer curves acquired at a series of  $V_{SD}$  values using a sweep rate of 200 V/s.  $V_G$  was swept from +10 V to -50 V, then back to +10 V. (j) Time traces of  $|I_D|$  as  $V_G$  is stepped from 0 to -50 V. Here,  $V_{SD} = -15$  V. (k) Comparison of the normalized  $|I_D|$  time traces from (j), with  $I_{D,norm} = \frac{I(t) - I_{V_G=0}}{I_{peak} - I_{V_G=0}}$ , where I(t) is the drain current at time *t*,  $I_{V_G=0}$  is the drain current at  $V_G = 0$  V, and  $I_{peak}$  is the peak drain current.

that are much wider than the channel,<sup>19</sup> are not important and do not affect the mobility for this device. Some of the other seven devices have geometries that may support substantial fringing currents (Figure S21), but we do not attempt to correct the extracted mobility values for this geometric effect because (i) the error in the mobility is small and uncertain, and (ii) the contact resistance and incomplete transient correction cause an uncertain and possibly larger error in the opposite direction.

These results are in contrast to our recent report of degenerate *n*-channel transport in polycrystalline, ALD-infilled epi-SL FETs.<sup>11</sup> In that work, we found that infilling epi-SLs with ALD alumina generates a large concentration of shallow donor defects that cause heavy electron doping of the films. We have since discovered that these donors can be passivated (or perhaps compensated) by mild thermal annealing of the infilled epi-SLs under either an inert atmosphere or air (Figure S22). Conveniently, the heating steps used to prepare the EBL resist layers (one 30 min dwell at 90 °C and two 3 min dwells at 150 °C) during FET fabrication also reproducibly passivate/ compensate the shallow donors and convert the FETs from poorly modulated *n*-channel devices to well-modulated *p*-channel devices. These data suggest that the *p*-channel behavior of these PbSe QD FETs results from annealing

rather than air exposure, the latter of which is well-known to pdope PbSe QD films.<sup>16</sup> However, since the annealing was performed in air, we cannot rule out the possibility of some airinduced oxidation of the heated films. An analysis of postmortem SEM images (Figures 1b and 2b and Figures S23 and \$24) and optical spectra (Figure \$22) shows that the annealing does not cause appreciable QD sintering/coarsening or loss of quantum confinement. We therefore believe that the observed changes in FET free carrier density and polarity are primarily caused by annealing-induced chemical reactions, atomic motion, and/or ligand rearrangements at the QD/alumina, QD/electrode and QD/SiO<sub>2</sub> interfaces. The annealing may also form/thicken epitaxial necks and improve their atomic coherence and thus the inter-QD electronic coupling by healing dislocations and relaxing strain defects, 13,14 despite encapsulation of the QDs by the conformal alumina coating.

Variable-temperature electrical measurements were used to study charge transport in the single-grain FETs. Figure 3 shows data for Device 1, while results from the other seven devices are provided in the Supporting Information. Decreasing the measurement temperature leads to a shift from *p*-channel to ambipolar transport and a sharp increase in the on–off ratio (from ~35 at 290 K to >10<sup>6</sup> at 12 K), consistent with the freeze-out of acceptor states and the influence of Schottky

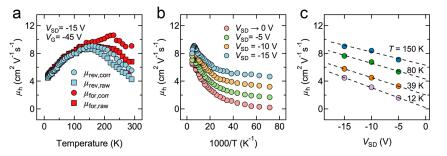

**Figure 4.** Temperature and field dependence of the hole mobility. (a) Hole mobility ( $V_{SD} = -15 \text{ V}$ ,  $V_G = -45 \text{ V}$ ) of Device 1 extracted from forward and reverse gate bias sweeps (200 V/s) without transient correction (squares) and with transient correction (circles). The mobility values converge below ~150 K because the bias-stress transient is quenched. (b)  $\mu_{rev,corr}$  determined at different  $V_{SD}$  values plotted as a function of inverse temperature to highlight the dependence of the low-temperature mobility on the longitudinal electric field. The field-free mobility curve ( $V_{SD} \rightarrow 0$  V, pink markers) was determined from the linear fits of  $\mu(V_{SD})$  presented in (c).  $V_G = -45 \text{ V}$ . (c) Linear fits of  $\mu_{rev,corr}$  as a function of  $V_{SD}$ . While only four temperatures are shown in (c), fits were performed across the entire temperature range (12–290 K) to produce the field-free mobility curve in (b).  $V_G = -45 \text{ V}$ .

barriers at the contacts (Figure 3a). The output curves (Figure 3b-e) display decreasing conductivity as the device is cooled. Transfer curves (Figure 3f-i) show that the threshold voltage monotonically shifts from positive values at room temperature to negative values ( $V_T \approx -10$  V) at 12 K. Furthermore, since the electron/hole trapping and ion motion that cause biasstress transients are generally thermally activated processes, the BSE is often progressively quenched at low temperatures. Below 150–200 K, the BSE current transients (Figure 3j,k) and *I*–*V* hysteresis are largely quenched and have only a minor impact on the transfer curves and measured carrier mobility.

Hole mobility  $(\mu_{\rm h})$  values were extracted from transfer curves acquired at T = 12-290 K (see Methods). Figure 4a shows the forward and reverse sweep mobilities for Device 1 with and without correction for bias-stress transients. Below ~150 K, the transient is negligible and the mobility values converge to a common weakly thermally-activated  $(d\mu/dT >$ 0) curve. The uncorrected data (squares in Figure 4a) show a peak mobility at ~150 K and a negative temperature dependence  $(d\mu/dT < 0)$  at higher temperatures that is suggestive of bandlike transport, 20-23 but this is likely an artifact of the bias-stress transients. The corrected data (circles) still show a  $d\mu/dT < 0$  region, but we cannot be certain if such behavior is real or the result of incomplete transient correction. Given this uncertainty and the small change of mobility with temperature  $(<2.5\times)$ , no conclusion can be made from the transport data regarding the presence of bandlike transport in this FET. All of the devices that we analyzed showed similar  $\mu(T)$  behavior (Figures S25 and S26). The typical  $\mu(T)$  behavior of bulk PbSe is shown in Figure S27 for comparison.

The hole mobility also depends on  $V_{\rm SD}$ , with the dependence being strongest at low temperature (Figure 4b). Plots of mobility versus  $V_{\rm SD}$  reveal a linear  $\mu(V_{\rm SD})$  dependence across the entire temperature range (Figure 4c and Figure S26). Linear fits of  $\mu(V_{\rm SD})$  were used to extrapolate a "field-free" mobility ( $V_{\rm SD} \rightarrow 0$  V), which is also plotted in Figure 4b. In short-channel FETs, the longitudinal electric field strength can result in a potential drop between neighboring QD centers ( $V_{\rm QD-QD}$ ) equal to or larger than the thermal energy kT, the charging energy  $E_{\rm C}$ , and the site energy disorder  $\Delta \alpha$  due to QD size dispersity and coupling disorder. In this case, the mobility can depend strongly on the magnitude of  $V_{\rm QD-QD}$  rather than kT,  $E_{\rm C}$  and  $\Delta \alpha$ .<sup>24</sup> For our epi-SLs, we calculate  $E_{\rm C} \approx 0.3$  meV and  $\Delta \alpha > 10$  meV (see Supporting Discussion 2).<sup>25</sup>

$V_{\rm QD-QD}$  can be estimated from  $V_{\rm SD}$  and the number of QDs along the transport path. If transport occurs predominantly in the QD monolayer closest to the gate dielectric, as is expected for FETs with conventional mexal-oxide gates, then the transport path is determined by the length of the epi-fused QD chains that run in the  $[100]_{SL}$  direction of the  $(01\overline{1})_{SL}$ oriented grains (Figure 1b). SEM imaging shows that the epi-SL grain in Device 1 has a misorientation angle  $\phi$  of 64° between its [100]<sub>SL</sub> and the FET channel (see Figure 2b and Table S1), such that carriers would need to travel through chains of ~2250 QDs to transit the channel. Assuming negligible potential drop at the contacts (an idealization), this yields  $V_{\text{QD-QD}}$  values of 2.2, 4.4, and 6.6 mV for  $V_{\text{SD}} = -5, -10$ , and -15 V, respectively. In devices where the epi-fused QD chains are better aligned with the channel, the channel length is shorter, or the second QD monolayer participates in transport (making transport isotropic in 2D),  $V_{\rm QD-QD}$  can be 20–30 meV at  $V_{SD} = -15$  V. Given that  $V_{QD-QD}$  is similar to or larger than kT,  $E_{\rm C}$ , and  $\Delta \alpha$ , a field-dependent mobility is expected, and the same  $\mu(V_{SD})$  trend was observed in the three other devices that we analyzed (Figures S25 and S26). Henceforth we focus only on the field- and transient-corrected mobility values.

The field-free, transient-corrected, reverse-swept hole mobility of our best device (Device 1) is 3.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature. This value is a conservative lower bound that does not fully correct for the bias-stress transient or account for possible potential drops at the source/drain contacts. The hole mobility peaks at ~6.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at T = 170-220 K, where the transient (hysteresis) is insignificant. To our knowledge, these are the highest hole mobilities yet reported for any QD solid, including PbX (previous record of  $\mu_h \approx 0.5$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>),<sup>8,26-30</sup> CdX, HgX,<sup>23</sup> CuInSe<sub>x</sub>S<sub>2-x</sub>,<sup>31</sup> and metal halide perovskite QDs,<sup>32</sup> which illustrates the importance of employing epitaxial connections for strong inter-QD coupling, controlled surface chemistry for doping and surface state management, and single-grain measurements to avoid transport bottlenecks by grain boundaries.

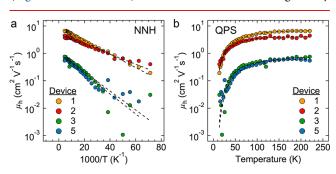

We analyzed the  $\mu(T)$  data of Devices 1–3 and 5 (the four devices analyzed in detail) with models of nearest-neighbor hopping (NNH), Efros–Shklovskii variable-range hopping (ES-VRH),<sup>33</sup> quantum percolation scaling (QPS),<sup>34</sup> and mixed conduction transport (a limit of QPS).<sup>23</sup> Due to the presence of current transients at higher temperatures, we limited our analysis to  $T \leq 220$  K, which excludes the  $d\mu/dT <$  0 region. The simple Arrhenius NNH expression  $\mu(T) = \mu_{\infty} \exp(-E_A/kT)$  with a temperature-independent prefactor  $\mu_{\infty}$  yields good fits with small activation energies of only 4–8 meV (Figure 5a and Table 1). These small activation energies may

**Figure 5.**  $\mu_h(T)$  fitting of four single-grain FETs. (a) NNH model fits. (b) QPS model fits. Fits were performed between 14 and 220 K. Data at 12 K were not included because the field-free mobility values at this temperature tended to be noisy, and >220 K data were excluded because of the BSE.

indicate that carriers find low-barrier percolative pathways through the epi-SLs.<sup>25</sup> Good fits were also obtained with the ES-VRH formula  $\mu(T) \sim (1/T) \exp(-(T_{\rm ES}/T)^{1/2})$ ,<sup>33</sup> which yielded localization lengths  $\xi = 6.1e^2/(4\pi\varepsilon_{\rm eff}\varepsilon_0k_{\rm B}T_{\rm ES})$  of just 2–4 nm, suggesting that hole wave functions are localized to single QDs and ES-VRH does not occur in these samples (Figure S28, Table 1, and Supporting Discussion 3). Including the normal  $T^{-1}$  dependence of the prefactor in the NNH expression<sup>35</sup> gave poor fits that severely underestimated the mobility at low temperature (Figure S29).

Quantitatively better fits were obtained using the quantum percolation scaling (QPS) model of Qu et al.<sup>34</sup> In this model, carriers delocalize within metallic clusters of well-coupled QDs characterized by a mobility  $\mu_{\text{met}}^{-1} = \mu_{\text{met},0}^{-1} + aT^{3/2}$  and hop between the clusters with a mobility  $\mu_{\text{hop}} = \mu_{\infty} \exp(-E_A/kT)$  to give an overall mobility  $\mu_{\text{OPS}}$ :

$$\mu_{\rm QPS}^{-1} = (\mu_{\rm met}/\mu_{\rm hop})^{1/2} (\mu_{\rm met}^{-1} + \Delta \mu_{\rm hop}^{-1})$$

Here,  $\Delta = (c - c_c)/c_c$  (where *c* and  $c_c$  are the concentration and critical concentration of hopping links, respectively) measures the dimensionless distance to the metal-insulator transition (MIT). The epi-SLs discussed in this report contain highly-uniform regions of epitaxially-fused QDs interspersed with a variety of point defects such as missing necks and QD vacancies. It is thus plausible that holes delocalize within the highly-uniform regions of the epi-SL and then hop between these regions. The QPS model yields the best fits as quantified by the residual sum of squares (RSS) method (Figure 5b and Supporting Discussion 4). The small  $\Delta$  of the two thinner, higher-mobility devices (Devices 1 and 2) suggests that the concentration of metallic clusters in these devices approaches

Table 1. Results of  $\mu(T)$  Fitting

the MIT to within a few percent (Table 1). Using the established critical exponent  $\nu = 1.33$ ,<sup>36</sup> this implies a localization length of 10–20 QDs for these two devices. Alternatively, we found localization lengths of 10–15 nm using the mixed conduction model that Lan et al. recently employed to assess transport in HgTe QD thin films (Table 1 and Figure S28).<sup>23</sup> Such localization lengths correspond to delocalization of holes within 3D clusters of 15–45 QDs.

Although the QPS model provides satisfactory fits of the  $\mu(T)$  data with physically sensible values, the picture of transport within epi-SLs remains unclear. Short localization lengths indicate that carriers remain localized within small clusters of QDs, likely as a result of the disorder in epi-SL neck size (including missing necks) and electronic coupling.<sup>8,13</sup> Surface/interface states, QD positional and orientational disorder, and point charges within the films can also disrupt the periodicity of the energy landscape and thereby localize charge carriers. Ongoing efforts to incorporate more perfect epi-SLs<sup>13,14,37,12</sup> into smaller FETs (<0.5  $\mu$ m channels) combined with strategies to eliminate or fill<sup>38</sup> carrier traps should soon enable electrical measurements of individual delocalized domains within epi-SL grains. Such small devices will require particularly low-resistance electrical contacts. It is also important to eliminate the bias-stress effect in order to obtain unambiguous  $\mu(T)$  data, which we have accomplished with amorphous PbSe QD films<sup>39</sup> but not yet with epi-SLs. The process for fabricating single-grain epi-SL devices demonstrated here sets the stage for systematic FET- and Hall-based charge transport studies of emergent miniband physics in these materials.

#### ASSOCIATED CONTENT

#### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acs.nanolett.2c03657.

Experimental methods, QD optical spectrum, structural and electrical characterization of each device, structure and transport data, transient correction methodology, effect of annealing, detailed  $\mu(T)$  data for each device, transport modeling, device fabrication details, estimate of site energy disorder and charging energy, comparison of charge transport models, and quantification of  $\mu(T)$ fits (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Author**

Matt Law – Department of Materials Science and Engineering, Department of Chemical and Biomolecular Engineering, and Department of Chemistry, University of California, Irvine, Irvine, California 92697, United States; o orcid.org/0000-0001-7645-9908; Email: matt.law@uci.edu

|        | NNH                     |                                                          | VRH                                     | QPS                          | mixed conduction      |

|--------|-------------------------|----------------------------------------------------------|-----------------------------------------|------------------------------|-----------------------|

| device | $E_{\rm A}~({\rm meV})$ | $\mu_{\infty} \ ({ m cm}^2 \ { m V}^{-1} \ { m s}^{-1})$ | $\xi (\mathrm{nm})/T_{\mathrm{ES}}$ (K) | $E_{ m A}~({ m meV})/\Delta$ | $\xi (nm)/T_{ES} (K)$ |

| 1      | $4.6 \pm 0.1$           | $8.6 \pm 0.1$                                            | 2.8 / 1000                              | 2.5 / 0.05                   | 10 / 281              |

| 2      | $3.9 \pm 0.2$           | $5.2 \pm 0.3$                                            | 3.6 / 792                               | 2.0 / 0.06                   | 15 / 189              |

| 3      | $7.5 \pm 0.2$           | $1.1 \pm 0.1$                                            | 2.1 / 1356                              | 4.8 / 0.10                   | 7.6 / 371             |

| 5      | $7.1 \pm 0.4$           | $1.1 \pm 0.1$                                            | 2.0 / 1395                              | 4.2 / 0.22                   | 4.1 / 686             |

#### Authors

- Alex Abelson Department of Materials Science and Engineering, University of California, Irvine, Irvine, California 92697, United States; Present Address: Materials Engineering Division, Lawrence Livermore National Laboratory, Livermore, CA 94550, USA

- **Caroline Qian** Department of Chemical and Biomolecular Engineering, University of California, Irvine, Irvine, California 92697, United States

- Zachary Crawford Department of Physics, University of California, Davis, Davis, California 95616, United States; orcid.org/0000-0002-6604-1687

- **Gergely T. Zimanyi** Department of Physics, University of California, Davis, Davis, California 95616, United States

Complete contact information is available at: https://pubs.acs.org/10.1021/acs.nanolett.2c03657

#### **Author Contributions**

A.A. synthesized the QDs, developed and carried out the single-grain FET fabrication, and performed imaging and electrical measurements. C.Q. fabricated the SL films and helped to fabricate the single-grain FETs. A.A., Z.C., and G.T.Z. modeled the data. M.L. directed the study and assisted with data interpretation. A.A. and M.L. wrote the manuscript with input from all authors.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

C.Q., Z.C., and M.L. were supported by the National Science Foundation under Grant No. DMR-2005210. A.A. was supported by the UC Office of the President under the UC Laboratory Fees Research Program Collaborative Research and Training Award LFR-17-477148. AFM measurements and parts of the manuscript preparation and data analysis were performed by A.A. under the auspices of the U.S. DOE by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344. Materials characterization was performed at the user facilities of the UC Irvine Materials Research Institute (IMRI), which is supported in part by the National Science Foundation through the UC Irvine Materials Research Science and Engineering Center (DMR-2011967). The authors thank I. Sequeira and J. Sanchez-Yamagishi for assistance with e-beam lithography and use of the calibrated optical microscope, J. Ziegler and R. Penner for the use of and assistance with their photolithography system, and C. Orme for assistance with AFM measurements.

#### REFERENCES

(1) Lazarenkova, O. L.; Balandin, A. A. Miniband Formation in a Quantum Dot Crystal. J. Appl. Phys. 2001, 89 (10), 5509-5515.

(2) Jiang, C.-W.; Green, M. A. Silicon Quantum Dot Superlattices: Modeling of Energy Bands, Densities of States, and Mobilities for Silicon Tandem Solar Cell Applications. *J. Appl. Phys.* **2006**, *99* (11), 114902.

(3) Kalesaki, E.; Evers, W. H.; Allan, G.; Vanmaekelbergh, D.; Delerue, C. Electronic Structure of Atomically Coherent Square Semiconductor Superlattices with Dimensionality below Two. *Phys. Rev. B* **2013**, *88* (11), 115431.

(4) Baumgardner, W. J.; Whitham, K.; Hanrath, T. Confined-but-Connected Quantum Solids via Controlled Ligand Displacement. *Nano Lett.* **2013**, *13* (7), 3225–3231. (5) Evers, W. H.; Goris, B.; Bals, S.; Casavola, M.; de Graaf, J.; van Roij, R.; Dijkstra, M.; Vanmaekelbergh, D. Low-Dimensional Semiconductor Superlattices Formed by Geometric Control over Nanocrystal Attachment. *Nano Lett.* **2013**, *13* (6), 2317–2323.

(6) Sandeep, C. S. S.; Azpiroz, J. M.; Evers, W. H.; Boehme, S. C.; Moreels, I.; Kinge, S.; Siebbeles, L. D. A.; Infante, I.; Houtepen, A. J. Epitaxially Connected PbSe Quantum-Dot Films: Controlled Neck Formation and Optoelectronic Properties. *ACS Nano* **2014**, *8* (11), 11499–11511.

(7) Evers, W. H.; Schins, J. M.; Aerts, M.; Kulkarni, A.; Capiod, P.; Berthe, M.; Grandidier, B.; Delerue, C.; van der Zant, H. S. J.; van Overbeek, C.; Peters, J. L.; Vanmaekelbergh, D.; Siebbeles, L. D. A. High Charge Mobility in Two-Dimensional Percolative Networks of PbSe Quantum Dots Connected by Atomic Bonds. *Nat. Commun.* **2015**, *6* (1), 8195.

(8) Whitham, K.; Yang, J.; Savitzky, B. H.; Kourkoutis, L. F.; Wise,

F.; Hanrath, T. Charge Transport and Localization in Atomically

Coherent Quantum Dot Solids. *Nat. Mater.* 2016, *15* (5), 557–563.

(9) Gómez-Campos, F. M.; Rodríguez-Bolívar, S.; Califano, M.

High-Mobility Toolkit for Quantum Dot Films. ACS Photonics 2016, 3 (11), 2059–2067.

(10) Balazs, D. M.; Matysiak, B. M.; Momand, J.; Shulga, A. G.; Ibanez, M.; Kovalenko, M. V.; Kooi, B. J.; Loi, M. A. Electron Mobility of 24 cm2V-1s-1 in PbSe Colloidal-Quantum-Dot Superlattices. *Adv. Mater.* **2018**, 30 (38), 1802265.

(11) Abelson, A.; Qian, C.; Salk, T.; Luan, Z.; Fu, K.; Zheng, J.-G.; Wardini, J. L.; Law, M. Collective Topo-Epitaxy in the Self-Assembly of a 3D Quantum Dot Superlattice. *Nat. Mater.* **2020**, *19* (1), 49–55.

(12) Qian, C.; Abelson, A.; Miller-Casas, A.; Capp, R.; Vinogradov, I.; Udagawa, N. S.; Ge, N.-H.; Law, M. Photobase-Triggered Formation of 3D Epitaxially Fused Quantum Dot Superlattices with High Uniformity and Low Bulk Defect Densities. *ACS Nano* **2022**, *16* (2), 3239–3250.

(13) Walravens, W.; Solano, E.; Geenen, F.; Dendooven, J.; Gorobtsov, O.; Tadjine, A.; Mahmoud, N.; Ding, P. P.; Ruff, J. P. C.; Singer, A.; Roelkens, G.; Delerue, C.; Detavernier, C.; Hens, Z. Setting Carriers Free: Healing Faulty Interfaces Promotes Delocalization and Transport in Nanocrystal Solids. *ACS Nano* **2019**, *13* (11), 12774–12786.

(14) Smeaton, M. A.; El Baggari, I.; Balazs, D. M.; Hanrath, T.; Kourkoutis, L. F. Mapping Defect Relaxation in Quantum Dot Solids upon In Situ Heating. *ACS Nano* **2021**, *15* (1), 719–726.

(15) Hansen, C.; Unruh, D.; Alba, M.; Qian, C.; Abelson, A.; Law, M.; Zimanyi, G. T. Hierarchical Carrier Transport Simulator for Defected Nanoparticle Solids. *Sci. Rep.* **2021**, *11* (1), 7458.

(16) Liu, Y.; Gibbs, M.; Perkins, C. L.; Tolentino, J.; Zarghami, M. H.; Bustamante, J.; Law, M. Robust, Functional Nanocrystal Solids by Infilling with Atomic Layer Deposition. *Nano Lett.* **2011**, *11* (12), 5349–5355.

(17) Osedach, T. P.; Zhao, N.; Andrew, T. L.; Brown, P. R.; Wanger, D. D.; Strasfeld, D. B.; Chang, L.-Y.; Bawendi, M. G.; Bulović, V. Bias-Stress Effect in 1,2-Ethanedithiol-Treated PbS Quantum Dot Field-Effect Transistors. *ACS Nano* **2012**, *6* (4), 3121–3127.

(18) Dong, A.; Chen, J.; Vora, P. M.; Kikkawa, J. M.; Murray, C. B. Binary Nanocrystal Superlattice Membranes Self-Assembled at the Liquid-Air Interface. *Nature* **2010**, *466* (7305), 474–477.

(19) Chen, C.; Chen, Z.; Xu, K.; Zheng, J.; Ou, H.; Wang, Z.; Chen, H.; Liu, X.; Wu, Q.; Chan, P. K. L.; Liu, C. Thin-Film Transistors with the Fringe Effect and the Correction Factor for Mobility Extraction. *IEEE Electron Device Lett.* **2019**, *40*, 897–900.

(20) Lee, J.-S.; Kovalenko, M. V.; Huang, J.; Chung, D. S.; Talapin, D. V. Band-like Transport, High Electron Mobility and High Photoconductivity in All-Inorganic Nanocrystal Arrays. *Nat. Nano.* **2011**, *6* (6), 348–352.

(21) Choi, J.-H.; Fafarman, A. T.; Oh, S. J.; Ko, D.-K.; Kim, D. K.; Diroll, B. T.; Muramoto, S.; Gillen, J. G.; Murray, C. B.; Kagan, C. R. Bandlike Transport in Strongly Coupled and Doped Quantum Dot Solids: A Route to High-Performance Thin-Film Electronics. *Nano Lett.* **2012**, *12* (5), 2631–2638. (22) Guyot-Sionnest, P. Electrical Transport in Colloidal Quantum Dot Films. *J. Phys. Chem. Lett.* **2012**, 3 (9), 1169–1175.

(23) Lan, X.; Chen, M.; Hudson, M. H.; Kamysbayev, V.; Wang, Y.; Guyot-Sionnest, P.; Talapin, D. V. Quantum Dot Solids Showing State-Resolved Band-like Transport. *Nat. Mater.* **2020**, *19* (3), 323–329.

(24) Yu, D.; Wang, C.; Wehrenberg, B. L.; Guyot-Sionnest, P. Variable Range Hopping Conduction in Semiconductor Nanocrystal Solids. *Phys. Rev. Lett.* **2004**, *92* (21), 216802.

(25) Liu, Y.; Gibbs, M.; Puthussery, J.; Gaik, S.; Ihly, R.; Hillhouse, H. W.; Law, M. Dependence of Carrier Mobility on Nanocrystal Size and Ligand Length in PbSe Nanocrystal Solids. *Nano Lett.* **2010**, *10* (5), 1960–1969.

(26) Talapin, D. V.; Murray, C. B. PbSe Nanocrystal Solids for nand p-Channel Thin Film Field-Effect Transistors. *Science* **2005**, *310* (5745), 86–89.

(27) Oh, S. J.; Berry, N. E.; Choi, J.-H.; Gaulding, E. A.; Paik, T.; Hong, S.-H.; Murray, C. B.; Kagan, C. R. Stoichiometric Control of Lead Chalcogenide Nanocrystal Solids to Enhance Their Electronic and Optoelectronic Device Performance. *ACS Nano* **2013**, 7 (3), 2413–2421.

(28) Zhao, M.; Yang, F.; Liang, C.; Wang, D.; Ding, D.; Lv, J.; Zhang, J.; Hu, W.; Lu, C.; Tang, Z. High Hole Mobility in Long-Range Ordered 2D Lead Sulfide Nanocrystal Monolayer Films. *Adv. Funct. Mater.* **2016**, *26* (28), 5182–5188.

(29) Scheele, M.; Engel, J. H.; Ferry, V. E.; Hanifi, D.; Liu, Y.; Alivisatos, A. P. Nonmonotonic Size Dependence in the Hole Mobility of Methoxide-Stabilized PbSe Quantum Dot Solids. *ACS Nano* **2013**, *7* (8), 6774–6781.

(30) Jo, C. H.; Kim, J. H.; Kim, J.; Kim, J.; Oh, M. S.; Kang, M. S.; Kim, M.-G.; Kim, Y.-H.; Ju, B.-K.; Park, S. K. Low-Temperature Annealed PbS Quantum Dot Films for Scalable and Flexible Ambipolar Thin-Film-Transistors and Circuits. *J. Mater. Chem. C* **2014**, 2 (48), 10305–10311.

(31) Draguta, S.; McDaniel, H.; Klimov, V. I. Tuning Carrier Mobilities and Polarity of Charge Transport in Films of CuInSexS2-x Quantum Dots. *Adv. Mater.* **2015**, *27* (10), 1701–1705.

(32) Kim, J.; Hu, L.; Chen, H.; Guan, X.; Anandan, P. R.; Li, F.; Tang, J.; Lin, C.-H.; Kalantar-Zadeh, K.; Tricoli, A.; Wu, T. P-Type Charge Transport and Selective Gas Sensing of All-Inorganic Perovskite Nanocrystals. *ACS Materials Lett.* **2020**, 2 (11), 1368– 1374.

(33) Efros, A. L.; Shklovskii, B. I. Coulomb Gap and Low Temperature Conductivity of Disordered Systems. J. Phys. C: Solid State Phys. 1975, 8 (4), L49.

(34) Qu, L.; Vörös, M.; Zimanyi, G. T. Metal-Insulator Transition in Nanoparticle Solids: Insights from Kinetic Monte Carlo Simulations. *Sci. Rep* **2017**, *7* (1), 7071.

(35) Bagley, B. G. The Field Dependent Mobility of Localized Electronic Carriers. *Solid State Commun.* **1970**, *8* (5), 345–348.

(36) Levinshtein, M. E.; Shklovskii, B. I.; Shur, M. S.; Efros, A. L. The Relation Between the Critical Exponents of Percolation Theory. *Soviet Physics JETP* **1975**, *42*, 197.

(37) Ondry, J. C.; Alivisatos, A. P. Application of Dislocation Theory to Minimize Defects in Artificial Solids Built with Nanocrystal Building Blocks. *Acc. Chem. Res.* **2021**, *54* (6), 1419–1429.

(38) Pinna, J.; Mehrabi K, R.; Gavhane, D. S.; Ahmadi, M.; Mutalik, S.; Zohaib, M.; Protesescu, L.; Kooi, B. J.; Portale, G.; Loi, M. A. Approaching Bulk Mobility in PbSe Colloidal Quantum Dots 3D Superlattices. *Adv. Mater.* **2022**, 2207364.

(39) Tolentino, J.; Gibbs, M.; Law, M. Elimination of bias stress effect in ligand-free quantum dot field-effect transistors. Manuscript in Preparation.