### **UC Riverside**

### **UC Riverside Electronic Theses and Dissertations**

### **Title**

Runtime Support For Maximizing Performance on Multicore Systems

### **Permalink**

https://escholarship.org/uc/item/99r4j1ws

### **Author**

Pusukuri, Kishore Kumar

### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

Runtime Support For Maximizing Performance on Multicore Systems

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Kishore Kumar Pusukuri

September 2012

### Dissertation Committee:

Dr. Rajiv Gupta, Chairperson

Dr. Laxmi N. Bhuyan

Dr. Walid Najjar

| The | Dissertat | ion of Kisł | nore Kuma | r Pusukuri is | approved:      |

|-----|-----------|-------------|-----------|---------------|----------------|

|     |           |             |           |               |                |

|     |           |             |           |               |                |

|     |           |             |           |               |                |

|     |           |             |           |               |                |

|     |           |             |           |               |                |

|     |           |             |           |               |                |

|     |           |             |           |               |                |

|     |           |             |           | Committe      | ee Chairperson |

|     |           |             |           |               | 1              |

University of California, Riverside

#### Acknowledgments

First and foremost I would like to sincerely thank my advisor, Dr. Rajiv Gupta, who was always there for me and shaped my research in many ways. His enthusiasm in research and hard working nature were instrumental in enabling my research to make the progress which it has made. I am particularly grateful for all the freedom he gave me in selecting research problems and his seemingly never-ending trust in my potential.

Next, I would like to thank the members of my dissertation committee, Dr. Laxmi N. Bhuyan and Dr. Walid Najjar for reviewing this dissertation. Their extensive and constructive comments have been very helpful in improving this dissertation.

I was fortunate enough to do various internships during the course of my Ph.D. In particular, my internship experience at Sun Microsystem Laboratories, Menlo Park, CA. was very rewarding and helpful for improving this dissertation. I would like to sincerely thank Dr. David Vengerov, Dr. Steve Heller, Rick Weisner, Darrin Johnson, Eric Saxe, and Kuriakose Kurivilla from Sun Microsystems and Dr. Alexandra Fedorova from Simon Fraser University for making my internship as a valuable research experience.

Next, I would like to express my gratitude to all the members of my research group including Min Feng, Changhui Lin, Yan Wang, Li Tan, and Sai Charan for helping me in many ways during these years. I would like to thank the rest of the Department of Computer Science and Engineering for providing a pleasant research environment.

I would also like to thank all my teachers I have had throughout my life. Last but not least, I would like to thank my family and friends who supported me throughout this endeavor. In particular, I wish to thank my wife, Swathi Sandhya, for her love and support.

### ABSTRACT OF THE DISSERTATION

Runtime Support For Maximizing Performance on Multicore Systems

by

#### Kishore Kumar Pusukuri

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, September 2012 Dr. Rajiv Gupta, Chairperson

Since multicore systems offer greater performance via parallelism, future computing is progressing towards use of machines with large number of cores. However, due to the complex interaction among characteristics of multithreaded applications, operating system policies, and architectural characteristics of multicore systems, delivering high performance on multicore systems is a challenging task. This dissertation addresses the above challenge by developing runtime techniques to achieve high performance when running a single multithreaded application as well as high system utilization and fairness when running multiple multithreaded applications. The runtime techniques are based on a simple monitoring system that captures important application characteristics and relevant architectural factors with negligible overhead.

To develop runtime techniques for achieving high performance when running a single multithreaded program on a multicore system, important performance limiting factors that impact the scalability of performance are identified. These factors include the threads configuration (i.e., the number of threads for a multithreaded program that provide the

vi

best speedup) and the thread scheduling and memory allocation polices employed. This dissertation presents two runtime techniques *Thread Reinforcer*, for dynamically determining appropriate threads configuration and *Thread Tranquilizer*, for dynamically selecting appropriate scheduling and memory allocation policies. By dynamically determining the appropriate threads configuration, scheduling policy, and memory allocation policy the performance of applications is maximized.

Lock contention is an important performance limiting factor for multithreaded programs on a multicore system. The dissertation presents two techniques *Thread Shuffling* and *FaithFul Scheduling* to limit the performance impact due to locks. *Thread Shuffling* reduces high lock acquisition latencies, resulting from the NUMA nature of a multicore system, via inter-CPU thread migrations. *FaithFul Scheduling* reduces the durations for which threads hold locks by minimizing lock holder thread preemptions through adaptive timequanta allocations. These techniques significantly enhance the performance of applications in the presence of high lock contention.

Finally, this dissertation presents a coscheduling technique called *ADAPT* for achieving high system utilization and fairness when running multiple multithreaded applications on multicore systems. *ADAPT* uses supervised learning techniques for predicting the effects of interference between programs on their performance and adaptively schedules together programs that interfere with each other's performance minimally. It achieves high throughput, high system utilization, and fairness when running multiple multithreaded applications.

# Contents

| Li            | st of | Figures                                                                  | xi  |

|---------------|-------|--------------------------------------------------------------------------|-----|

| $\mathbf{Li}$ | st of | Tables                                                                   | xiv |

| 1             | Intr  | roduction                                                                | 1   |

|               | 1.1   | Dissertation Overview                                                    | 3   |

|               |       | 1.1.1 Selecting Configuration for Delivering Performance                 | 3   |

|               |       | 1.1.2 Dealing with Performance Impact of Lock Contention                 | 5   |

|               |       | 1.1.3 Considering Interactions among Multiple Multithreaded Applications | 7   |

|               | 1.2   | Dissertation Organization                                                | 10  |

| 2             | Det   | ermining Number of Threads                                               | 11  |

|               | 2.1   | Identifying Important Performance Limiting Factors                       | 12  |

|               |       | 2.1.1 OPT-Threads > Number of Cores:                                     | 15  |

|               |       | 2.1.2 OPT-Threads < Number of Cores                                      | 21  |

|               | 2.2   | The Thread Reinforcer Framework                                          | 23  |

|               |       | 2.2.1 Algorithm                                                          | 25  |

|               |       | 2.2.2 Finding Thresholds                                                 | 29  |

|               | 2.3   | Evaluating Thread Reinforcer                                             | 30  |

|               | 2.4   | Summary                                                                  | 31  |

| 3             | Sele  | ecting System Policies                                                   | 34  |

|               | 3.1   | Performance Variation Study                                              | 37  |

|               |       | 3.1.1 Thread Migrations and Memory Allocation Policies                   | 37  |

|               |       | 3.1.2 Dynamic Priorities and Involuntary Context-switches                | 42  |

|               |       | 3.1.3 Combination of Memory Allocation and Scheduling Policies           | 44  |

|               | 3.2   | The Thread Tranquilizer Framework                                        | 49  |

|               | 3.3   | Evaluating Thread Tranquilizer                                           | 52  |

|               |       | 3.3.1 Improved Performance and Reduced Performance Variation             | 52  |

|               |       | 3.3.2 Improved Fairness and Effectiveness Under High Loads               | 55  |

|               | 3.4   | Summary                                                                  | 56  |

| 4 | Rec | lucing Lock Acquisition Overhead                            | 57  |

|---|-----|-------------------------------------------------------------|-----|

|   | 4.1 | Performance Degradation due to Locks and ccNUMA             | 58  |

|   | 4.2 | Thread Shuffling                                            | 64  |

|   |     | 4.2.1 Monitoring Threads                                    | 69  |

|   |     | 4.2.2 Forming Thread Groups                                 | 70  |

|   |     | 4.2.3 Performing Thread Shuffling                           | 71  |

|   | 4.3 | Evaluating Thread Shuffling                                 | 71  |

|   |     | 4.3.1 Performance Benefits                                  | 73  |

|   |     | 4.3.2 Cost and Efficiency                                   | 74  |

|   |     | 4.3.3 Time Varying Behavior                                 | 75  |

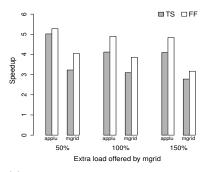

|   |     | 4.3.4 Multiple Applications                                 | 78  |

|   | 4.4 | Summary                                                     | 79  |

| 5 | Rec | lucing Critical Section Delays                              | 81  |

| J | 5.1 | Interaction between OS Scheduling and Contention Management | 82  |

|   | 5.2 | FaithFul Scheduling (FF)                                    | 85  |

|   | 0.2 | 5.2.1 Scaling-factor Table                                  | 86  |

|   |     | 5.2.2 Dealing with Phase Changes                            | 88  |

|   |     | 5.2.3 Dealing with Pipeline Parallelism                     | 89  |

|   |     | 5.2.4 Implementation of FF Policy                           | 90  |

|   | 5.3 | Evaluating FF policy                                        | 93  |

|   | 0.0 | 5.3.1 Benchmarks                                            | 93  |

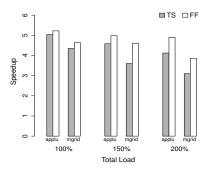

|   |     | 5.3.2 Against varying contention levels                     | 94  |

|   |     | 5.3.3 Against phase changes                                 | 95  |

|   |     | 5.3.4 Against dynamic load changes                          | 96  |

|   |     | 5.3.5 Performance Improvements                              | 97  |

|   |     | 5.3.6 Multiple Applications                                 | 99  |

|   | 5.4 | Summary                                                     | 100 |

| 6 | Cos | scheduling Multiple Multithreaded Applications              | 101 |

| • | 6.1 | Cache Miss-Ratio vs Lock-contention vs Latency              | 102 |

|   | 6.2 | The ADAPT Framework                                         | 105 |

|   | 0   | 6.2.1 The Cores Allocator                                   | 106 |

|   |     | 6.2.2 The Policy Allocator                                  | 115 |

|   |     | 6.2.3 Implementation of ADAPT                               | 121 |

|   | 6.3 | Evaluating ADAPT                                            | 124 |

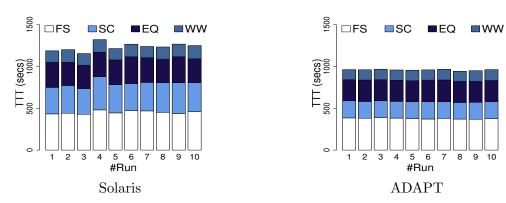

|   | 0.0 | 6.3.1 Performance and System Utilization Improvements       | 125 |

|   |     | 6.3.2 Impact on Performance Variation                       | 127 |

|   | 6.4 | Summary                                                     | 128 |

| 7 | Rel | ated Work                                                   | 129 |

| • | 7.1 | Balancing Parallelism and Resource Usage                    | 129 |

|   | ,   | 7.1.1 One Thread Per Core Model                             | 130 |

|   |     | 7.1.2 Dynamically Determining Number of Threads             | 130 |

|   |     | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                     |     |

|     | 7.2   | Configuring System Policies                                   | 32         |

|-----|-------|---------------------------------------------------------------|------------|

|     |       | 7.2.1 Study on Performance Variation                          | 32         |

|     |       | 7.2.2 Reducing Performance Variation                          | 33         |

|     |       | 7.2.3 NUMA Optimization Techniques                            | 34         |

|     | 7.3   | Lock Contention                                               | 34         |

|     |       | 7.3.1 Synchronization Mechanisms                              | 34         |

|     |       | 7.3.2 Reducing Lock Acquisition Overhead                      | 37         |

|     |       | 7.3.3 Reducing Critical Section Delays                        | 38         |

|     | 7.4   | Thread Scheduling                                             | 38         |

|     |       | 7.4.1 Operating System Scheduling                             | 38         |

|     |       | 7.4.2 Work Stealing                                           | 39         |

|     |       | 7.4.3 Thread Coscheduling                                     | 10         |

|     |       | 7.4.4 Other Scheduling Techniques                             | 13         |

| 8   | Con   | clusions 14                                                   | 4          |

|     | 8.1   | Contributions                                                 | 14         |

|     |       | 8.1.1 Selecting Configuration for Delivering Performance      | 15         |

|     |       | 8.1.2 Dealing with Performance Impact of Lock Contention 14   | 16         |

|     |       | 8.1.3 Coscheduling Multiple Multithreaded Programs            | <b>1</b> 7 |

|     | 8.2   | Future Directions                                             | 17         |

|     |       | 8.2.1 Enhancing Scalability of Resource Usage Monitoring 14   | 17         |

|     |       | 8.2.2 Using Monitoring for Runtime Power Management           | 18         |

|     |       | 8.2.3 Monitoring for Fault Isolation and High Availability 14 | 18         |

|     |       | 8.2.4 Monitoring and Coscheduling for Virtualized Systems 14  | 19         |

| Bil | വിറ്റ | raphy 15                                                      | 60         |

# List of Figures

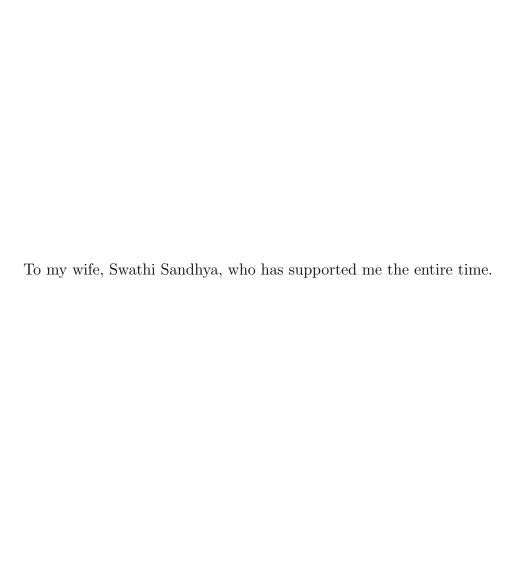

| 1.1               | Speedup behavior of PARSEC programs ferret, bodytrack, and facesim on          |                 |

|-------------------|--------------------------------------------------------------------------------|-----------------|

|                   | our 24-core machine for varying number of threads                              | 4               |

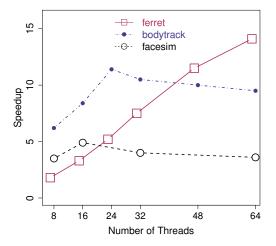

| 1.2               | Execution times of <i>streamcluster</i> and <i>facesim</i> programs in 10 runs | 5               |

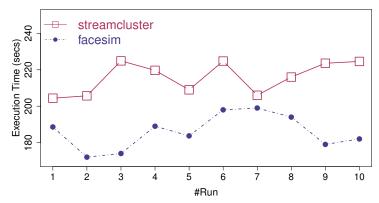

| 1.3               | Lock times of PARSEC and SPEC OMP programs when 64 threads are run             |                 |

|                   | on 64 cores spread across 4 CPUs                                               | 6               |

| 1.4               | Lock time (% of execution time), Thread Latency (% of execution time), and     | 0               |

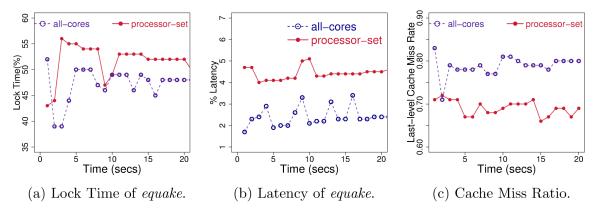

|                   | Last-level Cache Miss Ratio of equake when executed with facesim               | 9               |

| 1.5               | Lock Time (% of execution time), Thread latency (% of execution time), and     |                 |

|                   | Last-level Cache Miss Ratio of bodytrack when executed with applu              | 9               |

| 2.1               | Breakdown of elapsed time of critical threads                                  | 14              |

| 2.2               | Speedup behavior of PARSEC workloads for varying number of threads: the        |                 |

|                   | graph on the left shows the behavior of applications where maximum speedup     |                 |

|                   | was observed for $Number\ of\ Threads > Number\ of\ Cores = 24$ ; and          |                 |

|                   | the graph on the right shows the behavior of applications where maximum        |                 |

|                   | speedup was observed for $Number\ of\ Threads < Number\ of\ Cores = 24$ .      | 15              |

| 2.3               | swaptions: Cause of Erratic Speedup Changes                                    | 17              |

| $\frac{2.5}{2.4}$ | bodytrack: Cause of Decline in Speedup.                                        | 18              |

| 2.5               | Maximum Speedup When Number of Threads < Number of Cores                       | 21              |

| $\frac{2.5}{2.6}$ | Voluntary Context Switch Rate                                                  | $\frac{21}{22}$ |

| $\frac{2.0}{2.7}$ | VCX vs. ICX                                                                    | 22              |

| 2.1               | VCA VS. ICA                                                                    | 22              |

| 3.1               | The impact of thread migration on CPU-intensive and memory-intensive sin-      |                 |

|                   | gle threaded micro-benchmarks. Standard deviation (SD) of the running-         |                 |

|                   | times and the average number of thread migrations (last column) per run        |                 |

|                   | are presented in the table                                                     | 39              |

| 3.2               | Running-times and cache miss-rates of facesim (memory-intensive program)       |                 |

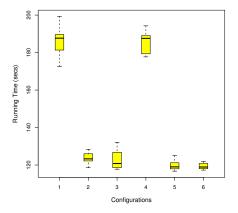

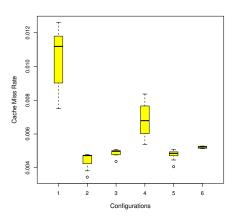

|                   | in 10 runs. Table 3.3 lists the configurations.                                | 45              |

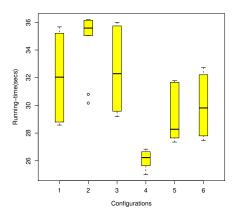

| 3.3               | Running-times and ICX Rates of mgrid (CPU-intensive program) in 10 runs.       |                 |

|                   | Table 3.3 lists the configurations                                             | 46              |

|                   |                                                                                |                 |

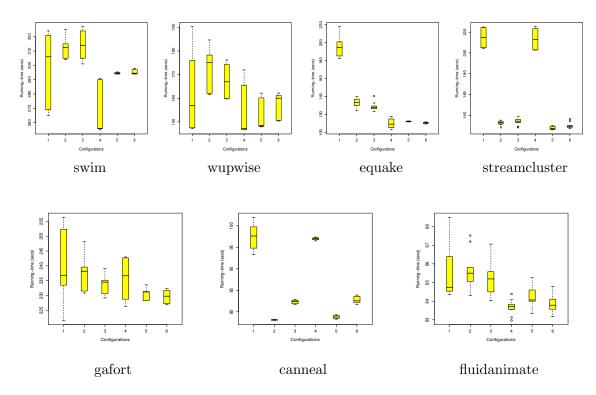

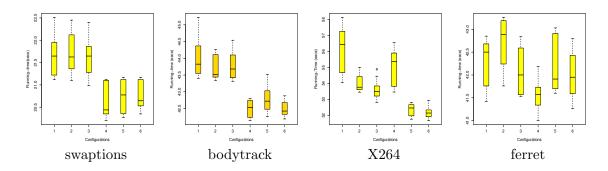

| 3.4        | Performance variation of memory-intensive programs is reduced with the combination of Random memory allocation and FX scheduling policies             | 47                              |

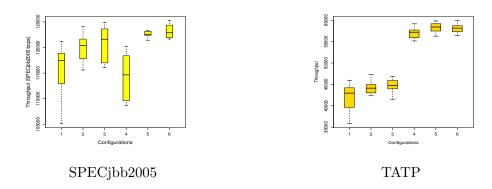

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.5        | Performance variation of SPECjbb2005 and TATP is reduced with the combination of Random and FX policies. Performance (throughput) is also             |                                 |

|            | ·                                                                                                                                                     | 47                              |

| 3.6        | Performance variation of CPU-intensive programs is reduced with FX scheduling policy. There is no significant effect of Random or RR policies on CPU- | 40                              |

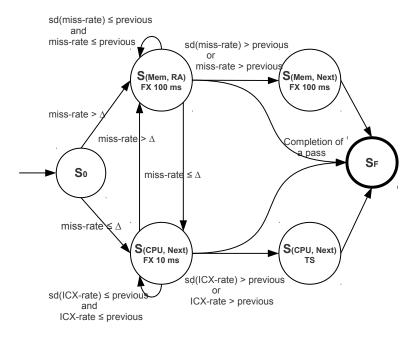

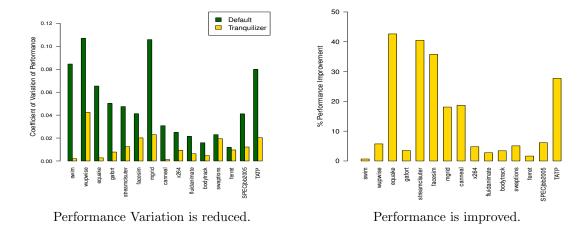

| 3.7        | 1 0                                                                                                                                                   | 48<br>50                        |

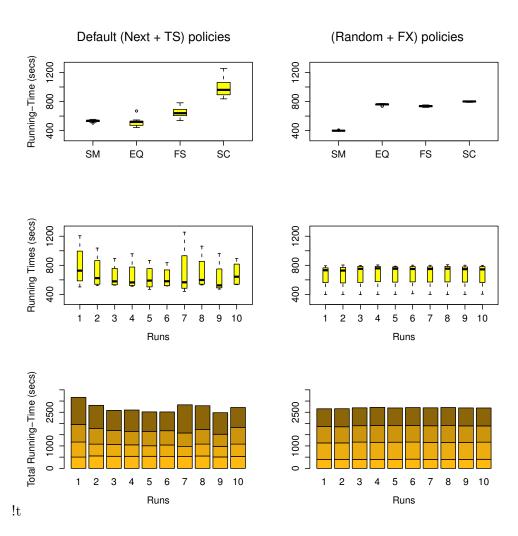

| 3.8        | Performance variation is reduced and performance is improved with Thread Tranquilizer. The bar plot shows another view of the reduction in perfor-    |                                 |

| 3.9        | Thread Tranquilizer is very effective against parallel runs of more than one                                                                          | <ul><li>51</li><li>54</li></ul> |

| 4.1        | Lock times of PARSEC and SPEC OMP programs when 64 threads are run                                                                                    | <b>F</b> 0                      |

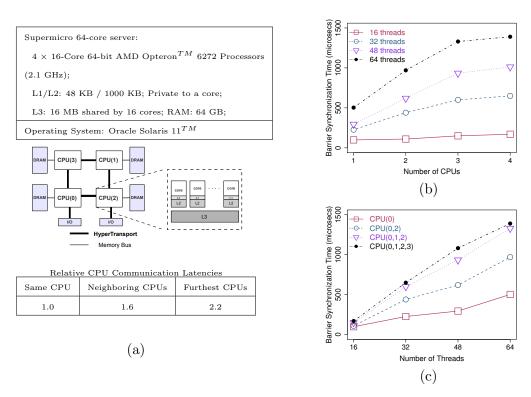

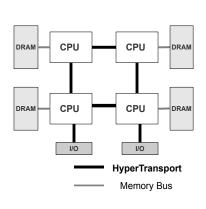

| 4.2        | (a) ccNUMA machine; (b) Barrier execution times for varying number of                                                                                 | 58<br>60                        |

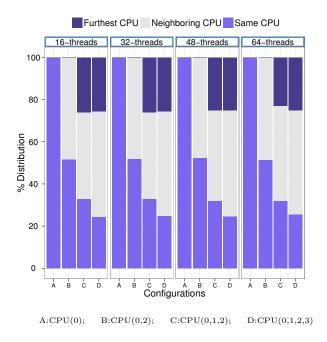

| 4.3        | $(Barrier)\ The\ distribution\ of\ lock\ transfers\ for\ successful\ (Acquire; Release)$                                                              | 64                              |

| 4.4        | 1                                                                                                                                                     | 66                              |

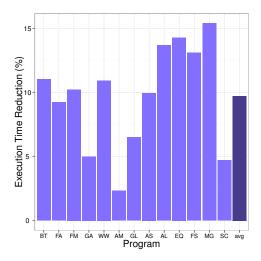

| 4.5        |                                                                                                                                                       | 72                              |

| 4.6        | 9                                                                                                                                                     | 72                              |

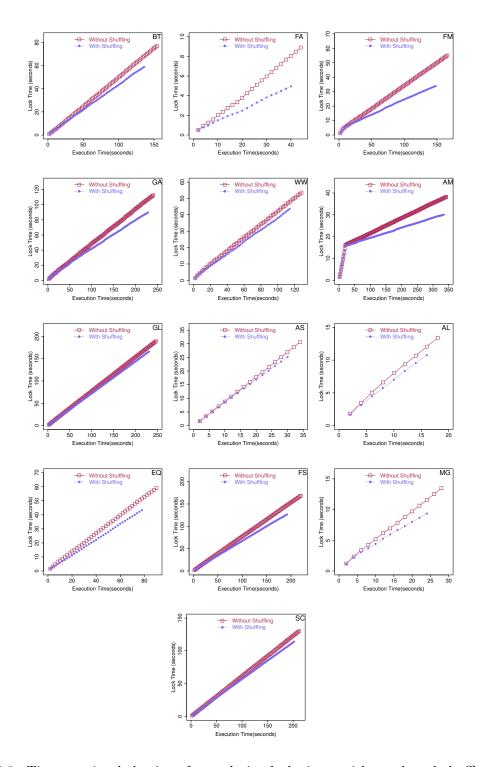

| 4.7<br>4.8 | Time varying behavior of cumulative lock times without thread shuffling and                                                                           | 74                              |

| 4.9        | 9                                                                                                                                                     | 76<br>77                        |

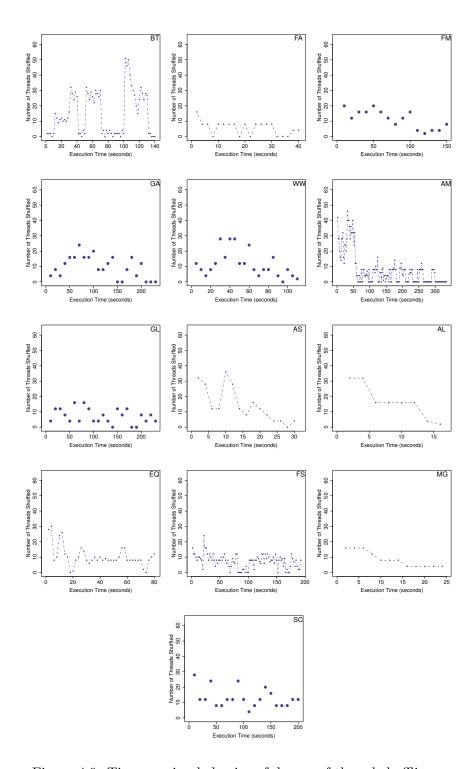

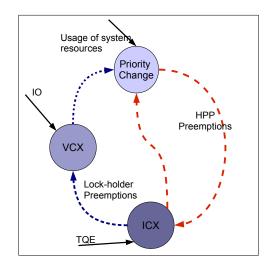

| 5.1        | Frequent changes in thread priority drastically increases thread context-<br>switches                                                                 | 83                              |

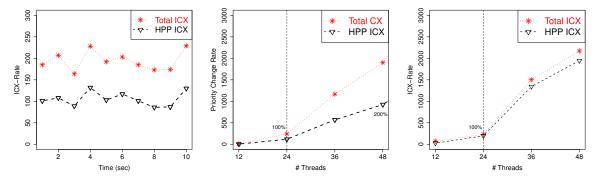

| 5.2        | The interactions between the TS policy and the spin-then-block policy create                                                                          | 84                              |

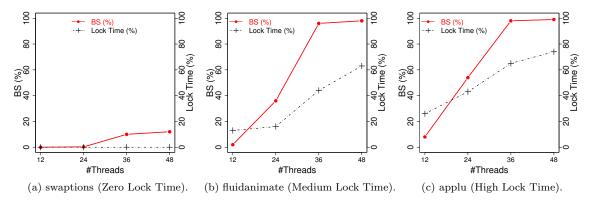

| 5.3        | BS vs Lock Time (24 threads is 100% load)                                                                                                             | 85                              |

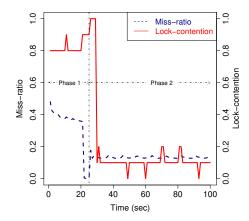

| 5.4        | Phase changes of ammp. Here ammp is run with 24 threads. Lock-contention value 1 means application experiences lock-contention for 100% of the total  |                                 |

|            | *                                                                                                                                                     | 89                              |

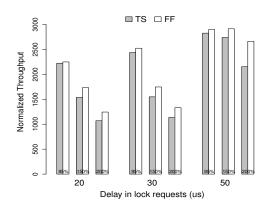

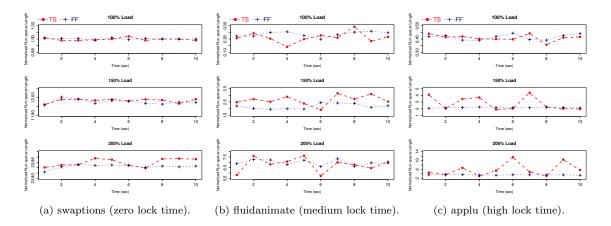

| 5.5        |                                                                                                                                                       | 95                              |

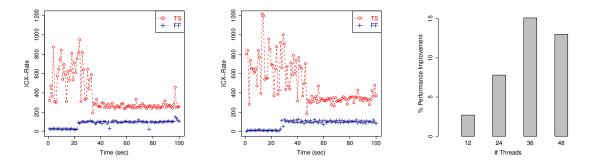

| 5.6        | FF policy effectively deals with phases of ammp program and improves its                                                                              | 00                              |

| 5.7        | •                                                                                                                                                     | 96<br>97                        |

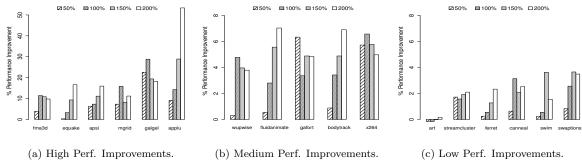

| 5.8        | - · ·                                                                                                                                                 | 98                              |

| 5.9        | Performance improvement of SPECjbb2005, facesim, and TATP with FF                                                                                     | <i>J</i> O                      |

| -          |                                                                                                                                                       | 98                              |

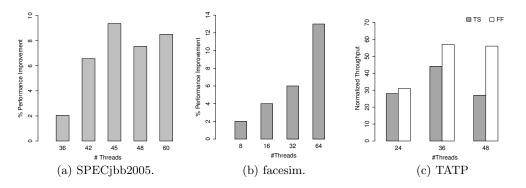

| 5.10 | FF policy is very effective against parallel runs of more than one application. | 100 |

|------|---------------------------------------------------------------------------------|-----|

| 6.1  | The machine has four 16-core CPUs and are interconnected with Hyper-            |     |

|      | Transport. Table shows the number of cores allocated to two programs A          |     |

|      | and B in different cores-configurations                                         | 103 |

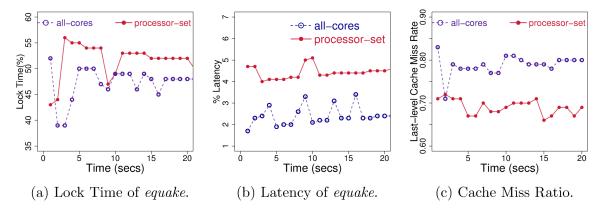

| 6.2  | Lock time (% of execution time), Thread Latency (% of execution time), and      |     |

|      | Last-level Cache Miss Ratio of equake when executed with facesim                | 104 |

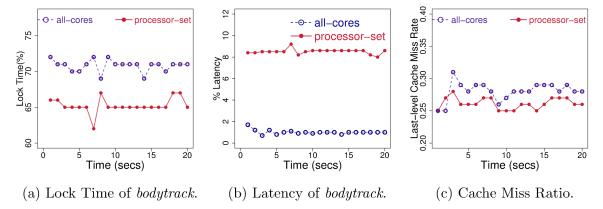

| 6.3  | Lock Time (% of execution time), Thread latency (% of execution time), and      |     |

|      | Last-level Cache Miss Ratio of bodytrack when executed with applu               | 105 |

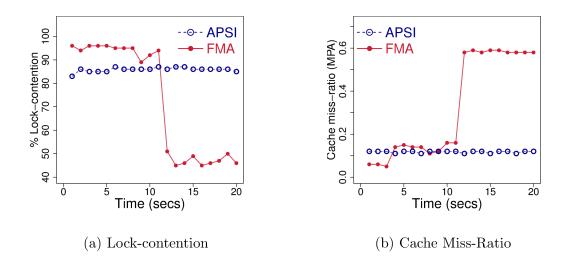

| 6.4  | While APSI has steady behavior, FMA shows a significant phase change            | 114 |

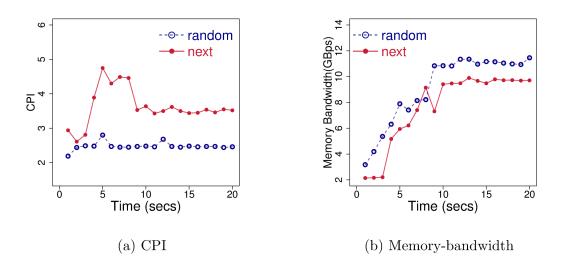

| 6.5  | CPI is high with next policy. Random policy improves memory-bandwidth.          | 118 |

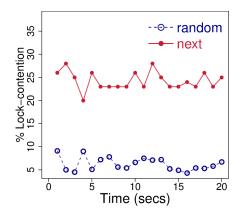

| 6.6  | Random policy reduces lock-contention                                           | 119 |

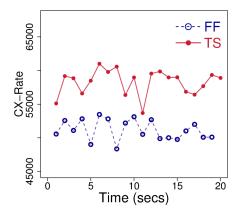

| 6.7  | FF policy reduces context-switch rate of APSI                                   | 120 |

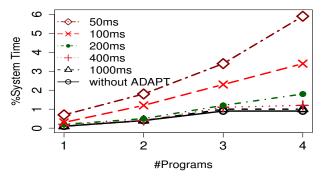

| 6.8  | Size of time-interval vs System overhead                                        | 123 |

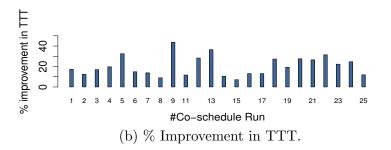

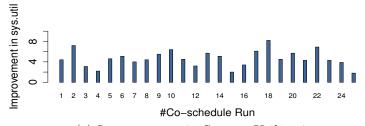

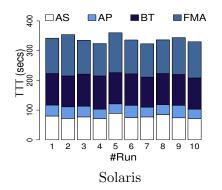

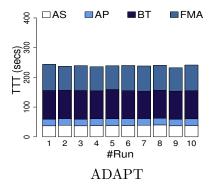

| 6.9  | ADAPT improves TTT and system utilization compared to the default So-           |     |

|      | laris scheduler. Here, improvement in system utilization = (utilization with    |     |

|      | ADAPT - utilization with Solaris)                                               | 126 |

| 6.10 | ADAPT improves performance of all the four memory-intensive programs            | 127 |

| 6.11 | ADAPT improves performance of all the four CPU-intensive programs               | 128 |

# List of Tables

| 2.1 | Maximum speedups observed and corresponding number of threads for PAR-                    |     |

|-----|-------------------------------------------------------------------------------------------|-----|

|     | SEC programs on the 24-core machine                                                       | 13  |

| 2.2 | Behavior of ferret                                                                        | 20  |

| 2.3 | Factors considered wrt to the number of threads                                           | 23  |

| 2.4 | Table 2.4: Algorithm vs. Optimal (PARSEC programs)                                        | 31  |

| 2.5 | Algorithm vs. Optimal (Other programs)                                                    | 32  |

| 2.6 | Search Overhead (seconds) for PARSEC programs                                             | 33  |

| 2.7 | Search Overhead (seconds) for Other programs                                              | 33  |

| 3.1 | Performance variation of the programs                                                     | 36  |

| 3.2 | Memory Allocation Policies                                                                | 41  |

| 3.3 | Configurations                                                                            | 45  |

| 3.4 | Thread Tranquilizer improves performance and reduces performance varia-                   |     |

|     | tion simultaneously by applying the combination of Random and FX policies.                |     |

|     | Standard deviation values are used to allow the readers to easily map the                 |     |

|     | boxplots (length of the boxplot) with the standard deviation values. $\ . \ . \ .$        | 53  |

| 4.1 | Thread shuffling multiple applications                                                    | 79  |

| 5.1 | The Scaling-factor Table. The range of the scaling-factor is 0.10. $ \dots  \dots  \dots$ | 88  |

| 6.1 | Initial predictors and the target $usr_ab$ of the PAAP model                              | 108 |

| 6.2 | VIF values of PAAP predictors                                                             | 108 |

| 6.3 | Models                                                                                    | 110 |

| 6.4 | VIF values of the PACC model predictors                                                   | 112 |

| 6.5 | Models                                                                                    | 112 |

| 6.6 | The actual and predicted $usr\_FA$ and $usr\_SM$ values with PAAP and PACC                |     |

|     | models are shown here                                                                     | 113 |

## Chapter 1

## Introduction

The advent of multicore architectures provides an attractive opportunity for achieving high performance for a wide range of multithreaded applications. However, exploiting the parallelism they offer, to improve performance of multithreaded programs is a challenging task. This is because of the complex interaction between several factors that affect the performance including: application characteristics (e.g., degree of parallelism, lock contention, and memory bandwidth requirements); operating system policies (e.g., scheduling and memory management policies); and architectural characteristics (e.g., cache hierarchy and non-uniform memory access latencies).

Current practices fail to fully consider the above factors and hence do not fully realize the potential of multicore systems in delivering performance for multithreaded applications. Here are some instances of common practices that illustrate the lack of full consideration of above factors. Multithreaded applications are often written such that it is the responsibility of the user to specify the number of threads to be created to exploit paral-

lelism. An uninformed user may select too few or too many threads for execution and thus achieve suboptimal performance. Modern Operating Systems (OSs) such as OpenSolaris and GNU/Linux do not distinguish between threads from multiple single threaded applications and multiple threads corresponding to a single multithreaded application. Therefore they fail to consider the interactions among different multithreaded applications running on the system and effectively coschedule them. Even under the scenario when a single multithreaded application is being run on the system, these OSs exhibit certain drawbacks. Since they are oblivious to lock contention among threads of a multithreaded application, they fail to consider contention when scheduling threads across the CPUs of a cache-coherent Non-Uniform Memory Access (ccNUMA) multicore system. The default OS memory allocation policy aims to exploit data locality by allocating data close to the threads. Though these policies work well for multiple single threaded programs, this is not the case for multithreaded programs. This is because many multithreaded programs involve communication between threads, leading to contention for shared objects and resources.

To alleviate the above problems, this dissertation develops lightweight runtime techniques to monitor important resource-usage characteristics of multithreaded applications, understand the interactions between OS policies and execution behavior of the applications, and then adaptively create appropriate number of threads, assign appropriate number of cores, and select appropriate OS scheduling and memory allocation policies.

### 1.1 Dissertation Overview

This dissertation consists of three parts. First, it presents runtime monitoring techniques to select the configuration under which an application performance is expected to be high. The configuration includes factors such as, number of threads, the scheduling policy, and the memory management policy. Second, as an application executes under the selected configuration, it presents techniques to minimize the harmful impact of high lock contention on program performance. In particular, it presents techniques to minimize the times threads spend on acquiring locks and durations for which they hold locks. All of the above work is carried out in context of executing a single multithreaded application on a multicore system. The third part of this dissertation develops runtime techniques for effectively coscheduling multiple multithreaded applications being simultaneously run of the system.

#### 1.1.1 Selecting Configuration for Delivering Performance

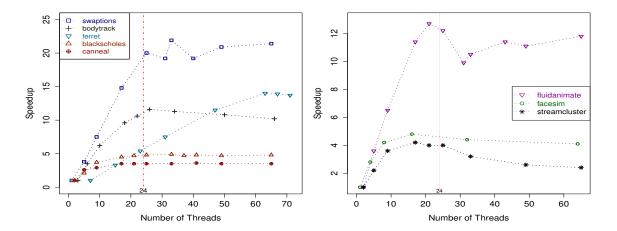

The performance of a multithreaded program running on a multicore system is sensitive to the number of threads used to run the application (i.e., threads configuration), as it impacts the application's resource-usage characteristics. For example, the number of threads that produce maximum speedups vary widely for PARSEC [1] programs on our 24-core machine running OpenSolaris. As Figure 1.1 shows, not only does the maximum speedup achieved by the three PARSEC programs vary widely (from 4.9x for facesim to 14x for ferret), the number of threads that produce maximum speedups also varies widely (from 16 threads for facesim to 63 threads for ferret). Therefore, for achieving the best per-

formance for a multithreaded program, it should be run with a suitable number of threads. However, an uninformed user may select too few or too many threads for execution and thus achieve suboptimal performance. An attractive technique for solving this problem is to dynamically determine the suitable number of threads for running the program. However, dynamically finding a suitable number of threads for a multithreaded program running on a multicore system is a challenging problem because it requires identifying important application characteristics. This dissertation presents a runtime technique called Thread Reinforcer, which monitors important application characteristics at runtime to guide the search for determining appropriate number of threads that are expected to yield the best speedup.

Figure 1.1: Speedup behavior of PARSEC programs ferret, bodytrack, and facesim on our 24-core machine for varying number of threads.

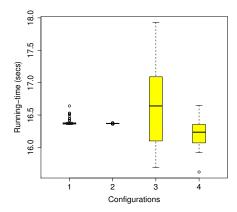

The performance of a multithreaded program is sensitive to the OS scheduling and memory allocation policies employed. This is because the interactions between program memory reference behavior and the OS scheduling and memory allocation policies significantly impacts application performance. These interactions make the performance of a program highly sensitive to small changes in resource usage characteristics of the program. In particular, significant variations in the performance are observed from one execution of a program to the next, even when the program input remains unchanged and no other applications are being run on the system. Figure 1.2 shows that the PARSEC programs streamcluster and facesim exhibit significant variation in their execution times across ten runs even when their inputs remain unchanged. This dissertation presents a runtime technique called Thread Tranquilizer, which simultaneously reduces performance variation and improves performance by adaptively choosing appropriate memory allocation and process scheduling policies based upon the resource usage characteristics of the programs.

Figure 1.2: Execution times of streamcluster and facesim programs in 10 runs.

### 1.1.2 Dealing with Performance Impact of Lock Contention

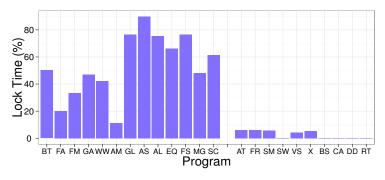

On a ccNUMA system, the performance of a multithreaded application is often impacted greatly by lock contention. Figure 1.3 presents the lock times of programs from PARSEC and SPEC OMP benchmark suites. Here, the lock time is defined as the percent-

age of elapsed time a program spends on performing operations on locks. As Figure 1.3 shows, the first 13 programs out of a total of 23 programs, exhibit very high lock times when they are run with 64 threads on a 64-core machine.

PARSEC: blackscholes (BS); bodytrack (BT); canneal (CA); dedup (DD); fluidanimate (FA); facesim (FS); ferret (FR); raytrace (RT); streamcluster (SC); swaptions (SW); vips (VS); x264 (X); SPEC OMP: applu (AL); ammp (AM); art (AT); apsi (AS); equake (EQ); fma3d (FM); gafort (GA); galgel (GL); mgrid (MG); swim (SM); wupwise (WW)

Figure 1.3: Lock times of PARSEC and SPEC OMP programs when 64 threads are run on 64 cores spread across 4 CPUs.

This dissertation considers the following two reasons for high lock times:

• High lock acquisition latencies. On a ccNUMA system the performance of a multithreaded application is highly sensitive to the distribution of application threads across the multiple multicore CPUs. In particular, when multiple threads compete to acquire a lock, due to the NUMA nature of the architecture, the time spent on acquiring locks by threads distributed across different CPUs is greatly increased.

• Prolonged durations for which locks are held. Under high load conditions, frequent preemption of lock holder threads can slow down the progress of lock holder threads and increase lock times. In particular, negative interaction between the Time Share (TS) thread scheduling policy and the spin-then-block lock-contention management policy dramatically increases lock holder thread preemptions under high loads.

To address the above problems, this dissertation presents two techniques *Thread Shuffling* and *Faithful Scheduling*. *Thread Shuffling* minimizes the times threads spend on acquiring locks through inter-CPU thread migrations and *Faithful Scheduling* minimizes lock holder thread preemptions via adaptive time-quanta allocations.

## 1.1.3 Considering Interactions among Multiple Multithreaded Applications

Since the performance of multithreaded applications often does not scale to fully utilize the available cores in a multicore system, simultaneously running multiple multithreaded applications becomes inevitable to fully utilize such machines. However, coscheduling multithreaded programs effectively on such machines is a challenging problem.

There are two different cores configurations that can be used for coscheduling multiple multithreaded programs on a multicore system: all-cores configuration; and processor-set configuration. In all-cores configuration each program is run using all the cores while in processor-set configuration each program is run on a separate processor-set to minimize interference between the programs. A processor-set is a pool of cores such that if a multi-threaded program is assigned to a processor-set, OS migrates the threads of the program

only across the cores belonging to the processor-set for balancing load. Next, it is illustrated how the cores configuration impacts the lock times (time spent on lock operations and in critical sections), latency (time ready threads spend waiting for a core to become available), and last level cache miss ratios (cache misses/accesses). These impacts collectively determine which configuration is the most suitable.

When two memory-intensive and high lock contention multithreaded programs facesim and equake are coscheduled in the above two configurations, all-cores configuration gives better overall performance. This is even though, due to their memory-intensive nature, these programs suffer from higher last-level cache miss ratios under all-cores configuration. This is because facesim and equake are also high lock-contention programs. As Figure 1.4 shows, equake experiences high lock times and latency in processor-set configuration compared to all-cores configuration. Likewise, although not shown here, facesim also experiences high lock times and latency in processor-set configuration compared to all-cores configuration. Thus, the trade-off between lock contention, latency, and last-level cache miss ratio results in the all-cores configuration delivering better performance.

When two CPU intensive and high lock-contention multithreaded programs bodytrack and applu are co-scheduled, processor-set configuration provides high performance

compared to all-cores configuration. As shown in Figure 1.5, thread latency of bodytrack is

low in all-cores configuration compared to processor-set configuration. Likewise, although

not shown here, the thread latency of applu is also low in all-cores configuration. However,

as shown in Figure 1.5, lock time and last level cache miss ratio for bodytrack are higher in

all-cores configuration. Likewise, the lock times of applu is also high in all-cores configu-

Figure 1.4: Lock time (% of execution time), Thread Latency (% of execution time), and Last-level Cache Miss Ratio of *equake* when executed with *facesim*.

ration. Therefore, the trade-off between lock times, last level cache miss ratio, and thread latency results in the processor-set configuration delivering better performance.

Figure 1.5: Lock Time (% of execution time), Thread latency (% of execution time), and Last-level Cache Miss Ratio of bodytrack when executed with applu.

Therefore, for effective coscheduling of multithreaded programs, cores must be allocated adaptively according to the resource-usage characteristics of the multithreaded programs being run simultaneously. To address this problem, this dissertation presents

a runtime technique called ADAPT. It uses supervised learning techniques for predicting the effects of interference between programs on their performance and adaptively schedules together programs that interfere with each other's performance as little as possible. It achieves high throughput, high system utilization, and fairness when running multiple multithreaded applications.

### 1.2 Dissertation Organization

The contents of this dissertation are organized as follows. Chapter 2 describes the *Thread Reinforcer* for dynamically determining appropriate number of threads for a multithreaded application. Chapter 3 presents the *Thread Tranquilizer* to select appropriate memory allocation and scheduling policies according to the resource-usage characteristics of multithreaded applications. Chapter 4 describes the *Thread Shuffling* technique to minimize lock acquisition latencies of threads of a multithreaded application running on ccNUMA multicore system. Chapter 5 presents the *Faithful Scheduling* to reduce lock holder thread preemptions. In chapter 6, the technique ADAPT, for coscheduling multiple multithreaded applications is described. Related work is given in Chapter 7 and the conclusions of the dissertation are summarized in Chapter 8.

## Chapter 2

## Determining Number of Threads

The performance of a multithreaded program running on a multicore system is sensitive to the number of threads used to run the multithreaded program (i.e., the threads configuration), as it impacts the application's resource-usage characteristics. Using too few threads leads to under exploitation of parallelism in the application and using too many threads degrades application performance because of lock-contention and contention of shared resources. One simple method for finding the appropriate number of threads is to run the application with different number of threads and find the number of threads that gives the best performance. However, this is time-consuming, does not work if the number of threads is input dependent, does not adapt to the system's dynamic behavior, and therefore is not a practical solution. An attractive alternative technique for solving this problem is to dynamically determine the suitable number of threads for running a multithreaded program on a multicore system. This dissertation presents such a technique called Thread Reinforcer.

### 2.1 Identifying Important Performance Limiting Factors

Dynamically finding a suitable number of threads for a multithreaded program running on a multicore system is a challenging problem because it requires identifying important application characteristics. Therefore, first a performance study of eight PARSEC programs for different numbers of threads ranging from a few threads to 128 threads was conducted. Table 2.1 shows the maximum speedup (Max Speedup) for each program on the 24-core machine along with the minimum number of threads (called OPT Threads) that produced this speedup. As shown in Table 2.1, not only does the maximum speedup achieved by these programs vary widely (from 3.6x for canneal to 21.9x for swaptions), the number of threads that produce maximum speedups also varies widely (from 16 threads for facesim to 63 threads for ferret). Moreover, for the first five programs the maximum speedup results from creating more threads than the number of cores, i.e. OPT-Threads is greater than 24. For the other three programs OPT-Threads is less than the number of cores.

The above performance study shows that the number of threads used to run a multithreaded application is crucial in achieving high performance on a multicore system. Next, using the *prstat* [2] utility, the following main components of the execution times for threads in each application are considered to help identify the performance limiting factors.

- 1. User: The percentage of time a thread spends in user mode.

- 2. System: The percentage of time a thread spends in processing the following system events: system calls, system traps, text page faults, and data page faults.

Table 2.1: Maximum speedups observed and corresponding number of threads for PARSEC programs on the 24-core machine.

| Program        | Max Speedup | OPT Threads |

|----------------|-------------|-------------|

| swaptions      | 21.9        | 33          |

| ferret         | 14.1        | 63          |

| bodytrack      | 11.4        | 26          |

| blackscholes   | 4.9         | 33          |

| canneal        | 3.6         | 41          |

| fluidanimate   | 12.7        | 21          |

| facesim        | 4.9         | 16          |

| stream cluster | 4.2         | 17          |

- 3. Lock-contention: The percentage of time a thread spends waiting for locks, condition-variables etc.

- 4. **Latency**: The percentage of time a thread spends waiting for a CPU. In other words, although the thread is ready to run, it is not scheduled on any core.

Next, the above times for all threads are studied to see if changes in these times would explain the changes in speedups observed by varying number of threads. Although the data for all threads was examined, it quickly became apparent that in many programs not all threads were critical to the overall speedup. Based on this study, *critical threads* were identified and then studied in greater detail. The critical threads for each application are

| Program       | Critical Threads   |

|---------------|--------------------|

| ferret        | Rank stage Threads |

| canneal       | Main Thread        |

| swaptions     | Worker Threads     |

| blackscholes  | Main Thread        |

| bodytrack     | All Threads        |

| fluid animate | Worker Threads     |

| streamcluster | Worker Threads     |

| facesim       | All Threads        |

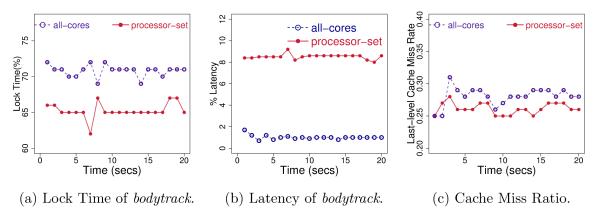

Figure 2.1: Breakdown of elapsed time of critical threads.

listed in the table below. Figure 2.1 provides the breakdown of the time of critical threads in the above four categories – this data is for the OPT-Threads run and is the average across all critical threads. As shown in Figure 2.1, in some programs lock time (LCK) plays a critical role, in others the threads spend significant time waiting for a CPU as latency (LAT) is high, and the system time (SYS) is the highest for *canneal* and *blackscholes*.

In the subsequent sections the above times for each of the programs are analyzed in greater detail to study their relationship with speedup variations that are observed when number of threads is varied. Furthermore, the program characteristics that are the causes for the observed speedup variations are identified.

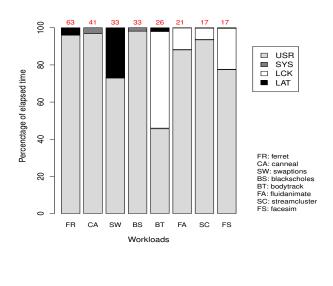

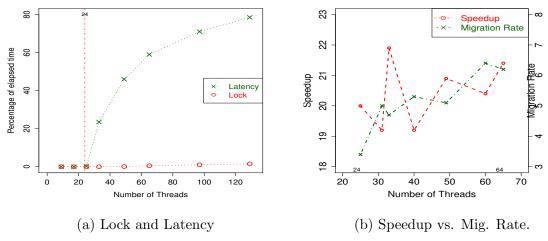

Figure 2.2: Speedup behavior of PARSEC workloads for varying number of threads: the graph on the left shows the behavior of applications where maximum speedup was observed for  $Number\ of\ Threads > Number\ of\ Cores = 24$ ; and the graph on the right shows the behavior of applications where maximum speedup was observed for  $Number\ of\ Threads < Number\ of\ Cores = 24$ .

#### 2.1.1 OPT-Threads > Number of Cores:

Scalable Performance. As shown in the graph on the left in Figure 2.2, for the three programs (swaptions, bodytrack, and ferret) in this category, the speedups scale quite well. As the number of threads is varied from a few threads to around 24, which is the number of cores, the speedup increases linearly with the number of threads. However, once the number of threads is increased further, the three programs exhibit different trends as described below:

• (Erratic) swaptions: Although the speedup for swaptions can be significantly increased

-- from 20 for 25 threads to 21.9 for 33 threads -- its trend is erratic. Sometimes the

addition of more threads increases the speedup while at other times an increase in

number of threads reduces the speedup.

- (Steady Decline) bodytrack: The speedup for bodytrack decreases as the number of threads is increased beyond 26 threads. The decline in speedup is quite steady.

- (Continued Increase) ferret: The speedup for ferret continues to increase linearly. In fact the linear increase in speedup is observed from the minimum number of 6 threads all the way up till 63 threads. Interestingly no change in behavior is observed when the number of threads is increased from less than the number of cores to more than the number of cores.

Next the differing behaviors are traced back to specific characteristics of these programs.

swaptions: To understand the erratic behavior of speedups observed in swaptions, first the lock contention and latency information are examined. As shown in Figure 2.3(a), the lock contention (LOCK) is very low and remains very low throughout and the latency (LAT) increases steadily which shows that the additional threads created are ready to run but are simply waiting for a CPU (core) to become available. This causes the execution time to remain the same. However, upon further analysis, the correlation between the speedup behavior and thread migration rate was identified as the reason behind the erratic behavior of speedups observed in swaptions. As shown in Figure 2.3(b), when the migration rate goes up, the speedup goes down and vice versa – the migration rate was measured using the mpstat [2] utility. Migrations are expensive events as they cause a thread to pull its working set into cold caches, often at the expense of other threads [2]. Thus, the speedup

behavior is a direct consequence of changes in thread migration rate.

Figure 2.3: swaptions: Cause of Erratic Speedup Changes.

The OS scheduler plays a significant role here as it is responsible for making migration decisions. When a thread makes a transition from sleep state to a ready-to-run state, if the core on which it last ran is not available, the thread is likely to be migrated to another available core. In general, one would expect more migrations as the number of threads increases beyond the number of cores. However, if the number of threads is divisible by the number of cores, then the likelihood of migrations is less compared to when this is not the case. In the former case, the OS scheduler can allocate equal number of threads to each core, balancing the load, and thus reducing the need for migrations. Thus, variations in degree of load balancing across cores causes corresponding variations in thread migration rate and hence the observed speedups. For example, in Figure 2.3(b), the thread migration rate for 48 threads on 24 cores is lower than thread migration rate for 40 threads on 24 cores. Moreover, low thread migration rate can be expected when the input load (128 swaptions) is perfectly divisible by the number of threads (e.g., 16, 32, 64 etc.).

bodytrack: Next consider the steady decline in speedup observed for bodytrack. Figure 2.4(a) shows that although the latency (LAT) rises as more threads are created, so does the lock contention (LOCK) which is significant for bodytrack. In addition, bodytrack is an I/O intensive benchmark where I/O is performed by all the threads and it produces around 350 ioctl() calls per second. Both lock contention and I/O have the consequence of increasing the thread migration rate. This is because both lock contention and I/O result in sleep to wakeup and run to sleep state transitions for the threads involved. When a thread wakes up from the sleep state, the OS scheduler immediately tries to give a core to that thread, if it fails to schedule the thread on the same core that it used last, it migrates the thread to another core. As shown in Figure 2.4(b), the thread migration rate for bodytrack rises with the number of threads which causes a steady decline in its speedup.

Figure 2.4: bodytrack: Cause of Decline in Speedup.

ferret: The behavior of this program is interesting as the speedup for it increases linearly starting from 6 threads to all the way up to 63 threads even though only 24 cores are available. To understand this behavior the program was examined in greater detail. The program is divided into six pipeline stages – the results of processing in one stage are

passed on to the next stage. The stages are: Load, Segment, Extract, Vector, Rank, and Out. The first and last stage have a single thread but each of the intermediate stages are a pool of n threads. Between each pair of consecutive stages a queue is provided through which results are communicated and locking is used to control queues accesses.

The reason for the observed behavior is as follows. The Rank stage performs most of the work and thus the speedup of the application is determined by the Rank stage. Moreover the other stages perform relatively little work and thus their threads together use only a fraction of the compute power of the available cores. Thus, as long as cores are not sufficiently utilized, more speedup can be obtained by creating additional threads for the Rank stage. The maximum speedup of 14.1 for ferret was observed when the total number of threads created was 63 which actually corresponds to 15 threads for Rank stage. That is, the linear rise in speedup is observed from 1 thread to 15 threads for the Rank stage which is well under the total of 24 cores available – the remaining cores are sufficient to satisfy the needs of all other threads.

The justification of the above reasoning can be found in the data presented in Table 2.2 where the average percentage of USR and LOCK times for all stages and SYS time for only Load stage are shown because all other times are quite small. The threads belonging to Segment, Extract, and Out stages perform very little work and mostly spend their time waiting for results to become available in their incoming queues. While the Load and Vector stages do perform significant amount of work, they nevertheless perform less work than the Rank stage. The performance of the Rank stage determines the overall speedup – adding additional threads to the Rank stage continues to yield additional speedups

Table 2.2: Behavior of ferret.

| Total   | n  |     | Load (1 | l)   | Segn | ent (n) | Extr | act (n) | Vect | or (n) | Rai  | nk (n) | Ou  | t (1) | Speedup |

|---------|----|-----|---------|------|------|---------|------|---------|------|--------|------|--------|-----|-------|---------|

| Threads |    | USR | SYS     | LOCK | USR  | LOCK    | USR  | LOCK    | USR  | LOCK   | USR  | LOCK   | USR | LOCK  |         |

| 15      | 3  | 22  | 4       | 74   | 8    | 92      | 1    | 99      | 44   | 56     | 100  | 0      | 0.5 | 99.3  | 3.3     |

| 31      | 7  | 44  | 7.8     | 48   | 6.7  | 93      | 1    | 99      | 43   | 57     | 100  | 0      | 0.6 | 99    | 7.5     |

| 47      | 11 | 56  | 11.3    | 32   | 5.4  | 95      | 1    | 99      | 40   | 60     | 100  | 0      | 0.7 | 99    | 11.5    |

| 55      | 13 | 64  | 14      | 19   | 5    | 95      | 1    | 99      | 44   | 56     | 98   | 0      | 0.7 | 99    | 12.5    |

| 63      | 15 | 79  | 20      | 0    | 5    | 95      | 1    | 99      | 43   | 57     | 96   | 0      | 0.7 | 99    | 14.1    |

| 71      | 17 | 77  | 20      | 0    | 5    | 95      | 1    | 99      | 37   | 63     | 80   | 16     | 0.7 | 99    | 13.8    |

| 87      | 21 | 78  | 17      | 0    | 4    | 96      | 1    | 99      | 28   | 72     | 65   | 33     | 0.4 | 99.3  | 13.7    |

| 103     | 25 | 75  | 17      | 0    | 3    | 97      | 1    | 99      | 24   | 76     | 53.5 | 45     | 0.4 | 99.3  | 13.4    |

| 119     | 29 | 74  | 17      | 0    | 3    | 97      | 1    | 99      | 20   | 80     | 46   | 52.5   | 0.4 | 99.4  | 13.2    |

| 127     | 31 | 70  | 20      | 0    | 3    | 97      | 1    | 99      | 19   | 81     | 40   | 59     | 0.4 | 99.4  | 13.1    |

as long as this stage does not experience lock contention. Once lock contention times start to rise (starting at n = 17), the speedup begins to fall.

To further confirm the above observations, the number of threads in the *Rank* stage were increased and the number of threads in other intermediate stages was lowered. While the configuration with (1, 10, 10, 10, 16, 1) threads gave a speedup of 13.9, the configuration with (1, 16, 16, 16, 16, 1) threads gave the same the speedup. This further confirms the importance of the *Rank* stage.

Performance Does Not Scale. (blackscholes and canneal) Although the maximum speedups of these programs (4.9 and 3.6) are observed when 32 and 40 worker threads are created, the speedups of both these programs increase very little beyond 16 worker threads. This is because most of the work is performed by the main thread causing the overall CPU utilization to become low. The main thread takes up 85% and 70% of the time for blackscholes and canneal respectively. During rest of the time the parallelized part of the program is executed by worker threads. The impact of parallelization of this limited part on the overall speedup diminishes with increasing number of threads.

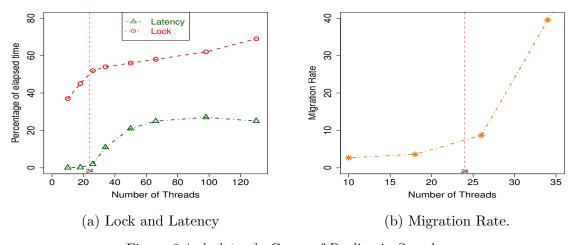

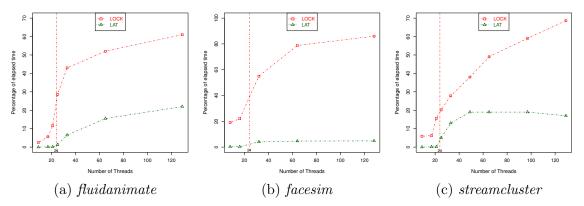

### 2.1.2 OPT-Threads < Number of Cores

The three programs where maximum speedup was achieved using fewer threads than number of cores are *fluidanimate*, *facesim*, and *streamcluster*. In these programs the key factor that limits performance is lock contention. Figure 2.5 shows that the time due to lock contention (LOCK) dramatically increases with number of threads while the latency (LAT) shows modest or no increase. The maximum speedups are observed at 21 threads for *fluidanimate*, 16 threads for *facesim*, and 17 threads for *streamcluster*.

Figure 2.5: Maximum Speedup When Number of Threads < Number of Cores.

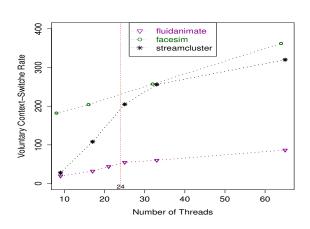

When the number of threads is less than the number of cores, the load balancing task of the OS scheduler becomes simple and thread migrations become rare. Thus, unlike *swaptions* and *bodytrack* where maximum speedups were observed for greater than 24 threads, thread migration rate does not play any role in the performance of the three programs considered in this section. However, the increased lock contention leads to slow-downs because of increased *context switch rate*. Context-switches are divided into two types: involuntary context-switches (ICX) and voluntary context-switches (VCX). Involuntary context-switches occur when threads are involuntarily taken off a core (e.g., due to

expiration of their time quantum). Voluntary context-switches occur when a thread performs a blocking system call (e.g., for I/O) or when it fails to acquire a lock. In such cases a thread voluntarily releases the core using the yield() system call before going to sleep using  $lwp\_park()$  system call. Therefore as more threads are created and lock contention increases, VCX context switch rate rises as shown in Figure 2.6. It is also worth noting that most of the context switches performed by the three programs are in the VCX category. The VCX and ICX data are measured using the prstat utility. Figure 2.7 shows that the percentage of VCX ranges from 84% to 97% for the three programs considered here. In contrast, the VCX represents only 11% and 13% of context switches for swaptions and ferret.

| Program        | VCX (%) | ICX (%) |

|----------------|---------|---------|

| fluidanimate   | 84      | 16      |

| facesim        | 97      | 3       |

| stream cluster | 94      | 6       |

| swaptions      | 11      | 89      |

| ferret         | 13      | 87      |

Figure 2.6: Voluntary Context Switch Rate.

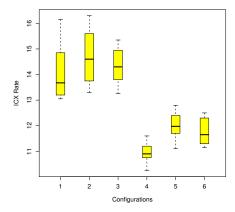

Figure 2.7: VCX vs. ICX.

From the above scalability analysis of PARSEC programs, it is clear that the speedup behavior of an application correlates with variations in lock time (LOCK), migration rate (MIGR\_RATE), voluntary context-switch rate (VCX\_RATE), and CPU utilization (CPU\_UTIL). Moreover, the relationship between above factors and the number of threads

from the above scalability analysis is also derived. Table 2.3 shows the factors that play an important role when the number of threads is no more than the number of cores (i.e., 24) versus when the number of threads is greater than the number of cores. The lock contention is an important factor which must be considered throughout. However, for  $\leq$  24 threads the voluntary context-switch rate is important while for > 24 threads the thread migration rate is important to consider. In general, the limit of parallelism for a program may reach at any time. Therefore the degree of parallelism (CPU utilization) is an important factor to consider throughout. The above observations are a direct consequence of our observations made during the study presented earlier.

Table 2.3: Factors considered wrt to the number of threads.

| Factor                     | $\leq$ 24 Threads | > 24 Threads |

|----------------------------|-------------------|--------------|

| Lock-contention            | Yes               | Yes          |

| Voluntary Context-switches | Yes               | -            |

| Migrations                 | -                 | Yes          |

| Degree of parallelism      | Yes               | Yes          |

Thus, *Thread Reinforcer* monitors the above characteristics for dynamically determining a suitable number of threads for a multithreaded application.

### 2.2 The Thread Reinforcer Framework

The applications considered allow the user to control the number of threads created using the command line argument n. Since our experiments show that the number of threads

that yield peak performance varies greatly from one program to another, the selection of n places an added burden on the user. Therefore, in this section, a framework for automatically selecting the number of threads is developed.

The framework runs the application in two steps. In the first step the application is run multiple times for short durations of time during which its behavior is monitored and based upon runtime observations Thread Reinforcer searches for the appropriate number of threads. Once this number is found, in the second step, the application is fully reexecuted with the number of threads determined in the first step. Since the applications do not support varying number of threads online, they need to be rerun for short durations. Thus, Thread Reinforcer does not consider phase changes of the target program. However, out of the 16 programs tested, only the *ammp* program shows two significantly different phases and its first phase dominates the execution. Therefore Thread Reinforcer works well also for the *ammp* program.

Each time an application is to be executed on a new input, Thread Reinforcer is used to determine the appropriate number of threads for that input. This is done in order to handle applications whose runtime behavior is input dependant and thus the optimal number of threads may vary across inputs. Our goal is twofold: to find the appropriate number of threads and to do so quickly so as to minimize runtime overhead. Since the applications considered take from tens of seconds to a few hundred seconds to execute in the OPT-Threads configuration, Thread Reinforcer is designed in such a way that the times it takes to search for appropriate number of threads is only a few seconds. This ensures that the benefits of the algorithm outweigh the runtime overhead of using it.

#### 2.2.1 Algorithm

Based on the above observations, Thread Reinforcer searches for appropriate number of threads in the range of  $T_{min}$  and  $T_{max}$  threads as follows. It runs the application for increasing number of threads for short time durations. Each successive run contains either  $T_{step}$  or  $T_{step}/2$  additional threads. The decision of whether or not to run the program for higher number of threads and whether to increase the number of threads by  $T_{step}$  or  $T_{step}/2$ , is based upon changes in profiles observed over the past two runs. The profile consists of the four factors: lock contention, thread migration rate, voluntary context switch rate, and the degree of parallelism (processor utilization). The values of each of these measures are characterized as either low or high based upon set thresholds for these parameters. Our algorithm not only examines the current values of above profiles, it also examines how rapidly they are changing. The changes of these values over the past two runs are denoted as  $\Delta Lock$ contention,  $\Delta$ Migration-rate,  $\Delta$ Voluntary-context-switch-rate, and  $\Delta$ CPU-utilization. The changes are also characterized as low and high to indicate whether the change is gradual or rapid. At any point in the penultimate run represents the current best solution of our algorithm and the last run is compared with the previous run to see if it should be viewed as an improvement over the penultimate run. If it is considered to be an improvement, then the last run becomes our current best solution. Based upon the strength of improvement, the program is run with  $T_{step}$  or  $T_{step}/2$  additional threads. The above process continues as long as improvement is observed. Eventually Thread Reinforcer terminates if no improvement or degradation is observed, or the maximum number of threads  $T_{max}$  is reached.

Algorithm 1 presents Thread Reinforcer in detail. Thread Reinforcer is initiated

#### **Algorithm 1: FindN()** returns the best value for command line parameter.

```

Thresholds and Profile Data Structure:

```

- -- Profile P: (CPU\_UTIL, LOCK, VCX\_RATE, MIGR\_RATE);

- --  $(T_{best}, N_{best})$  is the current best solution;  $P_{best}$  is its profile;

- --  $(T_{try}, N_{try})$  is the next solution tried;  $P_{try}$  is its profile;

- --  $\Delta$  P.field =  $P_{try}$ .field  $P_{best}$ .field;

- -- low returns true/false if P.field or  $\Delta$  P.field is low/not low;

- -- high returns true/false if P.field or  $\Delta$  P.field is high/not high;

- --  $T_{step}$  is increments in which number of threads is increased;

- --  $T_{min}/T_{max}$  is minimum/maximum number of threads allowed;

#### Subroutines:

- -- Convert(T): converts number of threads T into command-line parameter value N;

- -- getProfile(N): collect profile P for 100 milliseconds run with parameter N;

#### Input : Target Multithreaded Benchmark Program

Output: Returns command-line parameter corresponding to the optimal number of threads

```

\begin{split} T_{best} &= T_{min}; \, N_{best} = \operatorname{Convert}(T_{best}); P_{best} = \operatorname{getProfile}(N_{best}); \\ T_{try} &= T_{min} \, + \, T_{step}; \, N_{try} = \operatorname{Convert}(T_{try}); P_{try} = \operatorname{getProfile}(N_{try}); \\ \text{if } Terminate(P_{best}, P_{try}) &== TRUE \text{ then} \\ &\mid \text{ return } (N_{best}); \end{split}

```

## end

#### repeat

```

T_{best} = T_{try}; N_{best} = N_{try}; P_{best} = P_{try};

T_{try} = \text{ComputeNextT}(P_{best}, P_{try});

N_{try} = \text{Convert}(T_{try});

P_{try} = \text{getProfile}(N_{try});

\text{terminate} = \text{Terminate}(P_{best}, P_{try});

\text{until terminate} = TRUE;

```

return  $(N_{best});$

## Algorithm 1: FindN() continued

```

Terminate(P_{best}, P_{try}):

```

```

// terminate if no more parallelism was found.

if low(P_{try}.\Delta \mathit{CPU\_UTIL}) then

return (TRUE);

\ensuremath{//} terminate for high lock contention, VCX rate, and migration rate.

else if high(P_{try}.LOCK) then

if high(P_{try}.\Delta LOCK) or (T_{try} \leq NumCores \ {\bf and} \ high(P_{try}.\Delta VCX\_RATE)) or (T_{try} > 1)

NumCores and high(P_{try}.\Delta\ MIGR\_RATE)) then

return (TRUE);

\mathbf{end}

// terminate if no more threads can be created.

else if T_{try} == T_{max} then

T_{best} = T_{try} \; ; \, N_{best} = N_{try} ;

\mathbf{return}\ (\mathrm{TRUE});

// otherwise do not terminate.

else

return (FLASE);

end

```

#### Algorithm 1: FindN() continued

### ComputeNextT( $P_{best}$ , $P_try$ ):

```

\begin{array}{l} \text{if } T_{try} \leq \textit{NumCores then} \\ & \text{if } low(P_{try}.LOCK) \text{ or } low(P_{try}.\Delta \textit{VCX\_RATE}) \text{ or } (high(P_{try}.LOCK) \text{ and} \\ & low(P_{try}.\Delta LOCK)) \text{ then} \\ & & \Delta T = T_{step}; \\ & \text{else} \\ & & \Delta T = (T_{step})/2; \\ & \text{end} \\ & \text{else} \\ & & \Delta T = T_{step}; \\ & \text{else} \\ & & \Delta T = T_{step}; \\ & \text{else} \\ & & \Delta T = T_{step}; \\ & \text{else} \\ & & \Delta T = (T_{step})/2; \\ & \text{end} \\ & \text{end} \\ & \text{end} \\ & \text{return } (\text{minimum}(T_{try} + \Delta T, T_{max}); \end{array}

```

by calling FindN() and when it terminates it returns the value of command like parameter n that is closest to the number of threads that are expected to give the best performance. FindN() is iterative – it checks for termination by calling Terminate() and if termination conditions are not met, it calls ComputeNextT() to find out the number of threads that must be used in the next run. Consider the code for Terminate(). It first checks if processor utilization has increased from the penultimate run to the last run. If this is not the case then the algorithm terminates otherwise the lock contention is examined for termination. If lock contention is high then termination occurs if one of the following is true: lock contention has increased significantly; number of threads is no more than the number of cores and

voluntary context switch rate has sharply increased; or number of threads is greater than the number of cores and thread migration rate has sharply increased. Finally, the algorithm is not terminated if the above termination condition is not met. However, it is terminated if the upper limit for number of threads is reached. Before iterating another step, the number of additional threads to be created is determined. ComputeNextT() does this task – if the overheads of locking, context switches, or migration rate increase slowly then  $T_{step}$  additional threads are created; otherwise  $T_{step}/2$  additional threads are created.

Next section presents evaluation of *Thread Reinforcer* against PARSEC and SPEC OMP programs. However, before experimentation, the various thresholds used by Thread Reinforcer need to be selected.

#### 2.2.2 Finding Thresholds

Three of the eight programs: fluidanimate, facesim, and blackscholes to guide the selection of thresholds. These selected programs were run with small inputs: for fluidanimate and blackscholes, the simlarge input is used and for facesim the simsmall input is used. Next, the profiles of the programs are studied and the threshold values for LOCK, MIGR\_RATE, VCX\_RATE, CPU\_UTIL are identified as follows. The threshold values were chosen such that after reaching the threshold value, the value of the profile characteristic became more sensitive to the number of threads and showed a rapid increase. There are two types of threshold values: absolute thresholds and  $\Delta$  thresholds. The  $\Delta$  threshold indicates how rapidly the corresponding characteristic is changing. For LOCK and VCX\_RATE both thresholds are used by our algorithm. For MIGR\_RATE and CPU\_UTIL only  $\Delta$  threshold

is used. It should be noted that the three programs that were chosen to help in selection of thresholds collectively cover all four of the profile characteristics: for *fluidanimate* both LOCK and MIGR\_RATE are important; for *facesim* VCX\_RATE is important; and for *blackscholes* CPU\_UTIL is important.

## 2.3 Evaluating Thread Reinforcer

First Thread Reinforcer is evaluated against PARSEC programs. Table 2.4 presents the number of threads found by Thread Reinforcer and compares it with the OPT-Threads number that was reported earlier in Table 2.1. The corresponding speedups for these number of threads are also reported. As shown in Table 2.4, for the first four programs (facesim, bodytrack, swaptions, ferret) the number of threads found by our algorithm is exactly the same as OPT-Threads. For the next two programs, fluidanimate and streamcluster, the numbers are close as they differ by  $T_{step}/2(=4)$  and  $T_{step}(=8)$  respectively. The loss in speedups due to this suboptimal choice of the number of threads in quite small. For the last two programs, canneal and blackscholes, the number of threads Thread Reinforcer selects is much smaller than OPT-Threads. This is because the speedup of these programs rises very slowly and thus the change in CPU-utilization is quite low. The search overhead varies from 0.5 seconds to 3.2 seconds while the parallel execution times of the programs range from 21.9 seconds to 226 seconds.

Since Thread Reinforcer uses the thresholds of PARSEC programs, Thread Reinforcer is evaluated against programs other than PARSEC. For this, Thread Reinforcer is tested against seven SPEC OMP programs and PBZIP2 program, a total of eight other

programs. As shown in Table 2.5, Thread Reinforcer identifies optimal or near optimal number of threads for most of these programs. Moreover, the search overhead is very low compared to the parallel execution-time of the programs. Tables 2.6 and 2.7 show this.

Table 2.4: Algorithm vs. Optimal (PARSEC programs).

| Program        | Number o  | f Threads | Speed     | lups    |

|----------------|-----------|-----------|-----------|---------|

|                | Algorithm | Optimal   | Algorithm | Optimal |

| facesim        | 16        | 16        | 4.9       | 4.9     |

| bodytrack      | 26        | 26        | 11.4      | 11.4    |

| swaptions      | 33        | 33        | 21.9      | 21.9    |

| ferret         | 63        | 63        | 14.1      | 14.1    |

| fluidanimate   | 25        | 21        | 12.2      | 12.7    |

| stream cluster | 25        | 17        | 4.0       | 4.2     |

| canneal        | 9         | 41        | 2.9       | 3.6     |

| blackscholes   | 9         | 33        | 3.7       | 4.9     |

## 2.4 Summary

This chapter presented a runtime technique, Thread Reinforcer, to dynamically determine the suitable number of threads for a multithreaded application for achieving high performance on a multicore system. Thread Reinforcer monitors performance limiting factors degree of parallelism, lock contention, thread migrations and context-switches at runtime using simple utilities available on modern OS for determining appropriate number of threads that are expected to yield the best speedup. Thread Reinforcer identifies optimal

or near optimal number of threads for most of the PARSEC programs studied and as well as for SPEC OMP and PBZIP2 programs.

Table 2.5: Algorithm vs. Optimal (Other programs).

| Program | Number o  | f Threads | Speed     | lups    |

|---------|-----------|-----------|-----------|---------|

|         | Algorithm | Optimal   | Algorithm | Optimal |

| ammp    | 24        | 24        | 11.8      | 11.8    |

| art     | 32        | 32        | 8.8       | 8.8     |

| fma3d   | 16        | 20        | 5.5       | 5.7     |

| gafort  | 64        | 48        | 9.7       | 9.8     |

| mgrid   | 16        | 16        | 5.0       | 5.0     |

| swim    | 32        | 24        | 3.9       | 4.0     |

| wupwise | 24        | 24        | 8.6       | 8.6     |

| pbzip2  | 24        | 28        | 6.7       | 6.9     |

Table 2.6: Search Overhead (seconds) for PARSEC programs.

| Program        | $T_{search}$ | $T_{parallel}$ | Percentage |

|----------------|--------------|----------------|------------|

| canneal        | 0.5          | 131            | 0.4%       |

| facesim        | 1.1          | 186            | 0.6%       |

| blackscholes   | 0.5          | 85             | 0.6%       |

| stream cluster | 3.2          | 226            | 1.4%       |

| fluidanimate   | 1.5          | 69             | 2.2%       |

| ferret         | 1.3          | 41.9           | 3.1%       |

| bodytrack      | 1.6          | 43.8           | 3.7%       |

| swaptions      | 0.9          | 21.3           | 4.2%       |