## **UC Riverside**

## **UC Riverside Electronic Theses and Dissertations**

### **Title**

Improving Performance and Energy Efficiency of GPUs through Locality Analysis

## **Permalink**

https://escholarship.org/uc/item/9gp7781h

### **Author**

Tripathy, Devashree

## **Publication Date**

2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

Improving Performance and Energy Efficiency of GPUs through Locality Analysis

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Devashree Tripathy

September 2021

### Dissertation Committee:

Prof. Laxmi Bhuyan, Chairperson

Prof. Nael Abu-Ghazaleh

Prof. Zizhong Chen

Prof. Daniel Wong

University of California, Riverside

## Acknowledgments

Finishing this dissertation marks the end of a major chapter of my life and the beginning of a new innings. I thank you all from the bottom of my heart, for your unquestionable support, continuous encouragement and endless patience, that helped me navigate my PhD Journey.

First of all, I would like to thank my advisor, Dr. Laxmi Bhuyan for believing in me and granting me the freedom to pursue the research projects. His technical, editorial and general advice, and mentoring was pivotal in the completion of the dissertation. I would also like to thank my dissertation committee members, Dr. Daniel Wong for his support and endless help in my research, Dr. Zizhong Chen and Dr. Nael Abu-Ghazaleh for their support and guidance as this dissertation shaped from a proposal to a complete study. Their constructive feedback has helped me immensely to improve the quality of this dissertation.

Next, I would like to thank my amazing collaborators, Dr. Manoranjan Satpathy, Amirali Abdolrashidi, Hadi Zamani Sabzi and Debiprasanna Sahoo. Especially, Amirali for listening to my crazy ideas and improvising those, brainstorming with me, Bashar for standing by me through thick and thin, and Debiprasanna for collaborating and mentoring me on various occasions. I would like to thank all the professors, mentors, co-workers, teachers, students, friends in my life for being there for me and believing in me. I thank my labmates and fellow graduate researchers: Hadi Zamani Sabzi, Liang Zhou, Mehmet Esat Belviranli, Chih-hsun Chou, Keval Vora, Amlan Kusum, Quan Fan, Rameswar Panda, Anguluri Rajasekhar, Kiran Ranganathan, Marcus Chow, Ali Jahanshahi, Sourav Panda, Madhurima Chakraborty and Chengshuo Xu (Bruce).

Finally, most importantly, I would like to express my gratitude towards my family for their unconditional support during my pursuit of this arduous journey. Especially, I thank my parents, Dr.Chitaranjan Tripathy and Minakshi Tripathy for providing me a strong education foundation to begin with and rowing the seeds of research aptitude since childhood, my brother, Nachiket Tripathy for always motivating me, my in-laws, for their love, support and encouragement, last but not the least, thanks to my best friend and my dear husband Bibek Mishra without whose unconditional love and support this dissertation would not have been possible. He actually underwent this journey along with me by my side, and sometimes was a part of it more than me. He not only encouraged me to think out of the box and aim for the best in life, but also stayed committed to the PhD process with me till the end, by putting up with my countless work-hours and keeping me focused on the priorities when I had too many things on my plate.

This dissertation includes content published in the following proceedings:

- 1. **Devashree Tripathy**, Amirali Abdolrashidi, Laxmi Narayan Bhuyan, Liang Zhou, and Daniel Wong. "Paver: Locality graph-based thread block scheduling for gpus." ACM Transactions on Architecture and Code Optimization (TACO), June 2021.

- 2. **Devashree Tripathy**, Amirali Abdolrashidi, Quan Fan, Daniel Wong and Manoranjan Satpathy. "LocalityGuru: A PTX Analyzer for Extracting Thread Block-level Locality in GPGPUs." 15th International Conference on Networking, Architecture, and Storage (NAS), October 2021.

- 3. **Devashree Tripathy**, Hadi Zamani Sabzi, Debiprasanna Sahoo, Laxmi Narayan Bhuyan and Manoranjan Satpathy. "Slumber: Static-Power Management for GPGPU Register Files." ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), August 2020.

To all taxpayers who subsidized my education.

#### ABSTRACT OF THE DISSERTATION

Improving Performance and Energy Efficiency of GPUs through Locality Analysis

by

#### Devashree Tripathy

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, September 2021 Prof. Laxmi Bhuyan, Chairperson

The massive parallelism provided by general-purpose GPUs (GPGPUs) possessing numerous compute threads in their streaming multiprocessors (SMs) and enormous memory bandwidths have made them the de-facto accelerator of choice in many scientific domains. To support the complex memory access patterns of applications, GPGPUs have a multi-level memory hierarchy consisting of a huge register file and an L1 data cache private to each SM, a banked shared L2 cache connected through an interconnection network across all SMs and high-bandwidth banked DRAM. With the amount of parallelism GPUs can provide, memory traffic becomes a major bottleneck, mostly due to the small amount of private cache that can be allocated for each thread, and the constant demand of data from the GPU's many computation cores. This results in under-utilization of many SM components like register file, thereby incurring sizable overhead in the GPU power consumption due to wasted static energy of the registers. The aim of this dissertation is to develop techniques that can boost the performance in spite of small caches and improve power management techniques to boost energy saving.

In our first technique, we present *PAVER*, a priority-aware vertex scheduler, which takes a graph-theoretic approach towards thread-block (TB) scheduling. We analyze the cache locality behavior among TBs and represent the problem using a graph representing the TBs and the locality among them. This graph will then be partitioned to TB groups that display maximum data sharing and assigned to the same SM by the locality-aware TB scheduler. This novel technique also reduces the leakage and dynamic access power of the L2 caches, while improving the overall performance of the GPU.

In our second study, *Locality Guru*, we seek to employ the JIT analysis to find the data-locality between structures at various granularity such as threads, warps and TBs in a GPU Kernel using the load register's address tracing through a syntax tree. This information can help make smarter decisions for a locality aware data-partition and scheduling in single and multi-GPUs.

In the previous techniques, we gained performance benefit by exploiting the datalocality in the GPUs, which eventually translates to static energy saving in the whole GPU. Next, we analyze the static energy saving of the storage structures like L1 and L2 caches by directly applying power management techniques to save power during the time they are idle.

Finally, we develop, *Slumber*, a realistic model for determining the wake-up time of registers from various under-volting and power gating modes. We propose a hybrid energy saving technique where a combination of power-gating and under-volting can be used to save optimum energy in the register file depending on the idle period of the registers with a negligible performance penalty.

# Contents

| Li | st of        | Figures                                                    | xiii |  |  |

|----|--------------|------------------------------------------------------------|------|--|--|

| Li | st of        | Tables                                                     | xvi  |  |  |

| 1  | Intr         | roduction                                                  | 1    |  |  |

|    | 1.1          | Data-Locality Aware Thread Block Scheduler                 | 3    |  |  |

|    | 1.2          | A PTX Analyzer to Extract TB Level Locality                | 6    |  |  |

|    | 1.3          | Static-Power Management for the Caches                     | 8    |  |  |

|    | 1.4          | A Static-Power Management Technique for the Register Files | 10   |  |  |

|    | 1.5          | Dissertation Organization                                  | 12   |  |  |

| 2  | Related Work |                                                            |      |  |  |

|    | 2.1          | CPU Cache Locality                                         | 13   |  |  |

|    | 2.2          | GPU Cache Locality                                         | 15   |  |  |

|    |              | 2.2.1 Locality aware TB Scheduling                         | 15   |  |  |

|    |              | 2.2.2 Locality aware Warp Scheduling                       | 17   |  |  |

|    | 2.3          | Compiler Assisted Locality Analysis                        | 18   |  |  |

|    | 2.4          | CPU Power Optimization Techniques                          | 20   |  |  |

|    | 2.5          | GPGPU Power Optimization                                   | 21   |  |  |

| 3  | PAV          | VER: Locality Graph-based Thread Block Scheduling for GPUs | 23   |  |  |

|    | 3.1          | Background and Motivation                                  | 24   |  |  |

|    |              | 3.1.1 Baseline GPGPU architecture                          | 25   |  |  |

|    |              | 3.1.2 L1/L2 hit and miss distribution                      | 27   |  |  |

|    | 3.2          | Generating Locality Graphs                                 | 29   |  |  |

|    |              | 3.2.1 PAVER overview                                       | 29   |  |  |

|    |              | 3.2.2 Locality Graph:                                      | 29   |  |  |

|    |              | 3.2.3 Identifying Locality Information                     | 32   |  |  |

|    | 3.3          | PAVER Thread Block (TB) Scheduling                         | 37   |  |  |

|    |              | 3.3.1 Maximum Spanning Tree-based TB Scheduler (MST-TS)    | 37   |  |  |

|    |              | 3.3.2 k-way Partition-based TB Scheduler (Kway-TS)         | 39   |  |  |

|    |              | 3.3.3. Recursive Bi partition-based TR Schedular (RR TS)   | 40   |  |  |

|          | 3.4            | PAVER Runtime                                                                 |

|----------|----------------|-------------------------------------------------------------------------------|

|          |                | 3.4.1 Hardware Implementation                                                 |

|          |                | 3.4.2 Task Stealing                                                           |

|          | 9.5            | 3.4.3 Generalized Runtime Algorithm for all TB Policies                       |

|          | 3.5            | Evaluation                                                                    |

|          |                | 3.5.1 Methodology                                                             |

|          |                | 3.5.2 Benchmarks                                                              |

|          |                | 3.5.3 Results                                                                 |

|          |                | 3.5.4 Speedup Results                                                         |

|          |                | 3.5.5 L1 Misses                                                               |

|          | 3.6            | Conclusion                                                                    |

| 4        | Loc            | alityGuru: A PTX Analyzer for Extracting Thread Block-level Local-            |

|          | ity            | in GPGPUs 59                                                                  |

|          | 4.1            | Background                                                                    |

|          | 4.2            | LocalityGuru                                                                  |

|          |                | 4.2.1 PTX Analysis with Syntax Trees 61                                       |

|          |                | 4.2.2 Syntax Tree Construction                                                |

|          |                | 4.2.3 Locality Graph from Syntax Tree                                         |

|          |                | 4.2.4 Summary                                                                 |

|          | 4.3            | Results and Discussion                                                        |

|          | 1.0            | 4.3.1 Methodology                                                             |

|          |                | 4.3.2 Understanding the Patterns                                              |

|          |                | 4.3.3 Validating the Results                                                  |

|          | 4.4            | Conclusion                                                                    |

|          |                |                                                                               |

| <b>5</b> | $\mathbf{Sno}$ | oze: Cache Leakage Energy Management in GPGPUs 75                             |

|          | 5.1            | Background and Motivation                                                     |

|          | 5.2            | Snooze Design                                                                 |

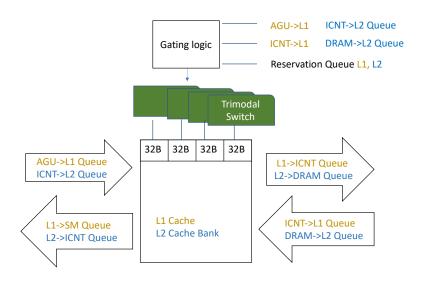

|          |                | 5.2.1 Hardware Support                                                        |

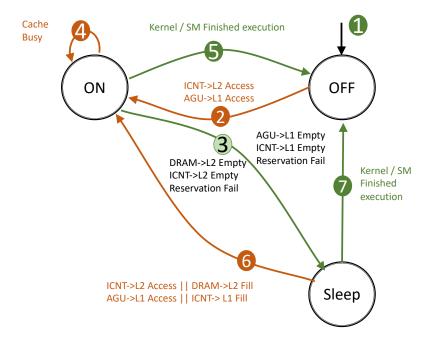

|          |                | 5.2.2 Power Mode Transition                                                   |

|          | 5.3            | Results and Discussion                                                        |

|          |                | 5.3.1 Methodology                                                             |

|          |                | 5.3.2 Energy Savings                                                          |

|          | 5.4            | Conclusion                                                                    |

| 6        | Slin           | mber: Static-Power Management for GPGPU Register Files 91                     |

| U        | 6.1            | Motivation                                                                    |

|          | 0.1            | 6.1.1 Register File Organization                                              |

|          |                | 6.1.2 Conservative wake-up                                                    |

|          |                | 6.1.3 Slumber Overview                                                        |

|          | 6.2            | Static Power Reduction Metrics Estimation                                     |

|          |                |                                                                               |

|          | 6.3            | Slumber Design                                                                |

|          |                | 6.3.1 Compiler-generated Hints                                                |

|          |                | 6.3.2 Power-Gating and Under-volting Opportunities in Register File (RF). 103 |

| Bi | Bibliography |        |                                           |     |  |

|----|--------------|--------|-------------------------------------------|-----|--|

| 7  | Con          | clusio | n and Future Work                         | 113 |  |

|    | 6.5          | Conclu | asion                                     | 112 |  |

|    |              | 6.4.4  | Performance Penalty                       | 112 |  |

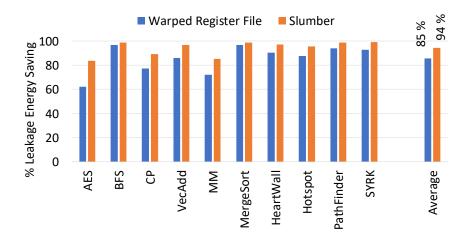

|    |              | 6.4.3  | Leakage energy efficiency improvement     | 111 |  |

|    |              | 6.4.2  | Comparison with Warped Register File [2]  | 110 |  |

|    |              | 6.4.1  | Methodology                               | 110 |  |

|    | 6.4          | Result | s and Discussion                          | 110 |  |

|    |              | 6.3.4  | Re-Architecting Register File for Slumber | 108 |  |

|    |              | 6.3.3  | Power Mode Transition                     | 105 |  |

# List of Figures

| 3.1  | GPU memory hierarchy                                                                                                                            | 2 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3.2  | Data reference sharing distribution                                                                                                             | 2 |

| 3.3  | PAVER Overview: Paver generates the locality graphs by identifying the locality information in the PTX code at JIT. The TB-graph partitions are |   |

|      | then fed to TB scheduler at run-time to leverage the inter-TB data locality.                                                                    | 3 |

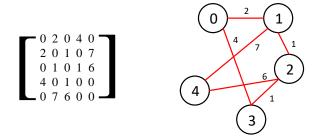

| 3.4  | An example of an adjacency matrix and the corresponding locality graph .                                                                        |   |

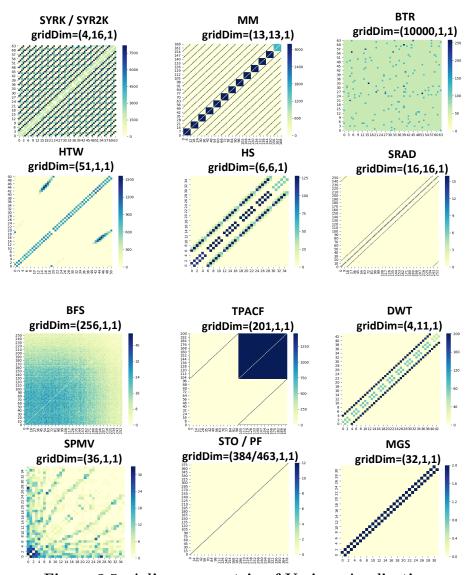

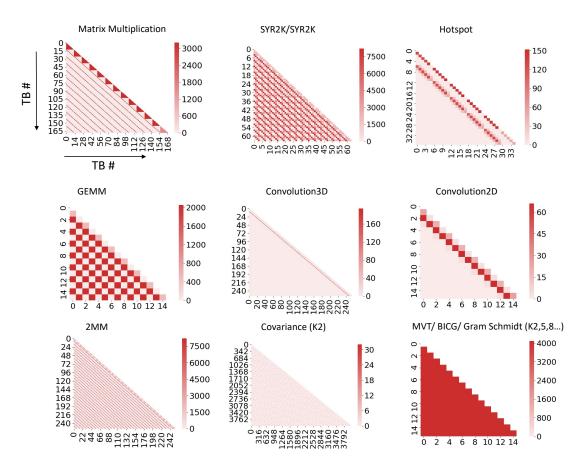

| 3.5  | Adjacency matrix of Various Applications                                                                                                        | 3 |

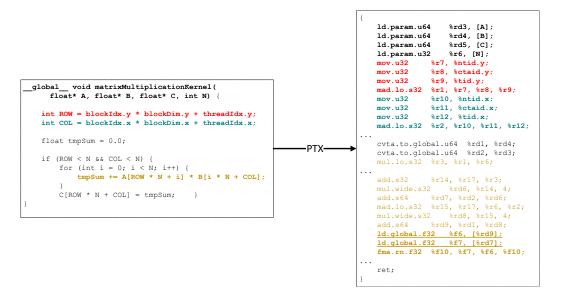

| 3.6  | Matrix multiplication source code (left) and some of its corresponding PTX                                                                      |   |

|      | representation (right)                                                                                                                          | 3 |

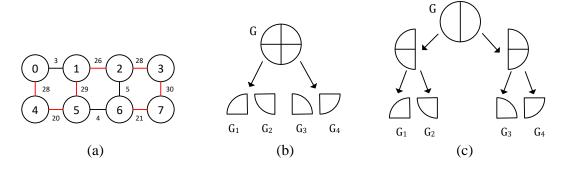

| 3.7  | Overview of TB grouping and ordering approaches. (a) maximum spanning                                                                           |   |

|      | tree. (b) k-way partitioning. (c) recursive bipartitioning                                                                                      | 3 |

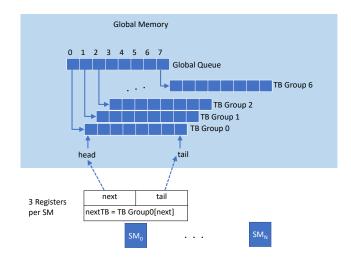

| 3.8  | Storing TB Groups in Global Memory: Once the TB-Groups are generated by                                                                         |   |

|      | different graph-partitioning strategies (MST, Kway, Recursive Bipartitioning),                                                                  |   |

|      | they are stored in the global memory. A global queue (located in global                                                                         |   |

|      | memory) is used to store the pointers to these TB groups. Each SM is                                                                            |   |

|      | associated with two registers (next, tail) which point to the TB group's head                                                                   |   |

|      | (initially) and tail assigned to that SM, respectively. Once the current TB                                                                     |   |

|      | from the TB group is issued to the SM and starts executing, the <i>next</i> register                                                            |   |

|      | value is updated to point to next TB in the TB group and the next TB                                                                            |   |

|      | register is loaded with the new value i.e. TB group[next]. This next TB                                                                         |   |

|      | register guides the thread block scheduler.                                                                                                     | 4 |

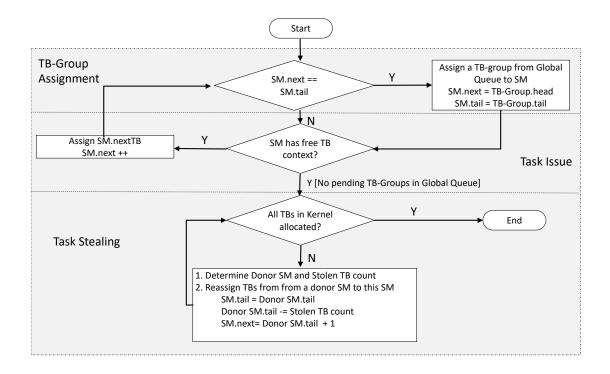

| 3.9  | PAVER Runtime Flowchart                                                                                                                         | 4 |

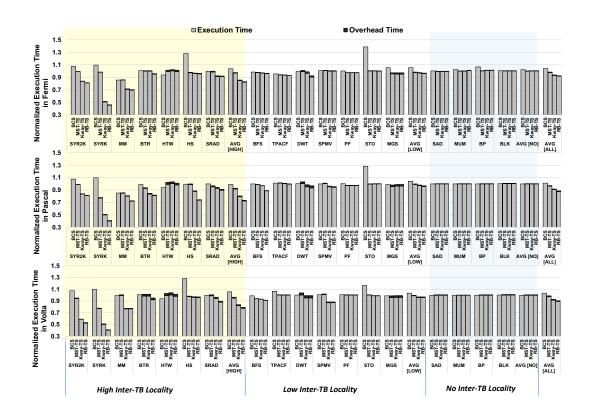

| 3.10 | Kernel Execution Time and JIT Analysis Overhead of BCS, MST-TS, k-way-                                                                          |   |

|      | TS, RB-TS normalized w.r.t. baseline TB scheduling policy (LRR), on Fermi                                                                       |   |

|      | (top row), Pascal (middle) and Volta architectures (bottom)                                                                                     | 4 |

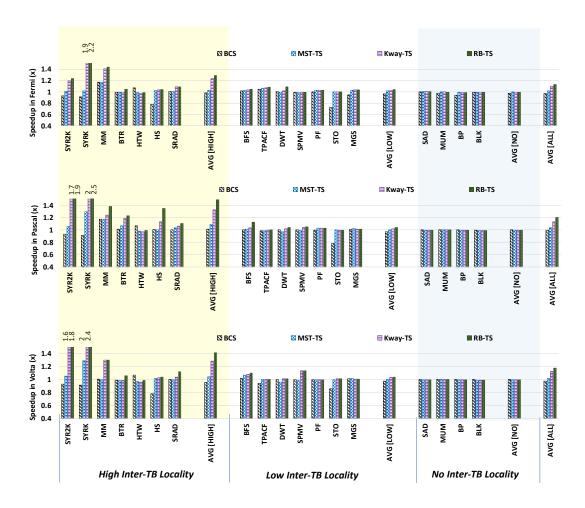

| 3.11 | Speedup of BCS, MST-TS, k-way-TS, RB-TS normalized w.r.t. baseline TB                                                                           |   |

|      | scheduling policy (LRR), on Fermi (top row), Pascal (middle) and Volta                                                                          |   |

|      | architectures (bottom)                                                                                                                          | - |

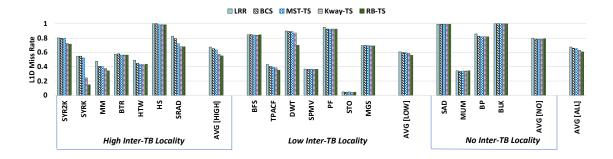

| 3.12 | L1 miss rate comparison of LRR, BCS, MST-TS, $k$ -way-TS and RB-TS in                                                                           |   |

|      | Fermi                                                                                                                                           | ŀ |

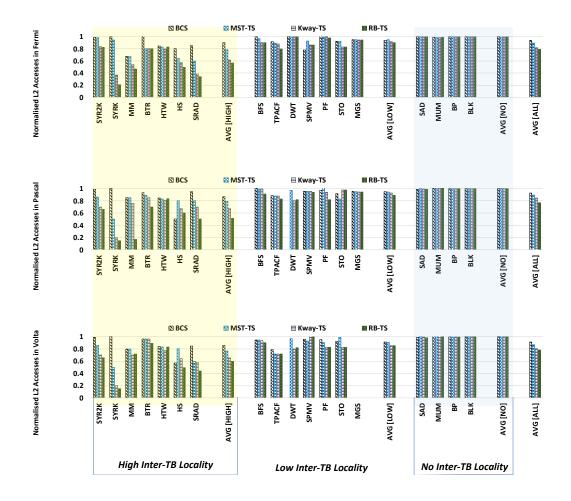

| 3.13              | L2D access comparison for BCS, MST-TS, $k$ -way-TS and RB-TS normalized w.r.t. LRR for applications with high, low and no inter-TB locality, on Fermi (top), Pascal (middle) and Volta architectures (bottom). | 54 |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

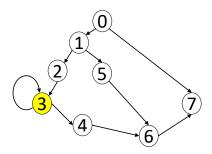

| 4.1               | Control flow graph of the PTX basic blocks (bb) for matrix multiplication. Basic block 3 (highlighted) contains the ld.global instructions and has a self-loop.                                                | 60 |

| 4.2               | self-loop                                                                                                                                                                                                      | 62 |

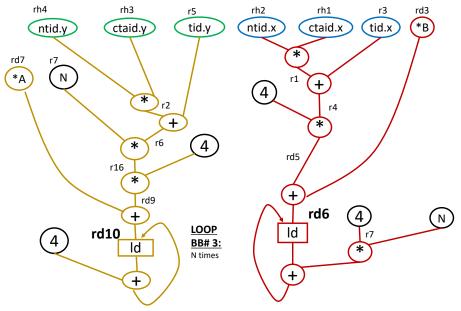

| 4.2<br>4.3<br>4.4 | Abstract Syntax for Matrix Multiplication Application                                                                                                                                                          | 70 |

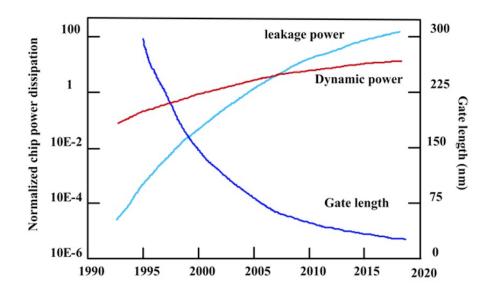

| 5.1               | With the reduction in the feature size in the recent technology nodes, the                                                                                                                                     |    |

|                   | leakage power dominates the dynamic power [19]                                                                                                                                                                 | 77 |

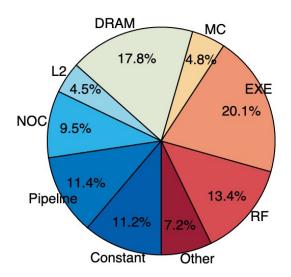

| 5.2               | Average Power Consumption for GTX 480 [86]                                                                                                                                                                     | 78 |

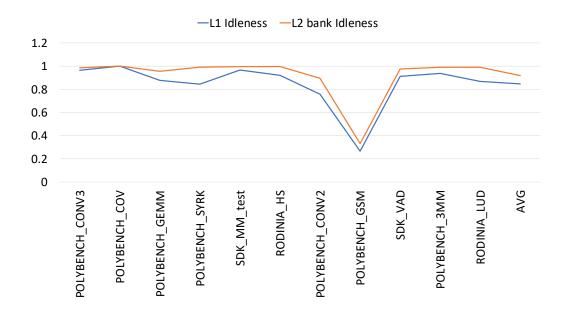

| 5.3               | Idleness period normalized to the total execution time for L1 and L2 Bank                                                                                                                                      | 79 |

| 5.4               | On the left figure the different colors show the numbers for different (a) L1                                                                                                                                  |    |

|                   | $(SM\ 014)$ and $(b)\ L2$ banks $(012)$ Observations: Most idle cycles are                                                                                                                                     |    |

| 5.5               | shorter than 10 cycles                                                                                                                                                                                         | 80 |

|                   | Brown and Blue respectively                                                                                                                                                                                    | 81 |

| 5.6               | State Transition Diagram for L1 cache and L2 banks. 3 power states are ON,                                                                                                                                     |    |

|                   | Sleep and OFF                                                                                                                                                                                                  | 83 |

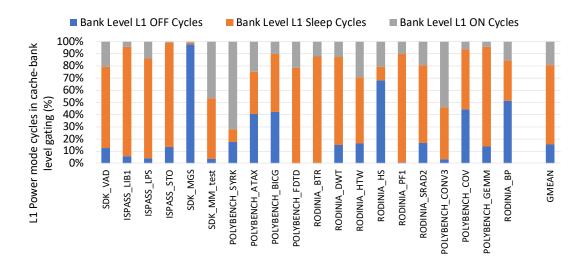

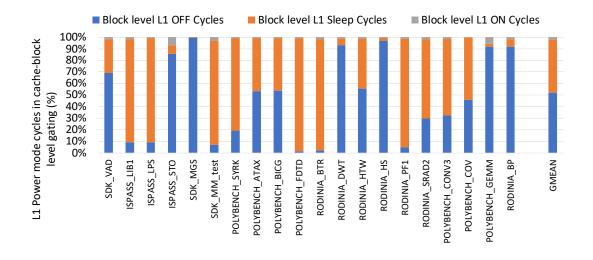

| 5.7               | % distribution of the cycles in different states in L1 cache for cache bank-level                                                                                                                              | 0. |

| F 0               | gating in Fermi                                                                                                                                                                                                | 85 |

| 5.8               | % distribution of the cycles in different states in L1 cache for cache block-level                                                                                                                             | 0. |

| 5.0               | gating in Fermi                                                                                                                                                                                                | 85 |

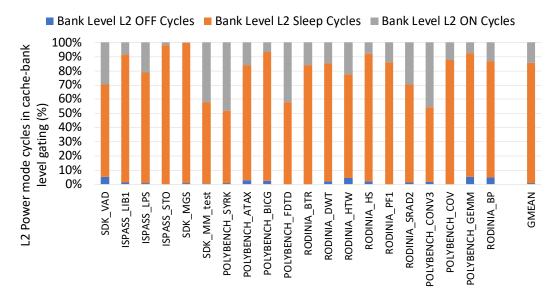

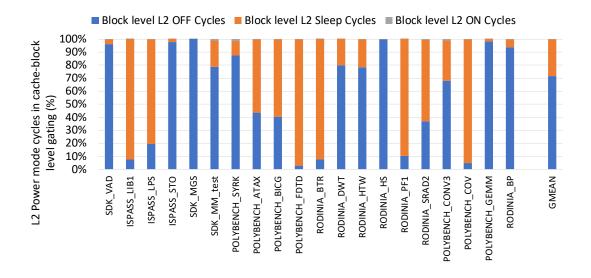

| 5.9               | bank-level gating in Fermi                                                                                                                                                                                     | 86 |

| 5 10              | % distribution of the cycles in different states in L2 cache Bank for cache                                                                                                                                    | 00 |

| 5.10              | block-level gating in Fermi                                                                                                                                                                                    | 86 |

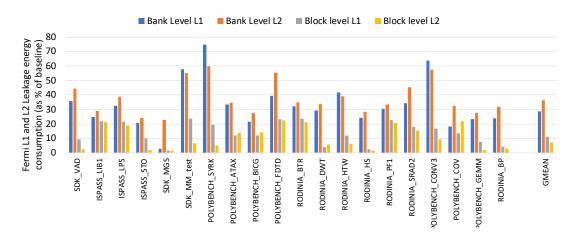

| 5 11              | Fermi Leakage Energy Consumption for L1 and L2 caches using Cache bank-                                                                                                                                        | 00 |

| J.11              | level vs block-level gating as a % of the default leakage energy consumed                                                                                                                                      |    |

|                   | without any energy saving technique                                                                                                                                                                            | 87 |

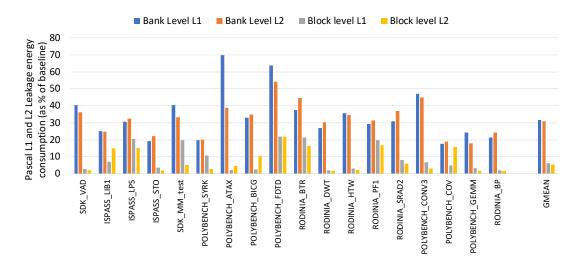

| 5.12              | Pascal Leakage Energy Consumption for L1 and L2 caches using Cache bank-                                                                                                                                       | 01 |

| J.12              | level vs block-level gating as a % of the default leakage energy consumed                                                                                                                                      |    |

|                   | without any energy saving technique                                                                                                                                                                            | 87 |

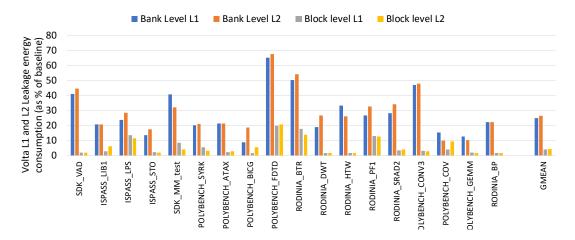

| 5.13 | Volta Leakage Energy Consumption for L1 and L2 caches using Cache bank-<br>level vs block-level gating as a % of the default leakage energy consumed<br>without any energy saving technique | 88  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

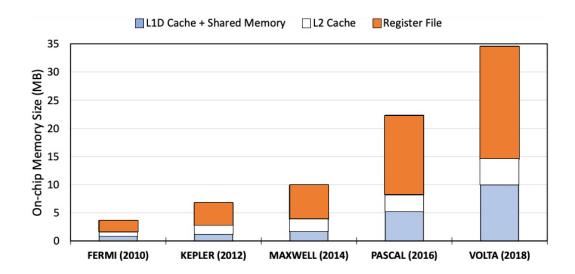

| 6.1  | The Register File size has out grown the cumulative size of L2 Cache, L1 cache and Shared memory in GPUs over the years. Static Energy consumed                                             |     |

|      | by the storage structures is proportional to their sizes                                                                                                                                    | 93  |

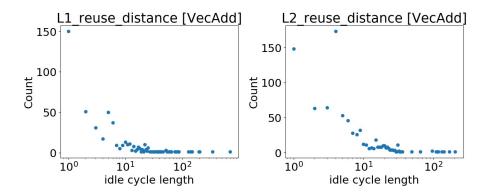

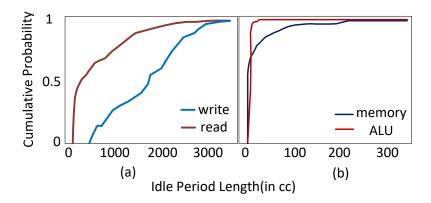

| 6.2  | GPGPU registers Idle Period Distribution for Vector Add application: (a)                                                                                                                    |     |

|      | Cumulative Density Function (CDF) for the reuse distance of the register-                                                                                                                   |     |

|      | writes and register-reads. (b) CDF of the time difference between the cycle                                                                                                                 |     |

|      | when the instruction is scheduled by the warp scheduler and the cycle when                                                                                                                  |     |

|      | the register is updated                                                                                                                                                                     | 94  |

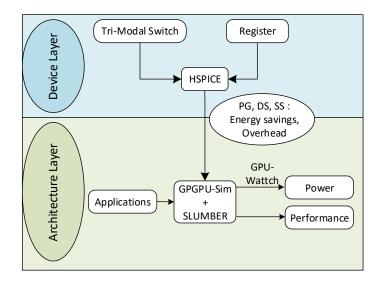

| 6.3  | Slumber Overview showing Cross-layer methodology                                                                                                                                            | 96  |

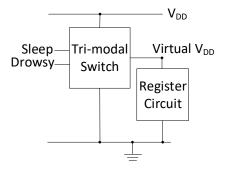

| 6.4  | Varying the voltage across the register using Tri-modal switch                                                                                                                              | 97  |

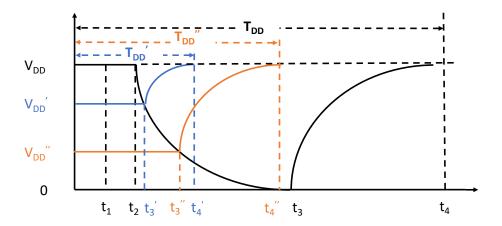

| 6.5  | Target circuit state transition during power gating interval                                                                                                                                | 98  |

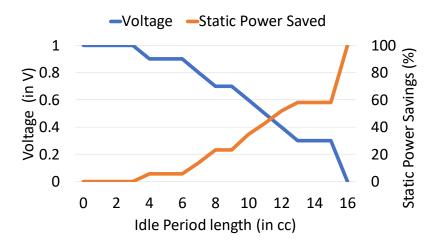

| 6.6  | Determination of optimal under-volting level and associated static power                                                                                                                    |     |

|      | savings based on the idle period length                                                                                                                                                     | 99  |

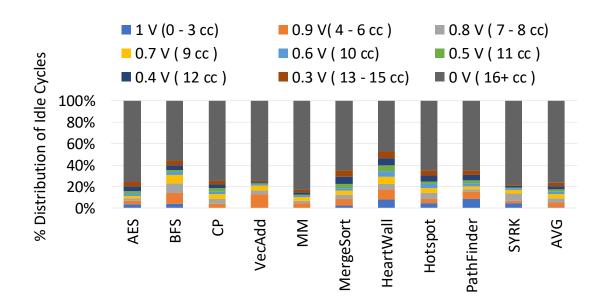

| 6.7  | Idle Period Distribution based on length                                                                                                                                                    | 100 |

| 6.8  | Idle Period Distribution across Sleep States                                                                                                                                                | 100 |

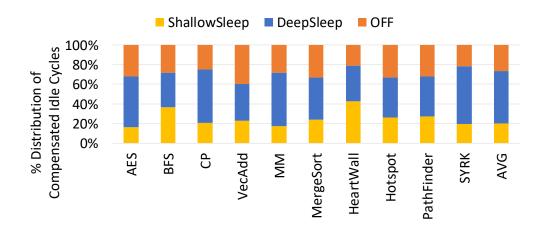

| 6.9  | FSM of the Slumber Algorithm                                                                                                                                                                | 105 |

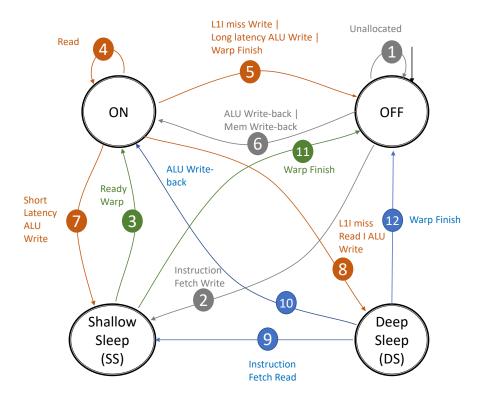

| 6.10 | 9                                                                                                                                                                                           |     |

|      | switch output using mux and Slumber control Logic in order to enable Power                                                                                                                  |     |

|      | Gating $(V = 0)$ , Under-volting modes (SS: Shallow Sleep, DS: Deep Sleep)                                                                                                                  |     |

|      | and ON state $(V = V_{dd})$                                                                                                                                                                 | 108 |

| 6 11 | Leakage Energy Savings                                                                                                                                                                      | 111 |

# List of Tables

|     | Fermi, Pascal, Volta GPU specifications (for evaluation) Data reference sharing across TBs for various applications from [1, 24, 100, 135]. |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | GPU cache configuration in different architectures                                                                                          |     |

| 6.1 | Power management modes for Register File.                                                                                                   | 102 |

## Chapter 1

## Introduction

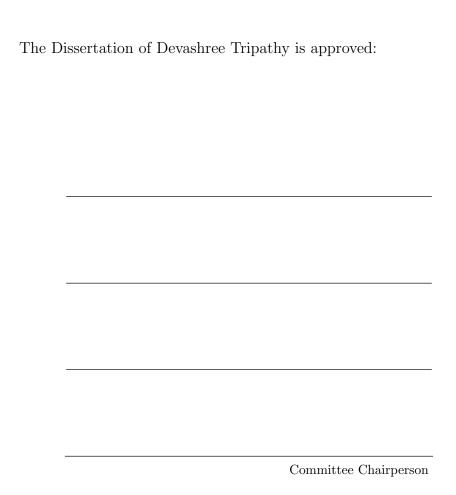

The massive parallelism provided by general-purpose GPUs (GPGPUs) is in demand from many areas of industry and research. Possessing numerous compute threads in their streaming multiprocessors (SMs) and enormous memory bandwidths as high as 1555 GB/s [105], GPGPUs have become the de-facto accelerator of choice in many scientific domains. To support the complex memory access patterns of applications, GPGPUs have a multi-level memory hierarchy consisting of an L1 data cache private to each SM, a banked shared L2 cache connected through an interconnection network across all SMs and high-bandwidth banked DRAM.

With the amount of parallelism GPUs can provide, memory traffic becomes a major bottleneck for present-day GPUs, mostly due to the small amount of private cache that can be allocated for each thread, and the constant demand of data from the GPU's many computation cores. With the ever-increasing data size of GPU applications, and each thread having to process more data, simply increasing the cache sizes is not a viable option, since

the additional area will incur extra cost and overhead. This means that smaller L1 and L2 caches are much more likely to suffer from cache thrashing, i.e. eviction of cache lines which could have been used by other execution units. Cache thrashing can lead to more cache operations, which means more energy consumption, and tremendous under-utilization of the other GPU resources, resulting in under-performance [33,67,141,160,162]. To minimize this, all threads need to utilize the shared cache memory spaces with each other as efficiently as possible. Efficient use of the memory system as well as co-locating the compute and data together is important for exploiting the massive computational capability offered by GPGPUs to their full potential. A key approach to efficiently improve the memory bandwidth is data locality – (i) increasing the data reuse within the SM at the thread, warps and thread block (TB) level, thereby reusing the L1 cache lines before it is evicted; and (ii) placing the data close to the computation so as to reduce the communication across multiple SMs within a GPU or even multiple GPUs. There is no generalized technique which exploits the data locality present in various applications to improve the efficiency of cache and memory system usage. There have been prior research on addressing the memory bottleneck issues, including the prefetching [75, 128], cache management [147], locality-aware schedulers [87, 148], memory-level parallelism [40, 165, 168] etc. All these techniques need the data locality information which is either known a priori using profiling techniques, or learnt and predicted during the kernel execution. For extracting the locality information, we use profiling in section 1.1 and a PTX analyzer at the JIT time in section 1.2.

Along with the challenge to maintain high GPU throughput and performance by mitigating the memory bottleneck issue, the leakage power dissipation has become one of the major concerns with technology scaling. The GPGPU storage structures like caches and register file have grown in size over last decade in order to support the parallel execution of thousands of threads. Given that each thread has its own dedicated set of physical registers, these registers remain idle when corresponding threads go for long latency operation. Existing research [2,39] shows that the leakage energy consumption of the storage structure can be reduced by either power gating or reducing to a data-retentive low-leakage voltage (Drowsy Voltage) to ensure that the data is not lost while not in use. Sections 1.3 and 1.4 in this thesis introduce to evaluate these techniques and explore new architecture to further increase energy saving.

## 1.1 Data-Locality Aware Thread Block Scheduler

The most common relationships between the threads sharing the cache are readafter-write (RAW) and read-after-read (RAR) cases. RAW constitutes data dependency

among tasks, e.g. thread blocks (TBs), also known as *structured parallelism*. In this case,

a certain execution order among the tasks will be formed and the execution time will be

bound to a *critical path*. Exploiting this order can improve the performance substantially.

There have been numerous works on structured parallelism in CPUs [7,37,45,127], and more

recently in the realm of GPUs [5,17,148]. In particular, they try to exploit the data locality

between parent and child TBs.

RAR, or local data sharing, on the other hand, happens in *unstructured parallelism*, in which the tasks are independent, and thus free to be executed in any order. Its impact is more prominent when there is no write-allocate policy in place. As a result, the program's

outcome would be correct regardless of task ordering and location of execution. However, processes can still subtly affect each other in terms of shared resources and, by extension, the performance, in contrast to the more explicit sharing in structured parallelism. To make better use of the cache data, the data locality of the parallel-run tasks must be observed and considered with respect to a given cache architecture. Research works have addressed this issue in the multi-core CPU area [62,159], and Wang et al [148] improved cache performance with respect to data-reuse involving parent-child thread blocks in GPUs. To the best of our knowledge, there has been no research on exploiting data locality in unstructured parallelism in GPUs.

At the TB level, there have been attempts to take advantage of locality based on a specific data access pattern. In [81], Lee et al. propose Block CTA Scheduling (BCS) which naively assigns two consecutive TBs to the same SM. However, their approach works only for row-major applications, i.e. applications optimized to run with row-major data structures, such as matrix multiplication, n-body, and hotspot. Since the grid structure of the tasks is application-specific, PAVER addresses this problem with a more generic graph-based approach to improve performance and memory efficiency. We do so by creating a graph of TBs using their data sharing statistics, where the vertices represent the TBs and a weighted edge between two TB denotes the number of shared data locations between them.

Designing a graph structure requires us to know the access footprint per TB in the application a priori and then deciding which TBs to group in the same SM to maximize the cache utilization. Hence, it is necessary to analyze the cache access characteristics before the execution. Compiler-assisted methods can extract locality information directly from

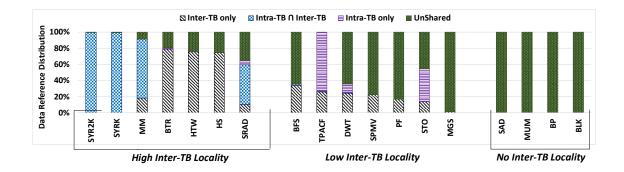

the code itself e.g. static compiler analysis, which can be used to optimize cache bypassing, warp scheduling, thread throttling, etc. [67,69,91]. We propose PAVER (Priority Aware Vertex Scheduler), a TB scheduler that can utilize the RAR information between the TBs while allocating them to the SMs. In PAVER, we propose a just-in-time compilation approach to gather the data sharing statistics among the TBs which run the same kernel and are able to use the same allocated memory. The JIT analysis is accomplished in a GPU after compilation and before the kernel launch [104]. We partition the graph in order to assign TB groups with the most locality to SMs. We explore various graph partitioning policies, such as k-way and recursive bi-partitioning algorithms based on METIS graph partitioning software [63], and Prim's maximum spanning tree (MST)-based algorithm [117]. The partitioning is stopped when the maximum number of TBs is allocated to an SM, as determined by the application and resources. To improve load balancing between SMs, we also incorporate a task-stealing process to move a TB from one SM queue to another when all the TBs in the latter finish early. This ensures a decent load balance in the final phase of the execution.

Our partitioning algorithm ensures maximum cache sharing within an SM for L1 locality, high L2 locality among the SMs, and also ensures load balancing between the SMs. In a SM, maximum allowed concurrent TBs are sent for execution in the form of bunches of 32 threads each, called a warp, to a warp scheduler. This scheduler checks for ready warps within the pool of available warps and once a TB has finished execution, another TB assigned to that SM starts executing. There are several warp scheduling policies with the baseline policy as Greedy Then Oldest (GTO) in which a single warp is prioritized for

execution until it hits a long latency operation after which it is replaced by the warp which was assigned to the core for the longest period of time. PAVER is able to gain significant speedup by reusing the L1 and L2 cache data. However, extracting the locality information and then deriving insights to design efficient TB scheduler can be infeasible and tedious for larger workloads and unknown applications.

## 1.2 A PTX Analyzer to Extract TB Level Locality

Paver obtains the data locality information through profiling. Such profiling work has also been done for both CPUs [8,62,144,164,167] and GPUs [38,130] for extracting the memory and execution time traces. However, as the profiling step has tremendous overhead, research has been started recently to speed up the GPU profiling through sampling and other techniques [62]. Profiling requires the user to run the code in order to detect opportunities to improve the performance. For input dependent applications, the profiled data extracted might not be valid for a different input data or other executions. To minimize the user burden of extracting the profiled data apriori, we propose to automate the locality extraction process by analyzing the intermediate IR (PTX), as discussed in the following sub-section.

Some of the recent works use programming language constructs to associate the thread to a mapped data in order to extract the data address range accessed by a thread [22, 23, 37, 134]. However, these approaches add to the programmer's burden of learning a new language and using it to rewrite the program. Locality Descriptor [146] expresses the data locality using program semantics, which needs the programmer to explicitly specify the static tile dimensions, compute and data mapping and data sharing pattern. TAFE [118]

estimates the thread address footprints of the static as well as dynamic data-dependent applications before kernel launch. The thread to data address index range relation coefficients are extracted by manual inspection of the application source code.

A benefit of analyzing a flat IR such as PTX code over the CUDA source code is that it has fewer program constructs and simpler program semantics. For example, CUDA constructs such as "for loop" and "while loop" that are syntactically different, but semantically equivalent, tend to correspond to similar PTX. Similarly, the conditional "if-else" and "ternary" statements that have syntactically different but semantically equivalent CUDA source code are compiled to similar PTX code. PTX representation uses an assembly-like structure for a virtual GPU architecture, and is only higher-level than the SASS format which executes on a specific GPU architecture.

In LocalityGuru, we aim to derive the relationship between the thread blocks and the memory addresses accessed by them. A detailed compiler analysis is performed on the PTX intermediate representation to extract the data locality in terms of number of common data elements shared between all thread block pairs in a kernel. The static analysis helps us determine the stride distance between two consecutive thread blocks in the grid as well as the data-dependency between the TBs due to the loop iterations. In LocalityGuru, we perform a detailed static compiler analysis to automatically extract the thread to index range relationship from the intermediate representation (IR) of the source code (in PTX format). We analyze the PTX code at JIT compilation time before the kernel launch and perform the detailed static index analysis to derive the equation for the thread/TB mapping to data element indices accessed. We validate the results of the TB locality graph obtained through

automated LocalityGuru PTX analyzer by comparing with the profiling data-locality results.

Our approach imposes zero timing overhead on the kernel execution time.

## 1.3 Static-Power Management for the Caches

In the previous sections, the increased speedup saves the static energy of the entire GPU as the application aided by data locality analysis finishes sooner compared to the default case. However, due to long memory latency, and lack of parallelism, the GPU storage structures are under-utilized. Next, we explore the static energy saving of the storage structures like Caches and Register Files by leveraging the reuse distance or temporal locality distance between the subsequent accesses to the Caches.

In the past, the CMOS transistors used to have negligible leakage power dissipation. However, as the feature size decreases, the subthreshold leakage power dissipation has increased. As the processor technology shrinks below  $0.1\mu$ m, the leakage power dominates the total power consumed by the circuit [71]. In recent years, the primary objective of the chip design is shifting from achieving highest performance to achieving high performance as well as energy efficiency (Performance per Watt). This metric is very important in the case of the de-facto accelerators like GPUs which are power hungry while delivering high throughput. There is a lot of static energy saving opportunity in the caches as they are idle in most of the gpu execution cycles.

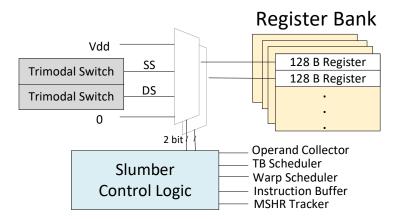

There has been a lot of work on saving the CPU cache power using undervolting and power gating [6,39,70,95]. The caches can be switched to either state-rentive "drowsy" low leakage mode or state-destroying power gated mode. In the drowsy mode ( $0 < V_{drowsy} <$

$V_{DD}$ ), the contents of the caches are not lost, however, in the power gated mode (V = 0 Volts), the contents of the caches are wiped out as the transistors are discharged below the minimum threshold voltage needed for data retention. Trimodal switch [111] is used to switch the target circuit (cache) into one of the three states: ON  $(V_{DD})$ , OFF (0 Volts) or drowsy  $(V_{drowsy})$ . In [39], the drowsy control signal is used to switch a idle cache line to the drowsy mode regardless of its access history. Another paper [70] extends this technique for instruction caches along with the next target sub-bank predictor, where only one sub-bank is active and the rest are in drowsy mode. Some other papers [6,95] use the cache access pattern and cache line re-use distance information to switch the cache line to drowsy state or OFF state. Once the cache line is turned off, they fetch the lost cache data from the lower level memory hierarchy. In the GPU cache leakage energy savings context, one of the recent works [151] proposes a cache-level power management technique to switch the cache array to drowsy or OFF mode when there are no pending access request to the cache.

Our proposed cache power management design "Snooze" under-volts the L1 and L2 caches when there are no pending accesses in the queues (Address Generation Unit $\rightarrow$ L1, Interconnect $\rightarrow$ L1, Interconnect $\rightarrow$ L2, and DRAM $\rightarrow$ L2), which leads to significant leakage energy savings with negligible performance penalty. The caches are undervolted at various granularities like cache bank-level and cache line or block-level and it is observed that the line-level gating yields more leakage energy savings compared to the bank-level gating as a cache line has longer idle period and is less frequently accessed compared to a cache bank on a average.

# 1.4 A Static-Power Management Technique for the Register Files

Over the past decades, the GPUs have continued to scale up in terms of number of concurrent threads and cores. In order to support the faster context switching among the active threads, the register file size per core has also grown in size. The register file is currently the largest SRAM structure on the die and hence consumes the most leakage energy compared to L1 and L2 caches. One of the main limitations of the General Purpose Graphic Processor Units (GPGPUs) is the heterogeneity in workloads with different degrees of parallelism resulting in major resource under-utilization [5,160]. This results in wasted energy especially in case of the register files, which constitute 18% of the total GPU chip power consumption and 32% of the streaming multi-processor's (SM) leakage power [54,86].

One way to save energy is to power gate the unused components when they are not in use. However, the memory components like register files lose data when power-gated. Authors of [2,39] propose a drowsy mode, where the state of the memory cells or passive units are retained by lowering the voltage to a minimum voltage, called drowsy voltage. The active units or the functional units are turned off, i.e. read and write accesses cannot be performed. However, switching the component to deep sleep (drowsy) mode can result in performance penalty due to high wake-up latency. Under-volting is a technique to set an optimum voltage level (less than  $V_{DD}$ ) that has less wake-up latency as compared to the deep sleep state that mitigates the performance penalties. However, the undervolting level of the functional elements will be different. Our detailed modelling of under-volting the registers using the trimodal switch [111] with HSPICE [136] shows that the drowsy

voltage energy break-even time (EBT) can be as high as 13 clock cycles (cc), therefore, the performance penalty incurred can not be neglected. Hence, we argue that there is a need for an intermediate under-volting level with less transition time. In this thesis, we propose two undervolting levels of 0.3 Volt and 0.9 Volt referred to as deep sleep and shallow sleep state respectively. The shallow state can be used when the idle period falls much below the EBT for the drowsy state. The register is **under-volted** to a state retentive voltage if (a) next access to the register is a read access, or (b) idleperiod length is larger than the corresponding energy break-even time (EBT).

We use static compiler analysis to determine the type of register's next access and, thereby, predict the idle period length of the register. Then we determine the under-volting level based on the idle period length and EBT. Though all the prior approaches [2,150] under-volt the registers associated with a warp, we show that the registers can instead be power-gated if the contents of the registers are not useful anymore. Since the register inter-access distance is about 789 clock cycles on an average [2], power-gating the idle registers which are waiting to be written leads to significant leakage energy benefits. It should be noted that power-gating is only possible if the idle-period length is more than the power-gating break-even time. The registers can be **power-gated** only under the following circumstances:

- (a) register is not allocated to any thread block (TB),

- (b) next pending access to the register is "Write", as write resets the register contents.

- (c) The warp has finished executing the kernel. Since the register shall be re-allocated when next thread-block is allocated to the SM, the physical registers for the warp

can be power-gated till all the other warps for the TBs finish executing the kernel.

Thereby saving maximum static energy while in the OFF state.

We propose Slumber, a hybrid energy saving technique where a combination of power-gating and under-volting can be used to save optimum energy depending on the idle period of the registers with a negligible performance penalty.

## 1.5 Dissertation Organization

The rest of the dissertation is organized as follows: Chapter 2 summarizes the related works in different categories like locality based resource partitioning, locality aware scheduling techniques, and power management techniques in CPUs and GPUs. In chapter 3, we describe our graph theoritic approach to analyse the data locality among the thread blocks (TB) in a kernel and design various TB ordering and grouping strategies to gain speedup. Chapter 4 discuss automated compiler based approach to extract the locality information of any unknown application at the Just-In-Time compilation time. The JIT PTX analyzer overcomes the limitations of profiling approach incase of larger workloads and unknown applications. Chapter 5 and Chapter 6 discuss the proposed power-management technique for the GPU Caches and Register File respectively. Different undervolting techniques are employed depending on the idle period length and the storage structures are switched on just before their predicted accesses to mitigate any potential performance penalty. Finally, Chapter 7 concludes this dissertation by giving a summary of our work as well as directions for future work.

## Chapter 2

## Related Work

This chapter covers the literature related to the studies proposed in this thesis. First, we provide the related work for locality in GPUs, resource based partitioning and the locality aware warp and thread block scheduling techniques. Next, we discuss the compiler assisted locality information extraction works, and then, we summarize the general power management solutions for cache and register file energy efficiency.

## 2.1 CPU Cache Locality

The idea of using data locality to improve the performance and reduce the memory bottleneck started in the realm of CPUs and continued to multicores. As the cores have become more complex, so have the cache hierarchies, which means that any unnecessary cache action can now leave more of a negative impact on the performance and the energy efficiency [159]. According to [164], even though exploiting inter-core cache locality is in progress, it should not be without taking intra-core locality into account, for it could actually

perform worse than only exploiting intra-core locality. There have been analyses of the tradeoff between cache reuse and vectorization on CPUs, but in the end, they should be used in the right place and it mainly depends on the application type and the architecture [129]. Kandemir et al [62] argue that different cache hierarchies in different architectures makes it difficult for the programmer to optimize the application for all architectures, and presents a compiler-based method in which loop iterations are assigned to different cores and scheduled based on the cache topology and cache access pattern.

In [164], Zhang et al. use a compiler-based strategy to create a computation block dependency graph, targeting data reuse on multicore CPUs. Their observation on data reuse balance leads them to develop a task mapping and scheduling policy that balances inter-core and intra-core data reuse.

Task stealing has also been incorporated and explored in recent literature. Yoo et al [159] propose a locality-aware scheduler for unstructured parallel applications in a multi-core CPU which increases the speedup and reduces the energy consumption for a 32-core system by 2.05x and 47% respectively, and shows that the benefit will increase as the number of cores increase, an additional 1.83x for 1024 cores. They capture the data sharing of an application using special programming APIs and use this information to create a task sharing graph. Then, they generate task groups to be launched on each core keeping the cache topology in consideration. They also perform task reordering to capture temporal locality and task stealing for load balancing. The work proposed by Lifflander et al [92] increases cache locality for recursive programs by tracking data reuse opportunities and, using work stealing, interleaving the execution of the function that can use them.

## 2.2 GPU Cache Locality

Koo et al [74] categorize the load instructions into deterministic, where the address is calculated using thread ID, thread block ID, etc., and non-deterministic (from user input, etc.) Deterministic loads are observed to have a more coalesced access pattern in a stark contrast to the non-deterministic loads which can create far more reservation fails in the cache. They then suggest solutions to alleviate the issue with such loads, such as pre-fetching for indirect addresses [77], reworking the cache hierarchy, and assigning neighboring TBs with data locality to the same SM, the last one being the focus of our work in Chapter 3. Vijaykumar et al [146] has also shown the potential of exploiting locality by proposing the 'Locality Descriptor', which enables definition of locality abstractions on software by the programmer, and utilization thereof by the hardware, improving performance by an average of 26.6% when exploiting locality in the caches. Their work also enables using hardware techniques to improve the performance, such as TB scheduling and cache management. Our work lifts the requirement of software abstraction definition from the programmer, and instead seeks to use a generalized compiler-based approach to extract the block locality among the TBs and utilize them in the SM task assignment stage.

## 2.2.1 Locality aware TB Scheduling

Making use of the locality among thread blocks can prove challenging since very little is known about the exact underlying TB scheduling architecture. Several cache locality algorithms and structures have been proposed for GPGPUs in recent years which include some form of a thread block scheduler within. As mentioned earlier, most of them have

a rather naive approach as they develop heuristics based on workload behavior (e.g. data layout) to exploit data locality. Another drawback is that many of them target specific structures only, e.g. grid applications [142]. Our work (Chapter 3), however, focuses on a more generalized approach to exploit data locality where there is no need to know the application's access patterns, making it effective for applications with all types of structures.

In [87], Ang Li et al. develop a locality-aware TB clustering framework that can exploit inter-TB locality for GPU applications, obtaining an average speedup of 46% and 41% on GTX570 (Fermi) and GTX1080 (Pascal) respectively. This framework can be integrated into a GPU compiler and used on existing GPUs. In their work they argue that inter-TB locality can be exploited only in applications whose algorithmic behavior is known beforehand. They create a new kernel with TBs having inter-TB locality clustered together.

Chen et al [25] propose a hardware-software approach for applications with structural data access, both row- and column-major applications. It checks the address ranges of the ready TBs and issues the TB with the maximum overlapping address range with the TBs already executing on that SM, increasing data reuse and improving the performance by 9% over the BCS scheduling [81]. The maximum overlapping address is determined with the assumption that each TB accesses a continuous 2D space in the cache, whereas our work has a more generalized approach. Also, in [137], Abdulaziz et al. devise a sharing-aware TB scheduler Based on their observation that around 70% of data sharing takes place between consecutive thread block IDs. It assigns TB groups of consecutive TB IDs to the SMs while maintaining load balance among SMs. To aid the scheduler, they also devise a cache replacement policy in L1 and L2 levels such that the L1 cache tries to maximize the number

of cache blocks private to that SM, while L2 cache maximizes the number of cache blocks shared across SMs. This prevents cache block duplication in L1 and L2. Most of their performance benefits come from efficient cache replacement policies as compared to their TB scheduling policy.

The idea of temporal locality could also be extended to dynamic parallelism [59]. Wang et al [148] propose a locality-aware scheduler specifically for dynamic parallelism, in which the TBs belonging to child kernel will be scheduled on the same SM as those of the parent kernel are on, with 27% performance improvement. This paper shows that similar to parallel TBs, locality among parent and child TBs can also be high and therefore exploited.

#### 2.2.2 Locality aware Warp Scheduling

Augmenting the warp schedulers exists in many works for different applications, including exploitation of data locality within the TB. In [121], the warp scheduler rearranges the access patterns of different warps as well as the threads in the warps to reduce the L1 cache misses and thrashing significantly, resulting in 24% performance improvement. The same authors proposed [122] which checks the control flow of the execution and divergences, and uses a predictive approach to schedule threads such that the L1 cache size usage and the likelihood of thrashing is minimized, resulting in a 26% improvement over [121].

Oh et al [107] propose a locality-aware warp scheduler coupled with a pre-fetching scheme, yielding 31.7% performance improvement over the baseline. In this work, cache access patterns are analyzed and warps accessing the same cache line in the same time frame are grouped. If the first warp of the group hits the cache, the rest of the group will also be prioritized under the assumption that their accesses would also be hits, increasing data

utilization before eviction. Should the first warp miss, the pre-fetcher would attempt to pre-load the data for the other warps in the group as well.

It must be pointed out that we consider only spatial locality among the TBs because the temporal localities depend on the warp scheduling policies inside a streaming multiprocessor (SM). These are best handled by warp scheduling policies, such as CCWS [121], which can work orthogonal to the TB scheduling policies. When applied with PAVER (Chapter 3), they will further improve the performance.

## 2.3 Compiler Assisted Locality Analysis

Prior works have proposed various methods to improve performance leveraging the data locality in different applications. In some works, the programmer provides hints in the code which would be used to optimize locality [18,118,124,146]. Locality Descriptor [146] lets the user express and use the data locality information in GPUs through software to allow optimization for the programmer, combined with hardware to leverage the data locality in the application. Sometimes, new programming languages have been proposed to support the expression of data locality [16,22,23,37,134,143,157].

Compiler analysis has already been used by several works for data locality [65, 88, 94, 109]. Index analysis in compilers has been utilized to perform loop transformations in the source code targetted at improving data locality [14, 131, 158]. However, in Chapter 4, we choose to utilize the PTX intermediate code which is architecture-agnostic and holds the control and data flow information better than source code, which may not be always available to the user.

CODA [68] uses static analysis to compute the stride distance between two consecutive thread blocks (TBs) at runtime. This information is used to determine the size of the data accessed by a TB and ensure that the TBs and the data they access are co-located on the same GPU. Though this approach captures the TB index range in case of the 2D regular grid applications exhibiting strided accesses, a more detailed analysis of the code is needed to account for other access patterns in various applications. LADM [65] classifies the TB locality pattern in the application into one of seven patterns using static compiler analysis to check for loop variance of array indices. However, this process uses the CUDA source code, which may not be always available to the user, whereas LocalityGuru seeks to find the relationships between the GPU registers through PTX analysis. The static analysis helps us determine the stride distance between two consecutive thread blocks in the grid as well as the dependency of the data accessed by a TB on the loop iteration. TAFE [118] allows the programmer to send static kernel data and dynamic memory information to the device in order to extract their data locality information, and contains hardware to track data-dependent accesses, reducing the software overhead. Therefore, indirect memory accesses can be obtained, albeit through user APIs in the code. However, in Chapter 4, we choose to utilize the PTX intermediate code which is architecture-agnostic and holds the control and data ow information better than source code, which may not be always available to the user.

# 2.4 CPU Power Optimization Techniques

Power gating (PG) and Dynamic Voltage Scaling are two highly effective techniques proposed in literature to reduce the energy consumption in the processors. PG power management technique turns off the functional units by gating their supply voltage to reduce the power at circuit level when they are unused. A tri-mode switch [111] can be used to drive the target circuit (combinational or sequential logic) in one of three states ON, OFF and drowsy. Drowsy mode preserves the state of the circuit block in the low-leakage mode were as the power gating is a state-destroying mode where the data in the circuit is lost. The ability of data retention in drowsy mode has been the reason for wide use of the trimodal switched in implementing the data-retentive power gating designs.

Several techniques to save the leakage power in caches have been extensively studied [6,39,70,95]. Drowsy cache approach to save energy in the data cache caches has received significant attention [39]. Each cache line has three states: ON,OFF and drowsy. A "drowsy" control signal is used to switch the idle cache line to drowsy state (state-retentive). Similarly, [70] employed similar drowsy leakage current reduction technique to save the leakage energy in the instruction caches. [6,95] uses the prior knowledge of cache access pattern and cache line re-use distance to switch the cache line to drowsy state or OFF state. Once the cache line is turned off, they rely on the lower level memory hierarchy to get the required lost cache data.

Register file power management has received significant attention. Previous works have focused on reducing the register file power consumption from circuit level [49], microarchitecture level [28] till the software level [11,115]. The number of active registers used

were reduced using compile time register file partitioning and recompilation in [44]. Then the register file was partitioned into two sections: active and inactive. The inactive registers were switched to drowsy mode and the register file power is saved as the applications use a reduced set of the registers (active).

## 2.5 GPGPU Power Optimization

Prior works have proposed architectural modifications to increase the idle-period length as well as save energy in specific GPU components such as caches [151], execution units [3,125,156,163] and register file [2].  $\mu$  C -States [64] identifies the non-bottleneck components in the GPU data-path based on their utilization. The authors propose to clock-gate the data-retentive components and power-gate the non-data-retentive ones. They turn-off or tune-down half of the width of non-bottleneck resources leading to energy savings. Wang et. al. [149] propose architectural-level power-gating mechanisms for the graphics pipeline to save leakage power in shader clusters, fixed-function geometry units and execution units.

The access patterns of the GPU cache are different from CPU cache as it suffers from high miss rate and low locality. Wang et al. [151] propose a static energy saving technique for the L1 caches and L2 caches in GPUs. They switch the L1 cache (private) to a SM into the state preserving low leakage mode when there are no ready warps at the warp scheduler. Similarly, L2 is switched to low leakage mode when there are no pending requests. However, when the kernel exits, the caches are no more accessed and hence, are put to OFF state. [152] aggressively switches the cache lines to low power mode and also

bypasses the L1 data cache in some cases to save on the leakage power.

The register file (RF) resources are generally over provisioned to meet the high performance targets, however, their average utilization remains low [2, 141]. To address the under utilization issue and save the leakage power, several novel RF power management techniques like register sharing [53,55], re-purposing the RF as cache or shared memory [35, 73, 77] and power gating the idle registers [2, 48, 82] have been proposed. The prior work "warped register file" [2] uses a similar concept as "Drowsiness" [39] to place the allocated registers in the drowsy state by default; the state is changed to ON when they are accessed. The un-allocated registers are in OFF state. They save the leakage energy of the RF by switching the registers to drowsy mode after each accesses. Due to branch divergence and limited parallelism, there can be several idle threads in warp. They identify the idle threads and save the dynamic energy by not charging the bit and work lines of the registers of idle threads. [82] use a register compression scheme to save register file power. The energy required to access a register file is reduced by reducing the number of register banks needed to store the warp registers. They also power gate a register bank when none of the bank entries are allocated for a register. [48] proposes a hybrid power gating control for mobile GPUs which captures both long and short-term unused cycles of the register file and uses the appropriate power gating mode to reduce the leakage energy consumption.

# Chapter 3

# PAVER: Locality Graph-based

# Thread Block Scheduling for GPUs

This chapter presents a locality graph based thread block scheduler, PAVER, to elegantly solve the complex problem of exploiting the data locality in applications exhibiting unstructured parallelism. PAVER proposes a novel graph-theoretic approach for TB scheduling on GPUs based on the cache sharing behavior between the TBs. The following outlines the organization of this chapter:

- In Section 3.1, we explore the baseline architecture and show how locality awareness can benefit the application performance.

- In Section 3.2, we generate the *TB locality graphs* of various benchmarks through analyzing memory access behaviour of individual thread blocks. We also present details of the JIT compiler analysis, adopted in this chapter.

- In Section 3.3 we design TB scheduling policies, starting from MST, and improve it to k-way partitioning and recursive graph bi-partitioning. We compare these partitioning techniques to understand its effect on L1 and L2 locality.

- In Section 3.4 we explain the PAVER runtime and TB scheduling and how task stealing can help with an application's load balancing. We further discuss the architectural support to store the TB-groups produced by various TB-partitioning strategies and using them to guide TB scheduling.

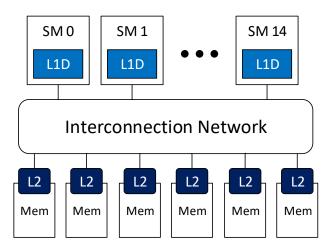

- In Section 3.5, we evaluate PAVER and show that our proposed scheduler can achieve average speedup of 29%, 49.1%, 41.2% compared to LRR in Fermi, Pascal and Volta architectures. Benchmarks selected from widely used benchmark suites Parboil [135], Rodinia [24], Polybench [116], ISPASS [1], and CUDA SDK [100] were analyzed and classified into high, low and no inter-TB locality categories.

# 3.1 Background and Motivation

TB scheduling is managed by the GigaThread engine in Nvidia GPUs [84]. Despite efforts to approximate the behavior of the TB scheduler [98], there are few official details on it. The baseline TB scheduler is assumed to be using a loose round-robin (LRR) policy, as empirically observed in prior work [87]. A round-robin policy implicitly takes advantage of locality among consecutive TBs that can simultaneously access the L2 cache. To capture both L1 and L2 locality, some prior works assign TBs at the granularity of a group of consecutive TBs (typically groups of two) to an SM [81,137]. These prior techniques specifically exploit the two-dimensional data grid with locality typically occurring between TBs in the same

row. Such a policy is bound to fare poorly if there is large column-wise communication, or even worse, if the communication between TBs is arbitrary.

As a novelty, we attempt to establish an order in thread block execution by using a graph-based approach to maximize data locality. This method is completely generic and is able to extract locality patterns through graph-theoretic approaches regardless of the application's data layout or algorithmic behavior. To this end, we determine the locality among all the thread blocks per kernel before the kernel launch, and create a weighted graph pertaining to that kernel (for multi-kernel applications, a graph is generated for each kernel). The vertices are annotated with thread block IDs and the edge weights represent the number of shared data references between two TBs. The higher the weight of an edge between two nodes, the higher is the locality between the two TBs. We will later explore various locality graph partitioning techniques in order to assign TBs to SMs to maximize cache reuse.

## 3.1.1 Baseline GPGPU architecture

Table 3.1: Fermi, Pascal, Volta GPU specifications (for evaluation)

| Architecture                      | Fermi     | Pascal              | Volta      |

|-----------------------------------|-----------|---------------------|------------|

| # of SMs                          | 15        | 28                  | 80         |

| Max # of TBs/Warps/Threads per SM | 8/48/1536 | 32/32/2048          | 32/64/2048 |

| L1/Shared Mem. Cache Size per SM  | 16/48 KB  | $48/96~\mathrm{KB}$ | 32/96  KB  |

| Total L2 Cache Size               | 768 KB    | 3MB                 | 4.5MB      |

| Core Frequency                    | 700 MHz   | 1 GHz               | 1.2 GHz    |

In this work, we use Nvidia GTX480 (Fermi [101]), Nvidia TITANX (Pascal [102]) and Nvidia TITANV (Volta [103]) architectures for evaluation purposes. Our technique exploits application-level characteristics and can be generally applicable to all architectures. Table 3.1 describes the specifications of GTX480, TITANX and TITANV, and Figure 3.1

Figure 3.1: GPU memory hierarchy

depicts the memory hierarchy layout for a generic GPU. As it can be seen, every streaming multiprocessor (SM) has an L1 cache, and there is an L2 cache per memory channel that is shared by all the SMs. Whenever a load operation attempts to access a data which is already cached, it is considered a *cache hit*. Otherwise, it results in a *cache miss*, and the cache will request the data from the lower memory in the hierarchy. A miss can occur due to the data simply never being present (cold miss), or due to the data block being evicted from cache because of cache size limit (capacity miss), or set conflicts (conflict miss), or becoming stale after another 'sibling' cache has modified it. In Fermi, however, since there is a write-evict policy [106], we do not experience cache invalidations due to coherence protocols.

All load/store units (LDST) in the SMs have a memory coalescing unit to reduce unnecessary cache accesses. To further accommodate memory coalescing and avoid extra memory traffic, an SM's L1 data cache has a miss status holding register (MSHR) table, which sends the request to the L2 cache and holds the pending data block request while it is being loaded. If another thread tries to access the same block again, it is called a *hit*

reserve or MSHR hit. In this case, the operation will wait for the request in the MSHR to be finished. There can be MSHR hits in a cache only if there is data sharing across warps. If the MSHR is full, any more requests will be a miss and named a reservation fail [13].

## 3.1.2 L1/L2 hit and miss distribution

There are two main types of locality: temporal and spatial. Temporal locality refers to the same data in the cache used at different times, while spatial locality involves different units accessing different parts of the same data block, e.g. two TBs accessing two adjacent elements in the same cache line. We define a term called "block locality" to capture the usage frequency of any data element inside a data block either due to temporal or spatial locality during the execution. If the GPU knows which data block is needed by which specific TB, it can schedule the appropriate TB before the data block is evicted. GPU execution can benefit from a planned scheduling, which maximizes data locality in all caches. If TBs that use distant parts of the memory also share the same SM, it will lead to unnecessary L1 evictions and thrashing, hurting the performance. Similarly, if TBs executing on different SMs lack block locality, they will suffer from L2 eviction.