# **UC Davis**

## **UC Davis Electronic Theses and Dissertations**

#### **Title**

Design of Display Stream Compression Video Codecs

#### **Permalink**

https://escholarship.org/uc/item/9j85h9hn

#### **Author**

Wu, Shifu

## **Publication Date**

2021

Peer reviewed|Thesis/dissertation

# Design of Display Stream Compression Video Codecs

Ву

## SHIFU WU DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in

Electrical and Computer Engineering

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Bevan M. Baas, Chair

Venkatesh Akella

Rajeevan Amirtharajah

$\begin{array}{c} \text{Committee in Charge} \\ 2021 \end{array}$

© Copyright by Shifu Wu 2021 All Rights Reserved

# Abstract

Video displays with ultra-high-definition (UHD) resolutions such as 4K (3840 × 2160) and 8K (7680 × 4320) are now available. Video frame rates such as 120 frames per second (fps) and beyond are becoming more prevalent. Moreover, new display technologies have enabled wide color gamut (WCG) and high dynamic range (HDR). As a result, the required bandwidth to transmit uncompressed video data over display links has dramatically increased (e.g., 120 Gbps for 8K videos with 30-bit color at 120 fps); however, the physical layer bandwidth is not keeping pace with this demand. To address the disparity, a widely accepted low-cost solution is to compress the video stream prior to transmission and decompress upon being displayed. The Display Stream Compression (DSC) standard developed by Video Electronics Standards Association (VESA) enables low-cost and low-latency hardware implementations of visually lossless video codecs over display links. This dissertation analyzes the DSC algorithm, presents three hardware encoder architectures and the design of a fabricated and first published encoder chip, discusses four hardware decoder architectures and six decoder implementations, and describes the design of many-core software DSC decoders.

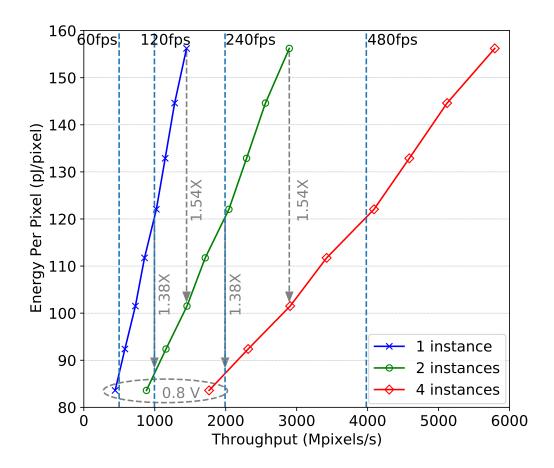

The DSC encoder hardware architectures for a slice encoder, a slice-interleaved encoder, and a time-interleaved encoder are presented. A DSC encoder chip based on the time-interleaved encoder architecture and supporting up to 4K video resolution is designed and fabricated in TSMC 28 nm CMOS technology. The chip is capable of processing two slices in parallel, resulting in a throughput of two pixels per cycle for 4:4:4 pixels, and four pixels per cycle for 4:2:2 and 4:2:0 pixels. The chip shares combinational computational resources across slices, requiring 627.7 K logic gates, yielding a 1.75 times logic area reduction. The time-interleaved encoding scheme lowers energy per pixel by 1.87–1.96 times compared to non-interleaved encoding at nominal voltage. At 1.15 V, the chip achieves up to 1448 megapixels per second (Mpixels/s) at 362 MHz, which is equivalent to 174.6 fps for 4K videos. At 0.8 V, it achieves 441 Mpixels/s for 4:2:2/4:2:0 pixels and 221 Mpixels/s for 4:4:4 pixels, while demonstrating a minimum energy of 84 pJ, 92 pJ, and 163 pJ per 4:2:0, 4:2:2, and 4:4:4 pixel, respectively. The chip achieves 2.7–33 times lower area and 2.0–45 times better throughput

per area compared to prior video encoder chips.

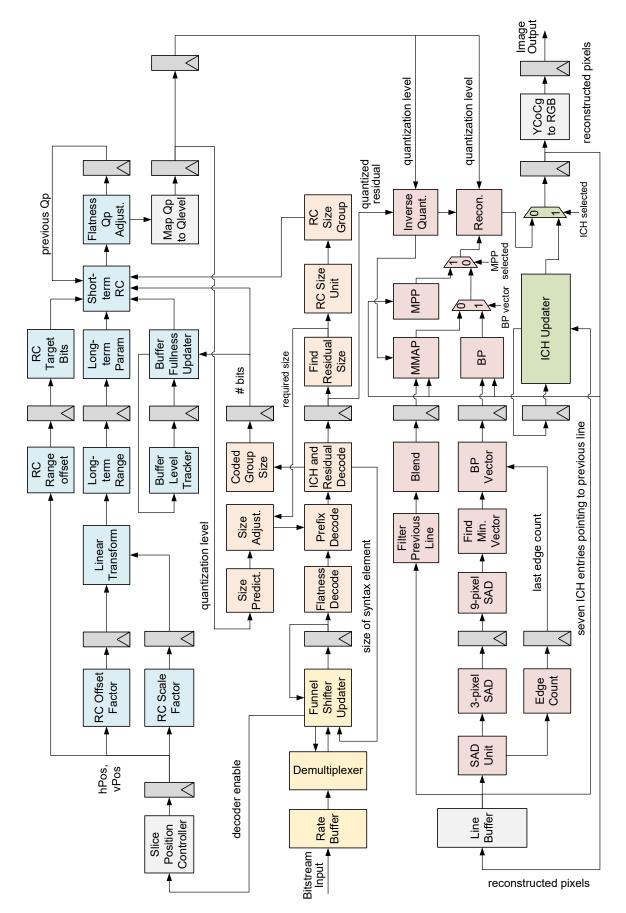

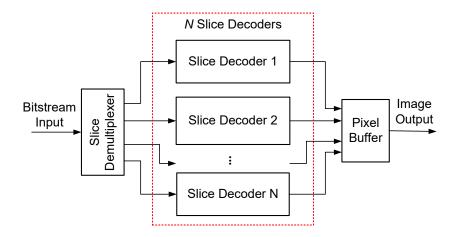

Next, this dissertation presents four hardware architectures for DSC decoders. A slice decoder design realizes the DSC algorithm and achieves a throughput of three pixels per cycle for 4:4:4 pixels, and six pixels per cycle for 4:2:2 and 4:2:0 pixel formats. A slice-interleaved decoder architecture is proposed to support decoding of multiple columns of slices per picture with minimum area overhead. A parallel slice decoder architecture utilizes multiple parallel slice decoders to linearly increase the throughput. In addition, a parallel-interleaved decoder architecture offers area and throughput trade offs. To evaluate the proposed architectures, six decoders are implemented in 28 nm CMOS using a standard-cell-based design flow. The six implemented decoders support decoding of 1080p ( $1920 \times 1080$ ) videos, and require 169.6-627 K logic gates. At 1.0 V, the decoders operate at maximum frequencies of 495-610 MHz, achieve maximum throughput of 1490-13,040 Mpixels/s while dissipating 22.9-58.6 pJ per pixel. The slice decoder achieves five times higher throughput than prior work.

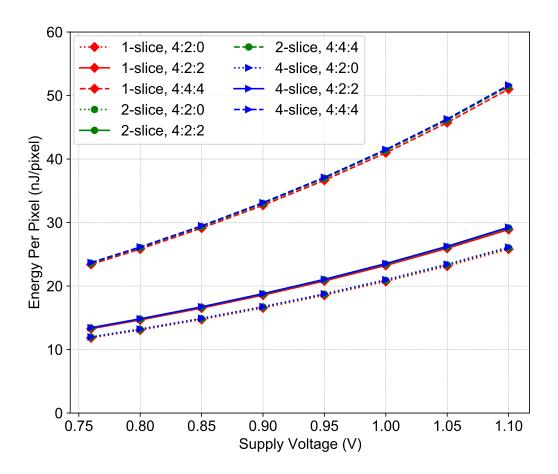

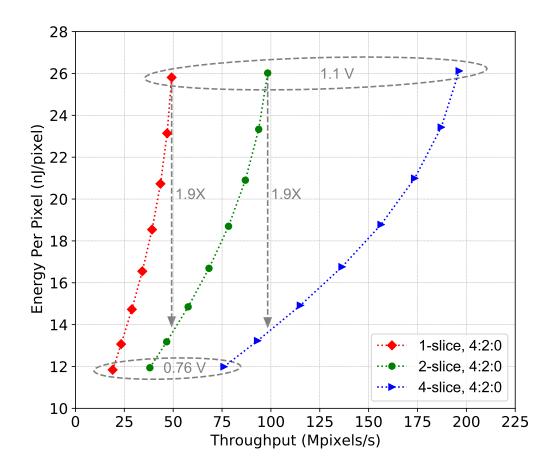

Furthermore, this dissertation presents the design of software DSC decoders on a fine-grained many-core processor array. The slice decoder exploits fine-grained task-level and component-level parallelism and can decode pictures configured into one column of slices; it is implemented with 88 processors and 2 memory modules. The parallel slice decoders facilitate higher performance by leveraging scalable slice-level parallelism; two designs that process two and four slices in parallel are implemented utilizing from 178 processors and 4 memory modules to 359 processors and 6 memory modules. At 1.75 GHz and 1.1 V, the proposed decoder decode 1080p videos in 4:2:0, 4:2:2, and 4:4:4 pixel formats—achieving up to 94.7 fps, 95.6 fps, and 47.9 fps. The minimum energy of 11.8 nJ, 13.3 nJ, and 23.4 nJ per 4:2:0, 4:2:2, and 4:4:4 pixel is achieved in the slice decoder at 0.76 V. The proposed designs achieve up to 159 times higher throughput and 769 times lower energy per pixel than a DSC decoder implemented on one core of an Intel i7-7700HQ processor.

To my wife Hui, and my parents.

# Acknowledgments

The journey of my PhD study has been challenging but yet a learning and growing experience. I would not be able to get it done without the support from many people.

I would like to express my sincerest gratitude to my advisor and mentor, Professor Bevan Baas, for his valuable guidance and support on my research throughout my PhD study. He introduced me into digital VLSI design research and I have learned from him on conducting independent research and presenting work with clear writing. I have benefited a lot from his vision, enthusiasm, and valuable feedback.

I would like to thank Professor Venkatesh Akella for serving in my qualifying examination and dissertation committee, and Professor Rajeevan Amirtharajah for serving in my dissertation committee. I deeply appreciate their valuable feedback on my dissertation. I would like to thank Professor Hussain Al-Asaad, Professor Khaled Abdel-Ghaffar, and Professor S. Felix Wu for serving on my qualifying examination committee.

I would like to thank Professor Massimo Alioto for his guidance on the DSC chip design and funding support for the chip fabrication, and for his valuable time and guidance in presenting the work in a clear and accurate manner of paper writing.

I would like to acknowledge Kalana De Silva and Snehlata Gutgutia for their valuable work on the DSC encoder chip project. I would like to extend my appreciation to Viveka Konandur for his help in the chip package related matters.

I would like to thank Brent Bohnenstiehl for his guidance and support over the years. He is very patient and always available. I have learned a lot from him. I would like to thank Brent for his work on the KiloCore software tool chain and Mark Hildebrand for his work on the task mapping on many-core processor arrays, which enabled efficient design of DSC decoders on the KiloCore processor array.

My special thanks goes to Satyabrata Sarangi and Timothy Andreas for their endless support as colleagues and great friends. We met when I started my PhD and have been working together and stay in close touch since then. I received generous help from Timothy during the testing of the DSC chip, which is highly appreciated. I would also like to thank both of them for their valuable and detailed feedback on my papers and dissertation.

I am grateful to have the privilege of working with past and current members of the

VLSI Computation Laboratory not already mentioned: Aaron Stillmaker, Bin Liu, Jon Pimentel, Emmanuel Adeagbo, Peiyao Shi, Renjie Chen, Jin Cui, Filipe Borges, Christi Tain, Sharmila Kulkarni, Yushan Wu, Arthur Hlaing, Zhangfan Zhao, Ziyuan Dong, Haotian Wu, Yikai Mao, Tony Tsoi, Yuanyuan Xiang, Delvin Huynh, and Sarvagya Singh.

I would like to express my special appreciation to my wife, Hui Wang. This dissertation would not be possible without her endless support and encouragement. I also owe many thanks to my parents for their support and help.

# Contents

| Al | bstra           | ct                                                         | ii              |

|----|-----------------|------------------------------------------------------------|-----------------|

| A  | cknov           | wledgments                                                 | $\mathbf{v}$    |

| Li | st of           | Figures                                                    | x               |

| Li | st of           | Tables                                                     | xiii            |

| 1  | $\mathbf{Intr}$ | roduction                                                  | 1               |

|    | 1.1             | Video Coding                                               | 1               |

|    |                 | 1.1.1 Overview                                             | 1               |

|    |                 | 1.1.2 Video Coding Standards                               | 2               |

|    |                 | 1.1.3 Compare DSC With Other Video Coding Standards        | 5               |

|    | 1.2             | Research Motivation                                        | 5               |

|    | 1.3             | Dissertation Organization                                  | 8               |

| 2  | Dist            | olay Stream Compression (DSC) Standard                     | 9               |

|    | 2.1             | Overview                                                   | 9               |

|    | 2.2             | DSC Encoding Algorithm                                     | 12              |

|    |                 | 2.2.1 DSC Encoding Process                                 | 12              |

|    |                 | 2.2.2 Color Space Conversion                               | 14              |

|    |                 | 2.2.3 Prediction, Quantization, and Reconstruction         | 14              |

|    |                 | 2.2.4 Indexed Color History (ICH)                          | 19              |

|    |                 | 2.2.5 Line Buffer                                          | 21              |

|    |                 | 2.2.6 VLC Entropy Encoding                                 | 22              |

|    |                 | 2.2.7 Rate Control                                         | 23              |

|    |                 | 2.2.8 Substream and Slice Multiplexing                     | 25              |

|    | 2.3             | DSC Decoding Algorithm                                     | 26              |

|    |                 | 2.3.1 DSC Decoding Process                                 | 26              |

|    |                 | 2.3.2 Slice and Substream Demultiplexing                   | $\frac{1}{27}$  |

|    |                 | 2.3.3 VLC Entropy Decoding                                 | 28              |

|    |                 | 2.3.4 Rate Control                                         | 29              |

|    |                 | 2.3.5 Line Buffer                                          | $\frac{29}{29}$ |

|    |                 | 2.3.6 Prediction, Inverse Quantization, and Reconstruction | 29              |

|    |                 | 2.3.7 Indexed Color History                                | 30              |

|    |                 | 2.3.8 Color Space Conversion                               | 30              |

|    | 2.4             | Summary                                                    | 30              |

| 3 | Har        | dware Architectures for DSC Encoders 31                    |

|---|------------|------------------------------------------------------------|

|   | 3.1        | Slice Encoder                                              |

|   |            | 3.1.1 System Controllers                                   |

|   |            | 3.1.2 Prediction, Quantization, and Reconstruction         |

|   |            | 3.1.3 Indexed Color History                                |

|   |            | 3.1.4 Line Buffer                                          |

|   |            | 3.1.5 Rate Control                                         |

|   |            | 3.1.6 VLC Entropy Encoder                                  |

|   |            | 3.1.7 Substream Multiplexing                               |

|   | 3.2        | Slice-Interleaved Encoder                                  |

|   |            | 3.2.1 Architecture                                         |

|   |            | 3.2.2 Dynamic Memory Allocation Across Slices              |

|   |            | 3.2.3 Slice Encode Timing and Extra Buffering              |

|   | 3.3        | Time-Interleaved Encoder                                   |

|   |            | 3.3.1 Time-Interleaved Encoding Architecture               |

|   |            | 3.3.2 Memory Architecture                                  |

|   |            | 3.3.3 Slice Encode Timing and Extra Buffering              |

|   | 3.4        | Summary                                                    |

|   | 3.1        |                                                            |

| 4 | ΑΙ         | SC Encoder Chip in 28 nm for 4K Video Resolution 56        |

|   | 4.1        | Design Goals and Key Features                              |

|   | 4.2        | Chip-Level Architecture                                    |

|   |            | 4.2.1 Double Data Rate I/O                                 |

|   |            | 4.2.2 Dual-Clock FIFO                                      |

|   |            | 4.2.3 On-Chip Test Generator                               |

|   |            | 4.2.4 Memories                                             |

|   | 4.3        | Physical Design                                            |

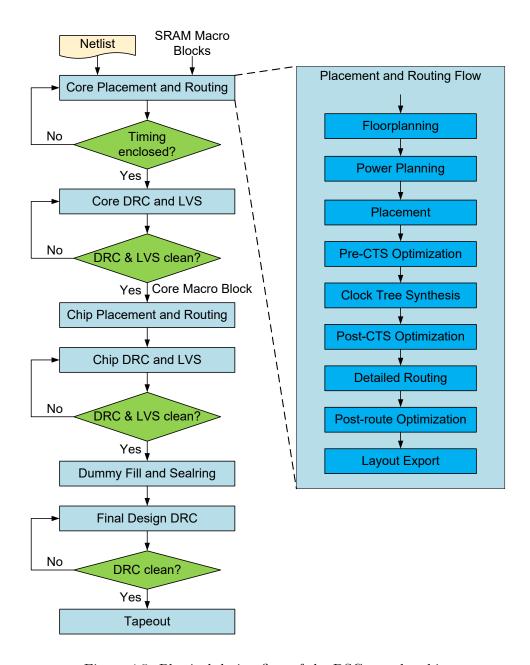

|   |            | 4.3.1 Physical Design Flow                                 |

|   |            | 4.3.2 Physical Design Results                              |

|   | 4.4        | Chip and Testing                                           |

|   |            | 4.4.1 Chip                                                 |

|   |            | 4.4.2 Testing                                              |

|   | 4.5        | Measured Results                                           |

|   |            | 4.5.1 Throughput                                           |

|   |            | 4.5.2 Energy Efficiency                                    |

|   |            | 4.5.3 Multi-Instance Scalability                           |

|   | 4.6        | Comparison With Video Encoder Chips                        |

|   | 4.7        | Summary                                                    |

| _ |            |                                                            |

| 5 |            | dware Architectures and Physical Design of DSC Decoders 79 |

|   | 5.1        | Slice Decoder                                              |

|   |            | 5.1.1 Substream Demultiplexing                             |

|   |            | 5.1.2 Entropy Decoder                                      |

|   |            | 5.1.3 Rate Control                                         |

|   |            | 5.1.4 Prediction, Inverse Quantization, and Reconstruction |

|   |            | 5.1.5 Indexed Color History                                |

|   | <b>-</b> ~ | 5.1.6 Line Buffer                                          |

|   | 5.2        | Slice-Interleaved Decoder                                  |

|   |            | 5.2.1 Architecture 83                                      |

|              |        | 5.2.2 Slice Decode Timing and Extra Buffering                  |            |

|--------------|--------|----------------------------------------------------------------|------------|

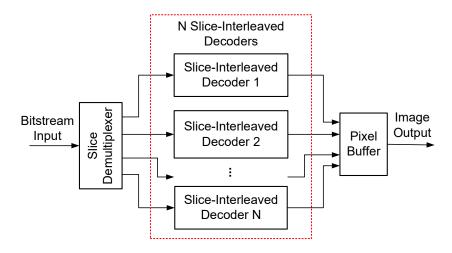

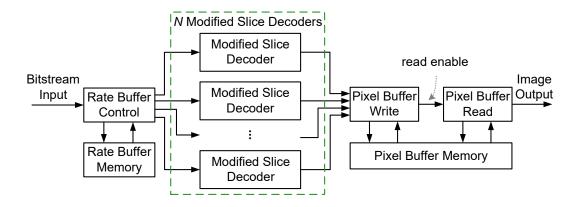

|              | 5.3    | Parallel Slice Decoders                                        |            |

|              |        | 5.3.1 Architecture                                             |            |

|              |        | 5.3.2 Slice Decode Timing and Extra Buffering                  | 36         |

|              | 5.4    | Parallel-Interleaved Decoder                                   | )(         |

|              |        | 5.4.1 Architecture                                             | )]         |

|              |        | 5.4.2 Slice Decode Timing and Extra Buffering                  | 12         |

|              | 5.5    | DSC Decoder Implementations in 28 nm CMOS                      | <b>)</b> 4 |

|              |        | 5.5.1 Design Flow and Implementations                          | )4         |

|              |        | 5.5.2 Results                                                  | )7         |

|              |        | 5.5.3 Scalability                                              |            |

|              |        | 5.5.4 Comparison With Related Work                             |            |

|              | 5.6    | Summary                                                        |            |

|              |        | v                                                              |            |

| 6            | DS     | C Decoders for Fine-Grained Many-Core Processor Arrays 10      | )4         |

|              | 6.1    | Introduction                                                   |            |

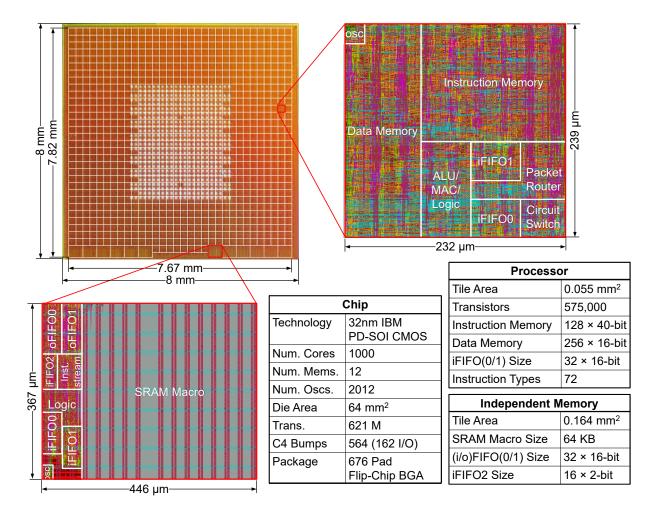

|              | 6.2    | The Targeted Many-Core Processor Arrays                        | )[         |

|              |        | 6.2.1 The KiloCore Chip                                        | )[         |

|              |        | 6.2.2 Programming Methodology                                  | )5         |

|              | 6.3    | Slice Decoder                                                  | )7         |

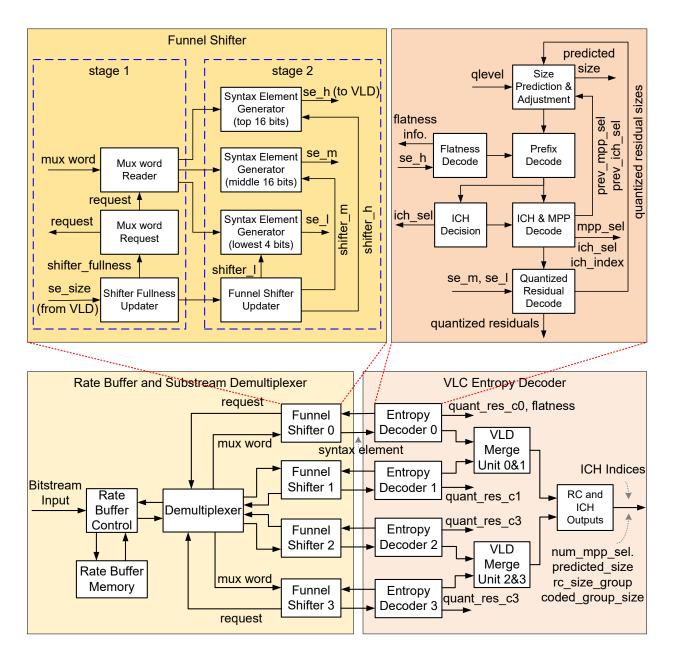

|              |        | 6.3.1 Rate Buffer and Substream Demultiplexer                  | )8         |

|              |        | 6.3.2 Entropy Decoder                                          | .(         |

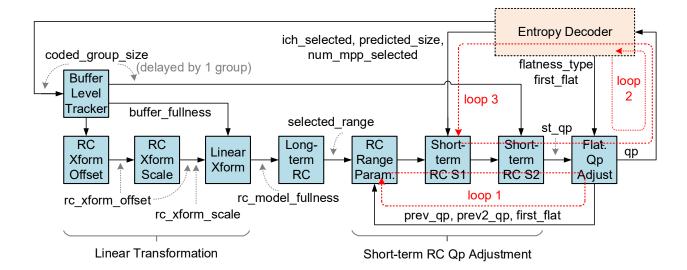

|              |        | 6.3.3 Rate Control                                             | .(         |

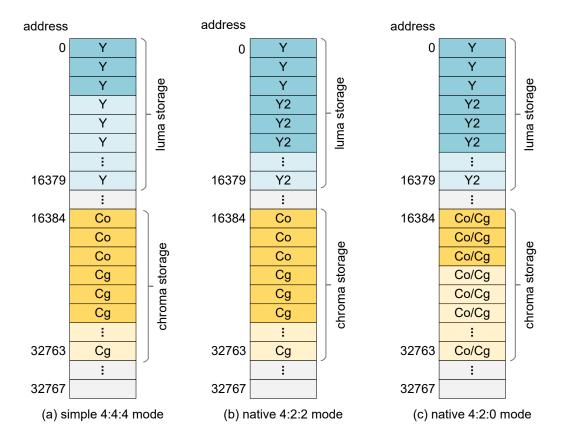

|              |        | 6.3.4 Line Buffer                                              |            |

|              |        | 6.3.5 Prediction, Inverse Quantization, and Reconstruction     |            |

|              |        | 6.3.6 Indexed Color History                                    |            |

|              |        | 6.3.7 Mapping Slice Decoder to a Many-Core Processor Array     |            |

|              | 6.4    | Parallel Slice Decoders                                        |            |

|              | 0.1    | 6.4.1 High-Level Dataflow                                      |            |

|              |        | 6.4.2 Parallel-2-Slice Decoder                                 |            |

|              |        | 6.4.3 Parallel-4-Slice Decoder                                 |            |

|              | 6 5    |                                                                |            |

|              | 6.5    | Simulation Results and Analysis                                |            |

|              |        | 6.5.1 Experimental Setup                                       |            |

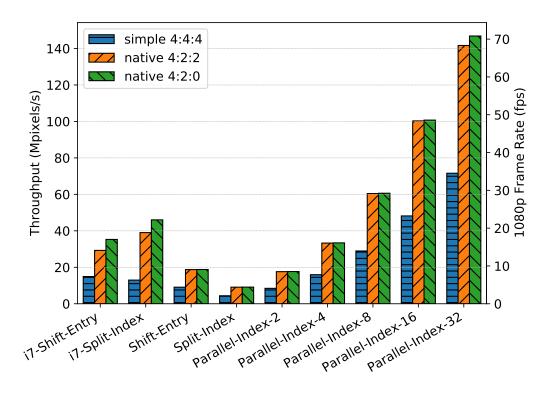

|              |        | 6.5.2 Throughput                                               |            |

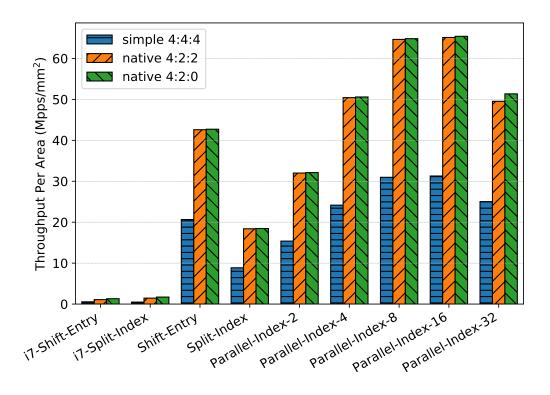

|              |        | 6.5.3 Area Efficiency                                          |            |

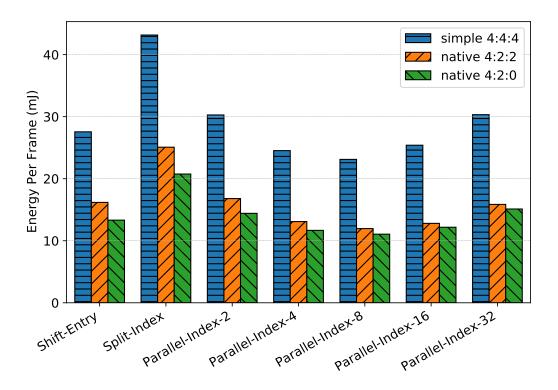

|              |        | 6.5.4 Energy Efficiency                                        |            |

|              |        | 6.5.5 Scalability for Higher Resolutions and Performance       |            |

|              |        | 6.5.6 Comparison With Other Software Video Decoders            |            |

|              | 6.6    | Summary                                                        | 66         |

| 7            | Cor    | nclusion and Future Work 13                                    | . (        |

| '            | 7.1    | Conclusion                                                     |            |

|              | -      |                                                                |            |

|              | 7.2    | Future Work                                                    |            |

|              |        | 7.2.1 DSC Algorithm Optimization                               |            |

|              |        | 7.2.2 DSC Codec on a Single Chip                               |            |

|              |        | 7.2.3 DSC Encoders for Fine-Grained Many-Core Processor Arrays | £ 1        |

| $\mathbf{G}$ | lossa  | ry 14                                                          | 2          |

| D:           | iblios | graphy 14                                                      | ,          |

| וע           | אסננטי | 21 abith                                                       | a (        |

# List of Figures

| 1.1  | Uncompressed data rate for various video resolutions                         | 6  |

|------|------------------------------------------------------------------------------|----|

| 2.1  | DSC usage in end-to-end systems                                              |    |

| 2.2  | YCbCr 4:2:2 pixels packed into virtual 4:4:4:4 container pixels              | 10 |

| 2.3  | YCbCr 4:2:0 pixels packed into virtual 4:4:4 container pixels                | 11 |

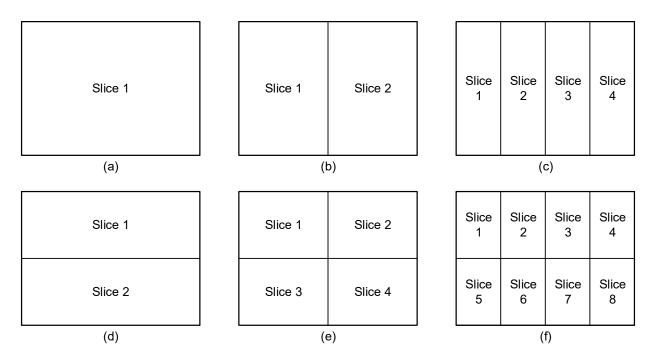

| 2.4  | Slice configurations                                                         | 12 |

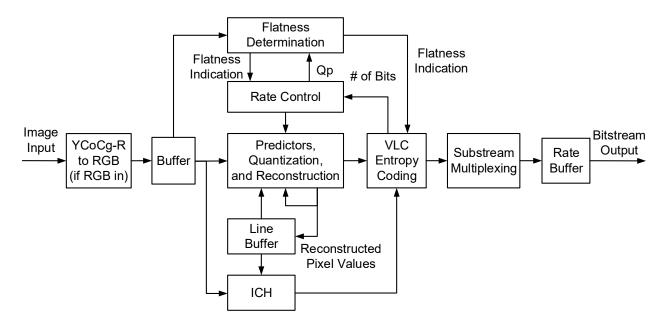

| 2.5  | DSC encoding process                                                         | 13 |

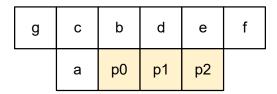

| 2.6  | Pixels used in modified median-adaptive prediction                           | 15 |

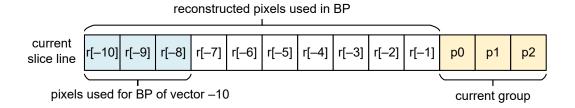

| 2.7  | Block prediction example                                                     | 16 |

| 2.8  | Pixels used in sum of absolute differences calculation for BP search         | 17 |

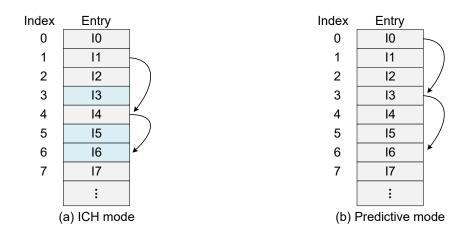

| 2.9  | ICH entries pointing to previous line in native 4:2:0 and 4:2:2 modes        | 19 |

|      | Indexed color history in the DSC encoder                                     | 20 |

|      | ICH update examples                                                          | 21 |

|      | DSU-VLC coding example                                                       | 22 |

|      | ICH coding example                                                           | 23 |

|      | Substream multiplexer and rate buffer in the DSC encoder                     | 25 |

|      | DSC decoding process                                                         | 27 |

| 2.16 | Substream demultiplexing in the DSC decoder                                  | 28 |

| 3.1  | System controllers used in the slice encoder                                 | 32 |

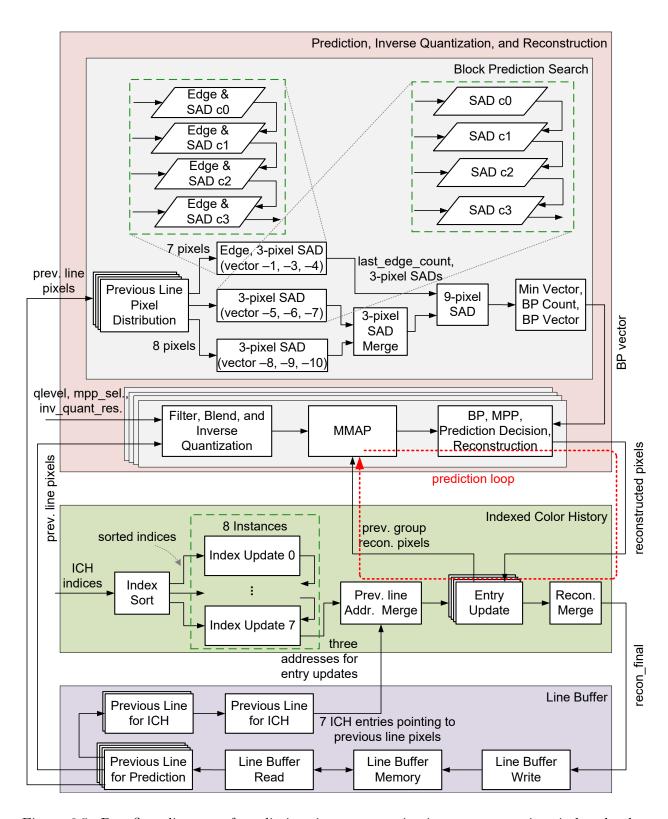

| 3.2  | Pipelined block diagram of prediction, quantization, reconstruction, and ICH | 34 |

| 3.3  | Four-stage pipeline of the BP search                                         | 35 |

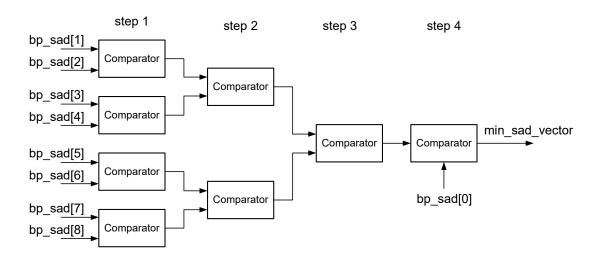

| 3.4  | Four steps to find the vector with the smallest sum of absolute differences  | 35 |

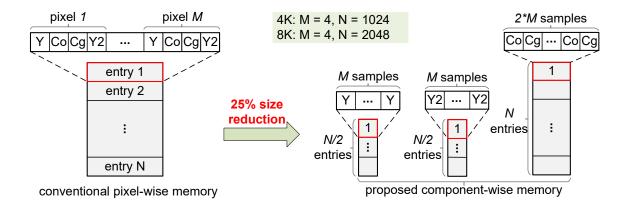

| 3.5  | Component-wise memory architecture for the line buffer                       | 36 |

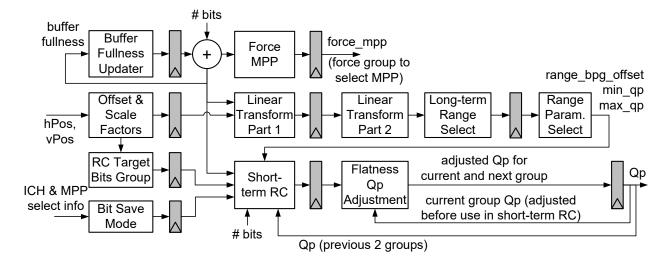

| 3.6  | Pipelined block diagram of rate control in the slice encoder                 | 38 |

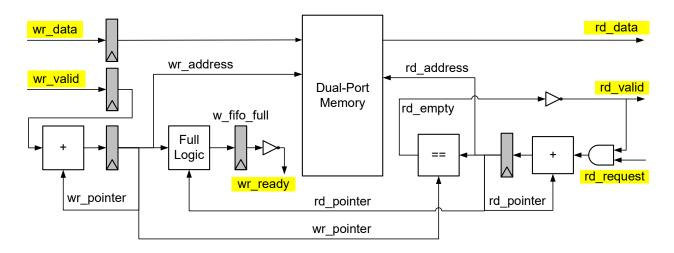

| 3.7  | Synchronous FIFO circuit                                                     | 40 |

| 3.8  | Mux word construction from syntax element for balance FIFO                   | 41 |

| 3.9  | Datapath of a slice-interleaved encoder architecture                         | 44 |

| 3.10 | v v                                                                          | 45 |

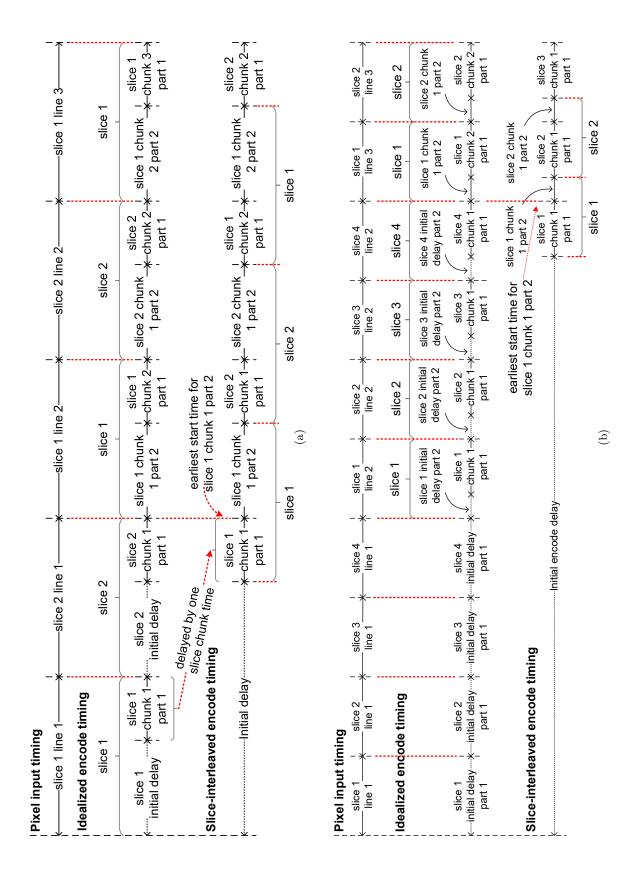

|      | Slice-interleaved encode timing for two and four slices per line             | 47 |

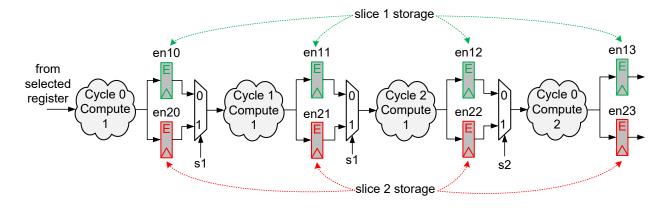

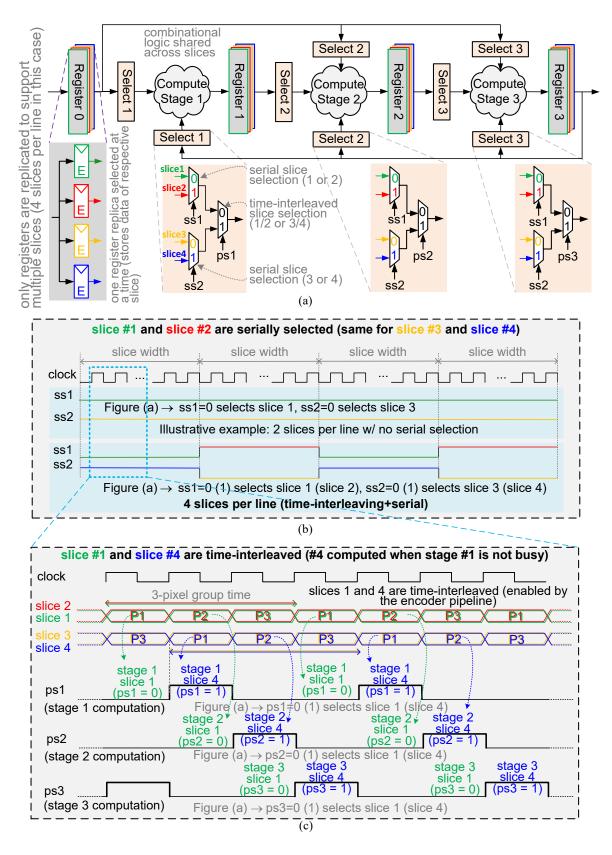

|      | Time-interleaved encoding architecture                                       | 49 |

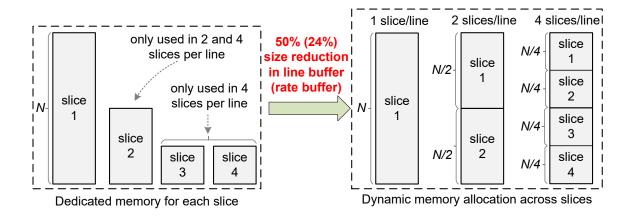

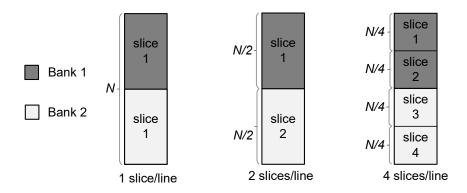

|      | Dynamic memory allocation in the time-interleaved encoder                    | 51 |

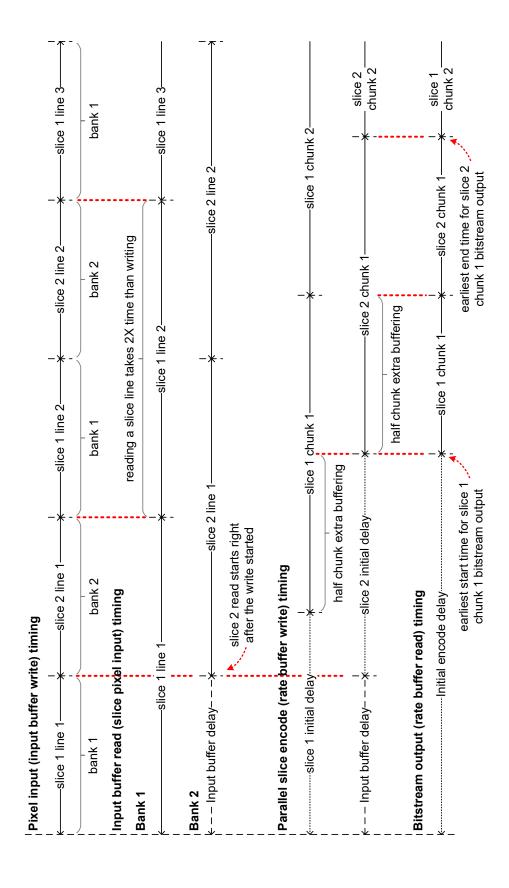

|      | Time-interleaved slice encode timing for two slices per line                 | 53 |

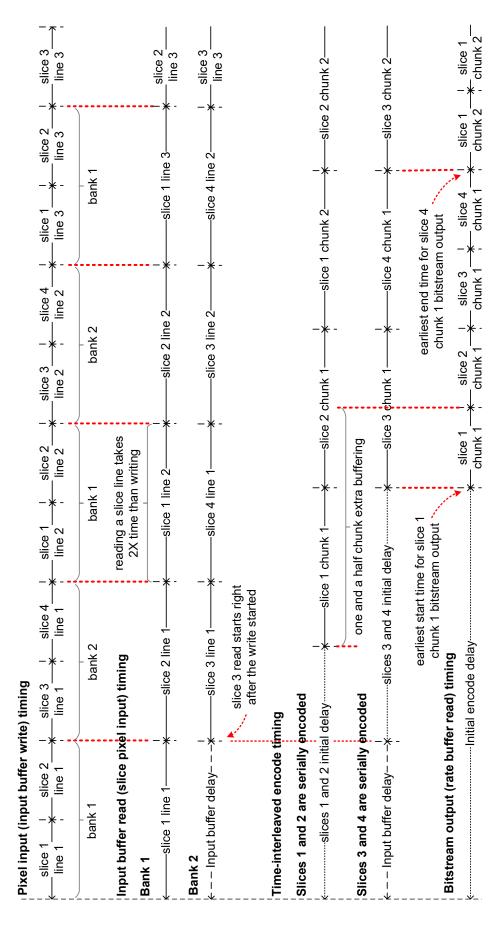

| 3.15 | Time-interleaved slice encode timing for four slices per line                | 54 |

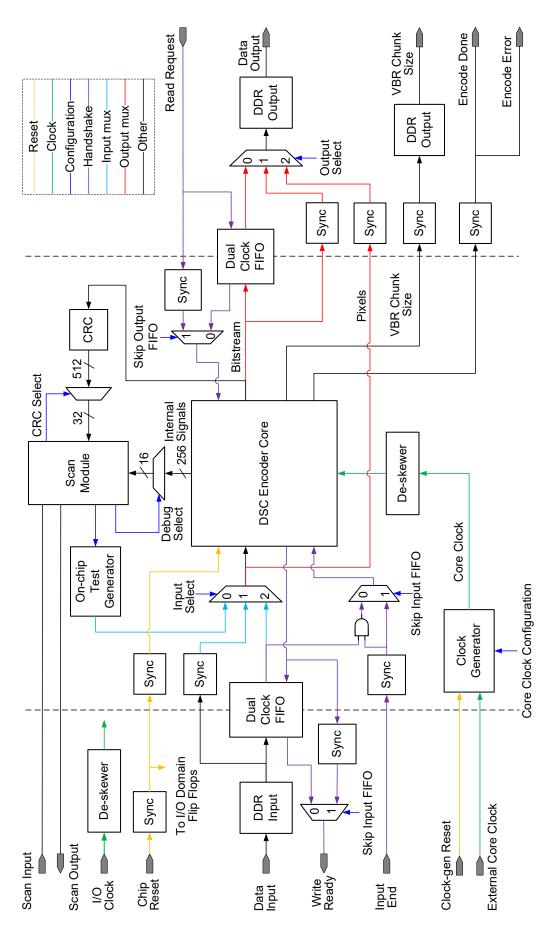

| 4.1  | Chip-level block diagram of the DSC encoder chip                             | 58 |

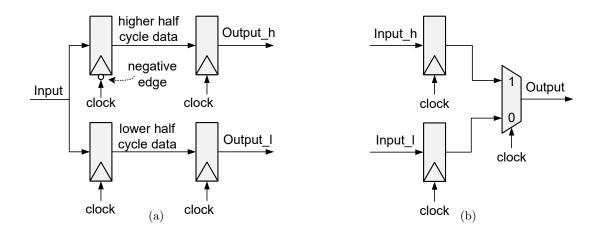

| 4.2  | Double data rate I/O                                                         | 59 |

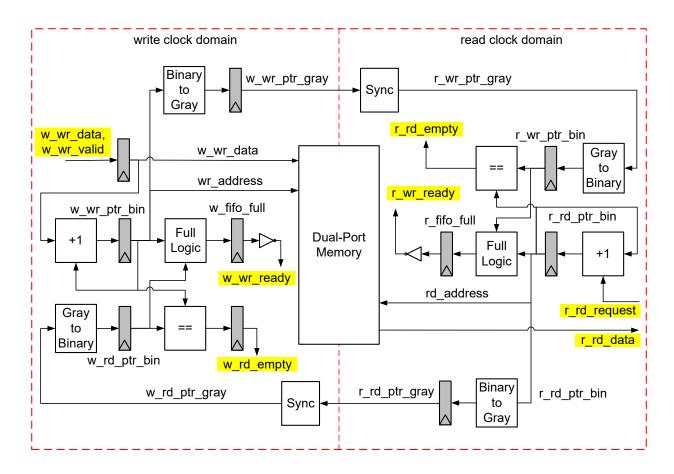

| 4.3  | Dual-clock FIFO circuit                                                      | 59 |

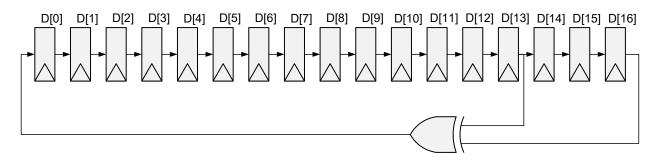

| 4.4  | Circuit of the 17-bit linear-feedback shift register                                   | 61  |

|------|----------------------------------------------------------------------------------------|-----|

| 4.5  | Physical design flow of the DSC encoder chip                                           | 65  |

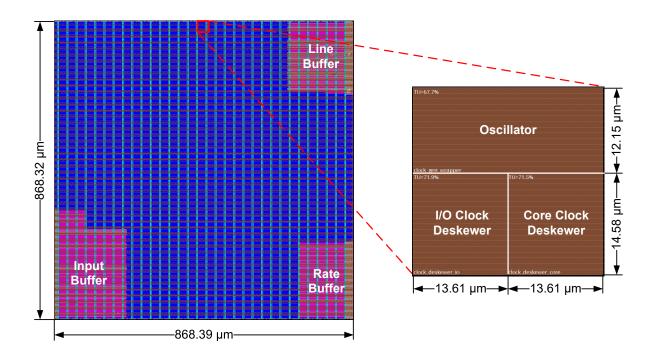

| 4.6  | DSC encoder core floorplan                                                             | 67  |

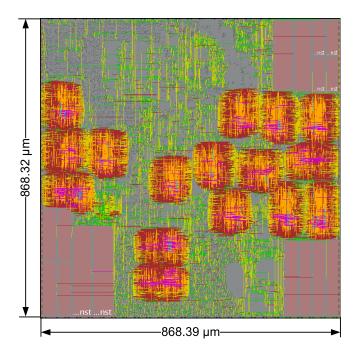

| 4.7  | DSC encoder core layout showing only the clock nets                                    | 67  |

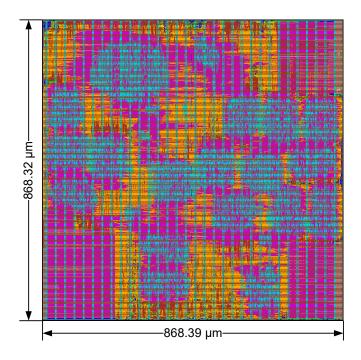

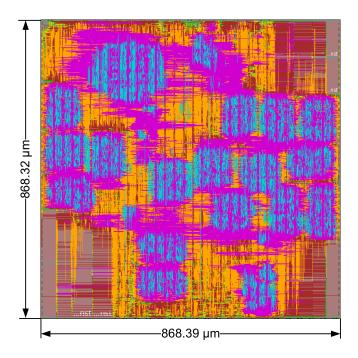

| 4.8  | DSC encoder core layout                                                                | 68  |

| 4.9  | DSC encoder core layout with power and ground nets hidden                              | 68  |

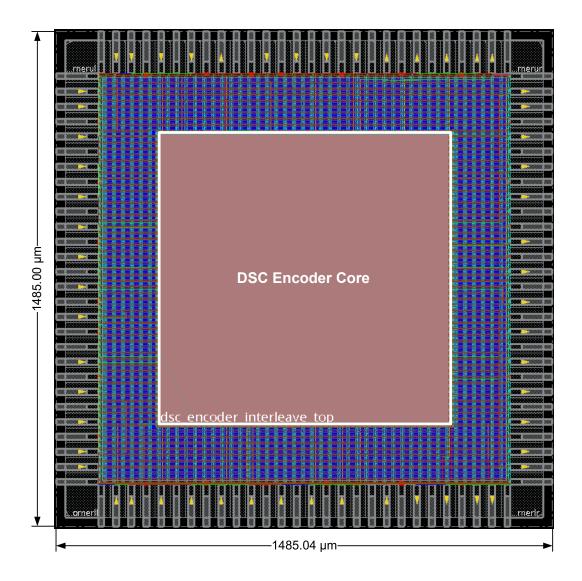

| 4.10 | DSC encoder chip layout                                                                | 69  |

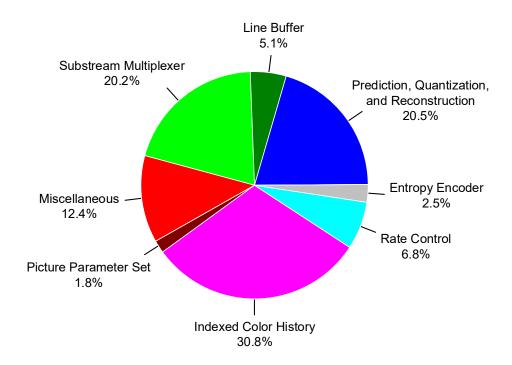

| 4.11 | DSC encoder core logic area breakdown                                                  | 70  |

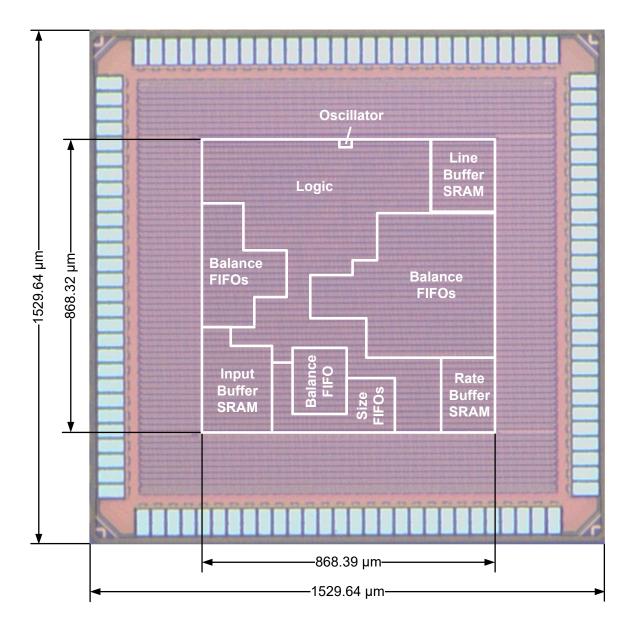

|      | DSC encoder chip die micrograph                                                        | 71  |

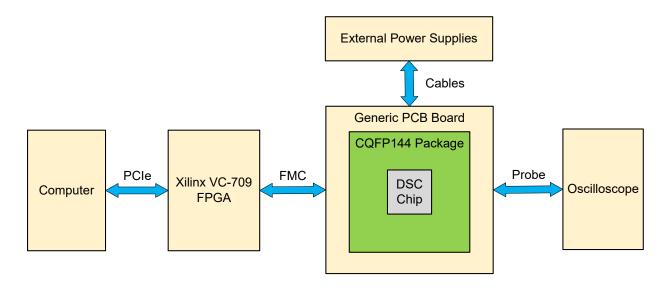

| 4.13 | Testing setup for the DSC encoder chip                                                 | 72  |

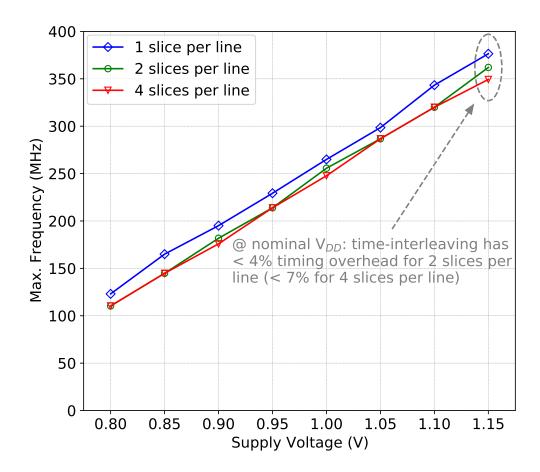

| 4.14 | Maximum core clock frequency versus supply voltage of the DSC encoder chip $$          | 73  |

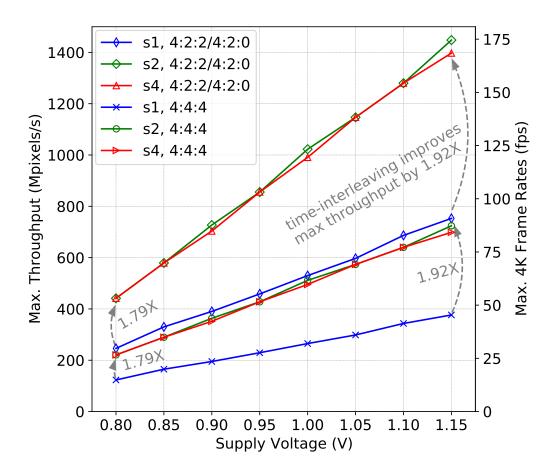

| 4.15 | Maximum throughput versus supply voltage of the DSC encoder chip                       | 74  |

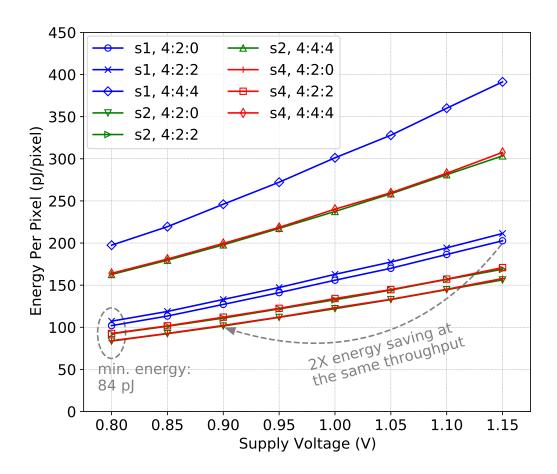

| 4.16 | Energy per pixel versus supply voltage of the DSC encoder chip                         | 75  |

| 4.17 | Multiple encoder instances scalability                                                 | 76  |

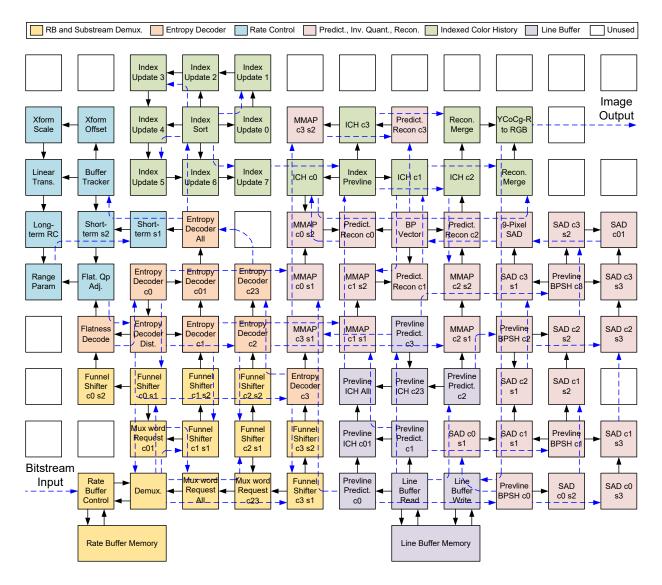

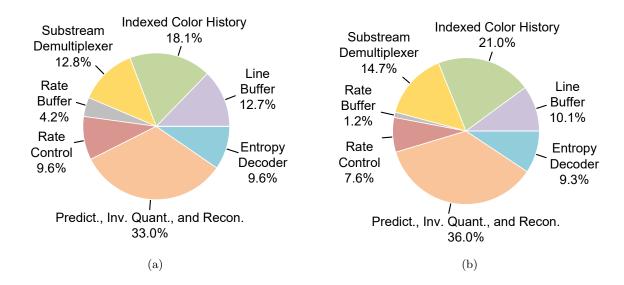

| 5.1  | Pipelined block diagram of the slice decoder                                           |     |

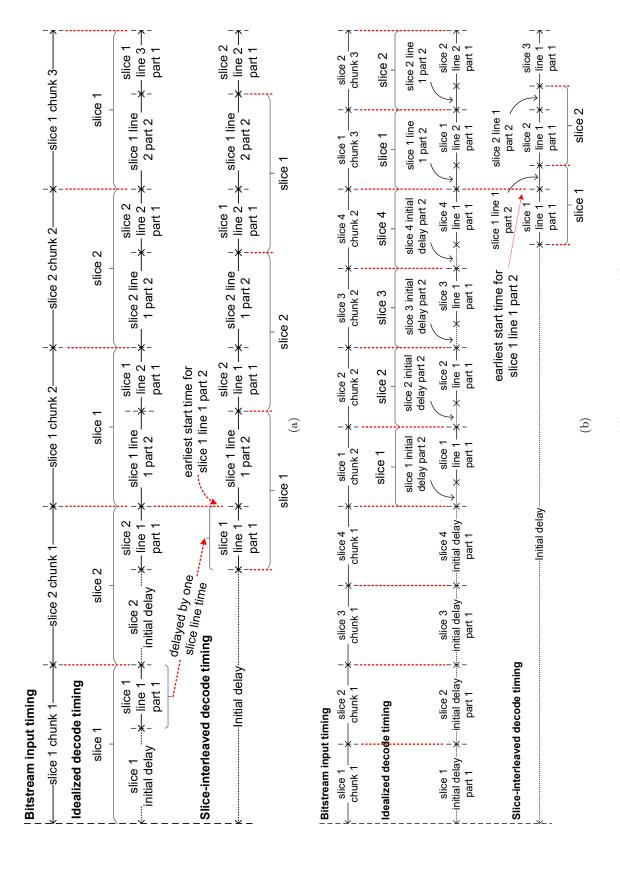

| 5.2  | Slice-interleaved decode timing for two and four slices per line                       | 84  |

| 5.3  | Parallel slice decoder architecture                                                    | 86  |

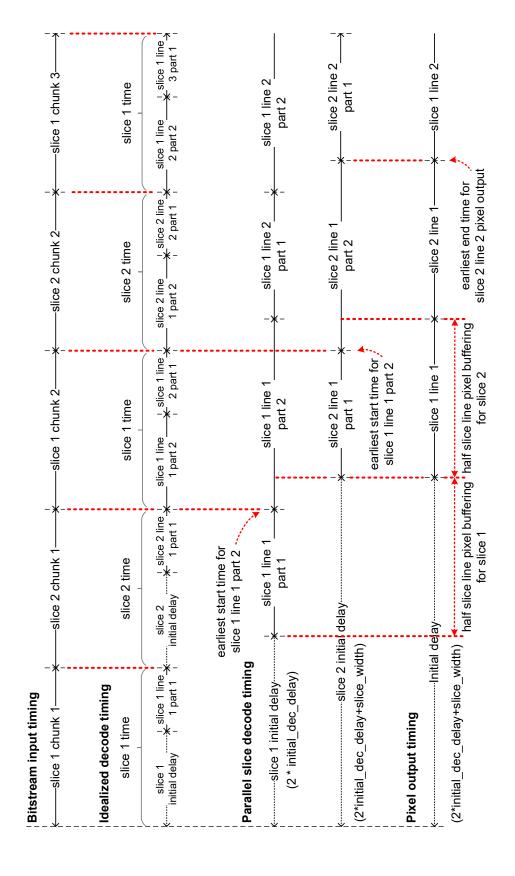

| 5.4  | Parallel slice decode timing for two slices per line                                   | 87  |

| 5.5  | Parallel slice decode timing for four slices per line                                  | 89  |

| 5.6  | Parallel-interleaved decoder architecture                                              | 91  |

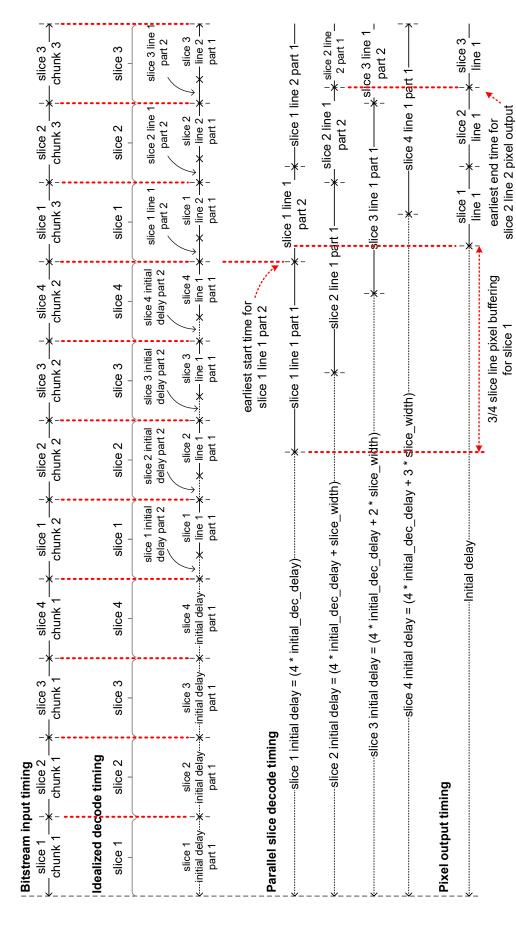

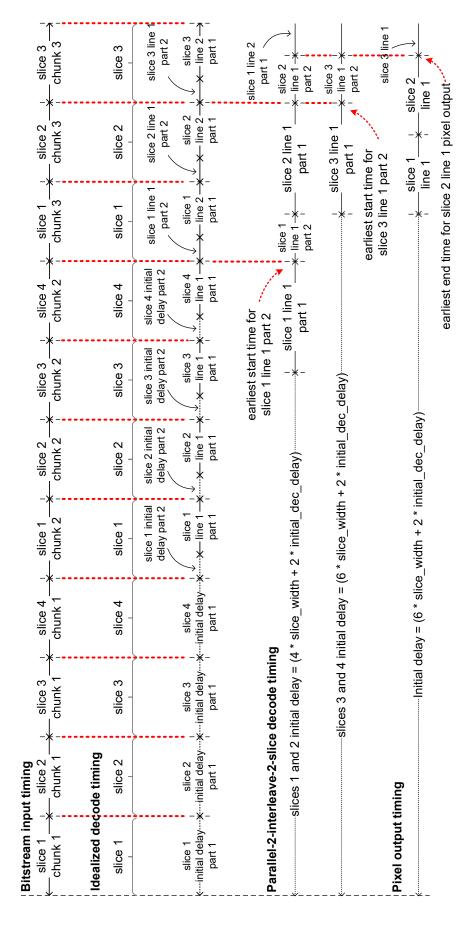

| 5.7  | Parallel-interleaved slice decode timing for four slices per line                      | 93  |

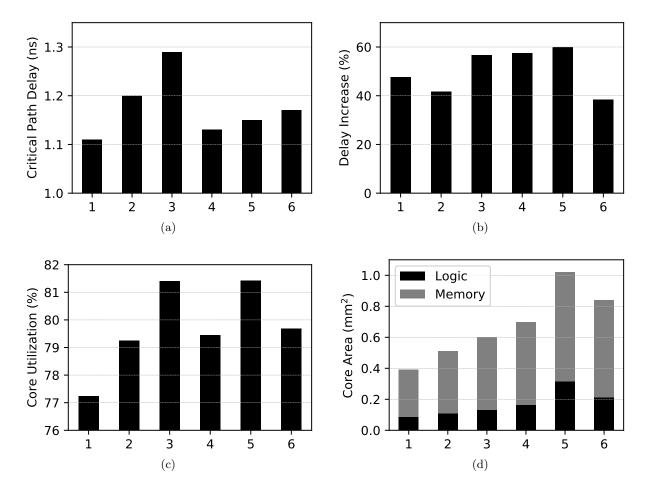

| 5.8  | Core layouts of the six implemented DSC decoders                                       | 96  |

| 5.9  | Comparison of the six implemented DSC decoders                                         |     |

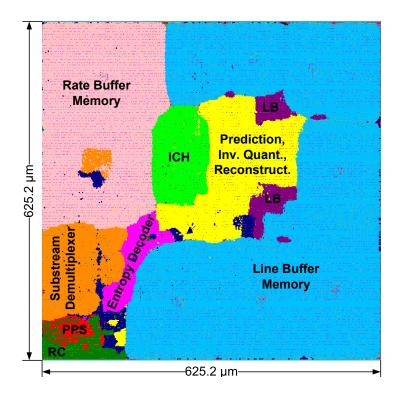

| 5.10 | Annotated layout of the slice decoder                                                  |     |

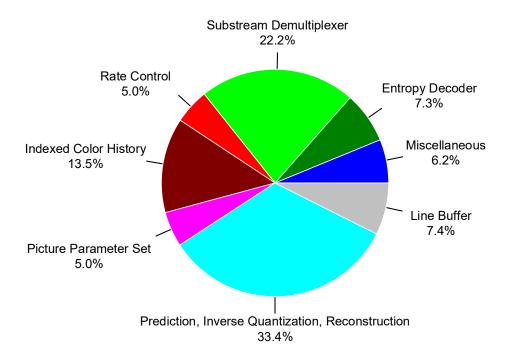

|      | Logic area breakdown of the slice decoder                                              | 99  |

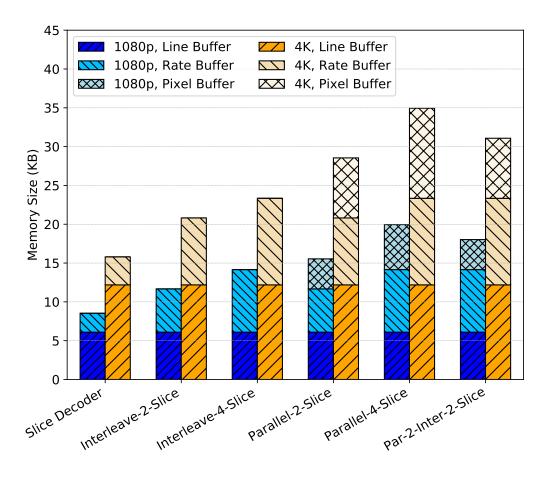

| 5.12 | Memory size requirements for 1080p and 4K                                              | 101 |

| 6.1  | Die photo and annotated layouts of the KiloCore chip                                   |     |

| 6.2  | Dataflow of the rate buffer, substream demultiplexer, and entropy decoder              |     |

| 6.3  | Dataflow of the rate control module                                                    |     |

| 6.4  | Line buffer storage for different pixel components                                     |     |

| 6.5  | Dataflow of the prediction, inverse quantization, reconstruction, ICH, and line buffer |     |

| 6.6  | Dataflow and processor mapping of the shift entry approach                             |     |

| 6.7  | Data dependency of the shift entry approach                                            |     |

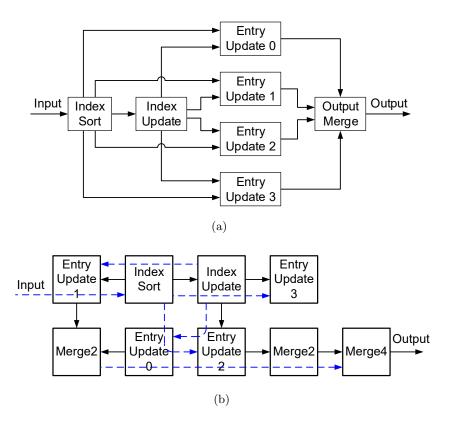

| 6.8  | Dataflow and processor mapping of the separate index and entry update approach .       |     |

| 6.9  | ICH index table update examples                                                        |     |

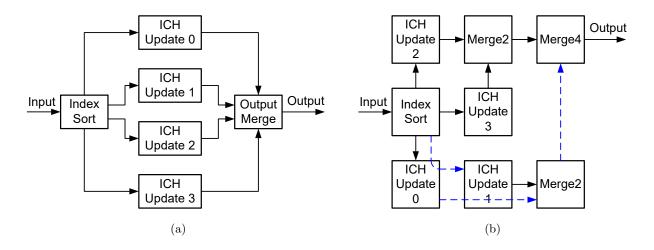

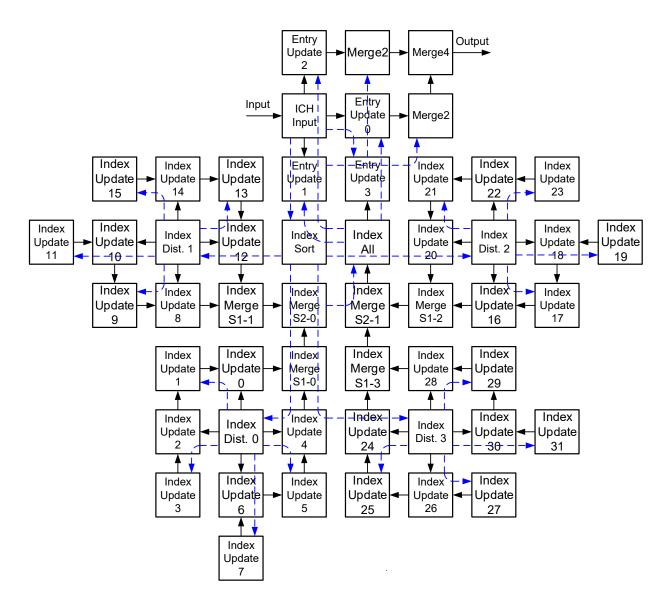

|      | Dataflow of the parallel index update approach                                         |     |

|      | Processor mapping of the parallel index update ICH designs                             |     |

|      | Processor mapping of the Parallel-Index-16 ICH design                                  |     |

|      | Processor mapping of the Parallel-Index-32 ICH design                                  |     |

|      | Throughput and frame rates of the many-core and i7 ICH designs                         |     |

|      | Throughput per unit chip area of the many-core and i7 ICH designs                      |     |

|      | Energy per 1080p frame of the many-core ICH designs                                    |     |

|      | Processor mapping of the slice decoder                                                 |     |

|      | Area and energy breakdown of the slice decoder                                         |     |

|      | Dataflow of the parallel slice decoder                                                 |     |

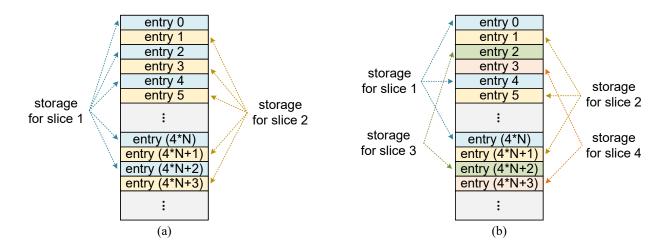

|      | Rate buffer and pixel buffer memory storage organization for parallel slice decoders . |     |

| 6.21 | Dataflow and processor mapping of the parallel-2-slice decoder                         | 129 |

| 6.22 | Dataflow and processor mapping of the parallel-4-slice decoder            |  | <br>130 |

|------|---------------------------------------------------------------------------|--|---------|

| 6.23 | Throughput versus voltage of the many-core software DSC decoders          |  | <br>132 |

| 6.24 | Throughput per area versus voltage of the many-core software DSC decoders |  | <br>133 |

| 6.25 | Energy per pixel versus voltage of the many-core software DSC decoders    |  | <br>134 |

| 6.26 | Energy per pixel versus throughput of the many-core software DSC decoders |  | <br>135 |

# List of Tables

| 3.1 | Size FIFO word width and depth              | 42  |

|-----|---------------------------------------------|-----|

| 4.2 | Binary code and gray code for 3-bit numbers | 63  |

| 5.1 | Comparison of the proposed DSC decoders     | 103 |

|     | Simulation voltages and frequencies         |     |

# Chapter 1

# Introduction

This chapter presents a brief overview of video coding and some state-of-the-art video coding standards. The research motivation and organization of this dissertation are also discussed.

## 1.1 Video Coding

#### 1.1.1 Overview

Video has been widely used in many applications, such as video recording and playback, video streaming, video conferencing, video surveillance, and so on. A video consists of a series of frames. Depending on the frame size, some common video resolutions include full high definition (Full HD) (1920×1080), 4K ultra-high-definition (UHD) (3840×2160), and 8K UHD (7680×4320). Uncompressed videos require very high data rates for real-time transmission and large space for storage. For example, 96 gigabits per second (Gbps) is required to transmit 8K videos with 8 bits per color component (bpc) at 120 frames per second (fps); 12 GB storage space is required to store one second of such uncompressed videos. Many applications reduce the size of video data through compression, which is achieved by encoding the uncompressed video data using video coding algorithms. The video data contain spatial redundancy within each frame and temporal redundancy between different frames. Video coding algorithms exploit ways to reduce the amount of redundancies which yields smaller data size to represent the video. Since lossless compression can only achieve very moderate compression ratio, practical video coding is mostly lossy which means the video data cannot be completely restored after compression and decompression.

#### 1.1.2 Video Coding Standards

Videos are compressed and decompressed based on standardized video coding algorithms. Some state-of-the-art video coding standards are discussed in this section.

The ITU-T and ISO/IEC standards have been widely used in daily lives. ITU-T developed the H.261 [1] standard in 1988 and the H.263 [2] standard in 1996, whereas ISO/IEC developed the MPEG-1 [3] standard in 1991 and the MPEG-4 Visual [4] standard in 1999. The two organizations jointly standardized the H.262/MPEG-2 Video [5] standard in 1995, the H.264/MPEG-4 Advanced Video Coding (AVC) [6] standard in 2003, the High Efficiency Video Coding (HEVC) [7] standard in 2013, and the newest Versatile Video Coding (VVC) [8] standard in 2020.

The VP8 [9] video coding standard was developed by On2 Technologies as a successor for its VPx codec family, which includes the VP3, VP4, VP5, VP6, and VP7 standards. VP8 was transferred to Google and open sourced in 2010. The standard was enhanced resulting in the next generation called VP9 [10]. AV1 [11] is the latest video coding standard of this series and was finalized by the Alliance for Open Media (AOMedia) in 2018.

The Joint Photographic Experts Group (JPEG) developed the Motion JPEG 2000 standard in 2001 and the JPEG XS standard [12] in 2019.

The Video Electronics Standards Association (VESA) has developed two display compression codecs: the Display stream compression (DSC) standard in 2014 and the VESA Display Compression-M (VDC-M) in 2018.

#### H.264/MPEG-4 Advanced Video Coding (AVC)

In March 2003, H.264/AVC [6] was finalized by the Joint Video Team (JVT), which was formed by the ITU-T Video Coding Experts Group (VCEG) and the ISO/IEC Moving Picture Experts Group (MPEG). Several extensions of H.264/AVC were developed between 2003 and 2009, such as the Scalable Video Coding (SVC) extension [13]. H.264 increases coding efficiency and is flexible for use over a broad variety of network types and application domains [14]. Its video coding layer uses the conventional block-based motion-compensated hybrid coding concepts with four important differences from its predecessors: 1) enhanced motion-prediction capability; 2) use of a small block-size exact-match transform; 3) adaptive in-loop deblocking filter; 4) enhanced entropy coding methods, which can achieve up to approximately 50% bit rate savings for equivalent

perceptual quality relative to the performance of prior standards [14]. H.264/AVC supports video resolution up to 8K UHD.

#### High Efficiency Video Coding (H.265)

High Efficiency Video Coding (HEVC) [7] is the successor of H.264/AVC and it is jointly standardized by the Joint Collaborative Team on Video Coding (JCT-VC) formed by the ITU-T VCEG and ISO/IEC MPEG standardization organizations. It was finalized in 2013. HEVC is also known as H.265 and MPEG-H Part 2. The main goal of HEVC is to enable significantly improved compression performance relative to existing standards—in the range of 50% bit-rate reduction for equal perceptual video quality [15]. In addition, it is designed to ease transport system integration and data loss resilience, as well as enable the implementation of parallel processing architectures [15]. HEVC addresses all applications of H.264/AVC with a focus on increased video resolution and increased use of parallel processing elements [15]. HEVC exploits temporal statistical dependencies via inter-picture prediction, spatial statistical dependencies via intra-picture prediction and transform coding of the residuals from prediction. The increased coding efficiency [16] yielded from the coding techniques comes at the cost of increased implementation complexity [17].

#### Versatile Video Coding (VVC)

Versatile Video Coding (VVC) [8] is the newest video coding standard finalized by the Joint Video Experts Team (JVET) of the ITU-T VCEG and ISO/IEC MPEG in July 2020. It is also known as H.266 and MPEG-I Part 3. VVC is designed to serve an ever-growing need for improved video compression as well as to support a wider variety of today's media content and emerging applications [18]. VVC achieves around 50% and 75% bit rate reduction over its predecessors HEVC and H.264/AVC, respectively [18]. VVC has a wide range of video applications, such as video with resolutions beyond standard- and high-definition, video with high dynamic range and wide color gamut, adaptive streaming with resolution changes, computer-generated and screen-captured video, ultra-low-delay streaming, 360° immersive video, and multi-layer coding [18].

#### AOMedia Video 1 (AV1)

AV1 is an open-source and royalty-free video coding standard developed by AOMedia. At the same video quality, AV1 achieves more than 30% bit rate reduction than its predecessor VP9 [19]. The AV1 format is already supported by many web platforms, including Android, Chrome, Microsoft Edge, and Firefox. It has also been used by web-based video service providers, including YouTube, Netflix, Vimeo, and Bitmovin [19].

#### JPEG XS

The JPEG XS standard is designed for inter-operable, visually lossless low-latency (from less than one line to maximum 32 lines of image) lightweight image compression that allows for low-complexity real-time implementation in application-specific integrated circuit (ASIC), field-programmable gate array (FPGA), central processing unit (CPU), and graphics processing unit (GPU) [12]. JPEG XS targets the following applications: 1) transport over video links and IP networks, 2) real-time video storage, 3) frame buffer compression, 4) omnidirectional video capture and rendering, and 5) sensor compression [20].

#### VESA Display Stream Compression (DSC)

The VESA DSC [21,22] video coding standard is widely accepted as a low-cost, visually lossless [23,24] codec for use in display links [25]. DSC was first introduced in 2014 as version 1.0, which was deprecated due to a bug that causes buffer overflow and was updated to DSC version 1.1 in 2015. DSC version 1.1 supports 4:4:4 pixels of 8 and 10 bits per component (bpc). DSC version 1.2 was published in 2016 with support for larger component bit depths (14 and 16 bpc) and YCbCr 4:2:2 and 4:2:0 pixels in native mode. The latest version 1.2a was published in 2017 which fixed the bug for 4:2:0 pixels in version 1.2. DSC compresses video data to as low as 8 bits per pixel (bpp), which yields three times compression for 24-bit color. DSC has been widely adopted by publicly known standards such as the DisplayPort and Embedded DisplayPort of VESA, High-Definition Multimedia Interface (HDMI), and Display Serial Interface (DSI).

#### VESA Display Compression-M (VDC-M)

The VDC-M standard was introduced by VESA in 2018. It can achieve higher compression (6 bpp) than DSC with increased hardware cost. Similar to DSC, VDC-M also provides visually lossless compression quality and targets applications such as low-power mobile computing. VDC-M has been adopted by the MIPI Display Serial Interface 2 (DSI-2).

#### 1.1.3 Compare DSC With Other Video Coding Standards

The VESA DSC video coding standard has four key attributes. First, DSC achieves visually lossless compression for various contents. Second, DSC uses a intra-frame, line-based coding algorithm, which results in very low latency for encoding and decoding. Third, DSC codecs can be implemented with low hardware costs. Since DSC performs intra-frame coding, it only requires a single picture line of buffering plus a small rate buffer, without the need of frame buffers. There is no computation intensive algorithms in DSC. Finally, DSC supports more color bit depths, including 8, 10, 12, 14, and 16 bpc.

Compared to the H.26x series of video coding standards, DSC achieves much lower hardware cost. The intra-only mode of these standards can be implemented with lower costs; however, they do not produce visually lossless quality for all contents. For example, the H.264/AVC intra-only mode can achieve visually lossless quality for most natural contents but is less effective with some content [25]. The screen content coding extension of HEVC (HEVC-SCC) [26] enhances the coding capability of HEVC for screen contents, but it has higher complexity compared to DSC [27]. The comparison between HEVC-SCC, VVC, AV1 and some other standards for their screen content coding capability is published [28].

Compared to Motion JPEG 2000, it does not achieve visually lossless quality for all types of content at 8 bpp with low hardware complexity for a real-time, high-throughput implementation [25]. The JPEG XS standard targets different set of applications which may not encounter certain types of content such as subpixel rendered text [25].

#### 1.2 Research Motivation

Many applications require transmission of video data over display links, such as digital televisions, extended display of computers, automotive video systems, mobile devices (e.g. smartphone, tablet), and augmented reality (AR) and virtual reality (VR) headsets. The video stream in digital televisions and extended displays is transmitted using digital cables. For mobile devices, the video captured by camera is transmitted to the display using internal wires.

Traditionally, uncompressed video data are transmitted over display links, since it results in best visual quality and the bandwidth of the physical layer is sufficient. However, as ultra-high-definition (UHD) video resolutions such as 4K UHD (3840×2160), 8K UHD (7680×4320) and beyond

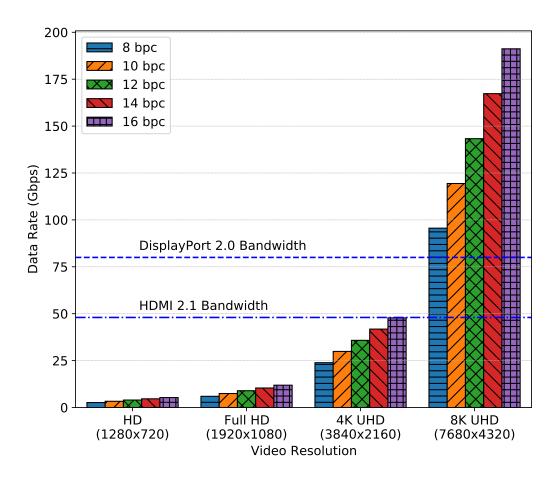

Figure 1.1: Uncompressed data rates for various video resolutions and component bit depths (8–16 bpc) at 120 frames per second.

are becoming prevalent (e.g., it is projected that 66% of connected flat-panel TV sets will be 4K [29]), the required data rate for transmitting uncompressed video dramatically increases. In addition, video frame rates such as 120 frames per second (fps) and beyond are more demanding. Moreover, new display technologies such as organic light emitting diode (OLED) and quantum dots have enabled wide color gamut (WCG) and high dynamic range (HDR) which motivates usage of higher color bit depth such as 10, 12, 14, and 16 bpc. As a result, the physical layer is no longer able to transmit raw video data. Figure 1.1 shows that the data rate increases exponentially with the increase of display resolution. Transmitting 8K UHD video at 120 fps requires 96 Gbps for 8 bpc and 191 Gbps for 16 bpc, which means two of the state-of-the-art display interfaces—DisplayPort (DP) 2.0 and High-Definition Multimedia Interface (HDMI) 2.1—are not able to support it.

To address the bandwidth disparity, one solution is to increase the physical layer bandwidth

by costly methods such as adding more wires and using more lanes. Although this approach can potentially fix the problem, there are several issues. First, adding more wires to display links can bring legacy compatibility issues. The existing devices may not be compatible with the new display link and thus huge costs will be incurred to upgrade the incompatible devices. Second, this solution increases power consumption. For mobile devices, higher power consumption means shorter battery life, which impacts user experience. Lastly, this approach is not scalable. The number of wires and lanes that can be added is limited. Even if it satisfies the current bandwidth demand, it will soon fall behind as the required data rate increases exponentially.

In contrast, a more compelling solution is to reduce the data rate by compressing the video data prior to transmission and decompressing them before display. As such, no hardware changes are needed to the current display links, and the pressure is alleviated without increasing power consumption. The Video Electronics Standards Association (VESA) has standardized the Display Stream Compression (DSC) [22,25] video coding standard to enable low-cost and low-latency hardware implementations of visually lossless video codecs over display links. DSC has been widely used in industry products. Specifically, DSC version 1.1 has been adopted by the Mobile Industry Processor Interface (MIPI) Alliance's Display Serial Interface (DSI) 1.2, DSI-2 1.0, and VESA Embedded DisplayPort (eDP) 1.4b; DSC version 1.2a has been adopted by HDMI 2.1, VESA DP 2.0, and VESA eDP 1.4b [30]. Thanks to the compression provided by DSC, HDMI 2.1 supports transmission of 4K at 120 fps and 8K at 60 fps.

There are some commercial DSC codecs available, such as the Hardent DSC IP cores [31]; however, the architecture details and performance results are not publicly available. A published DSC decoder design [32] focuses on optimizing the line buffer but does not include detailed architectures or post-layout results. Moreover, there are no existing work that demonstrates DSC codecs with measured data from silicon.

This dissertation investigates the design of DSC version 1.2a codecs (i.e., encoders and decoders) from the perspective of hardware architectural design, physical chip design, and fine-grained many-core software design. First, three hardware architectures are proposed for DSC encoders: a slice encoder architecture, a slice-interleaved encoder architecture, and a time-interleaved encoder architecture. A DSC encoder chip based on the time-interleaved architecture is designed and fabricated in TSMC 28 nm CMOS technology. Second, this dissertation discusses the design of

DSC decoders in two approaches: 1) application-specific integrated circuits (ASIC) design, and 2) software design on fine-grained multiple instruction multiple data (MIMD) many-core processor arrays. Four hardware architectures are proposed for the ASIC DSC decoders: a slice decoder architecture, a slice-interleaved decoder architecture, a parallel slice decoder architecture, and a parallel-interleaved decoder architecture. The many-core software design of the slice decoder and parallel slice decoders are discussed.

The proposed slice-interleaved encoder architecture, time-interleaved encoder architecture, and the slice-interleaved decoder architecture share computational logic and replicate only registers for different slices, which results in reduced hardware cost. The time-interleaved encoder architecture achieves increased throughput by utilizing idle cycles to process different slices. The parallel slice decoders achieve linearly increased throughput using replicated slice decoders which yields linearly increased area cost. The many-core software decoders demonstrate that fine-grained MIMD many-core computation platforms can achieve significant better performance and energy efficiency than coarse-grained general purpose processors. The ASIC decoders outperform the many-core software decoders in both performance and energy efficiency.

# 1.3 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter 2 provides a comprehensive overview of the VESA Display Stream Compression (DSC) video compression standard, focusing on the encoding and decoding algorithm. Chapter 3 presents three hardware architectures for DSC encoders. Chapter 4 discusses the design and measured results of a fabricated DSC encoder chip that supports real-time processing of 4K video resolution. Chapter 5 proposes four hardware DSC decoder architectures and physical design of six DSC decoders that are implemented based on the proposed architectures. Chapter 6 discusses the software design of DSC decoders for fine-grained many-core processor arrays. Chapter 7 concludes the dissertation and proposes future work.

# Chapter 2

# Display Stream Compression (DSC) Standard

This chapter overviews the VESA Display Stream Compression (DSC) standard [22], focusing on the system-level usage, concepts, and coding algorithms. A thorough analysis of the encoding and decoding processes is provided.

#### 2.1 Overview

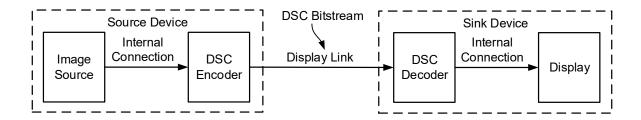

Figure 2.1 illustrates DSC usage in end-to-end systems, which consists of a source device, a display link, and a sink device. In the source device, an image source captures raw video data and sends them to the DSC encoder via an internal connection. The DSC encoder compresses the video data into a bitstream and sends it to the sink device over the display link. In the sink device, the DSC decoder receives the bitstream and decompresses it into raster-scan-ordered pixels, which are sent to a display through an internal connection. The display link can be either wired or wireless. Examples of the wired display links are MIPI Alliance's Display Serial Interface (DSI) Specification, DisplayPort (DP), Embedded DisplayPort (eDP), and High-Definition Multimedia Interface (HDMI).

DSC uses a line-based intra-picture video coding algorithm, which requires only current line and previous line reconstructed pixels, resulting in very low encoding and decoding latency. The main storage of DSC consists of a line buffer that stores one picture line of pixels, and a rate buffer that converts varying number of bits into constant bit rate. Unlike many other video coding

Figure 2.1: DSC usage in end-to-end systems [22].

Figure 2.2: YCbCr 4:2:2 pixels packed into virtual 4:4:4:4 containers in native 4:2:2 mode. Odd-position luma (Y1, Y3, Y5) is treated as the fourth independent component in a container pixel.

standards, no off-chip memory is needed in DSC. As a result, DSC codecs can be implemented with very low hardware cost.

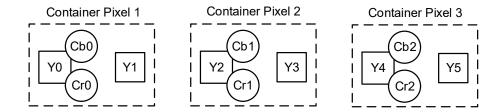

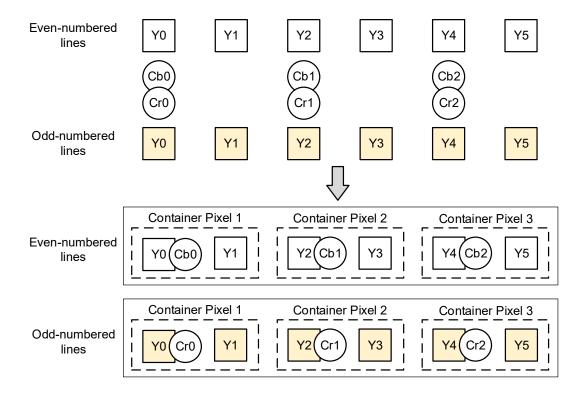

DSC version 1.1 supports 8, 10, and 12 bits per component (bpc); DSC versions 1.2 and 1.2a also support 14 and 16 bpc. All DSC versions support 4:4:4 pixels in both RGB and YCbCr formats. A YCbCr 4:4:4 pixel contains three *components*: one luma component (Y) and two chroma components (Cb and Cr). DSC version 1.1 supports YCbCr 4:2:2 pixel in *simple* mode only, where 4:2:2 pixels are upsampled to 4:4:4 format before encoding and downsampled to 4:2:2 after decoding. DSC versions 1.2 and 1.2a also support YCbCr 4:2:2 in *native* mode, in which two neighboring pixels are packed into a virtual, half-width 4:4:4:4 container and the even- and odd-position luma are treated as independent components, as shown in Figure 2.2. DSC version 1.2a adds support for YCbCr 4:2:0 pixel format in *native* 4:2:0 mode, in which two neighboring pixels are packed into a virtual, half-width 4:4:4 container the even- and odd-position luma are treated as independent components, as shown in Figure 2.3. The width of pictures and slices are effectively halved in native 4:2:0 and 4:2:2 modes.

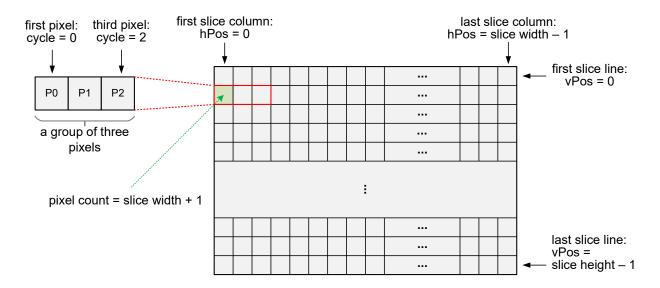

In DSC, a *picture* is defined as a frame for progressive format videos or a field for interlaced format videos. A picture is partitioned into one or more non-overlap rectangular identical-sized regions called *slices*, where each slice is independently coded. The number of columns of slices per

Figure 2.3: YCbCr 4:2:0 pixels packed into virtual 4:4:4 containers in native 4:2:0 mode. Odd-position luma (Y1, Y3, Y5) is treated as a independent component in the container pixel. Even-and odd-numbered lines contain Cb and Cr in the chroma, respectively.

picture is called the number of *slices per line*. A slice consists of a set of *groups*, each of which is consecutive (container) pixels of the same slice line. If slice width is not evenly divisible by three, the last group of each slice line contains fewer than three pixels and is called a *partial group*. Figure 2.4 shows some example slice configurations of a picture. In case the picture width is not evenly divisible by slice width, the rightmost column of slices extends beyond the right boundary of the picture and the value of the last pixel of each slice line is replicated for pixels outside the picture boundary. If the picture height is not evenly divisible by the slice height, the bottom rows of slices extend beyond the bottom of the picture, and midpoint values of each component are used for these regions. To minimize the amount of extra data to be sent over display links, it is desirable to choose configurations for which the picture width and height are evenly divisible by slice width and height, respectively.

The DSC algorithm is designed to allow encoders and decoders to be implemented with a throughput of one and three pixels per cycle, respectively. The throughput per pixel in native 4:2:0 and 4:2:2 modes are effectively doubled compared to simple 4:4:4 mode, since two pixels are

Figure 2.4: Example of pictures configured into: (a) one row and one column of slice; (b) one row and two columns of slices; (c) one row and four columns of slices; (d) two rows and one column of slices; (e) two rows and two columns of slices; (f) two rows and four columns of slices.

packed into one container. To achieve higher throughput, the DSC algorithm is easily parallelized by configuring pictures to more than one slice per line and processing each column of slices of a picture (Figure 2.4) with a separate instance of an encoder or decoder.

DSC uses a 128-byte picture parameter set (PPS) to store configuration information. PPS contains the information of DSC version, pixel format and color bit depth, specified bit rate, rate control parameters, and so on. Identical PPS should be used in the encoder and the decoder to ensure correct decoding; therefore, the encoder must communicate PPS to the decoder.

# 2.2 DSC Encoding Algorithm

#### 2.2.1 DSC Encoding Process

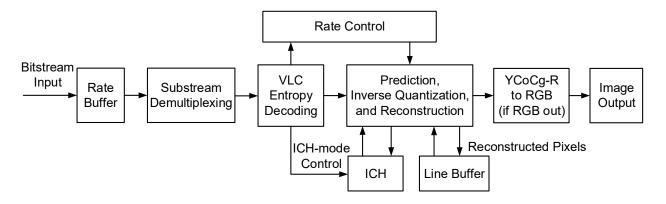

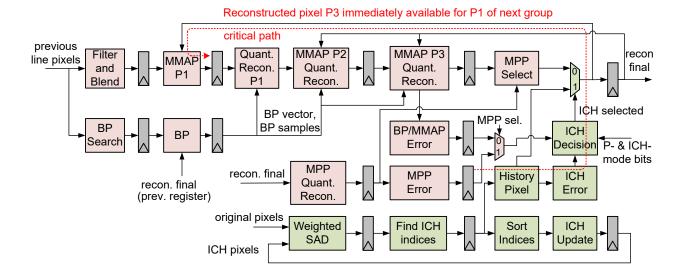

Figure 2.5 illustrates the DSC encoding process. RGB input image data are converted to reversible YCoCg (YCoCg-R) [33] format before further encoding. A pixel buffer stores a small number of original pixels for look-ahead flatness determination. The encoding process is performed on a group basis, and every group is coded in either predictive coding mode (P-mode) or indexed

Figure 2.5: DSC encoding process [22].

color history (ICH) coding mode (ICH-mode). For P-mode-coded groups, the samples are predicted with one of three predictors: modified median-adaptive prediction (MMAP), block prediction (BP), and midpoint prediction (MPP). Residuals, each of which is calculated by subtracting the predicted value from the original value, are quantized before being coded in entropy encoder. Reconstruction is performed by adding the inverse quantized residual to the predicted value. ICH keeps a record of 32 recently reconstructed pixels, each of which is addressed by a 5-bit index. If ICH-mode is selected, the best-matched ICH pixel is selected for each pixel in current group, and the three indices of the selected entries are coded in entropy encoder. The final reconstructed pixels are stored in the line buffer and used for MMAP and ICH in the next slice line. The variable length coding (VLC) entropy encoding codes P-mode groups using delta size unit-variable length coding (DSU-VLC) scheme, and ICH-mode groups using ICH coding with a special escape code. Rate control algorithm manages the rate buffer fullness and dynamically adjusts the quantization parameter (Qp) in every group to maximize perceived quality. If the upcoming pixels are flat, the Qp is dropped quickly. Substream multiplexing combines the three or four substreams into a single bitstream. The rate buffer converts a variable number of bits input which are used to code each group into a constant rate bitstream output, which is specified as bits per pixel (bpp) in the PPS.

#### 2.2.2 Color Space Conversion

DSC can accept both RGB or YCbCr color space inputs. RGB pixels are converted into YCoCg-R format, where chroma (Co and Cg) use one more bit than luma (Y) except in 16 bpc, where the least significant bit (LSB) is rounded off. YCbCr inputs are accepted without color space conversion; Cb and Cr are mapped to Co and Cg labels, respectively; Cb and Cr has the same bit depth as Y. The conversion is defined as follows [22]:

$$cscCo = R - B \tag{2.1}$$

$$t = B + (cscCo >> 1) \tag{2.2}$$

$$cscCg = G - t (2.3)$$

$$Y = t + (cscCq >> 1) \tag{2.4}$$

Where:

- t is a temporary value.

- cscCo and cscCg are the intermediate values for Co and Cg, respectively.

- Y is value of the luma component.

The Co and Cg values are centered around the midpoint for 8, 10, 12, or 14 bpc:

$$Co = cscCo + (1 << bits\_per\_component)$$

(2.5)

$$Cg = cscCg + (1 << bits\_per\_component)$$

(2.6)

For 16 bpc, Co and Cg are rounded to 16 bits before centering around the midpoint:

$$Co = MIN(0xFFFF, ((cscCo + 1) >> 1) + 0x8000$$

(2.7)

$$Cg = MIN(0xFFFF, ((cscCg + 1) >> 1) + 0x8000$$

(2.8)

#### 2.2.3 Prediction, Quantization, and Reconstruction

DSC uses three predictors: modified median-adaptive prediction (MMAP), block prediction (BP), and midpoint prediction (MPP), all of which are required for encoders. Every component of a group is predicted using one of the predictors. However, encoders can choose to disable BP if the decoder does not support it, or BP does not benefit the coding contents. In native 4:2:0 mode, BP applies to only luma components, and chroma components always select MMAP or MPP. In predictive coding (P-mode), a predicted value is calculated for each sample using the one of the three predictors, which is subtracted from the original sample value to produce the residual. The

Figure 2.6: Pixels used in MMAP of current group pixels (p0, p1, p2), modified from [22, Figure 6-1].

residuals are quantized and entropy-coded in the bitstream. Reconstruction produces the same reference pixels for prediction and ICH in encoders and decoders.

#### Modified Median-Adaptive Prediction (MMAP)

MMAP is the default prediction method in DSC. It predicts the current group using the reconstructed pixel values from the previous group and previous line that is above the current group. Figure 2.6 shows the pixels that are used in MMAP for the current group.

A horizontal low-pass filter [0.25, 0.5, 0.25] is applied to the previous line samples (c, b, d, e) in Figure 2.6) and produces filtered values  $(filter\_c, filter\_b, filter\_d, and filter\_e)$ . For example,

$$filter_c = (g + 2 * c + b + 2) >> 2$$

(2.9)

In the first group of each slice line, g and c are outside the left boundary of the slice and both of them use the same value of pixel b. For the last group of each slice line, pixel f is outside the right boundary of the slice and it uses the value of pixel e.

The filtered values are blended with the original pixel values and produce blended values  $(\tilde{c}, \tilde{b}, \tilde{d}, \text{ and } \tilde{e})$ . In the first group of each slice line, a and  $\tilde{c}$  are set to the midpoint of the component. For example,

$$\tilde{c} = c + CLAMP(filter_c - c, -((1 << qlevel)/2), ((1 << qlevel)/2))$$

(2.10)

where:

- *glevel* is the quantization level

- $\bullet$  *CLAMP* function is defined as:

$$CLAMP(x, min, max) = \begin{cases} min, & \text{if } x < min. \\ x, & \text{if } min \le x \le max. \\ max, & \text{if } x > max. \end{cases}$$

(2.11)

Figure 2.7: Block prediction example with BP vector of -10. The three pixels in current group p0, p1, and p2 are predicted as r[-10], r[-9], and r[-8], respectively.

The three pixels are predicted as:

$$p0 = CLAMP(a + \tilde{b} - \tilde{c}, MIN(a, \tilde{b}), MAX(a, \tilde{b}))$$

(2.12)

$$p1 = CLAMP(a + \tilde{d} - \tilde{c} + R0, MIN(a, \tilde{b}, \tilde{d}), MAX(a, \tilde{b}, \tilde{d}))$$

(2.13)

$$p2 = CLAMP(a + \tilde{e} - \tilde{c} + R0 + R1, MIN(a, \tilde{b}, \tilde{d}, \tilde{e}), MAX(a, \tilde{b}, \tilde{d}, \tilde{e}))$$

(2.14)

where:

- R0 is the inverse quantized residual of the first sample in the group

- R1 is the inverse quantized residual of the second sample in the group

- MIN and MAX return the minimum and maximum values, respectively

For the first line (and the second line of chroma in native 4:2:0 mode) of a slice, there are no previous line pixels and the samples are predicted as follows  $(cpnt\_bit\_depth)$  is the bit depth of the component and  $((1 << cpnt\_bit\_depth) - 1)$  is the maximum value of the component).

$$p0 = a \tag{2.15}$$

$$p1 = CLAMP(a + R0, 0, ((1 << cpnt\_bit\_depth) - 1))$$

(2.16)

$$p2 = CLAMP(a + R0 + R1, 0, ((1 << cpnt\_bit\_depth) - 1))$$

(2.17)

The MMAP of p1 and p2 depends on the inverse quantized residual of pixels to their left, i.e., p0 and p1, respectively. Therefore, MMAP of p1 and p2 must wait until the prediction, quantization, and inverse quantization of p0 and p1 finish, respectively. In general, this data dependency limits the throughput of DSC encoders to not more than one pixel per cycle.

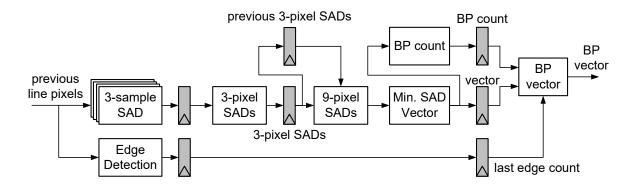

#### **Block Prediction**

Block prediction (BP) predicts the samples of the current group using reconstructed pixel values of previous groups in the current slice line. The offset from current sample to the pixel used for BP is called the BP vector, which is between -3 and -10; therefore, the three pixels within a

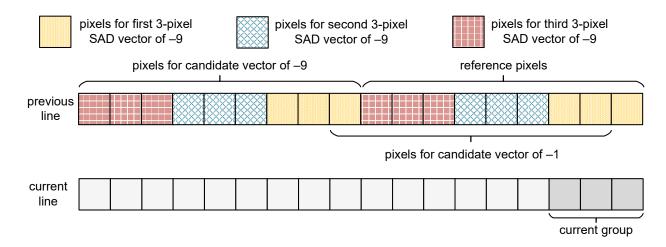

Figure 2.8: Pixels used in 3-pixel and 9-pixel sum of absolute differences (SAD) calculation for BP search. Current line pixels are not used in this calculation.

group can be predicted in parallel. Figure 2.7 shows an example of block prediction with BP vector of -10. BP helps improve the rendered quality of repeated patterns such as zone plates [25]. The selection of BP is for all pixels of all components in the group, except that BP in native 4:2:0 mode applies only to luma components, and chroma always select MMAP over BP.

#### **Midpoint Prediction**

The purpose of Midpoint prediction (MPP) is to limit the size of the quantized residuals to no larger than the quantized sample depth, i.e., the difference between the component bit depth (cpnt\_bit\_depth) and quantization level (qlevel). MPP predicts the sample as a value around the midpoint of the component, in which the qlevel number of LSBs are copied from the reconstructed value of the rightmost pixel in the previous group (prev\_recon).

$$p = (1 << (cpnt\_bit\_depth - 1)) + (prev\_recon \& ((1 << qlevel) - 1))$$

(2.18)

#### **Prediction Mode Selection**

The decision between MMAP and BP is made once per group and only uses the reconstructed pixel values from the previous line, which means the decision can be made by up to one slice line pixel time in advance.

To determine the BP vector, the encoder calculates 9-pixel sum of absolute differences (SAD) between the reference pixels and the pixels to the left, in which nine candidate vectors

(-1, -3, -4, -5, -6, -7, -8, -9, -10) are considered. Figure 2.8 shows the pixels used for calculating the 3-pixel SADs for candidate vector of -9. The 9-pixel SAD is calculated as the sum of three 3-pixel SADs, which are calculated by adding the 6-bit modified absolute differences between reference samples and the samples in the candidate vectors. In native 4:2:0 mode, only luma samples are included in the sum, whereas all samples are included in the sum for other modes. The modified absolute difference  $(modified\_abs\_diff)$  is computed by reducing the bit width of the absolute difference  $(abs\_diff)$  to six bits.

$$modified\_abs\_diff = MIN(abs\_diff >> (cpnt\_bit\_depth - 7), 0x3F)$$

(2.19)

Three 10-bit 3-pixel SADs are clamped to nine bits and added together to form a 11-bit 9-pixel SAD, three LSBs of which are truncated. The vector with the smallest SAD is used as the BP vector. If BP vector is -1, MMAP is selected for this group and the BP counter is reset to zero; otherwise BP counter increases by one if the current group is not the first three groups of the slice line. Block prediction is selected if current group is not a partial group, and BP counter is at least equal to three, and less than three pixels have passed since an edge occurred.

The size of quantized residuals of BP/MMAP are calculated. If the maximum size is greater than or equal to the quantized sample depth, MPP is used for the component. In addition, the encoder is forced to select MPP to produce a minimum data rate that avoids rate buffer underflow.

#### Quantization, Inverse Quantization, and Reconstruction

The residual (residual) is produced by subtracting the predicted sample value (pred\_sample) from the original sample value (orig\_sample). Quantized residuals (quantized\_residual) are controlled by the quantization level (qlevel) and are calculated as follows:

$$residual = oriq\_sample - pred\_sample$$

(2.20)

$$round = MAX(0, (1 << qlevel)/2 - 1)$$

(2.21)

$$quantized\_residual = \begin{cases} (residual + round) >> qlevel, & \text{if } residual \ge 0. \\ -((-residual + round) >> qlevel), & \text{if } residual < 0. \end{cases}$$

$$(2.22)$$

Inverse quantization is performed by shifting the quantized residual ( $quantized\_residual$ ) to the left by quantization level (qlevel) number of bits:

$$inverse\_quantized\_residual = quantized\_residual << qlevel$$

(2.23)

Reconstructed samples are calculated by adding the inverse quantized residual to the pre-

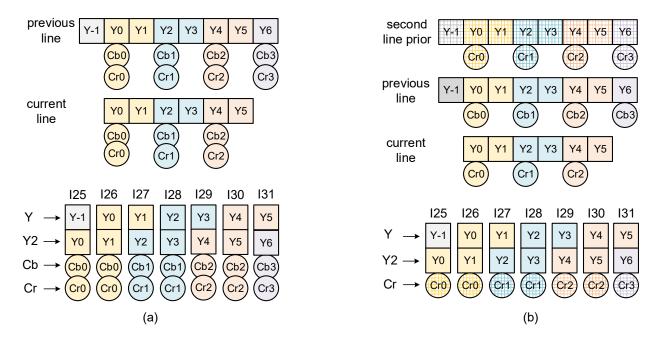

Figure 2.9: ICH entries pointing to previous line. (a) Native 4:2:2 mode. (b) Native 4:2:0 mode.

dicted value ( $pred\_sample$ ), and bound to zero and maximum value of the component ( $max\_value$ ).  $recon\_sample = CLAMP(pred\_sample + inverse\_quantized\_residual, 0, max\_value)$  (2.24)

#### 2.2.4 Indexed Color History (ICH)

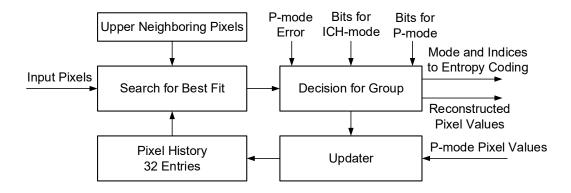

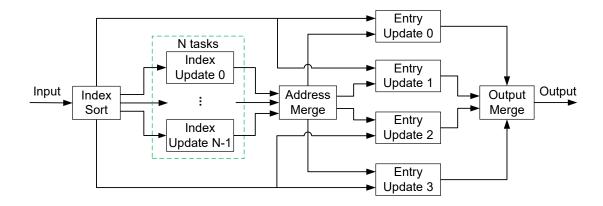

ICH maintains 32 entries of recently reconstructed pixels (container pixels in native modes) from predictive coding. All 32 entries are actual history pixels for the first line (and second line in 4:2:0 mode) of each slice; otherwise, only the first 25 entries are actual history pixels and the last seven entries point to reconstructed pixel values in the previous line. In 4:4:4 mode, the seven ICH pixels in the previous line are centered around the horizontal position of current group. Figure 2.9 shows the ICH entries pointing to the previous line in native 4:2:2 and 4:2:0 modes. ICH is helpful in coding contents that have similar pixel values appearing in close positions, such as computer-generated text and graphics. Figure 2.10 shows the ICH in the encoder, which consists of three steps: 1) search for the best ICH entries; 2) decide between ICH-mode and P-mode; and 3) update the ICH entries.

In every group, the encoder searches over the 32 ICH entries and finds the best match for each pixel of the group based on smallest weighted SAD between the original pixels and ICH pixels

Figure 2.10: Indexed color history in the DSC encoder [22].

over all components. The weight  $(w_c)$  is equal to two for luma and one for chroma.

$$weighted\_sad = \sum_{c} w_c * |orig_c - ich_c|$$

(2.25)

In case multiple indices have the smallest weighted SAD, the smallest index is selected for the pixel.

After the best ICH entries have been found for each pixel, the encoder decides between ICH-mode and P-mode, in which two factors are considered for ICH-mode to be selected: 1) for each pixel in the group, at least one ICH entry should exist such that the absolute difference between the pixel and the ICH entry of every component is within a threshold; 2) the rate-distortion (RD) cost of ICH-mode should be smaller than P-mode and and distortion of ICH-mode should also be less than P-mode if the next group is very flat. RD is the sum of the log2 of the maximum component-wise errors, whereas the total cost for ICH- and P-mode are the sum of the total number of bits used in that mode and the value of RD multiply by four.

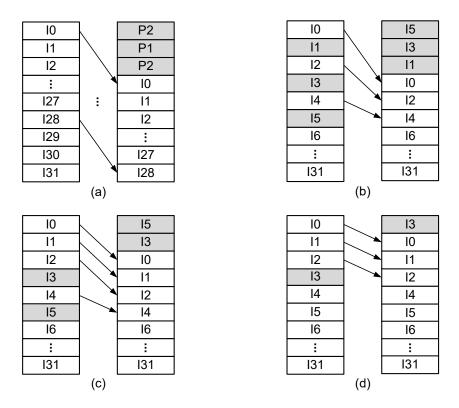

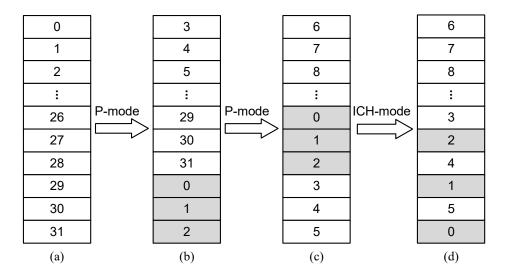

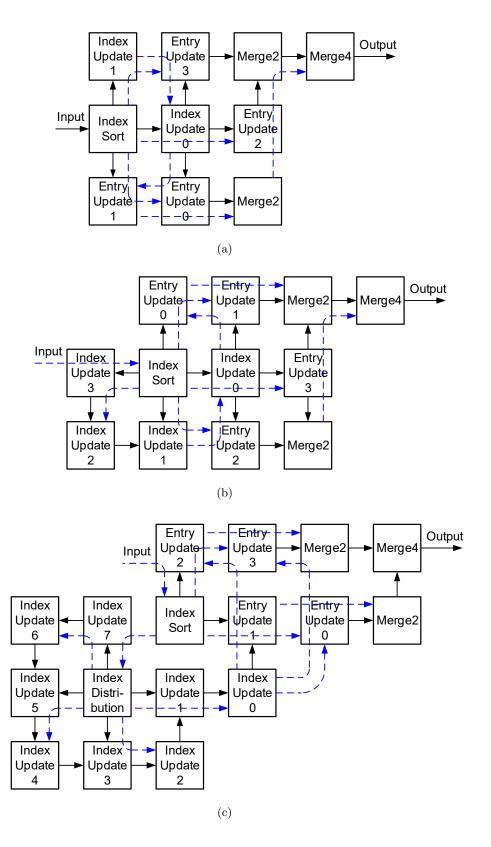

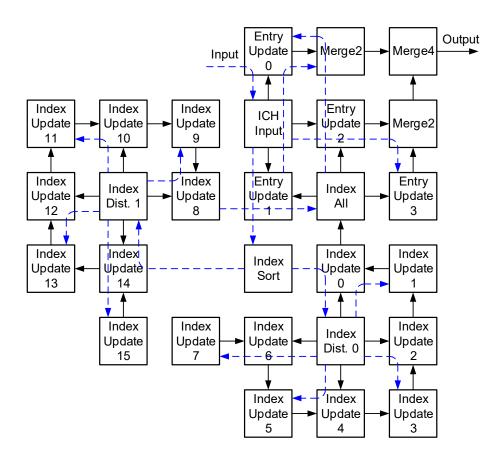

With the coding mode selected, the ICH is updated at the end of the group time. Figure 2.11 shows an example of updating the ICH records in both P-mode and ICH-mode. In P-mode, the reconstructed pixels of the current group, denoted as P0, P1, and P2 from left to right, enter the top of the ICH. All other entries are shifted down by three, as shown in Figure 2.11(a). In ICH-mode-coded groups, the selected ICH entries are moved to the top of the ICH. In Figure 2.11(b), the selected indices are 1, 3, and 5 for the left, middle, and right pixels, respectively. Therefore, I5 becomes the MRU, while I3 is moved to the second entry and I1 is moved to the third entry. The original entries I0, I2, and I4 are shifted down by three, two, and one, respectively, while other entries remain unchanged. When the number of unique indices is less than three, as shown in Figure 2.11(c-d), only the last occurrence of a replicated index is counted in ICH update.

Figure 2.11: ICH update examples. (a) P-mode. (b) ICH-mode with indices (1, 3, 5). (c) ICH-mode with indices (5, 3, 5). (d) ICH-mode with indices (3, 3, 3).

#### 2.2.5 Line Buffer

Line buffer stores the reconstructed pixel values of the previous line, which are used in ICH, BP search, and MMAP. The storage is one slice line per column of slices; therefore, the total storage requirement is one picture line of pixels, regardless of the number of slices per line.

In DSC, the decoder might use a bit depth that is smaller than the component's bit depth  $(cpnt\_bit\_depth)$  to reduce implementation cost. In this case, the decoder should communicate the maximum bit depth that it supports and the encoder should configure the  $linebuf\_depth$  in the PPS accordingly. The bit-width of the stored samples values  $(stored\_sample)$  in the line buffer is reduced as follows:

$$shift = MAX(0, cpnt\_bit\_depth - linebuf\_depth)$$

(2.26)

$$round = (shift > 0) ? (1 << shift - 1)) : 0$$

(2.27)

$$stored\_sample = MIN((sample + round) >> shift, (1 << linebuf\_depth) - 1)$$

(2.28)

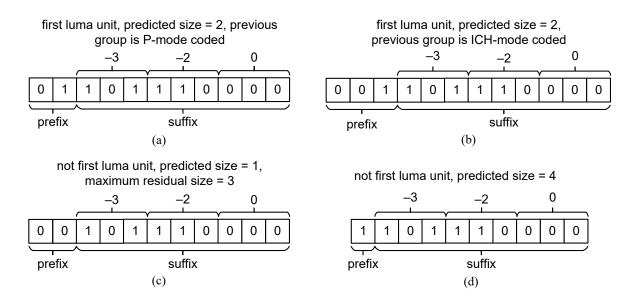

Figure 2.12: Examples of DSU-VLC codes with quantized residuals of (-3, -2, 0) coded in the suffix using 2's complement. (a) The first luma unit and prefix indicates size increase of one. (b) The first luma unit and prefix uses two "0" bits to indicate size increase of one since the previous group is coded with ICH-mode. (c) Not first luma unit, the trailing "1" bit is omitted since the maximum residual size of the group is equal to maximum residual size of the component. (d) Not first luma unit, the predicted size is larger than the actual size of the quantized residuals, a single "1" bit in the prefix indicates no change in size.

The sample value that is read from the line buffer should be shifted to the left.

$$read\_sample = stored\_sample << shift$$

(2.29)

#### 2.2.6 VLC Entropy Encoding

DSC uses delta size unit-variable length coding (DSU-VLC) for groups coded with P-mode, and indexed color history coding for ICH-mode-coded groups. The bits used to code each component of a group form a *syntax element*.

For every component of P-mode-coded groups, a residual size prediction and adjustment is performed using the change of quantization level from previous group to current group, and the size of quantized residuals ( $required\_size$ ) of the same component from the most-recent P-mode group.  $predicted\_size = (required\_size[0] + required\_size[1] + 2*required\_size[2] + 2) >> 2 \quad (2.30)$   $adj\_predicted\_size = CLAMP(predicted\_size - qlevel\_change, 0, cpnt\_bit\_depth - qlevel) \quad (2.31)$

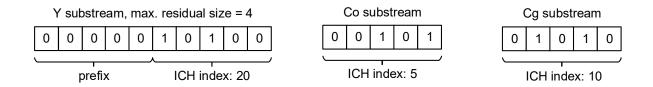

Figure 2.13: Example of an ICH coding for a group selecting ICH-mode with indices (20, 5, 10) for the leftmost, middle, and right pixels, respectively.

DSU-VLC for each unit includes a prefix which indicates the residual size, and a suffix that codes three quantized residuals. The prefix coding is a unary code which contains a number of "0" with a trailing "1" bit. The number of "0" bits indicates the size increase from the adjusted predicted size to the maximum residual size of the unit being coded in the current group. There are two cases that require modification: 1) if the previous group is coded with ICH-mode, a single "1" bit indicates ICH-mode is used again, "01" means no change in size, and "001" means size increase of one, etc; 2) when coding Y2, Co, and Cg units with maximum size, the trailing "1" bit is omitted since the decoder can infer it. Figure 2.12 shows four examples of DSU-VLC codes. The shortest DSU-VLC code for one unit is one bit, which contains a single "1" bit of prefix and no bits for suffix (all quantized residuals are zeros).

Indexed color history (ICH) coding uses a special escape code on the prefix of the first luma unit and no prefix for other units. If the previous group is coded in P-mode, the escape code indicates a prefix size that is one larger than the maximum length in P-mode, and the trailing "1" is omitted since the decoder can infer it. If the previous group is coded in ICH-mode, the prefix in the first luma unit contains a single bit of "1", which indicates ICH-mode is used again for the current group. The 5-bit ICH index for the leftmost pixel in the group is coded in the Y2 substream in native 4:2:2 mode and in the Y substream in other modes. The 5-bit ICH index for the middle and rightmost pixels in the group are coded in the Co and Cg substream, respectively. In ICH coding, a group requires at least 16 bits to code, which results in minimum bit rate of 5.333 bits per pixel. Figure 2.13 shows an example of ICH coding for a group not in native 4:2:2 mode.

#### 2.2.7 Rate Control

The rate control (RC) uses an idealized rate buffer model to manage the rate buffer fullness, and dynamically adjusts the quantization level to maximize the perceived quality. It consists of a

buffer level tracker, linear transformation, long-term parameter selection, short-term quantization parameter (Qp) adjustment, and flatness Qp overrides.

The buffer level tracker updates the original fullness of the RC buffer model. In every group, the number of bits used to code the group, which is provided by entropy encoding, is added to the buffer fullness. In addition, after the initial transmission delay, the number of bits to be transmitted per group is subtracted from the buffer fullness. In the last group of a chunk being processed, the buffer level tracker determines the number of adjustment bits, which is between zero and eight, to make the chunk size an integer number of bytes. In constant bit rate (CBR) mode, it signals the usage of MPP to guarantee a minimum bit rate if underflow could occur in the next group. In variable bit rate mode (VBR), buffer fullness is clamped to zero if the value will be less than zero; the correction amount is accumulated and is used to determine the actual chunk size.

Linear transformation adjusts the original buffer fullness ( $buffer\_fullness$ ) to a RC model fullness ( $rc\_model\_fullness$ ) which is a negative number and a value of zero means full.

$rc\_model\_fullness = (rc\_xform\_scale * (buffer\_fullness + rc\_xform\_offset)) >> 3$  (2.32) The offset value  $(rc\_xform\_offset)$  is modified in every group. It is designed to maintain constant quality during the initial delay, allocate extra bits for the first slice line (and also second slice line in native 4:2:0 mode), and ensure the slice is coded with the correct number of bits. The scale factor  $(rc\_xform\_scale)$  is used at the beginning and end of slice to maintain the RC model's usable range.

Long-term parameter selection uses 14 thresholds to define 15 ranges. The modified buffer fullness is compared against the thresholds and classified into one of the ranges. Each range has a minimum and a maximum quantization parameter, as well as an offset used for adjusting the targeted bits per group, all of which are used in short-term quantization parameter adjustment.

Short-term quantization parameter adjustment uses the parameters selected in long-term parameter selection, information provided in entropy encoding (i.e., predicted size, number of bits used to code the previous group), and quantization parameters of the previous two groups to make final adjustments of Qp for the next group.

The encoder performs flatness checks for the original pixels of each group in the upcoming supergroup, which is a set of four consecutive groups. Two flatness checks which use the current group pixels and the rightmost pixel in the previous group (first check) or the three pixels in the next group (second check) determines whether the group is "very flat" or "somewhat flat" by comparing the

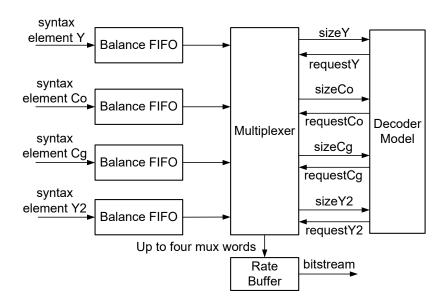

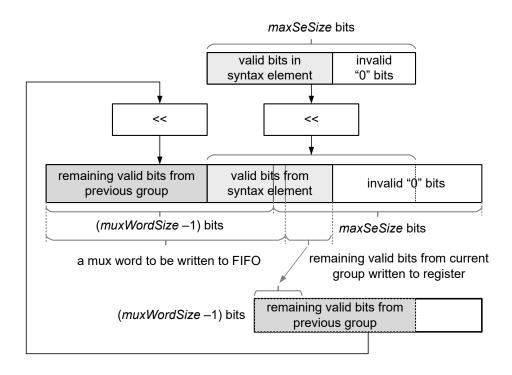

Figure 2.14: Substream multiplexer and rate buffer in the encoder, modified from [22, Figure 6-11]

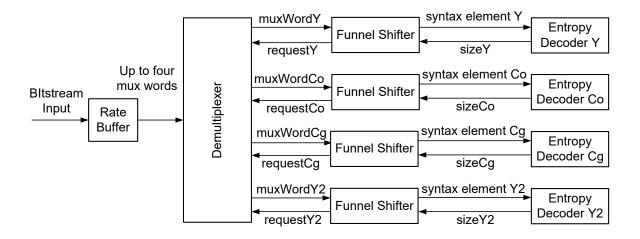

differences of the maximum and minimum sample values with two thresholds. When transitioning from non-flat to flat, Qp is dropped in the first flat group. Qp drops by four in "somewhat flat" groups and uses a constant value for "very flat" groups. Qp is mapped to quantization level before being used in prediction, quantization, reconstruction, and entropy encoding.

#### 2.2.8 Substream and Slice Multiplexing

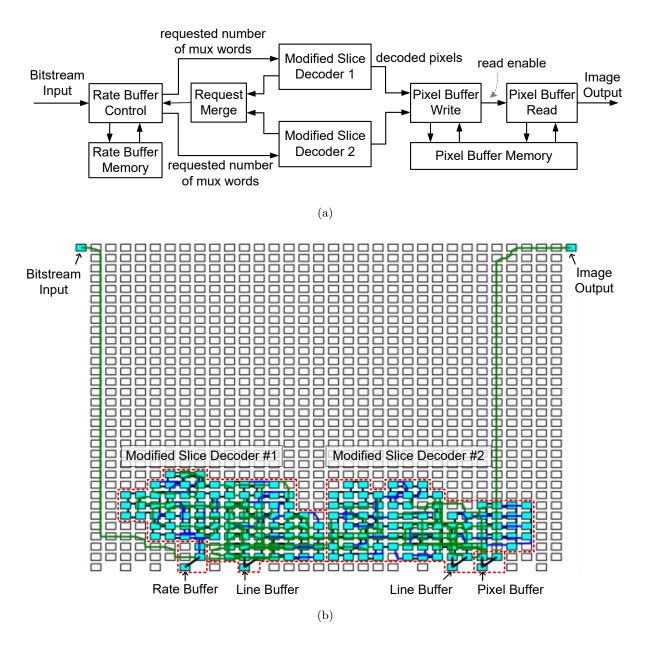

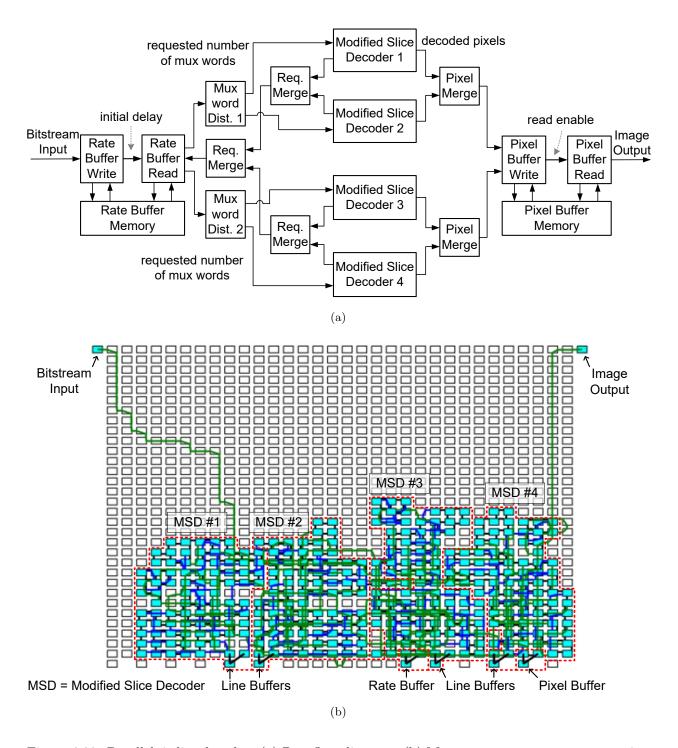

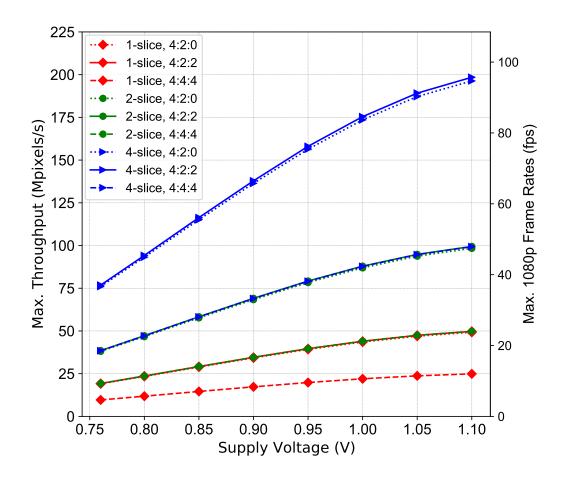

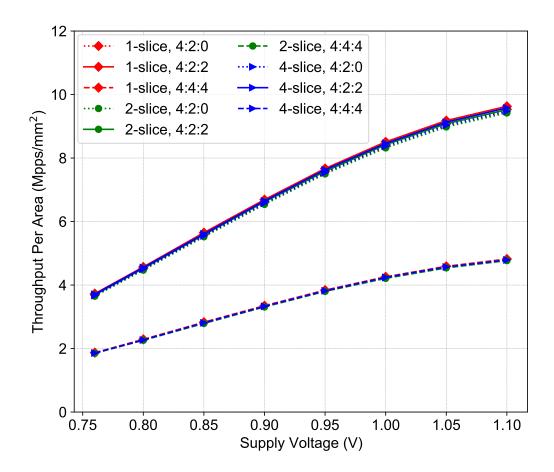

The syntax element of each component forms a *substream*. The three or four substreams are combined into a single bitstream using the substream multiplexing process. In simple 4:4:4 mode, the three substreams are for Y, Co, and Cg, respectively; the substream order in native 4:2:2 mode is the same as 4:4:4 mode for the first three substreams, and Y2 is in the fourth substream. The even-position luma (Y), odd-position luma (Y2), and chroma (Cb or Cr) in native 4:2:0 mode are the first, second, and third substreams, respectively. The fourth substream is only used in native 4:2:2 mode and is disabled for other modes.