# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Large-Scale Variability Characterization and Robust Design Techniques for Nanoscale SRAM

#### **Permalink**

https://escholarship.org/uc/item/9jk6x3wc

#### **Author**

Guo, Zheng

### **Publication Date**

2009

Peer reviewed|Thesis/dissertation

#### Large-Scale Variability Characterization and Robust Design Techniques for Nanoscale SRAM

by

Zheng Guo

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Tsu-Jae King Liu Professor Robert C. Leachman

Fall 2009

| The di | ssertation of Z | heng Guo,  | titled | Large-Scale  | Variability | Characterization | and | Robust |

|--------|-----------------|------------|--------|--------------|-------------|------------------|-----|--------|

| Design | Techniques for  | r Nanoscal | e SRA  | M, is approv | ved:        |                  |     |        |

| Chair | Date |

|-------|------|

|       |      |

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       |      |

|       | Date |

University of California, Berkeley

Copyright © 2009 by Zheng Guo

#### Abstract

Large-Scale Variability Characterization and Robust Design Techniques for Nanoscale SRAM

by

Zheng Guo

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

Continued increase in the process variability is perceived to be a major roadblock for future technology scaling. Its impact is particularly pronounced in large memory arrays due to both the utilization of minimum sized transistors and their extremely large data capacity. In order to enable the continued scaling of the next-generation embedded static random access memory (SRAM), the ability to monitor and characterize, on-chip, the variations in SRAM functionality and performance becomes critical for both gaining a deeper understanding of the sources of variability and for developing more robust circuits and topologies. This work presents a methodology to characterize, directly, the impact of process variability on the functionality of large SRAM-based cache memories - capable of collecting massive silicon data at little hardware and/or design overhead. In addition, a thorough investigation of various SRAM read stability and writeability metrics, including the proposed large-scale design metrics, is conducted to further understand the utility of each metric for SRAM yield prediction. The large-scale characterization methodology is validated on two different test chips, fabricated in an early commercial low-power 45nm CMOS process. This method can be easily extended to capture more than 6 standard deviations of parameter variations by increasing the SRAM array size, and therefore can serve as a valuable addition to the next-generation SRAM development vehicle.

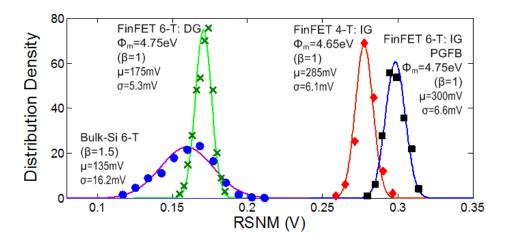

The enablement of future SRAM scaling will require technology and circuit co-design. The FinFET technology is particularly attractive for nanoscale SRAM design not only for its reduced  $\sigma_{VTH}$  and better control of the short channel effects (SCE), but also for the architectural flexibility enabled by its unique independently-gated (IG) operation. New bitcell designs are presented to take advantage of this IG operation in the form of a dynamic pass-gate feedback (PGFB). It is shown that the IG FinFET design using dynamic PGFB can both dramatically enhance the read stability of a 6-T SRAM cell and enable the practical design of a 4-T SRAM cell. While increased variability presents a formidable challenge for future SRAM scaling, the presented methodologies, both in testing and design, can facilitate its continuation.

# Contents

| Lis | t of                                                 | Figures                            | iii                                     |

|-----|------------------------------------------------------|------------------------------------|-----------------------------------------|

| Lis | t of                                                 | Tables                             | xiv                                     |

| 1   | 1.1<br>1.2<br>1.3<br>1.4<br>1.5                      | Technology and SRAM Scaling Trends | 1<br>1<br>3<br>8<br>10<br>11            |

| 2   | Cha<br>2.1<br>2.2<br>2.3                             | Introduction                       | 12<br>12<br>12<br>13<br>33              |

| 3   | Var: 3.1 3.2 3.3 3.4                                 | Introduction                       | 46<br>46<br>46<br>52<br>60              |

| 4   | Ana<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Introduction                       | 62<br>62<br>62<br>74<br>91<br>95<br>102 |

| 5   | Rob<br>5.1<br>5.2<br>5.3<br>5.4                      | Introduction                       | 109<br>113                              |

|                           | 5.5    | Summary           | 126 |

|---------------------------|--------|-------------------|-----|

| 6                         | Con    | nclusion          | 130 |

|                           | 6.1    | Key Contributions | 130 |

|                           | 6.2    | Future Work       | 132 |

|                           | 6.3    | Final Words       | 133 |

| $\mathbf{B}_{\mathbf{i}}$ | ibliog | graphy            | 134 |

# List of Figures

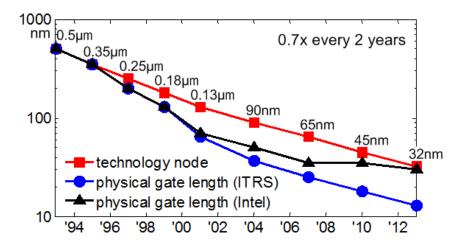

| 1.1        | Continued aggressive scaling for the transistor gate length $(L_G)$ by $0.7 \times$ every 2 years. ITRS data prior to 2001 are extracted from [120]; ITRS data after 2001 are provided from ITRS (2001-2007 editions) [73] scaling specifications. |   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|            | Intel data are provided from [12, 91, 99, 120] and indicate a significant slow-                                                                                                                                                                    | 0 |

| 1.2        | down in the scaling of the transistor $L_G$                                                                                                                                                                                                        | 2 |

|            | are provided from [158]. The ITRS scaling specifications [73] indicate smaller                                                                                                                                                                     |   |

|            | cell areas than the industry publications, but they correspond to the years                                                                                                                                                                        |   |

|            | of production (for different technology nodes), which typically lack behind                                                                                                                                                                        |   |

|            | industry publications by approximately 2 years (since the $90nm$ node)                                                                                                                                                                             | 3 |

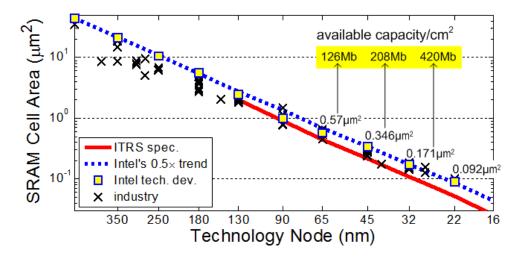

| 1.3        | Recent trend in SRAM $V_{DD}$ scaling [158] with a few high-density and high-                                                                                                                                                                      |   |

|            | performance designs (in $90nm$ , $65nm$ , and $45nm$ nodes) [12, 67, 148, 149, 162,                                                                                                                                                                |   |

|            | 163] shown as examples                                                                                                                                                                                                                             | 4 |

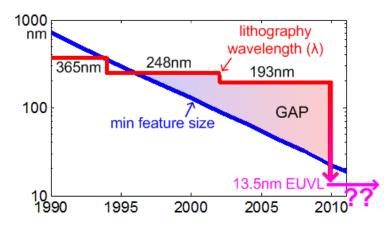

| 1.4        | Evolution of wavelength used in optical lithography [120], illustrating a shift to subwavelength lithography for the recent technology nodes. Currently, $193nm$ (ArF) immersion lithography is used for $45nm$ production and $32nm/22nm$         |   |

|            | development. It is still uncertain, at this time, when extreme ultraviolet lithography (EUVL) will be available for high-volume manufacturing, to close                                                                                            |   |

|            | the gap between the wavelength of the light source and the minimum feature                                                                                                                                                                         |   |

| 4 <b>-</b> |                                                                                                                                                                                                                                                    | 5 |

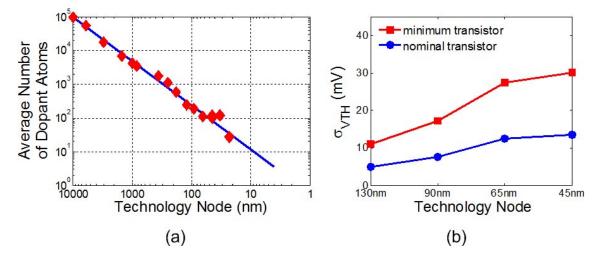

| 1.5        | (a) The average number of dopant atoms in the channel decreases with technology scaling; resulting in (b) increased $\sigma_{VTH}$ due to RDF. The figures are                                                                                     |   |

|            | adapted, with estimated data points, from [85]                                                                                                                                                                                                     | 5 |

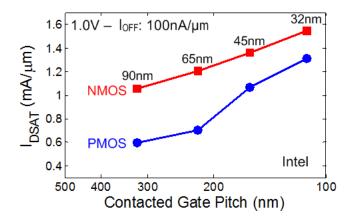

| 1.6        | Recent advancements in strain engineering have led to higher improvements                                                                                                                                                                          |   |

|            | in the PMOS $I_{DSAT}$ over the NMOS $I_{DSAT}$ - data estimated from [99]. For                                                                                                                                                                    |   |

|            | a minimum-sized SRAM bitcell, writeability is degraded due to a decreasing cell $\alpha$ -ratio                                                                                                                                                    | 7 |

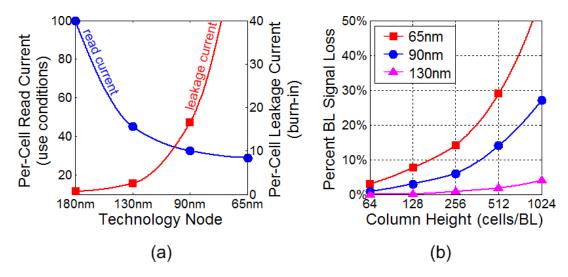

| 1.7        | cell $\alpha$ -ratio                                                                                                                                                                                                                               | 7 |

| 1.1        | read current ( $I_{READ}$ ) with technology scaling. (b) As a result, a large fraction                                                                                                                                                             |   |

|            | of the bit-line signal may be lost for higher column heights. Figures adapted,                                                                                                                                                                     |   |

|            | with estimated data points, from [114]                                                                                                                                                                                                             | 8 |

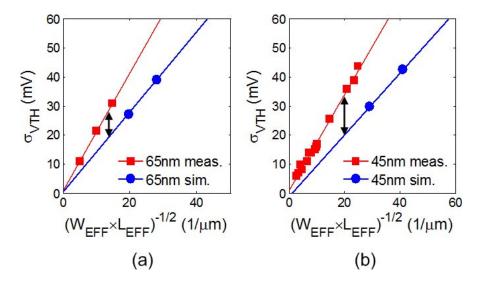

| 1.8  | Measured and simulated $\sigma_{VTH}$ due to RDF, under equivalent doping conditions, for (a) a $65nm$ process and (b) a $45nm$ process. The figures are adapted, with estimated data points, from [85] | Ĉ          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

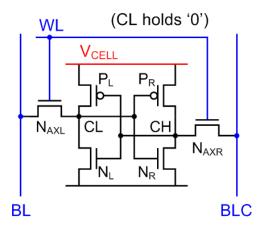

| 2.1  | Schematic of a 6-T SRAM bitcell                                                                                                                                                                         | 13         |

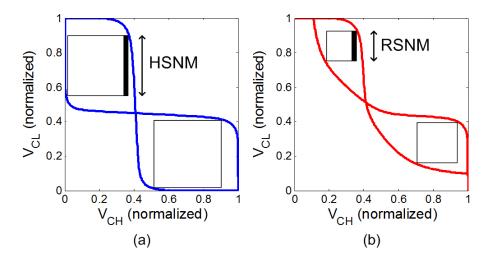

| 2.2  | (a) Definition of HSNM from simulated butterfly-curve. (b) Definition of                                                                                                                                |            |

|      | RSNM from simulated butterfly-curve                                                                                                                                                                     | 14         |

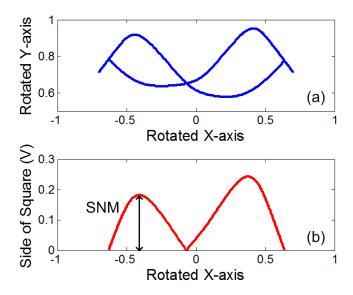

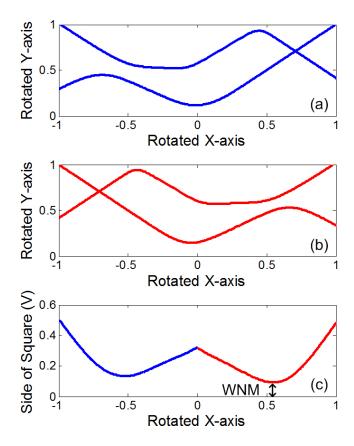

| 2.3  | (a) Read butterfly-curve rotated by 45°. (b) Length of the side of each em-                                                                                                                             |            |

|      | bedded square within the rotated butterfly-curves                                                                                                                                                       | 15         |

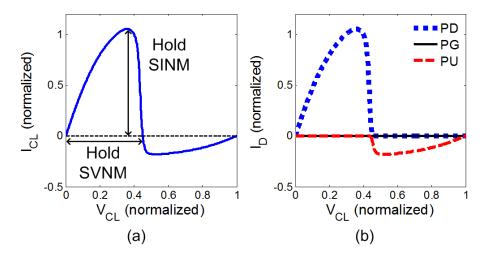

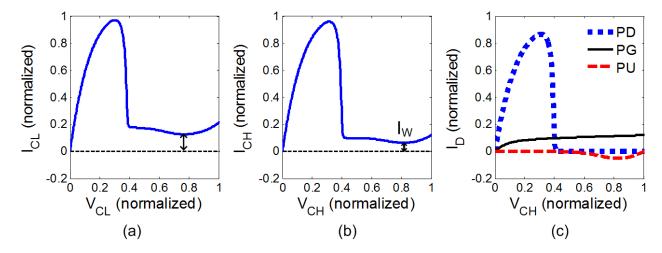

| 2.4  | (a) N-curve for sweeping $V_{CL}$ during the standby cycle. (b) $I_D$ of pull-down, pass-gate, and pull-up transistors while sweeping $V_{CL}$ during the standby N-                                    |            |

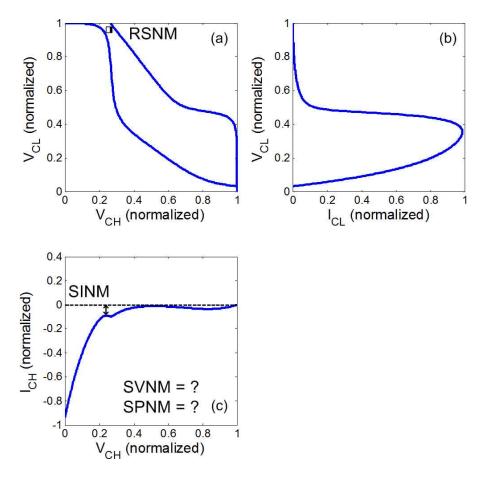

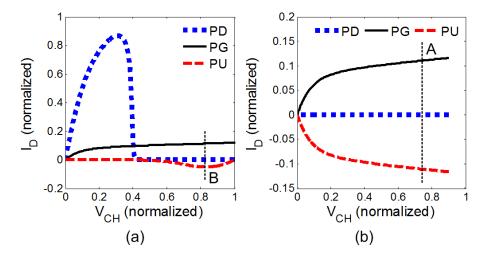

|      | curve characterization                                                                                                                                                                                  | 16         |

| 2.5  | (a) N-curve for sweeping $V_{CL}$ during the read cycle. (b) $I_D$ of pull-down, pass-gate, and pull-up transistors while sweeping $V_{CL}$ during the read N-curve                                     |            |

|      | characterization                                                                                                                                                                                        | 16         |

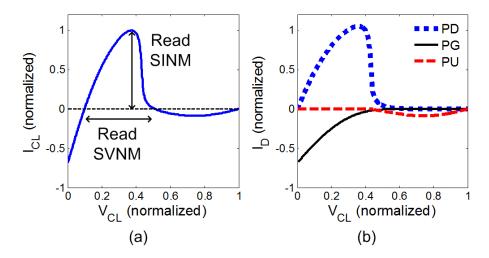

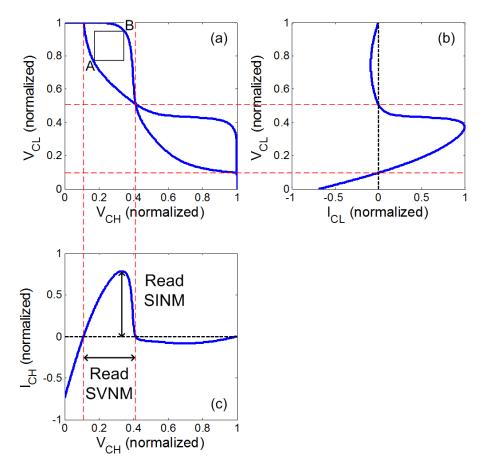

| 2.6  | (a) Butterfly-curve for SNM extraction during the read operation. (b) N-                                                                                                                                |            |

|      | curve for sweeping $V_{CL}$ during the read operation (x- and y-axis reversed for                                                                                                                       |            |

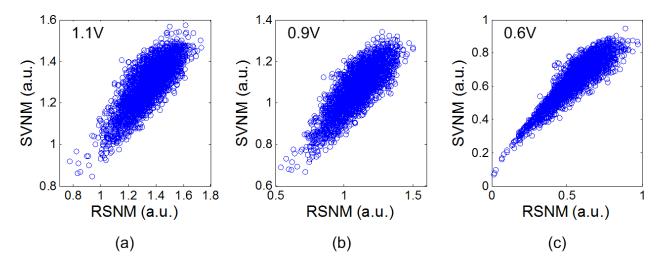

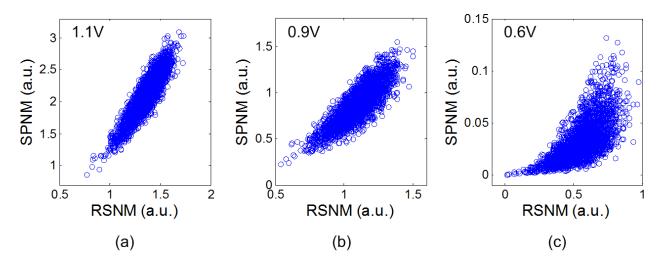

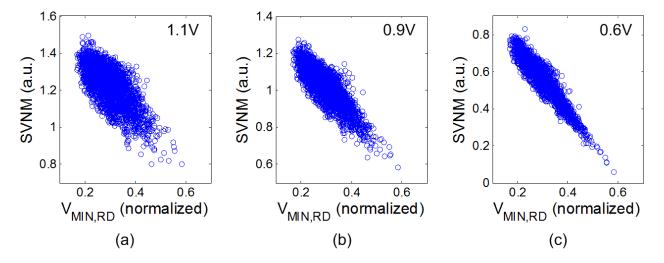

| 2.7  | comparison). (c) N-curve for sweeping $V_{CH}$ during the read operation Scatter plots for SVNM versus RSNM obtained from 3k-sample MC simula-                                                          | 17         |

|      | tions using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ ,                                                                                                                         |            |

|      | (b) $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                                                                                                                                           | 18         |

| 2.8  | (a) VTC pair for an SRAM cell with a negative read margin. (b) N-curve                                                                                                                                  |            |

|      | while sweeping $V_{CL}$ for an SRAM cell with a negative read margin (x- and y-                                                                                                                         |            |

|      | axis reversed for comparison). (c) N-curve while sweeping $V_{CH}$ for an SRAM                                                                                                                          | 4.0        |

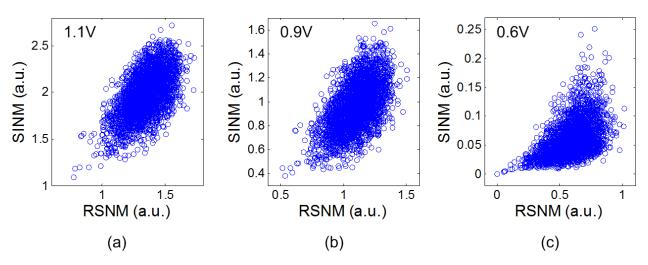

| 2.0  | cell with a negative read margin.                                                                                                                                                                       | 19         |

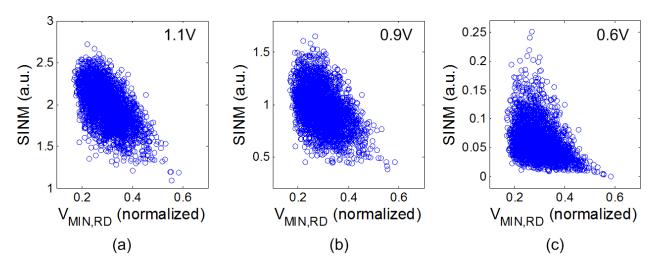

| 2.9  | Scatter plots for SINM versus RSNM obtained from 3k-sample MC simulations using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ , (b)                                                 |            |

| 0.40 | $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                                                                                                                                               | 19         |

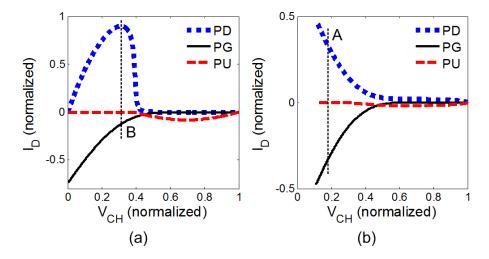

| 2.10 | (a) $I_D$ of pull-down, pass-gate, and pull-up transistors while sweeping $V_{CH}$ for                                                                                                                  |            |

|      | extracting the SINM near corner $B$ . (b) $I_D$ of pull-down, pass-gate, and pull-                                                                                                                      |            |

|      | up transistors as a function of $V_{CH}$ while sweeping $V_{CL}$ for the characterization                                                                                                               | 20         |

| ດ 11 | of corner A in the RSNM extraction                                                                                                                                                                      | 20         |

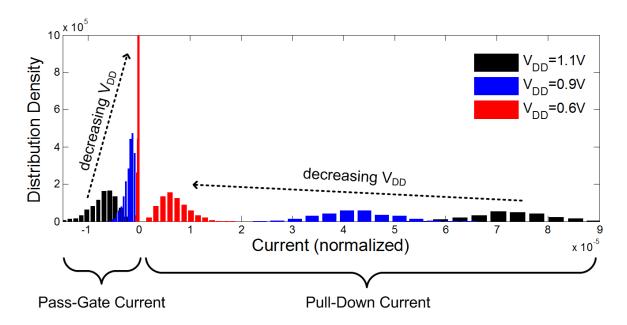

| 2.11 | Distribution densities of the pass-gate transistor and the pull-down transistor current contributions to SINM at $V_{DD} = 1.1V$ , $0.9V$ , and $0.6V$                                                  | 21         |

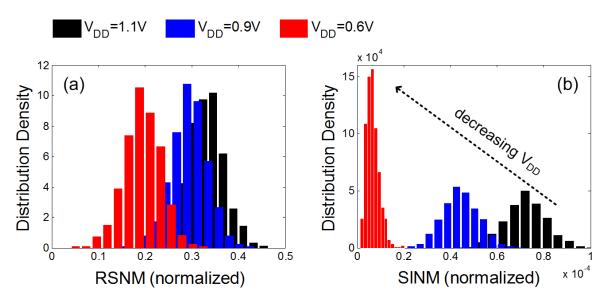

| 9 19 | Distribution densities of (a) RSNM and (b) SINM at $V_{DD} = 1.1V$ , 0.9V, and                                                                                                                          | <i>∠</i> 1 |

| 2.12 | 0.6 $V$                                                                                                                                                                                                 | 22         |

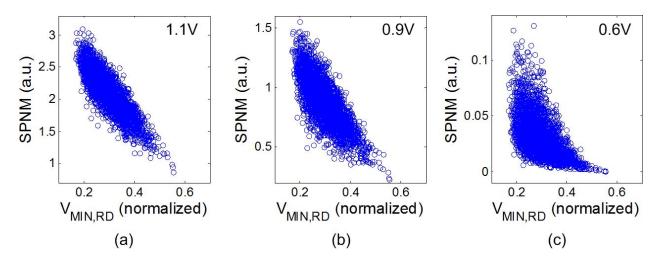

| 2 13 | Scatter plots for SPNM versus RSNM obtained from 3k-sample MC simula-                                                                                                                                   | 22         |

| 2.10 | tions using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ ,                                                                                                                         |            |

|      | (b) $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                                                                                                                                           | 23         |

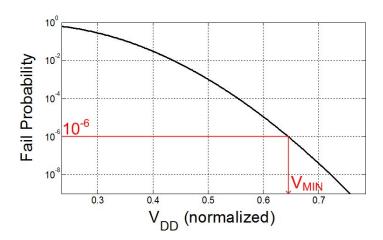

| 2.14 | Fail probability as a function of $V_{DD}$ - used to illustrate the definition of $V_{MIN}$ .                                                                                                           | 23         |

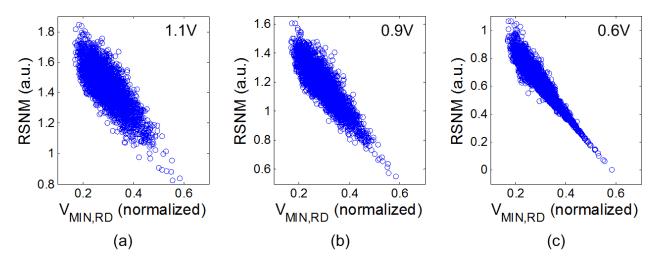

|      | Scatter plots for RSNM versus $V_{MIN,RD}$ obtained from 3k-sample MC simulations using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ ,                                             |            |

|      | (b) $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                                                                                                                                           | 24         |

|      | (*) * DD                                                                                                                                                                                                |            |

| 2.16 | Scatter plots for SVNM versus $V_{MIN,RD}$ obtained from 3k-sample MC simula-               |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | tions using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ ,             |    |

|      | (b) $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                               | 24 |

| 2.17 | Scatter plots for SINM versus $V_{MIN,RD}$ obtained from 3k-sample MC simula-               |    |

|      | tions using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ ,             |    |

|      | (b) $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                               | 25 |

| 2.18 | Scatter plots for SPNM versus $V_{MIN,RD}$ obtained from 3k-sample MC simula-               |    |

|      | tions using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 1.1V$ ,             |    |

|      | (b) $V_{DD} = 0.9V$ , and (c) $V_{DD} = 0.6V$                                               | 25 |

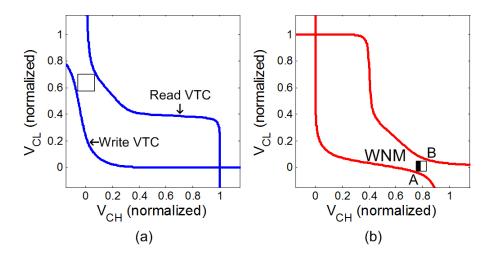

| 2.19 | Definition of WNM from simulated VTC-pair for (a) writing a '0' into $CL$ (or               |    |

|      | '1' into $CH$ ) and (b) writing a '1' into $CH$ (or '0' into $CL$ )                         | 27 |

| 2.20 | The VTC pair, rotated by $45^{\circ}$ , for (a) writing a '0' into $CL$ (or '1' into $CH$ ) |    |

|      | and (b) writing a '0' into $CH$ (or '1' into $CL$ ). (c) Length of the side of each         |    |

|      | embedded square within the rotated VTC pair                                                 | 28 |

| 2.21 | Definition of $I_W$ from measured N-curve for (a) writing a '0' into $CL$ (or '1'           |    |

|      | into $CH$ ) and (b) writing a '1' into $CH$ (or '0' into $CL$ ). (c) $I_D$ of pull-         |    |

|      | down, pass-gate, and pull-up transistors while sweeping $V_{CH}$ during N-curve             |    |

|      | characterization for writing a '1' into $CH$                                                | 29 |

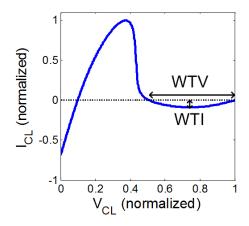

| 2.22 | Definition of WTV and WTI from measured N-curve                                             | 30 |

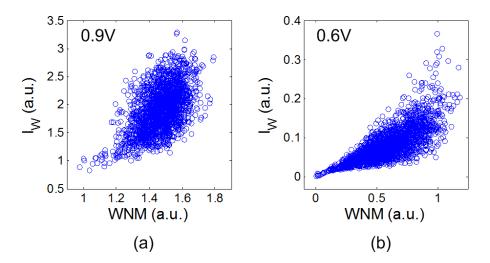

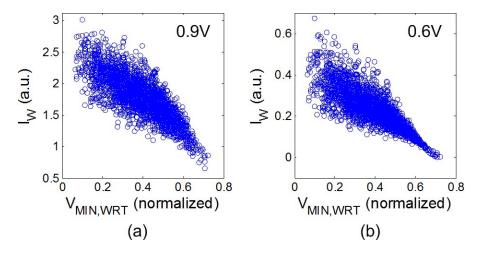

|      | Scatter plots for $I_W$ versus WNM obtained from 3k-sample MC simulations                   |    |

|      | using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 0.9V$ and                 |    |

|      | (b) $V_{DD} = 0.6V$                                                                         | 31 |

| 2.24 | (a) $I_D$ of pull-down, pass-gate, and pull-up transistors while sweeping $V_{CH}$ for      |    |

|      | extracting the $I_W$ near corner $B$ . (b) $I_D$ of pull-down, pass-gate, and pull-up       |    |

|      | transistors as a function of $V_{CH}$ while sweeping $V_{CL}$ for the characterization      |    |

|      | of corner A in the WNM extraction                                                           | 31 |

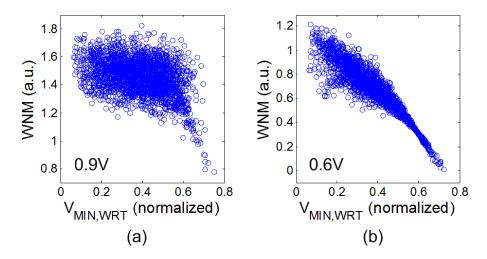

| 2.25 | Scatter plots for WNM versus $V_{MIN,WRT}$ obtained from 3k-sample MC simu-                 |    |

|      | lations using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 0.9V$             |    |

|      | and (b) $V_{DD} = 0.6V$                                                                     | 32 |

| 2.26 | Scatter plots for $I_W$ versus $V_{MIN,WRT}$ obtained from 3k-sample MC simula-             |    |

|      | tions using a commercial low-power $45nm$ CMOS process at (a) $V_{DD} = 0.9V$               |    |

|      | and (b) $V_{DD} = 0.6V$                                                                     | 32 |

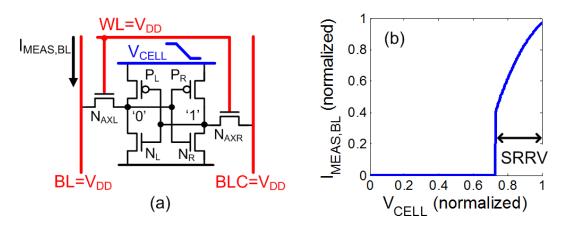

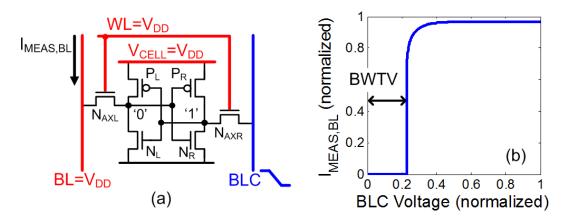

| 2.27 | (a) Measurement setup for characterizing SRRV. (b) Definition of SRRV from                  |    |

|      | simulated transfer curve                                                                    | 34 |

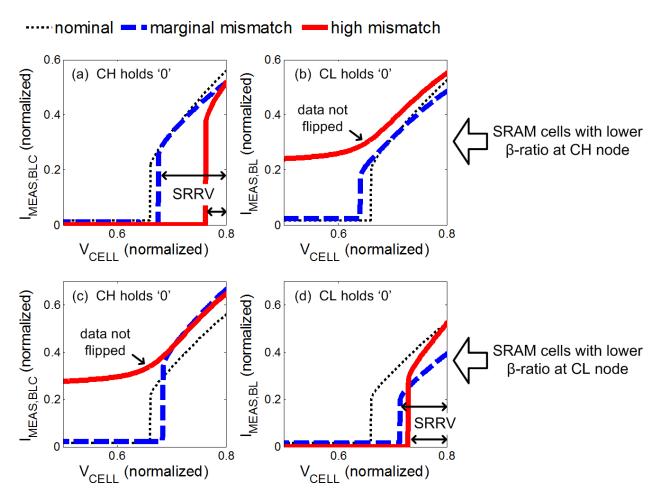

| 2.28 | (a) SRRV transfer curves for storing a $'0'$ at the less read-stable $CH$ node;             |    |

|      | all transfer curves exhibit sharp fall off in $I_{MEAS,BLC}$ . (b) SRRV transfer            |    |

|      | curves for storing a '0' at the more read-stable $CL$ node; only the transfer               |    |

|      | curve corresponding to a marginal intrinsic mismatch exhibit a sharp fall-off in            |    |

|      | $I_{MEAS,BL}$ , while the transfer curve corresponding to a high intrinsic mismatch         |    |

|      | shows a smooth bend in $I_{MEAS,BL}$ . (c) SRRV transfer curves for storing a               |    |

|      | '0' at the more read-stable $CH$ node; only the transfer curve corresponding                |    |

|      | to a marginal intrinsic mismatch exhibit a sharp fall-off in $I_{MEAS,BLC}$ , while         |    |

|      | the transfer curve corresponding to a high intrinsic mismatch shows a smooth                |    |

|      | bend in $I_{MEAS,BLC}$ . (c) SRRV transfer curves for storing a '0' at the less             |    |

|      | read-stable $CL$ node; all transfer curves exhibit sharp fall off in $I_{MEAS,BL}$ .        | 35 |

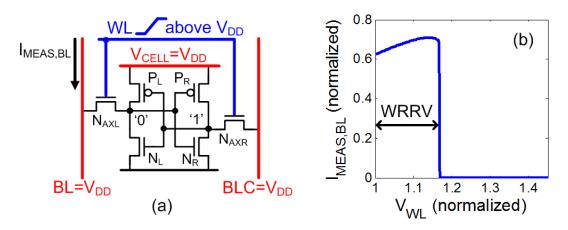

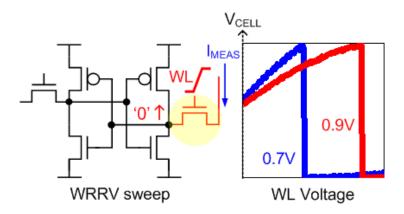

| 2.29                    | (a) Measurement setup for characterizing WRRV. (b) Definition of WRRV                    |                  |

|-------------------------|------------------------------------------------------------------------------------------|------------------|

|                         | from simulated transfer curve                                                            | 37               |

| 2.30                    | (a) WRRV transfer curves for storing a $'0'$ at the less read-stable $CH$ node;          |                  |

|                         | all transfer curves exhibit sharp fall off in $I_{MEAS,BLC}$ . (b) WRRV transfer         |                  |

|                         | curves for storing a $'0'$ at the more read-stable $CL$ node; only the transfer          |                  |

|                         | curve corresponding to a marginal intrinsic mismatch exhibit a sharp fall-               |                  |

|                         | off in $I_{MEAS,BL}$ , while the transfer curve corresponding to a high intrinsic        |                  |

|                         | mismatch shows a smooth $I_{MEAS,BL}$ . (c) WRRV transfer curves for storing a           |                  |

|                         | '0' at the more read-stable $CH$ node; only the transfer curve corresponding             |                  |

|                         | to a marginal intrinsic mismatch exhibit a sharp fall-off in $I_{MEAS,BLC}$ , while      |                  |

|                         | the transfer curve corresponding to a high intrinsic mismatch shows a smooth             |                  |

|                         | $I_{MEAS,BLC}$ . (c) WRRV transfer curves for storing a '0' at the less read-stable      |                  |

|                         | $CL$ node; all transfer curves exhibit sharp fall off in $I_{MEAS,BL}$                   | 38               |

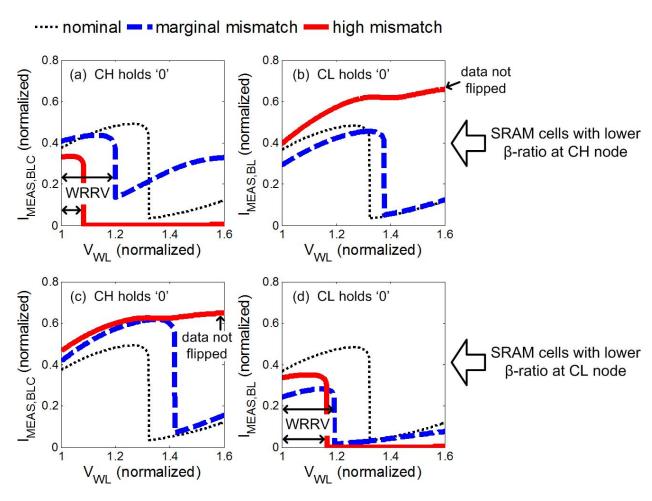

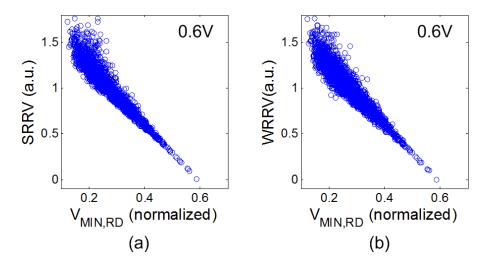

| 2.31                    | Scatter plots for (a) SRRV versus WRRV, (b) SRRV versus RSNM, and (c)                    |                  |

|                         | WRRV versus RSNM at $V_{DD} = 0.6V$ obtained from 3k-sample MC simula-                   |                  |

|                         | tions using a commercial low-power $45nm$ CMOS process                                   | 39               |

| 2.32                    |                                                                                          |                  |

|                         | at $V_{DD} = 0.6V$ obtained from 3k-sample MC simulations using a commercial             |                  |

|                         | low-power $45nm$ CMOS process                                                            | 39               |

| 2.33                    | (a) Measurement setup for characterizing BWTV. (b) Definition of BWTV                    |                  |

|                         | from simulated transfer curve                                                            | 41               |

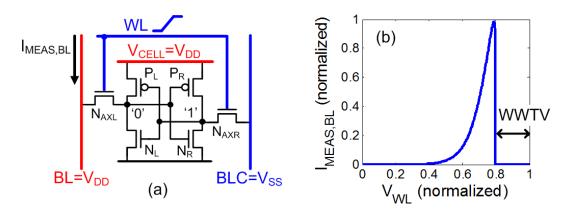

| 2.34                    | (a) Measurement setup for characterizing WWTV. (b) Definition of WWTV                    |                  |

|                         | from simulated transfer curve                                                            | 41               |

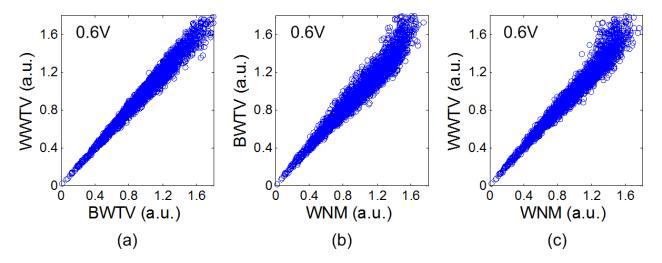

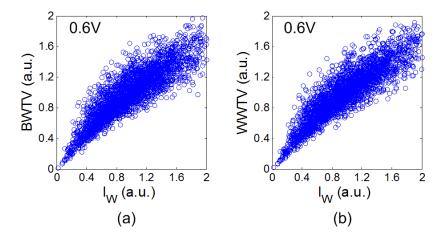

| 2.35                    | Scatter plots for (a) BWTV versus WWTV, (b) BWTV versus WNM, and                         |                  |

|                         | (c) WWTV versus WNM at $V_{DD} = 0.6V$ obtained from 3k-sample MC simu-                  |                  |

|                         | lations using a commercial low-power $45nm$ CMOS process                                 | 42               |

| 2.36                    |                                                                                          |                  |

|                         | 0.6V obtained from 3k-sample MC simulations using a commercial low-power                 |                  |

|                         | 45nm CMOS process                                                                        | 42               |

| 2.37                    | Scatter plots for (a) BWTV versus $V_{MIN,WRT}$ and (b) WWTV versus $V_{MIN,WRT}$        |                  |

|                         | at $V_{DD} = 0.6V$ obtained from 3k-sample MC simulations using a commercial             |                  |

|                         | low-power $45nm$ CMOS process                                                            | 43               |

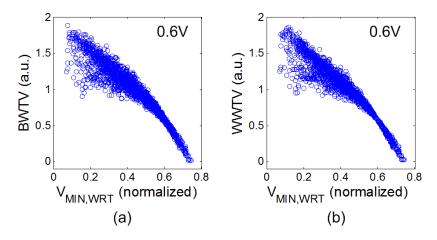

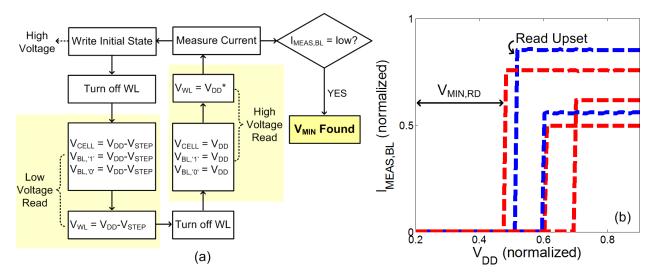

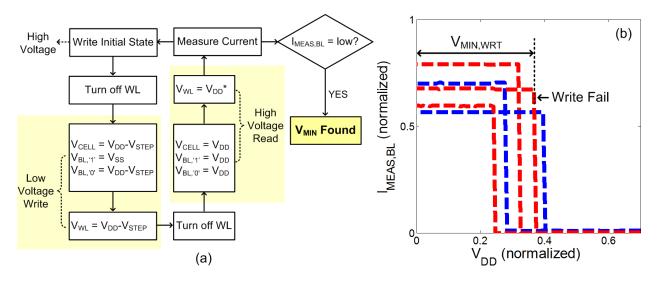

| 2.38                    |                                                                                          |                  |

|                         | ferent $V_{DD}$ points for $V_{MIN,RD}$ extraction                                       | 44               |

| 2.39                    | (a) Flow chart for $V_{MIN,WRT}$ characterization and (b) bit-line currents at           |                  |

|                         | different $V_{DD}$ points for $V_{MIN,WRT}$ extraction                                   | 45               |

| n 1                     |                                                                                          |                  |

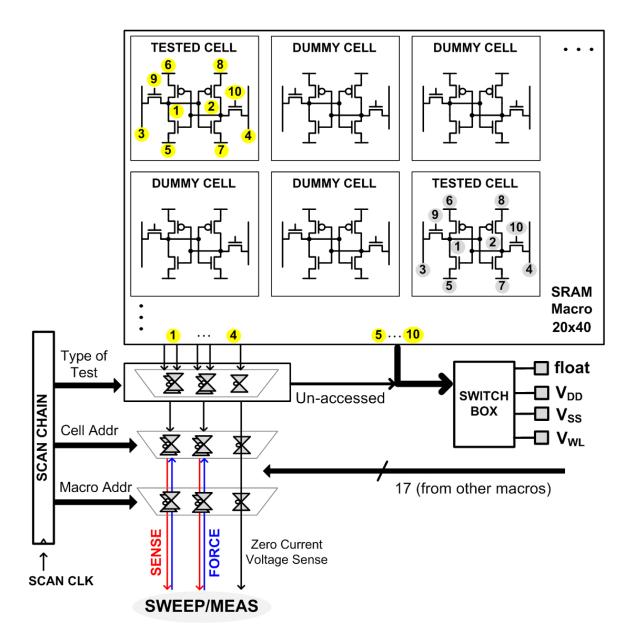

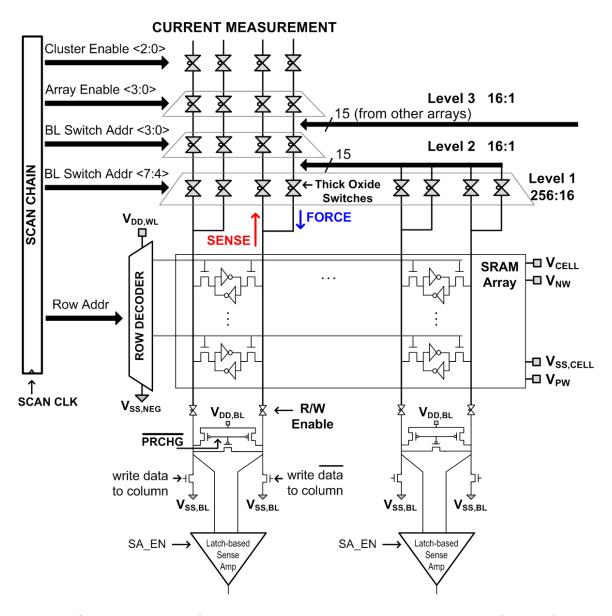

| 3.1                     | Circuit diagram of the all-internal-node access characterization scheme for the          | 4.               |

| 2.0                     | SRAM macros.                                                                             | 47               |

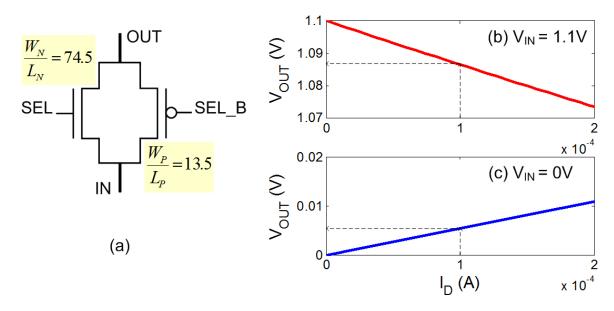

| 3.2                     | (a) Schematic of the thick-oxide CMOS transmission gate used in the switch               |                  |

|                         | network for both the all-internal-node access scheme and the direct bit-line             |                  |

|                         | access scheme. Simulated $V_{OUT}$ versus $I_D$ of the switch for (b) $V_{IN} = 1.1V$    | 40               |

| 3.3                     | and (c) $V_{IN} = 0V$                                                                    | 49<br>50         |

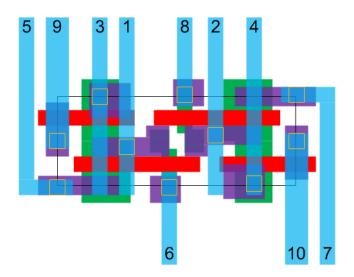

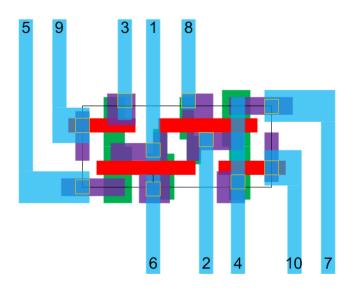

| 3.4                     | Layout cartoon for a $0.374 \mu\text{m}^2$ bitcell with all 10 internal nodes wired out. | 50<br>51         |

| $\mathbf{J}.\mathbf{T}$ | Layout cartoon for a 0.014 mil briten with all to internal hours when out.               | $o_{\mathrm{T}}$ |

| 3.5         | Layout cartoon for a 0.299 $\mu$ m <sup>2</sup> bitcell with all 10 internal nodes wired out                                         | 51         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.6         | Layout cartoon for a $0.252 \mu\text{m}^2$ bitcell with all 10 internal nodes wired out. The SRAM CUT is outlined by the dotted line | 52         |

| 3.7         | Circuit diagram of the direct bit-line characterization scheme for the func-                                                         | 32         |

| 5.1         | tional SRAM arrays                                                                                                                   | 53         |

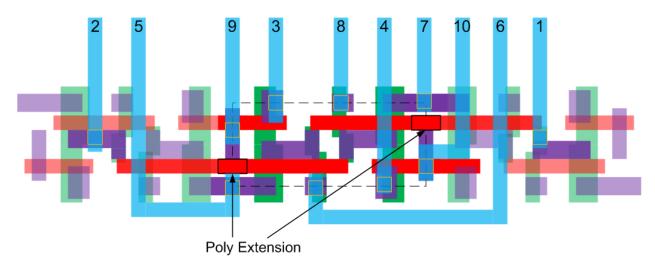

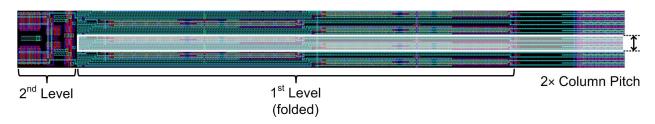

| 3.8         | Layout view (up to the M2 layer) showing the construction of the first level of                                                      | 99         |

| <b>J</b> .0 | the bit-line switch hierarchy within the column pitch of an SRAM sub-array                                                           |            |

|             | using the $0.374 \mu\text{m}^2$ bitcell design                                                                                       | 54         |

| 3.9         | Layout view (up to the M2 layer) showing the construction of the first level                                                         | 04         |

| 0.5         | of the bit-line switch hierarchy folded to fit within $2\times$ the column pitch of an                                               |            |

|             | SRAM sub-array using the 0.299 $\mu$ m <sup>2</sup> bitcell design                                                                   | 54         |

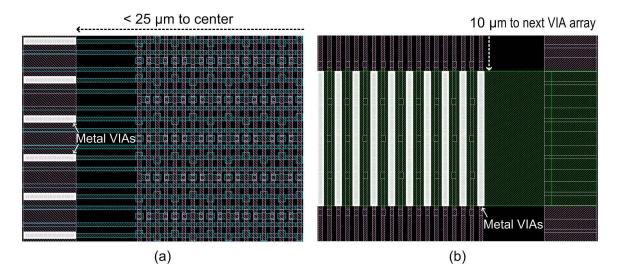

| 3.10        |                                                                                                                                      | 01         |

| 0.10        | mini-array. (b) Layout view showing the M3-M4 connection of $V_{SS,CELL}$ inside                                                     |            |

|             | the $128 \times 256$ mini-array                                                                                                      | 55         |

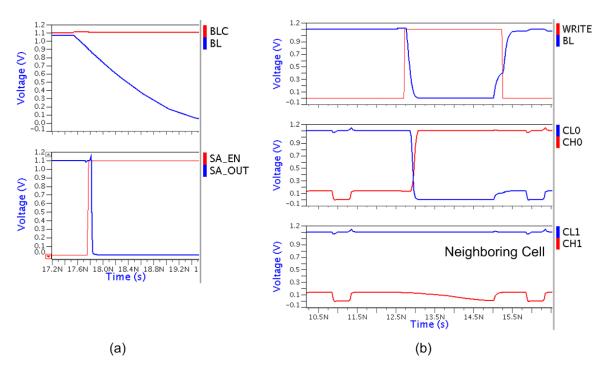

| 3.11        | Simulated waveforms during (a) the read cycle and (b) the write cycle showing                                                        |            |

|             | correct functionality.                                                                                                               | 56         |

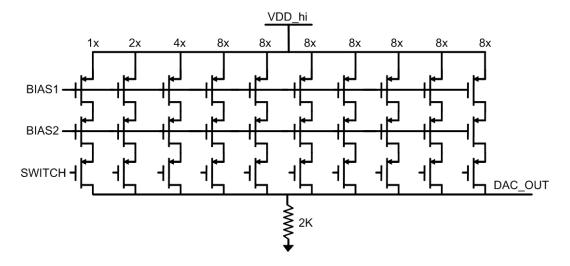

| 3.12        | Circuit diagram of a 3LSB-3MSB segmented DAC implemented to perform                                                                  |            |

|             | on-chip word-line sweep.                                                                                                             | 57         |

| 3.13        | Circuit diagram showing how the output of the 6-bit DAC is multiplexed to                                                            |            |

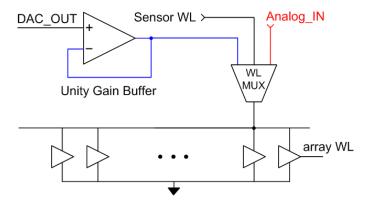

|             | drive the word-line                                                                                                                  | 57         |

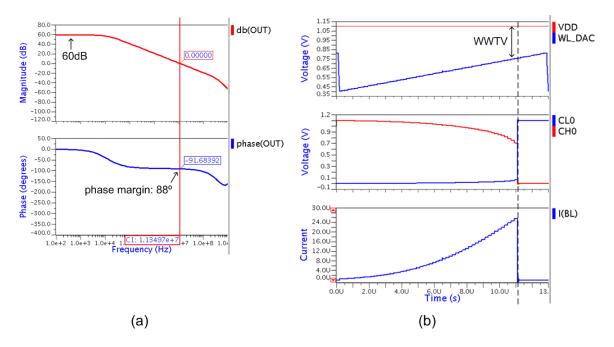

| 3.14        | (a) Simulated gain and phase frequency response waveforms for the folded                                                             |            |

|             | cascode operation amplifier used in the unity gain buffer. (b) Simulated tran-                                                       |            |

|             | sient waveforms showing the characterization of WWTV using the 6-bit DAC.                                                            |            |

|             | Note: the $BL$ current is scaled and does not reflect actual current values from                                                     |            |

| 0.15        | the simulation.                                                                                                                      | 59         |

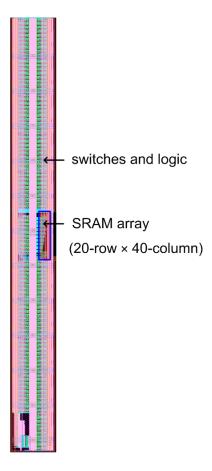

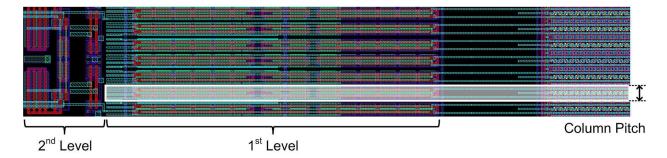

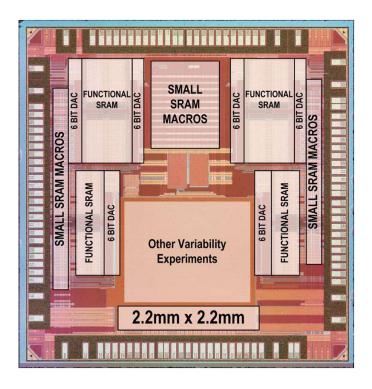

|             | Die photo of the first low-power $45nm$ CMOS test chip                                                                               | 60         |

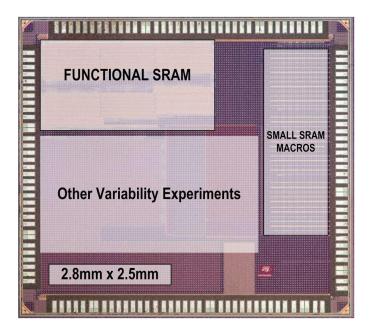

| 3.10        | Die photo of the second low-power 45nm CMOS test chip. This test chip                                                                |            |

|             | allows the characterization of 3 different SRAM bitcell designs, yielding cell                                                       | <i>G</i> 1 |

|             | areas of $0.374  \mu m^2$ , $0.299  \mu m^2$ , and $0.252  \mu m^2$                                                                  | 61         |

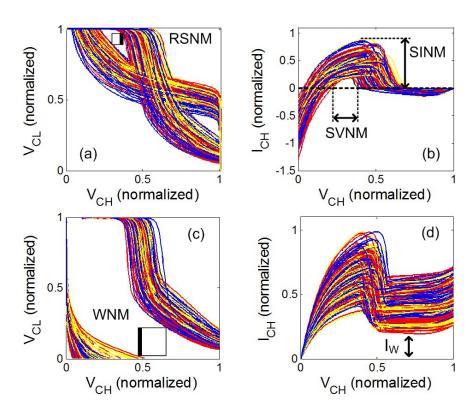

| 4.1         | Measured (a) butterfly-curves for RSNM extraction, (b) N-curves for SVNM                                                             |            |

|             | and SINM (as well as SPNM) extraction, (c) VTC pairs for WNM extraction,                                                             |            |

|             | and (d) N-curves for $I_W$ extraction from SRAM macros using all-internal-node                                                       |            |

|             | access                                                                                                                               | 63         |

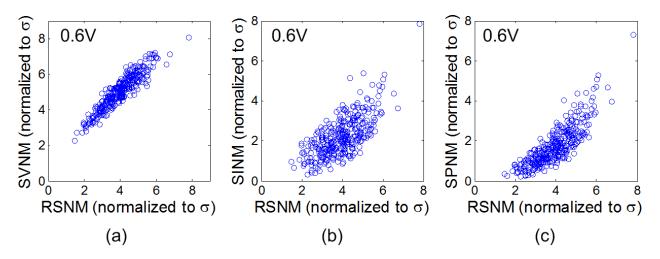

| 4.2         | Scatter plots for (a) SVNM versus RSNM, (b) SINM versus RSNM, and (c)                                                                |            |

|             | SPNM versus RSNM measured at $V_{DD} = 0.6V$ from the same SRAM macros                                                               |            |

|             | using all-internal-node access.                                                                                                      | 64         |

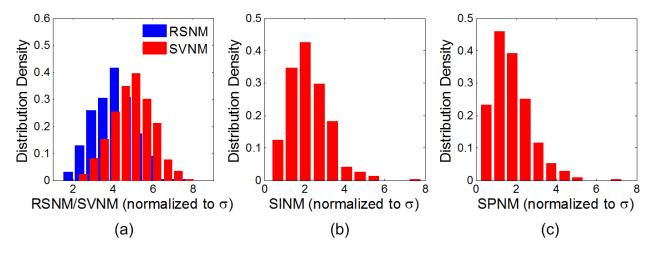

| 4.3         | Distribution densities of (a) RSNM/SVNM, (b) SINM, and (c) SPNM mea-                                                                 |            |

|             | sured at $V_{DD} = 0.6V$ from the same SRAM macros using all-internal-node                                                           |            |

|             | access. Note: the y-axis scale differs from Figure 2.12 because each metric is                                                       | 0.4        |

| 1 1         | normalized to its $\sigma$ value                                                                                                     | 64         |

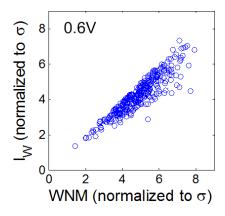

| 4.4         | Scatter plot for $I_W$ versus WNM measured at $V_{DD} = 0.6V$ from the same                                                          | a E        |

|             | SRAM macros using all-internal-node access                                                                                           | 65         |

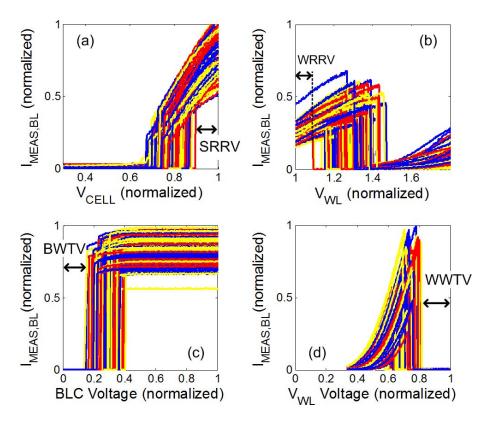

| 4.5  | Measured transfer curves for (a) SRRV extraction, (b) WRRV extraction, (c) BWTV extraction, and (d) WWTV extraction from functional SRAM arrays         |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | using direct bit-line access                                                                                                                            | 66 |

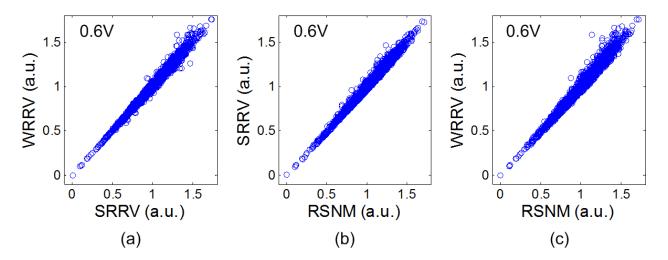

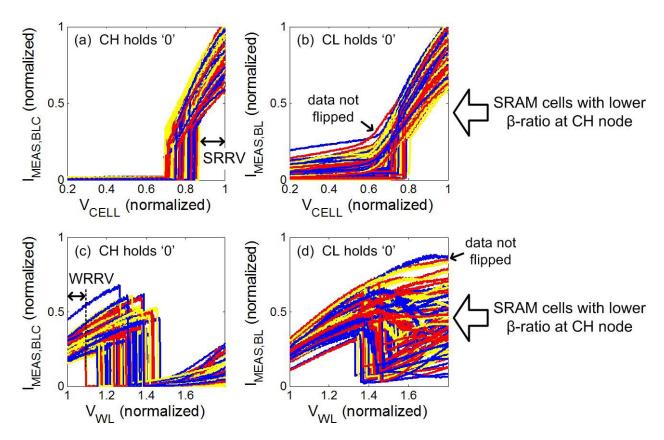

| 4.6  | (a) Measured SRRV transfer curves for storing a '0' at the less read-stable $CH$                                                                        |    |

|      | node; all transfer curves exhibit sharp fall off in $I_{MEAS,BLC}$ . (b) Measured                                                                       |    |

|      | SRRV transfer curves for storing a '0' at the more read-stable $CL$ node; only                                                                          |    |

|      | some transfer curves exhibit a sharp fall-off in $I_{MEAS,BL}$ while other transfer                                                                     |    |

|      | curves do not. (c) Measured WRRV transfer curves for storing a '0' at the less                                                                          |    |

|      | read-stable $CH$ node; all transfer curves exhibit sharp fall off in $I_{MEAS,BLC}$ .                                                                   |    |

|      | (d) Measured WRRV transfer curves for storing a '0' at the more read-stable                                                                             |    |

|      | $CL$ node; only some transfer curves exhibit a sharp fall-off in $I_{MEAS,BL}$ while                                                                    |    |

|      | other transfer curves do not                                                                                                                            | 67 |

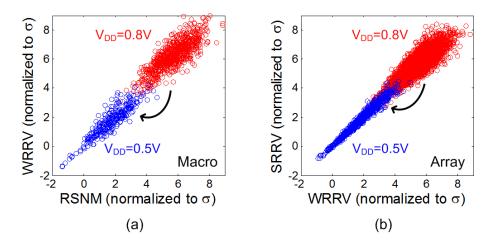

| 4.7  | (a) Scatter plot for WRRV versus RSNM measured from the same SRAM                                                                                       |    |

|      | macro using all-internal-node access at $V_{DD} = 0.8V$ and $0.5V$ . (b) Scatter                                                                        |    |

|      | plot for SRRV versus WRRV measured from the same functional SRAM array                                                                                  |    |

|      | using direct bit-line access at $V_{DD} = 0.8V$ and $0.5V$                                                                                              | 68 |

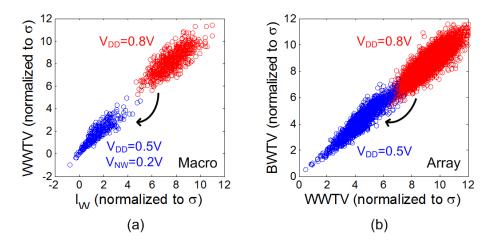

| 4.8  | (a) Scatter plot for WWTV versus $I_W$ measured from the same SRAM macro                                                                                |    |

|      | using all-internal-node access at $V_{DD} = 0.8V$ and at $V_{DD} = 0.5V$ with $V_{NW} =$                                                                |    |

|      | 0.2V. (b) Scatter plot for BWTV versus WWTV measured from the same                                                                                      |    |

|      | functional SRAM array using direct bit-line access at $V_{DD} = 0.8V$ and 0.5V.                                                                         | 68 |

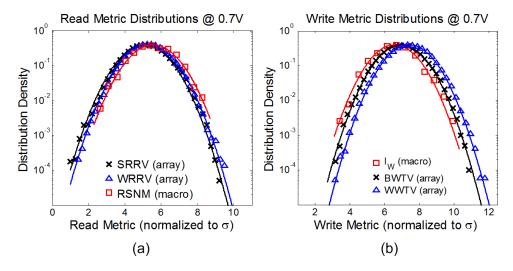

| 4.9  | Semi-log plots for (a) the measured read metric distributions using RSNM,                                                                               |    |

|      | SRRV, and WRRV at $V_{DD} = 0.7V$ ; and (b) the measured write metric distri-                                                                           |    |

|      | butions using $I_W$ , BWTV, and WTTV at $V_{DD} = 0.7V$                                                                                                 | 69 |

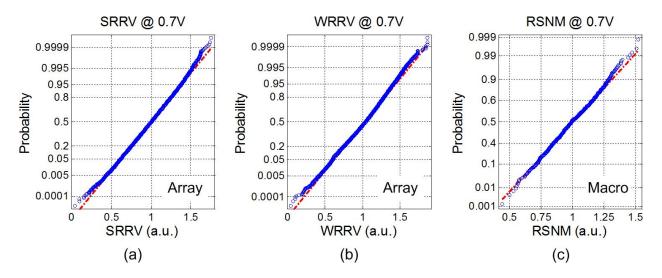

| 4.10 | Normal probability plots for (a) SRRV, (b) WRRV, and (c) RSNM measured                                                                                  |    |

|      | at $V_{DD} = 0.7V$                                                                                                                                      | 70 |

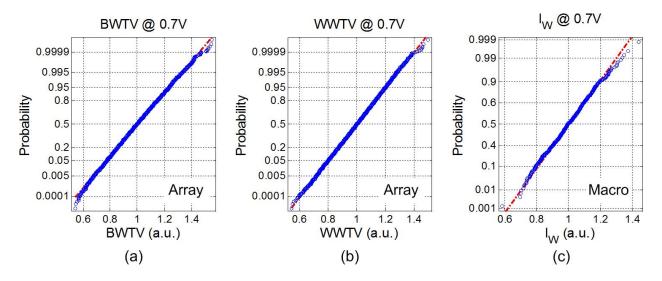

| 4.11 | Normal probability plots for (a) BWTV, (b) WWTV, and (c) $I_W$ measured                                                                                 |    |

|      | at $V_{DD} = 0.7V$                                                                                                                                      | 70 |

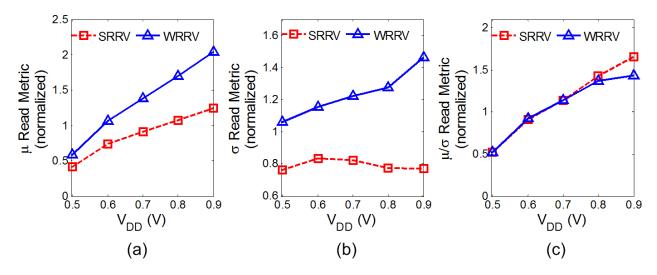

| 4.12 | Measured (a) $\mu$ , (b) $\sigma$ , and (c) $\mu/\sigma$ of SRRV and WRRV as a function of $V_{DD}$ .                                                   | 71 |

| 4.13 | The bit-line current sensitivity to the $WL$ overdrive is reduced due to a rise                                                                         |    |

|      | in the '0' storage node voltage and is more pronounced as $V_{DD}$ is increased                                                                         | 72 |

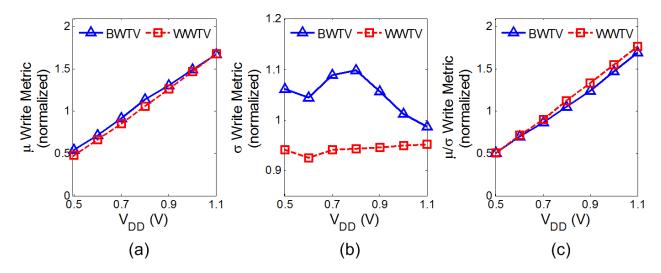

| 4.14 | Measured (a) $\mu$ , (b) $\sigma$ , and (c) $\mu/\sigma$ of BWTV and WWTV as a function of                                                              |    |

|      | $V_{DD}$                                                                                                                                                | 73 |

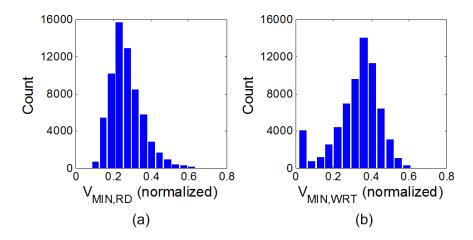

| 4.15 | Distributions of (a) $V_{MIN,RD}$ and (b) $V_{MIN,WRT}$ measured in a 64kb functional                                                                   |    |

|      | SRAM sub-array.                                                                                                                                         | 74 |

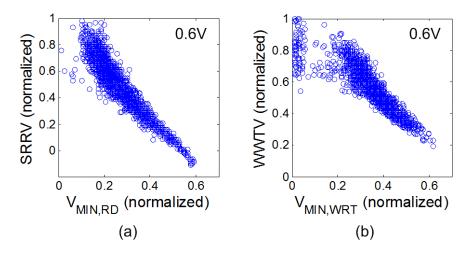

| 4.16 | Scatter plots for (a) SRRV versus $V_{MIN,RD}$ and (b) WWTV versus $V_{MIN,WRT}$                                                                        |    |

|      | measured in a 64kb functional SRAM sub-array demonstrating excellent cor-                                                                               |    |

|      | relation near failure. SRRV and WWTV are measured at $V_{DD} = 0.6V$ ; a                                                                                |    |

| 1 17 | $100mV$ word-line weak write is applied during $V_{MIN,WRT}$ characterization.                                                                          | 75 |

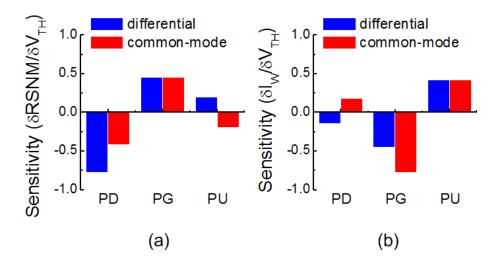

| 4.17 | Sensitivity of (a) RSNM and (b) WNM to differential and common-mode                                                                                     |    |

|      | variations in the pull-down, pass-gate, and pull-up transistor pairs within an                                                                          | 77 |

| 110  | SRAM bitcell [32]                                                                                                                                       | 77 |

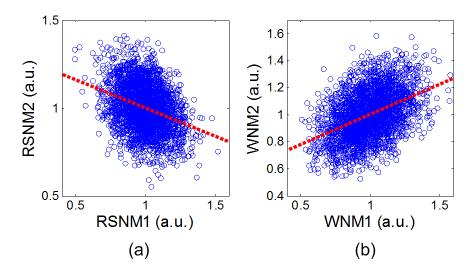

| 4.18 | , ,                                                                                                                                                     |    |

|      | a negative correlation between the read stability of the two data polarities.  (b) Scatter plot of WNM1 versus WNM2, along with a linear fit, showing a |    |

|      | positive correlation between the writeability for the two data polarities                                                                               | 78 |

|      | - DANTOLYA ANTEGRADOR DADWAAL ORG WELDGADIIDV TOL DIE DWO CADA DOMES                                                                                    | 10 |

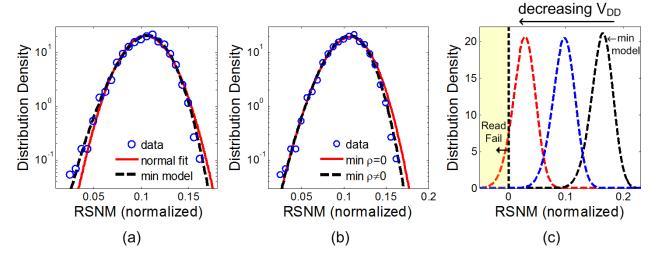

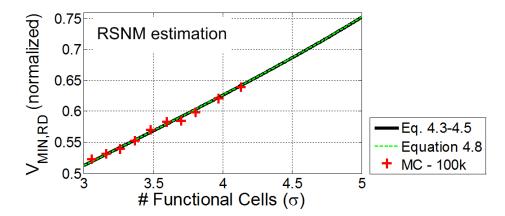

| 4.19 | Semi-log plot of the distribution density of the actual RSNM - taken as the minimum of two RSNMs - extracted from a $3k$ -sample MC simulation fitted in (a) using the normal $PDF$ and the $PDF$ defined by equations $4.3$ - $4.5$ ; and |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | in (b) using the $PDF$ defined by equations 4.3-4.5 with $\rho = 0$ and with the                                                                                                                                                           |    |

|      | extracted $\rho$ value. The worst-case tail matches nicely to the $PDF$ defined by                                                                                                                                                         |    |

|      | equations 4.3-4.5 with and without modeling the $\rho$ . (c) Fitted $PDF$ s using                                                                                                                                                          |    |

|      | equations 4.3-4.5 for three different values of $V_{DD}$ . The probability of read                                                                                                                                                         |    |

|      | stability failure at each value of $V_{DD}$ is equal to the area under the $PDF$ and                                                                                                                                                       |    |

|      | to the left of the line $y = 0$                                                                                                                                                                                                            | 79 |

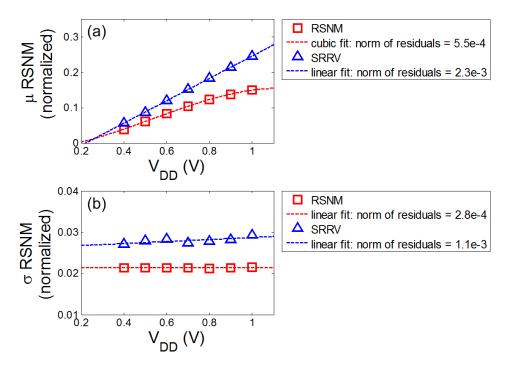

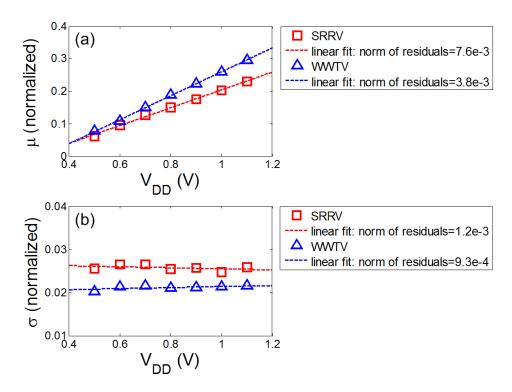

| 4.20 | The simulated (a) $\mu$ and (b) $\sigma$ for RSNM and SRRV, using 3k-sample MC simulations, as a function of $V_{DD}$ along with the corresponding polynomial fit                                                                          |    |

|      | and the norm of the residuals                                                                                                                                                                                                              | 81 |

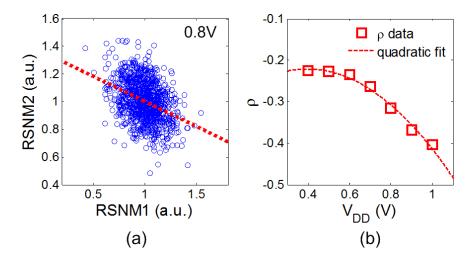

| 4.21 | , ,                                                                                                                                                                                                                                        |    |

|      | a negative correlation. Here, $V_{DD} = 0.8V$ is selected without any particular                                                                                                                                                           |    |

|      | reason. (b) The coefficient of correlation, $\rho$ , between RSNM1 and RSNM2 as                                                                                                                                                            |    |

| 4 00 | a function of $V_{DD}$ along with the quadratic fit                                                                                                                                                                                        | 82 |

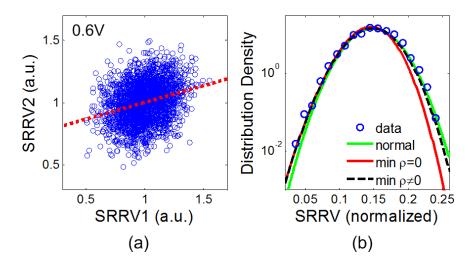

| 4.22 | 1                                                                                                                                                                                                                                          |    |

|      | cells allowing the characterization of SRRV for both data polarities, showing                                                                                                                                                              |    |

|      | a positive correlation. (b) Semi-log plot of the distribution density of SRRV                                                                                                                                                              |    |

|      | extracted from a 5k-sample MC simulation fitted using the normal <i>PDF</i> and                                                                                                                                                            |    |

|      | the $PDF$ s defined by equations 4.3-4.5 and by equation 4.8. The worst-case                                                                                                                                                               |    |

|      | tail matches nicely to the $PDF$ s defined by either equations 4.3-4.5 or equation                                                                                                                                                         |    |

|      | 4.8. A 5k-sample MC simulation is used to extract adequate samples of both SRRV1 and SRRV2 for accurate $\rho$ extraction                                                                                                                  | 83 |

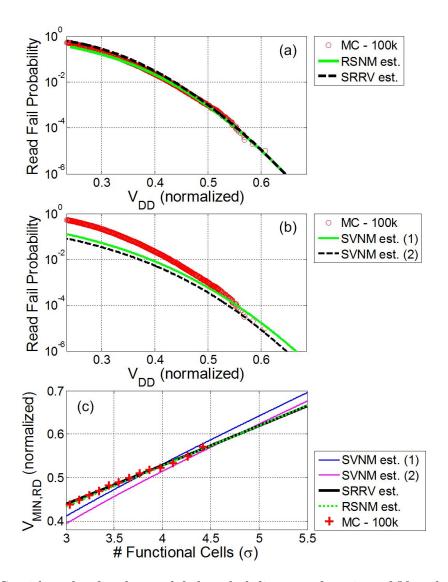

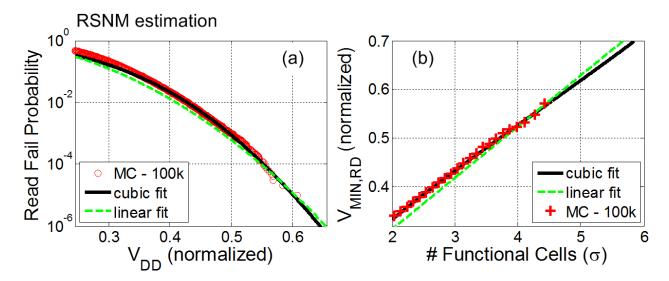

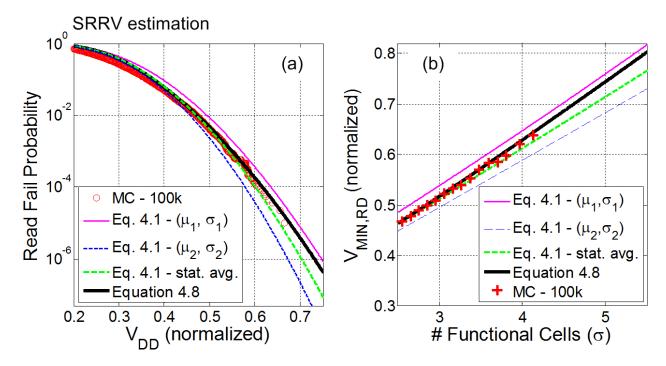

| 1 22 | Semi-log plot for the read fail probability as a function of $V_{DD}$ , both extracted                                                                                                                                                     | 0. |

| 4.20 | from a 100k-sample MC simulation and estimated (a) using RSNM and SRRV,                                                                                                                                                                    |    |

|      | and (b) using SVNM. (c) $V_{MIN,RD}$ as a function of the number of functional                                                                                                                                                             |    |

|      | SRAM cells, in units of $\sigma$ , extracted from a 100k-sample MC simulation and                                                                                                                                                          |    |

|      | estimated using RSNM, SRRV, and SVNM. The estimations using RSNM and                                                                                                                                                                       |    |

|      | SRRV matches very well against the results from MC, whereas the estimation                                                                                                                                                                 |    |

|      | using SVNM does not. The estimation using SVNM is done twice - with $\mu$                                                                                                                                                                  |    |

|      | and $\sigma$ fitted using (1) a full range of $V_{DD}$ values and (2) only higher $V_{DD}$ values.                                                                                                                                         | 84 |

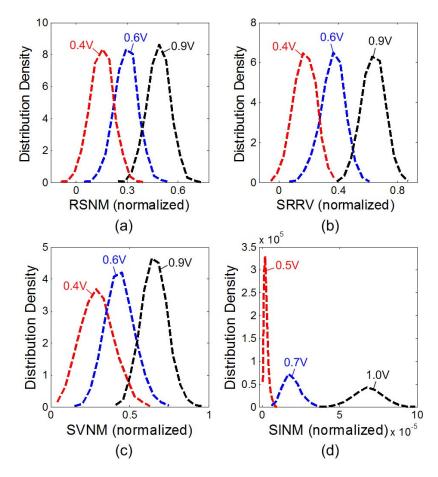

| 4.24 | Distribution densities, at three different supply voltages, of (a) RSNM, (b)                                                                                                                                                               |    |

|      | SRRV, (c) SVNM, and (d) SINM extracted from 3k-sample MC simulations                                                                                                                                                                       |    |

|      | for a single data polarity. The distributions of both SVNM and SINM become                                                                                                                                                                 |    |

|      | non-Gaussian as $V_{DD}$ is reduced                                                                                                                                                                                                        | 85 |

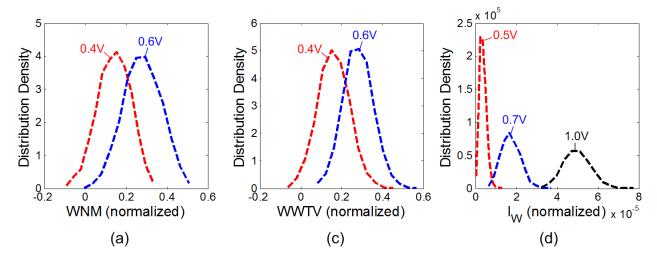

| 4.25 | Distribution densities of (a) WNM, (b) WWTV, and (c) $I_W$ extracted from                                                                                                                                                                  |    |

|      | 3k-sample MC simulations for a single data polarity. The distribution of $I_W$                                                                                                                                                             |    |

|      | become non-Gaussian as $V_{DD}$ is reduced                                                                                                                                                                                                 | 86 |

| 4.26 | (a) Semi-log plot for the read fail probability as a function of $V_{DD}$ ; and (b)                                                                                                                                                        |    |

|      | $V_{MIN,RD}$ as a function of the number of functional SRAM cells, in units of                                                                                                                                                             |    |

|      | $\sigma$ - both extracted from a 100k-sample MC simulation and estimated using                                                                                                                                                             |    |

|      | RSNM, with $\mu$ fitted either linearly or to a $3^{rd}$ order polynomial                                                                                                                                                                  | 87 |

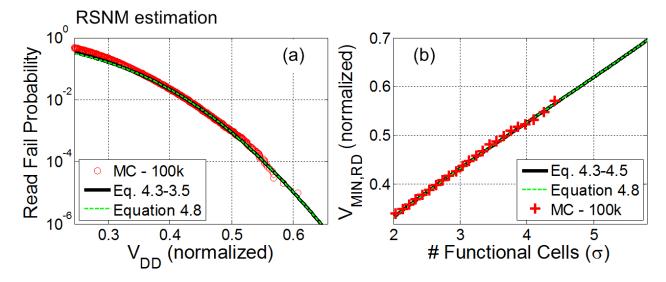

| 4.27 | (a) Semi-log plot for the read fail probability as a function of $V_{DD}$ ; and (b) $V_{MIN,RD}$ as a function of the number of functional SRAM cells, in units of                           |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $\sigma$ - both extracted from a 100k-sample MC simulation and estimated using                                                                                                               |    |

|      | RSNM, with its $PDF$ modeled by either equations 4.3-4.5 or equation 4.8                                                                                                                     | 87 |

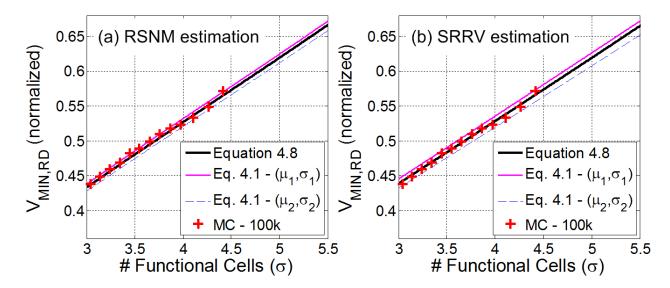

| 4 28 | $V_{MIN,RD}$ as a function of the number of functional SRAM cells, in units of $\sigma$ ,                                                                                                    | 01 |

| 1.20 | both extracted from a 100k-sample MC simulation and estimated using - (a)                                                                                                                    |    |

|      | RSNM with its $PDF$ modeled by either equation 4.8 or equation 4.1; and (b)                                                                                                                  |    |

|      | SRRV with its $PDF$ modeled by either equation 4.8 or equation 4.1                                                                                                                           | 88 |

| 4 29 | $V_{MIN,RD}$ as a function of the number of functional SRAM cells, in units of                                                                                                               | 00 |

| 1.20 | $\sigma$ , both extracted from a 100k-sample MC simulation and estimated using                                                                                                               |    |

|      | RSNM, with its $PDF$ modeled by either equations 4.3-4.5 or equation 4.8. A                                                                                                                  |    |

|      | systematic mismatch is introduced to the bitcell through a differential adjust-                                                                                                              |    |

|      | ment in the $L_G$ of the pull-down transistor pair - producing a $\sim 8\%$ shift in                                                                                                         |    |

|      | $\mu$ and a $\sim 6\%$ shift in $\sigma$ between SRRV1 and SRRV2                                                                                                                             | 88 |

| 4.30 |                                                                                                                                                                                              |    |

|      | $V_{MIN,RD}$ as a function of the number of functional SRAM cells, in units of $\sigma$ -                                                                                                    |    |

|      | both extracted from a 100k-sample MC simulation and estimated using SRRV,                                                                                                                    |    |

|      | with its $PDF$ modeled by either equation 4.8 or equation 4.1. A systematic                                                                                                                  |    |

|      | mismatch is introduced to the bitcell through a differential adjustment in the                                                                                                               |    |

|      | $L_G$ of the pull-down transistor pair - producing a $\sim 8\%$ shift in $\mu$ and a $\sim 6\%$                                                                                              |    |

|      | shift in $\sigma$ between SRRV1 and SRRV2                                                                                                                                                    | 89 |

| 4.31 | The (a) $\mu$ and (b) $\sigma$ of SRRV and WWTV, measured for 8k bitcells from                                                                                                               |    |

|      | a 64kb SRAM sub-array, as a function of $V_{DD}$ along with the corresponding                                                                                                                |    |

|      | linear fit and the norm of the residuals                                                                                                                                                     | 90 |

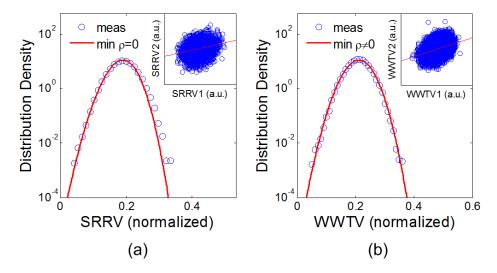

| 4.32 | Semi-log plot of the distribution densities of (a) SRRV, modeled using equa-                                                                                                                 |    |

|      | tion 4.8; and (b) WWTV, modeled using equations 4.3-4.5. Both SRRV and                                                                                                                       |    |

|      | WWTV, in this example, are measured for a 64kb SRAM sub-array. The                                                                                                                           |    |

|      | worst-case tail matches well in both cases. The scatter plots of SRRV2 ver-                                                                                                                  |    |

|      | sus SRRV1 and WWTV2 versus WWTV1 are included to show the positive                                                                                                                           |    |

|      | correlation from measurement                                                                                                                                                                 | 91 |

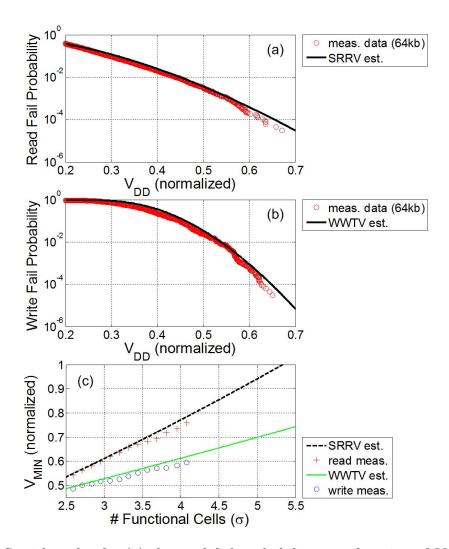

| 4.33 | Semi-log plot for (a) the read fail probability as a function of $V_{DD}$ , measured                                                                                                         |    |

|      | for a 64kb SRAM sub-array and estimated using SRRV; and (b) the write fail                                                                                                                   |    |

|      | probability as a function of $V_{DD}$ , measured for a 64kb SRAM sub-array and                                                                                                               |    |

|      | estimated using WWTV. (c) $V_{MIN,RD}/V_{MIN,WRT}$ as a function of the number                                                                                                               |    |

|      | of functional SRAM cells, in units of $\sigma$ - both measured and estimated. To                                                                                                             |    |

|      | reduce writeability and expose higher $V_{MIN,WRT}$ values, NMOS RBB and                                                                                                                     |    |

|      | PMOS FBB are applied during $V_{MIN,WRT}$ and WWTV measurements - word-                                                                                                                      |    |

|      | line weak write is not applied because WWTV characterization requires direct                                                                                                                 |    |

|      | word-line control. The data in (c) are so normalized to display both $V_{MIN,RD}$                                                                                                            |    |

|      | and $V_{MIN,WRT}$ results in the same graph. Results indicate good matching                                                                                                                  | 00 |

| 191  | between the estimated values and the measurement data                                                                                                                                        | 92 |

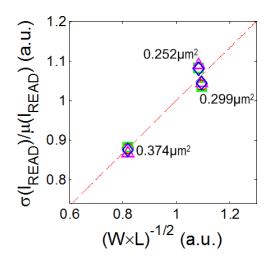

| 4.34 | $\sigma_{IREAD}/\mu_{IREAD}$ , measured from four separate 64kb SRAM sub-arrays, as a function of $1/\sqrt{W} \times \overline{I}$ for three different SPAM bit cell designs with cell areas |    |

|      | function of $1/\sqrt{W} \times L$ for three different SRAM bitcell designs with cell areas of 0.374 $\mu m^2$ 0.200 $\mu m^2$ and 0.252 $\mu m^2$                                            | വാ |

|      | of $0.374  \mu \text{m}^2$ , $0.299  \mu \text{m}^2$ , and $0.252  \mu \text{m}^2$                                                                                                           | 93 |

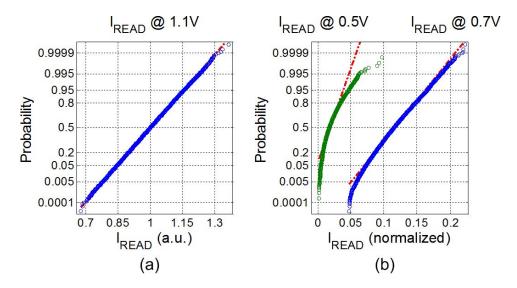

| 4.35 | Normal probability plots for (a) $I_{READ}$ measured at $V_{DD} = 1.1V$ and (b)                                                                           |       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | $I_{READ}$ measured at $V_{DD} = 0.7V$ and $V_{DD} = 0.5V$ . The data in (b) is normal-                                                                   |       |

|      | ized to the mean of $I_{READ}$ measured at $V_{DD} = 1.1V$                                                                                                | 94    |

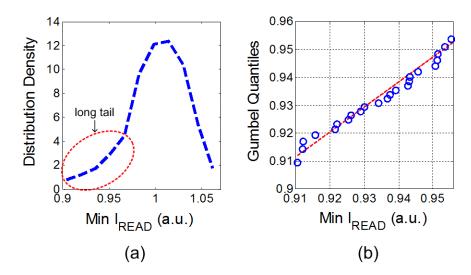

| 4.36 | (a) The distribution density of the measured minimum $I_{READ}$ over a 1kb                                                                                |       |

|      | SRAM block showing a long tail to the left. (b) Gumbel probability plot for                                                                               |       |

|      | the lower tail of the distribution for the measured minimum $I_{READ}$ over a 1kb                                                                         |       |

|      | SRAM block                                                                                                                                                | 94    |

| 4.37 | (a) Layout view for a $20 \times 40$ SRAM array, with gate-poly in the vertical                                                                           |       |

|      | direction, wired for all-internal-node access. Each array inside the test macro                                                                           |       |

|      | is surrounded by wide regions of STI in all directions. (b) $\mu$ of the measured                                                                         |       |

|      | $I_{DSAT}$ for pull-down, pass-gate, and pull-up transistors as a function of the                                                                         |       |

|      | distance from the edge of the array (normalized to the average distance). (c)                                                                             |       |

|      | $\mu$ of the measured $V_{TH,LIN}$ for pull-down, pass-gate, and pull-up transistors                                                                      |       |

|      | as a function of the distance from the edge of the array. (d) $\mu$ of RSNM and                                                                           |       |

|      | $I_W$ as a function of the distance from the edge of the array. All measurements                                                                          |       |

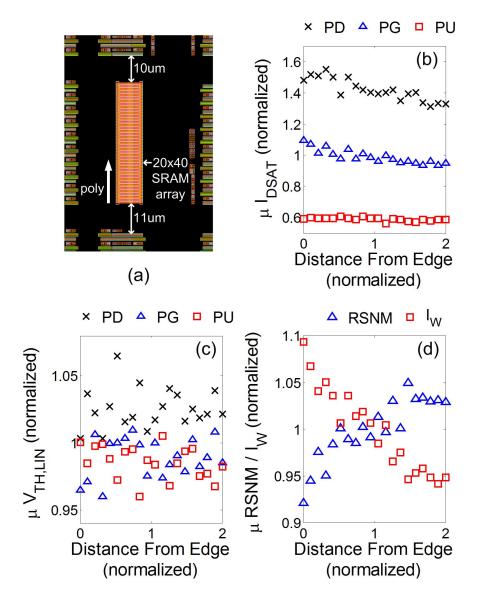

|      | are taken from SRAM macros via all-internal-node access                                                                                                   | 96    |

| 4.38 | Measured (a) SRRV, (b) WWTV, and (c) $I_{READ}$ as a function of row and                                                                                  |       |

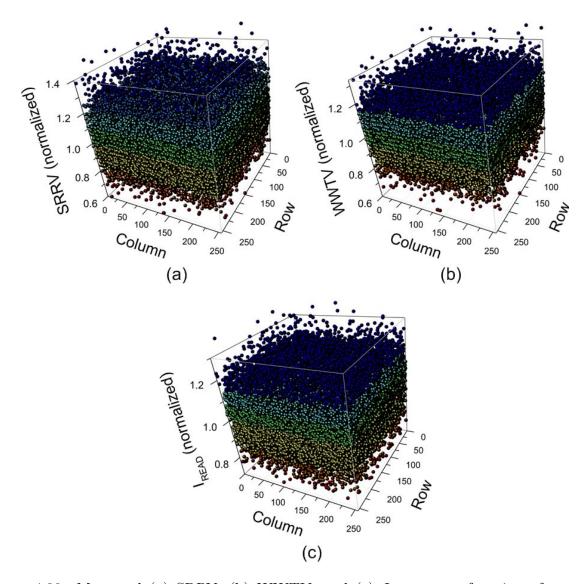

|      | column position within a 256 $\times$ 256 (64kb) functional SRAM sub-array                                                                                | 97    |

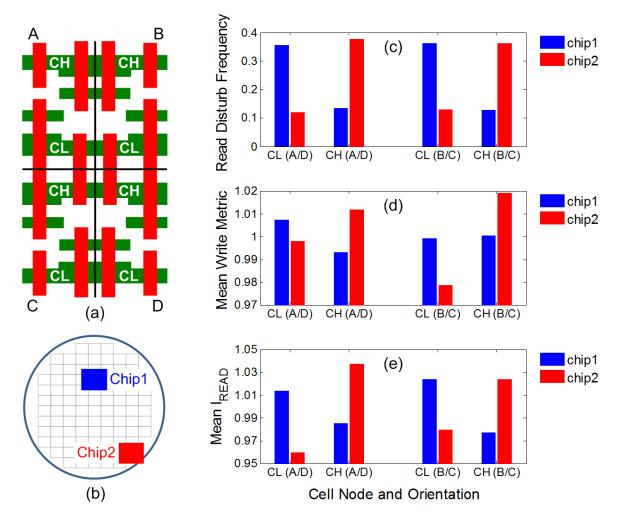

| 4.39 | (a) A 4-cell cluster in an SRAM array showing the 4 cell orientations; the                                                                                |       |

|      | storage nodes of orientations $C$ and $D$ are reversed in the drawing for clar-                                                                           |       |

|      | ification. (b) Wafer map identifying the measured chips. Measured (c) read                                                                                |       |

|      | disturb frequency, (d) $\mu$ of WWTV, and (e) $\mu$ of $I_{READ}$ for two test chips on                                                                   |       |

|      | the same wafer as a function of the cell storage node and the cell orientation.                                                                           | 99    |

| 4.40 | Layout cartoon of an SRAM cell showing the corner rounding of the PMOS                                                                                    |       |

|      | diffusions and the NMOS diffusions                                                                                                                        | 100   |

| 4.41 | 1                                                                                                                                                         |       |

|      | count as a function of $V_{DD}$ during a static read operation, and (c) fail bit                                                                          |       |

|      | count as a function of $V_{DD}$ during a static write operation, measured for 64kb                                                                        | 101   |

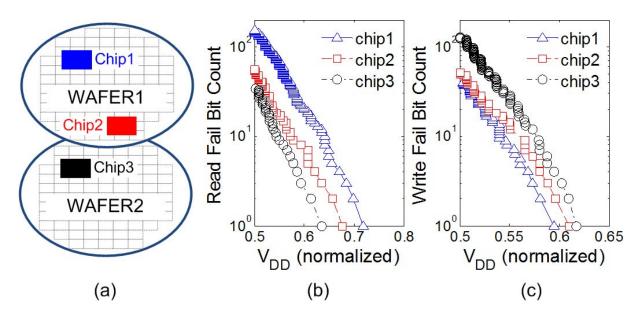

| 1 10 | SRAM sub-arrays on three test chips from two different wafers                                                                                             | 101   |

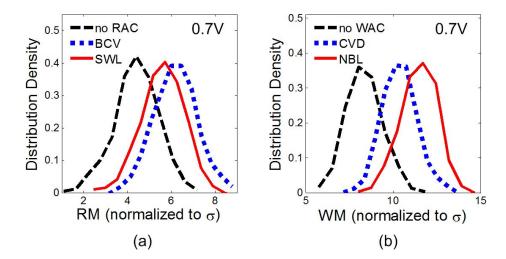

| 4.42 | Distribution densities of (a) measured read margins (using either SRRV or                                                                                 |       |

|      | WRRV) without RAC, and with BCV and SWL; and (b) measured write                                                                                           |       |

|      | margins (using WWTV) without WAC, and with CVD and NBL. Measure-                                                                                          | 100   |

| 1 19 | ments are taken for 2k-samples from a 64kb SRAM sub-array at $V_{DD} = 0.7V$ .                                                                            | 102   |

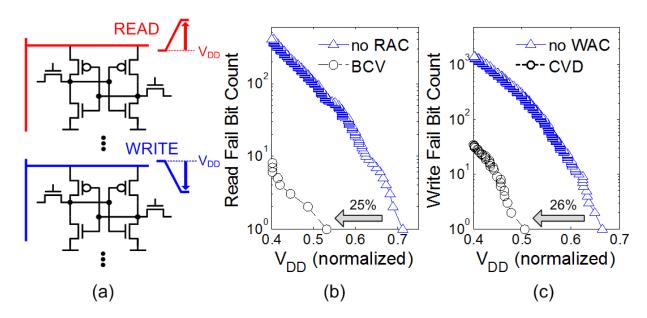

| 4.43 |                                                                                                                                                           |       |

|      | (CVD) scheme for read and write assist. (b) Fail bit count as a function of                                                                               |       |

|      | $V_{DD}$ during a read operation, measured for the same 64kb SRAM sub-array with no read assist circuits (RAC) and with a $100mV$ BCV. (b) Fail bit count |       |

|      | as a function of $V_{DD}$ during a write operation measured for the same 64kb                                                                             |       |

|      | SRAM sub-array with no write assist circuits (WAC) and with a $100mV$ CVD                                                                                 | 103   |

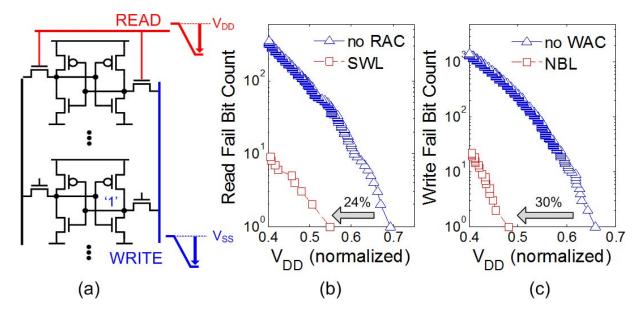

| 1 11 | (a) Simplified schematic of the suppressed word-line (SWL) and the negative                                                                               | .100  |

| 1.11 | bit-line (NBL) scheme for read and write assist. (b) Fail bit count as a function                                                                         |       |

|      | of $V_{DD}$ during a read operation measured for the same 64kb SRAM sub-array                                                                             |       |

|      | with no read assist circuits (RAC) and with a $100mV$ SWL. (b) Fail bit count                                                                             |       |

|      | as a function of $V_{DD}$ during a write operation measured for the same 64kb                                                                             |       |

|      | SRAM sub-array with no write assist circuits (WAC) and with a $100mV$ NBL                                                                                 | 104   |

|      | Side in Sas array with no willo applied off and with a 100ml Tibe                                                                                         | . 101 |

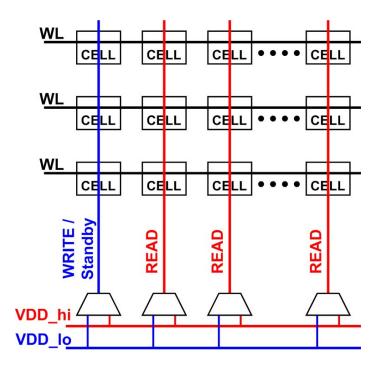

| 4.45 | Circuit diagram for a column based biasing scheme, implemented in [162], to independently achieve high read stability and writeability                                                                                                  | 105 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

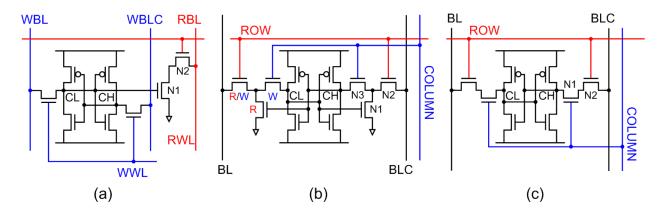

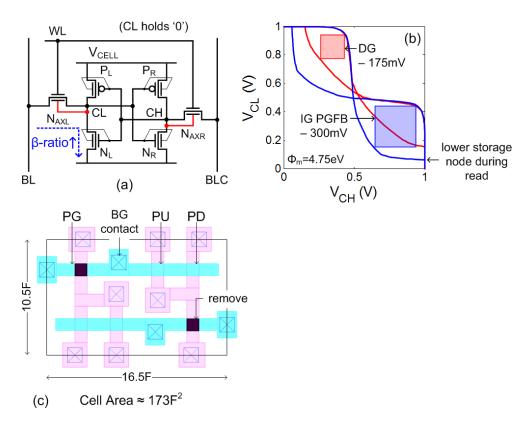

| 5.1  | Schematic of a (a) 8-T dual-port SRAM bitcell, (b) 10-T dual-port cross-point SRAM bitcell, and (c) 8-T single-port cross-point SRAM bitcell                                                                                            | 109 |

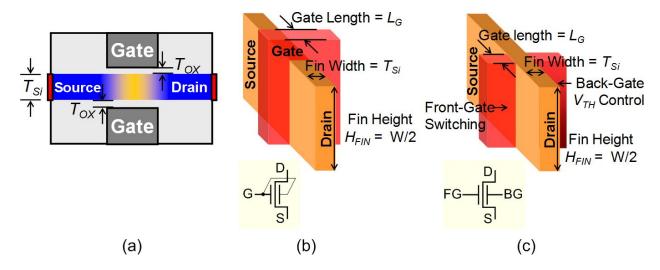

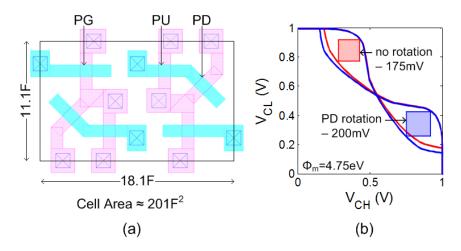

| 5.2  | (a) Cross-sectional schematic of the FinFET structure. The gates of the FinFET can either (b) swing together in double-gated (DG) operation or (c)                                                                                      | 110 |

| 5.3  | swing independently in independently-gated (IG) operation                                                                                                                                                                               | 110 |

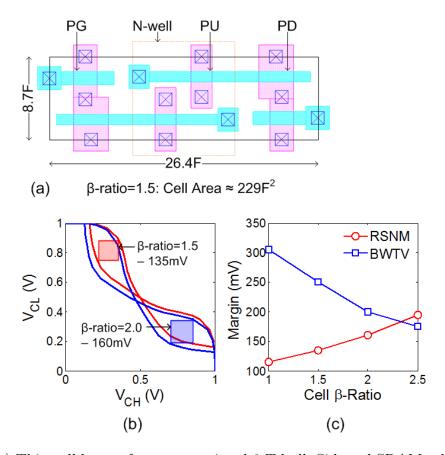

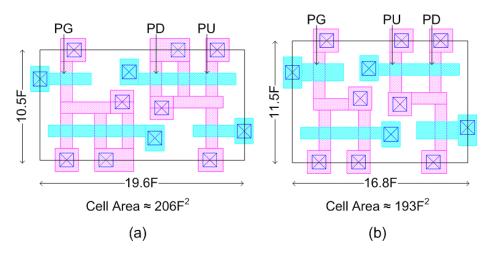

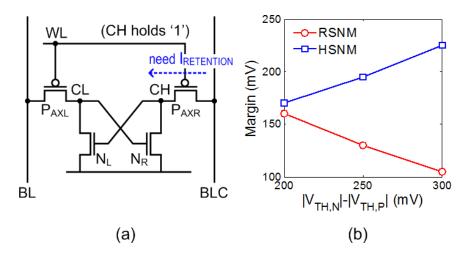

|      | widths of the pull-down transistors                                                                                                                                                                                                     | 113 |

| 5.4  | Thin-cell layout for a conventional double-gated (DG) FinFET based 6-T SRAM cell with $\beta$ -ratio = 1. The dark outline indicates the area of one                                                                                    |     |

|      | memory cell                                                                                                                                                                                                                             | 114 |

| 5.5  | Thin-cell layout for a conventional double-gated (DG) FinFET based 6-T                                                                                                                                                                  |     |

|      | SRAM cell with (a) 2 fins in the pull-down transistors and (b) $L_{G,pass-gate} =$                                                                                                                                                      | 111 |

| 5.6  | $2 \times L_{G,pull-down}$ . The dark outline indicates the area of one memory cell Read butterfly-curves for a conventional DG FinFET based 6-T SRAM cell with (a) 1 fin and 2 fins in the pull-down transistors, and (b) $L_G = 22nm$ | 114 |

|      | and $L_G = 44nm$ for the pass-gate transistors. (c) Impact of cell $\beta$ -ratio, determined by the number of pull-down transistor fins, on the cell read- and write-margins (RSNM is used as the read metric and BWTV is used as the  |     |

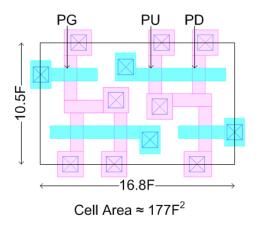

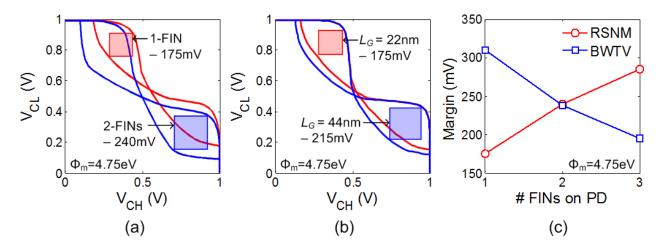

|      | write metric).                                                                                                                                                                                                                          | 115 |

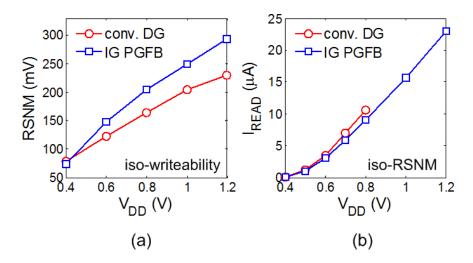

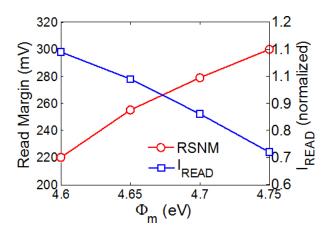

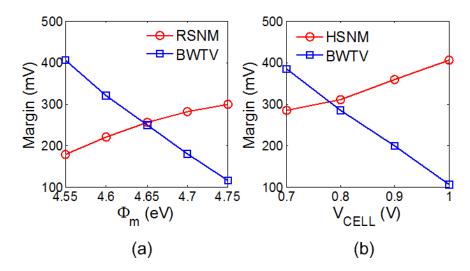

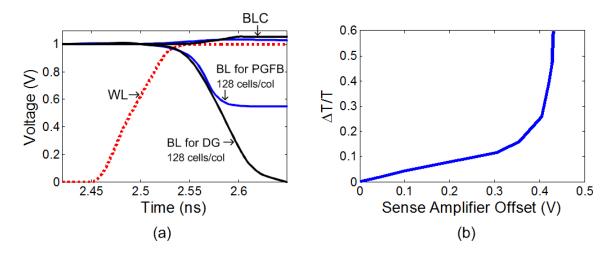

| 5.7  | (a) Thin-cell layout for a DG FinFET based 6-T SRAM cell with fin-rotation to increase the effective cell $\beta$ -ratio. The outline indicates the area of one                                                                         |     |

|      | memory cell. (b) Read butterfly-curves for a DG FinFET based 6-T SRAM                                                                                                                                                                   | 110 |

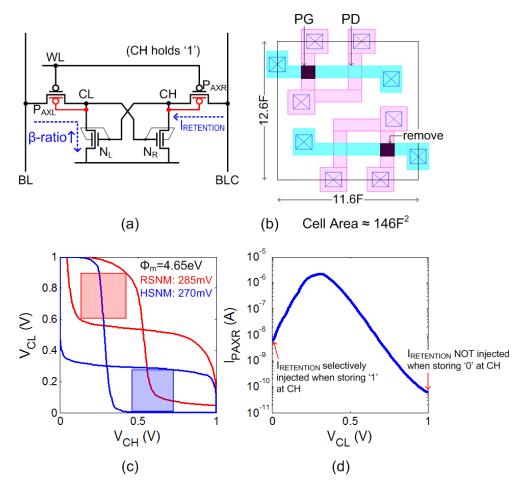

| 5.8  | cell with fin-rotation, showing improved RSNM                                                                                                                                                                                           | 116 |

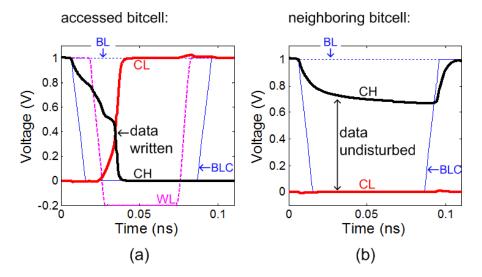

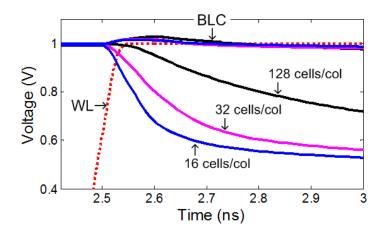

|      | (b) Read butterfly-curves for an IG FinFET based 6-T SRAM cell with dynamic PGFB, showing significantly improved RSNM. (c) Thin-cell layout for an IG FinFET based 6-T SRAM cell with dynamic PGFB, indicating zero                     |     |

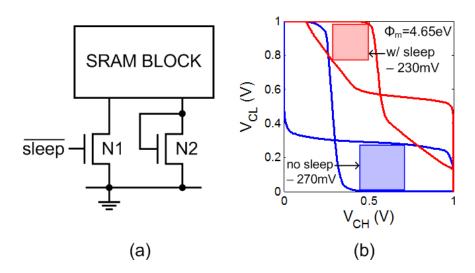

|      | area penalty compared to the conventional DG 6-T design. The dark outline                                                                                                                                                               |     |