# Lawrence Berkeley National Laboratory

Lawrence Berkeley National Laboratory

### Title

Understanding and Mitigating Multicore Performance Issues on the AMD Opteron Architecture

Permalink https://escholarship.org/uc/item/9k38d8ms

### Authors

Levesque, John Larkin, Jeff Foster, Martyn <u>et al.</u>

**Publication Date**

2007-03-07

## Understanding and Mitigating Multicore Performance Issues on the AMD Opteron<sup>™</sup> Architecture

John Levesque, Jeff Larkin, Martyn Foster, Joe Glenski, Garry Geissler, Stephen Whalen Cray Inc.

> Brian Waldecker AMD Inc.

Jonathan Carter, David Skinner, Helen He, Harvey Wasserman, John Shalf NERSC Division Lawrence Berkeley National Laboratory

> Hongzhang Shan, Erich Strohmaier Computational Research Division Lawrence Berkeley National Laboratory

> > March 7, 2007

This work was supported by the Director, Office of Science, Office of Advanced Scientific Computing Research of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

## Understanding and Mitigating Multicore Performance Issues on the AMD Opteron<sup>™</sup> Architecture

## Abstract

Over the past 15 years, microprocessor performance has doubled approximately every 18 months through increased clock rates and processing efficiency. In the past few years, clock frequency growth has stalled, and microprocessor manufacturers such as AMD have moved towards doubling the number of cores every 18 months in order to maintain historical growth rates in chip performance. This document investigates the ramifications of multicore processor technology on the new Cray XT4<sup>™</sup> systems based on AMD processor technology. We begin by walking through the AMD single-core and dual-core and upcoming quad-core processor architectures. This is followed by a discussion of methods for collecting performance counter data to understand code performance on the *Crav XT3*  $^{\text{TM}}$  and *XT4*  $^{\text{TM}}$  systems. We then use the performance counter data to analyze the impact of multicore processors on the performance of microbenchmarks such as STREAM, application kernels such as the NAS Parallel Benchmarks, and full application codes that comprise the NERSC-5 SSP benchmark suite. We explore compiler options and software optimization techniques that can mitigate the memory bandwidth contention that can reduce computing efficiency on multicore processors. The last section provides a case study of applying the dual-core optimizations to the NAS Parallel Benchmarks to dramatically improve their performance.<sup>1</sup>

### Introduction

Recent trends in microprocessors have shown a decreased rate of growth in clock speed as a result of having approached the power and thermal limits of current chip technology. As a result, additional computing power is being added to CPUs in the form of multiple compute cores operating at roughly constant clock rates. While the impact of multi-core parallelism at the commodity/desktop level is modest, the HPC sector, which needs regular significant increases in available computing power, is confronted with concurrencies that race upward in lieu of faster compute elements. Today's supercomputers harness tens of thousands of cores, and those on the drawing board are built from millions of cores. These architectures are implicitly betting that additional cores can be efficiently used. It is therefore important to understand at the level of HPC applications how these many thousands of tasks can make good use of each core.

Multicore computing is a paradigm shift at least as dramatic as the transition from vector platforms to MPPs. Whereas the transition to MPPs required careful examination of how best to use local versus remote (off node) resources, the transition to multicores requires examination of how best to share resources within and connected to the CPU. Multiple compute cores on a single CPU also introduce an additional layer in the hierarchy of parallelism used in scientific

<sup>&</sup>lt;sup>1</sup> AMD, Opteron, ACML, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Cray, XT3, XT4, CrayPAT, and LibSci are trademarks of Cray Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

codes. While this presents some new opportunities, it also presents new challenges in the form of inter-core resource conflict and contention.

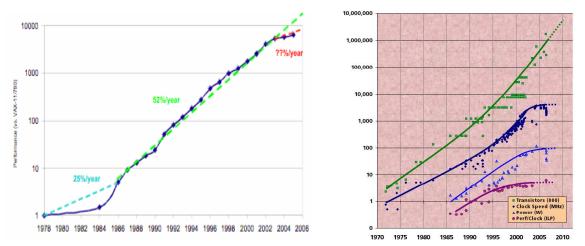

Figure 1: Recent trends in microprocessor performance and architecture. The figure on the left shows the average SPEC-Int performance over the past three decades (courtesy of David Patterson, from Patterson & Hennessy Vol. 4). The figure on the right shows that while the number of transistors that can be packed onto a chip continues to improve, all other traditional performance metrics (clock rate, ILP and power density) are flat-lining (courtesy of Kunle Olukotun, Lance Hammond, Herb Sutter, and Burton Smith). The industry response is to move to multicore chips.

The microprocessor industry's move to multicore is well under way, and for many reasons it is inevitable. Figure 1 shows recent trends in microprocessor performance. The diagram on the left shows the past three decades of exponential performance improvements for individual microprocessor cores as measured by SPEC-Int. However, starting in 2003, that growth has tailed off dramatically. The chart on the right shows that Moore's Law, which says silicon lithography improvements will enable 2x more transistors to be fit onto a chip approximately every 18 months, is still alive and well. However, all of the traditional sources of processor performance improvement (instruction-level parallelism [ILP], clock speed, and increased power density that results from pushing up the clock speed) are all flat-lining around the same time that the graph on the left shows departure from the 52%/year SPEC benchmark scaling. This indicates that using more transistors per chip to boost performance of individual CPUs, either by clock frequency scaling or increased ILP, is no longer effective. Consequently, the industry response is to move to multiple cores as their primary strategy for maintaining the per-chip performance improvements that have, until recently, matched the rate of Moore's law lithography improvements.

Since the move to multicore processors is inevitable, it is important to examine the consequences of this architectural change for application performance and to understand how to mitigate the performance bottlenecks that arise from these architectural choices. This document focuses on the performance bottlenecks that may arise when using multi-core AMD Opteron<sup>™</sup> sockets. While most of the data herein are have been gathered on dual core systems, we expect quad and higher core systems may further constrain available memory bandwidth per core. Given the current and likely continued trends in super-scalar systems, it is important that the application programmer understand the details of the imbalance of the system and techniques that can be used to restructure applications to more effectively utilize the caches and translation lookaside

buffers (TLB), and to take advantage of streaming SIMD extension (SSE) instructions to achieve the highest possible performance.

The first sections of the report document the architecture of the Opteron<sup>™</sup> socket, concentrating on those features of the architecture that must be understood to avoid memory contention. We then describe the performance tools available to obtain hardware counter data and how that can be used to better understand how the application is using the cores. Next, we use performance counter data to examine the effects of multicore AMD Opteron<sup>™</sup> processors on the efficiency of the NERSC-5 procurement benchmarks, the NAS kernels run in serial mode, and finally some microbenchmarks (STREAM and Apex-MAP) that isolate the source of performance bottlenecks. The last section describes how to optimize codes to improve multicore performance, including compiler options and techniques for restructuring an application to be more cachefriendly. In that section we will also discuss the use of SSE instructions, which while not particular to dual-core issues, are an important way to achieve higher performance on the socket.

## AMD Opteron ™ 1000, 2000, and 8000 Series Multicore Processor Architecture (also known as AMD Rev F or AMD NPT Family 0Fh)

## **Cache Organization**

The Opteron<sup>TM</sup> processors have level 1 instruction (L1I) and data (L1D) caches. There is a level 2 cache (L2) that can hold either instructions or data. The L1 caches and L2 cache are exclusive of each other. This means, in the case of data for example, an item of cached data will not be in both the L1D and the L2 caches at the same time. This allows the combined L1 and L2 caches to hold more data but may require more write-backs of data from L1 into L2 than in a design where the L1 contents are a subset of the L2 contents.

The L1 data cache is 64 KB in size and organized with 64 byte lines and is two-way set associative. Virtual address bits 14:6 determine which set is selected, and each of the two ways (i.e., lines) of this set is checked for a hit.

The L2 cache is 1 MB in size, 16-way set associative, and functions as a *victim cache*. This means it is filled with data that was previously in the L1 cache but was evicted as a result of the L1 cache replacement policy. An exception to this is the hardware prefetcher that speculatively prefetches data into the L2 based on detection of access patterns. The most common scenario, and that most amenable to support from hardware and software assistance, is one where the program is sequentially striding through the cache lines of the array. In contrast to the hardware prefetch mechanism, using software prefetch instructions—prefetchnta and prefetcht0/1/2 —will result in data being prefetched into the L1 cache. The rationale of these instructions is that explicitly issued software prefetches should be treated as less speculative and more likely to be used, therefore fetching into the L1 cache will be more optimal. The prefetchnta instruction biases the prefetched data to get evicted before other data as it means the data is non-temporal in nature.

For many applications the hardware prefetch mechanism should suffice, but for others that may access multiple streams of data, the software prefetch instructions allow explicit prefetching of

some or all streams into L1 cache. Many compilers provide tuning flags that give the compiler strong hints for utilizing prefetch instructions during code generation.

The L1 data cache is indexed using virtual address bits, but the tags are comprised of physical address bits. This allows indexing to be done before translation has completed. Due to the size of the 64 KB L1 cache, there are not enough untranslated bits (bits that fall through directly from virtual to physical address) available to index the cache using physical address bits only. The practical implication of this is that virtual to physical mappings can affect how data is placed in the cache and therefore affect performance.

Under Linux (or any OS that lazily allocates pages only when touched), there is a possibility that using translated address bits to index a cache can result in lost performance due to subtle interactions between the OS behavior and the cache design. An important rule of thumb for programmers is to initialize all data before reading it. This may sound obvious and is good programming practice, but there have been cases where data was assumed to be initialized to zero and read without initializing it to zero. However, under Linux, uninitialized data usually results in multiple virtual address pages being mapped to the same special physical page (called the *zero page*). Upon the first write to such a virtual page, Linux's *copy-on-write* mechanism causes a new physical page to be allocated and zeroed. Without such copy-on-write allocation occurring, accesses to different virtual pages that map to the same physical page can result in cache thrashing and poor performance. Since the L2 serves as a victim cache, the way in which a cache line would move from one index set to another set in the L1 (one form of thrashing) would be to get evicted to the L2 and then brought back into the L1.

A more subtle caveat has to do with each L1 cache line (64 bytes) being implemented in an eight-bank interleaved fashion. This means there are eight *banks* in the L1, and bits 5:3 of the virtual address select the bank. So a 64 byte cache line is really laid out evenly across the eight banks, with 8 bytes in each bank. A *bank conflict* can occur if two virtual addresses have different indices (bits 14:6) but the same bits for their bank (bits 5:3). In this case, only one load per cycle from L1 will be allowed rather than two per cycle if going to different banks. Practically speaking, if a loop appears to be having fewer loads per cycle than expected (possibly using the hardware performance counters), examination of the virtual addresses loaded in the loop may reveal such a conflict.

Besides the possibility of a cache bank conflict reducing performance as described above, the offsets between array addresses can, in rare instances, result in pathologically bad scenarios where only a portion of the cache gets effectively used. This can usually be solved by adding some padding to the suspect arrays, either by explicitly sizing them larger or using compiler flags to direct additional padding to be generated.

### **Translation Lookaside Buffers**

The translation lookaside buffers (TLBs) provide a faster method of translating virtual addresses to physical addresses without requiring accessing the multiple levels of page tables. There are two levels of TLBs. The level 1 TLB (L1 TLB) can hold 40 address translations. Of these 40, 8 are for 2 MB *large* pages and 32 are for 4 KB *regular* pages. The level 2 TLB (L2 TLB) can hold 512 translations for 4 KB pages only. Thus the TLB reach is 8 \* 2 MB = 16 MB for large

pages and 512 \* 4 KB = 2 MB for regular pages. In large-page mode, two of the TLB pages are pinned by the OS, so in practice, only six of the pages are available to applications (12 MB of coverage).

The L1 TLB is fully associative, and the L2 TLB is four-way set associative. If a program's data will fit within the 16 MB reach of the L1 TLB large pages, using large pages may be of benefit. However if the data exceeds that size, using small pages may actually perform better due to the L2 TLB and actual access patterns. Even codes that have relatively low page miss rates in small page mode can suffer when using large pages because so few pages are available. For instance, a code that walks linearly through seven or more distinct arrays will also thrash a six-entry TLB. Codes that rely on indirect access, such as row-compressed sparse matrix solvers or codes that use explicit representations of unstructured meshes, will consume one page per level of indirection. In those cases, the smaller page sizes may offer a lower miss rate despite smaller coverage of the memory, due to the larger numbers of pages available to the application. The 1 GB page sizes available in the quad-core system may alleviate this problem, but the 1 GB pages may prove impractical if an entire page (1 GB of the node memory) must be owned by the OS image (that would make 1 GB of the node memory inaccessible to applications).

## **Data Prefetch**

Both hardware and software based prefetch mechanisms are supported in the Opteron<sup>™</sup> processors.

The hardware prefetch mechanism detects and prefetches cachelines from main memory into the L2 cache. Detection of a stream for prefetching is based on detecting a pattern of increasing or decreasing successive cachelines. It takes two contiguous cacheline fetches, 1 and 1+1, that miss in the L2 to trigger the prefetch mechanism. Upon detection of this pattern, the prefetch hardware will initiate a fetch of the cache line 1+3. Accesses in strides larger than a single cacheline will not trigger the hardware prefetcher. Any sequence of L1 misses to successive cachelines can trigger the hardware prefetcher if tracking resources are available, including software prefetches that miss in the L1. The prefetchnta is an exception to this; since its intent is to avoid cache pollution, prefetchnta will not trigger the hardware prefetcher.

The facilities for software prefetching consist of

- prefetching via loads (standard mov instruction)

- prefetch, prefetcht0, prefetcht1, and prefetcht2 instructions

- prefetchw instruction

- prefetchnta instruction

The prefetch and prefetcht0/t1/t2 instructions all do the same thing on current generations of processors. These software prefetch instructions will bring data into the L1 data cache rather than the L2 as the hardware prefetch mechanism does. The t0/t1/t2 versions of the prefetch instructions are implementation dependent and may in future designs indicate what level of the cache hierarchy should serve as the destination for prefetched data. Software prefetch is always honored unless a load, store, or hardware prefetch to the same cacheline overrides it. There can be up to eight outstanding L2 misses at a time per core, regardless of whether they are due to load, store, or software prefetch instructions.

The prefetchw instruction provides a hint to the processor that the prefetched data is likely to be modified later and it may be better to bring it into the cache in exclusive mode rather than shared so that an upgrade to modified state can be done more efficiently. Currently this instruction is equivalent to a regular prefetch instruction, however.

The prefetchnta indicates the data being prefetched is non-temporal in nature and unlikely to be reused prior to being evicted from the cache. In this case, the data is still brought in to the L1 cache but is marked in a way to indicate it is not recently used and thus will be favored for replacement before other cachelines in its congruence class. This is useful for data that is not being written only. For data that is only being written, such as large array initializations or the destination of a memory block copy, it is recommended that the processor's write combining store mechanism be used.

Some general rules of thumb and remarks related to software prefetching are:

- Software prefetching six to eight cachelines ahead is typically good, as the latency of a prefetch instruction that misses in the L2 is on the order of 100 cycles. The latency for a software prefetch that hits in the L2 is on the order of 13 cycles.

- Try to have at least 100 cycles worth of computation in loop iterations between software prefetch instructions.

- Try to unroll loops so that each iteration works on an entire cacheline at a minimum. Multiple cachelines per iteration should be OK as well.

- Avoid multiple software prefetches to the same cacheline.

- Neither hardware nor software prefetches will be allowed to generate page fault exceptions. However, a prefetch that misses in the TLB will cause a TLB fill to be initiated.

For data that is being written and consists of one or more entire cachelines that are not likely to be used again soon, it is recommended that write combining store instructions be utilized. These are the mount versions of the mouinstructions. They will utilize special write combining store buffers in the processor and are flushed to main memory when an entire cacheline-sized buffer fills up. This reduces cache pollution for data unlikely to be needed again soon and enables more efficient write transactions into main memory. This will be faster than a prefetchw instructions since the cacheline is not first read from memory. Write combining instructions are not recommended, however, if the memory region being written to has been marked a "write-combining" in the processor's memory type range registers (MTRRs) or page attribute tables (PAT). One other caveat is that use of write combining stores may require a fence instruction be placed after the last such store in some cases for program correctness. Appendix B of the document "Software Optimization Guide for AMD64 Processors" describes more details about how the write combining store facility is implemented.

Table 1 shows what is generally the best prefetch strategy based on the dataset size and type of accesses. In this table, mount refers to any of the various flavors of non-temporal mount instructions (integer, float, packed, etc.). The term prefetch refers to any of the software prefetch/t0/t1/t2 instructions.

In the cases of sequential read-only and sequential read-write, it may be beneficial to issue two prefetch or two prefetchw instructions before entering a loop to jump start the hardware prefetcher. This may also cause subsequent software prefetches inside the loop to hit in the L2. If so, a software "prefetch-ahead" distance of less than the six to eight cachelines mentioned earlier may be preferable.

| Data                  | Less than 1/2               | Less than 1/2 L2 size       | ess than ½ L2 size or of unknown size |             |  |  |

|-----------------------|-----------------------------|-----------------------------|---------------------------------------|-------------|--|--|

|                       | L1 size                     | Reused                      | Not Reused                            | L2 size     |  |  |

| Read only             | prefetch or prefetchnta     | prefetch                    | prefetchnta                           | prefetchnta |  |  |

| Sequential read only  | hwprefetcher<br>+ prefetch  | hwprefetcher +<br>prefetch  | prefetchnta                           | prefetchnta |  |  |

| Read-write            | prefetchw                   | prefetchw                   | prefetchnta                           | prefetchnta |  |  |

| Sequential read-write | prefetchw                   | prefetchw                   | prefetchnta                           | prefetchnta |  |  |

| Write only            | prefetchw                   | prefetchw                   | movnt                                 | movnt       |  |  |

| Sequential write only | hwprefetcher<br>+ prefetchw | hwprefetcher +<br>prefetchw | movnt                                 | movnt       |  |  |

Table 1. Summary of prefetch strategies.

## **Upcoming Quad-Core Changes**

The upcoming quad-core processors provide a number of enhancements to improve performance. Highlights recently disclosed include:

- Support for an additional large page size of 1 GB. (4 KB and 2 MB are still supported.)

- A fully associative 48-entry L1 TLB where all 48 entries may be used for any of the three pages sizes (4 KB, 2 MB, 1 GB).

- A L2 TLB that can hold 512 4-KB page translations or 128 2-MB page translations.

- A 2 MB L3 cache is shared by the four cores and functions as a victim cache for each core's private L2 cache. The L2 caches are 512 KB per core. L1 caches remain at 64 KB and private to each core. The L3 is engineered for future expansion.

- Dual channel memory is now *unganged* or two independent channels. This should improve concurrency in memory accesses and improve the chances of hitting in an already open DRAM bank.

- Full 128-bit-wide floating point unit (4 flops/cycle).

- This makes it even more important to use full-width SSE2 instructions as opposed to the "upper/lower" half varieties if data alignment is known. In other words, instructions such as mulpd, addpd, movapd, etc. are preferable to ones such as mulsd, addsd, movhpd, movlpd, etc. That is, aligned data and vectorizable code become even more beneficial.

- Similarly, if the upper portion of a 128-bit XMM register does not matter, it is better to use movsd and movss to load scalar values into the lower portions of the XMM register instead of movlpd or movlps.

- For unaligned data, it may be better to use movupd or movdqu for loads and movhpd or movlpd for stores.

- Two 128 bit loads from L1D per cycles (versus current  $2 \times 64$  bit loads per cycle).

- Support for 48 bits of physical address (256 TB). Current Opteron<sup>™</sup> processors support 40 bits of physical address.

- A new hardware prefetch buffer in the memory controller that can track positive, negative, and non-unit strides. It will not speculatively fill the L3, L2, or L1 caches, but instead prefetches into dedicated prefetch buffers in the memory controller.

- A new data cache prefetcher that is adaptive and detects positive or negative non-unit stride patterns (e.g., non-adjacent cachelines) and adapts the prefetch distance based on prefetching success. Further, the prefetched data now gets brought into the L1 rather than the L2.

- Prefetchw software prefetch instruction is now implemented separate from prefetch (prefetchw denotes intent to modify and provides a hint to set the cacheline state according to the MOESI protocol appropriately).

## **General Source Code Level Optimizations**

While many optimizing compilers will detect and perform the following optimizations on their own, programming style can aid the compiler in detecting a potential optimization or knowing it is safe. A few ideas along these lines are:

- Declare functions that are not used outside the file in which they are declared as "static" functions. This will force internal linkage and may aid in function inlining versus the default external linkage.

- If it is not permissible to allow expression reordering (particularly floating point) by the compiler throughout the entire scope of a compilation unit, it may be useful to explicitly express parallelism in sections of code where the programmer knows reordering (e.g., reassociation) to be safe. An example of this would be a loop that computes a number of partial sums from different segments of an array rather than a single summation that is calculated by summing the array from start to end in order.

- Explicit calculation of common subexpressions and storing the value in a local variable may be useful in code where the compiler fails to detect the opportunity to compute a partial result and reuse it across loop iterations. A good example of this is a stencil operation in a 3D grid data structure where the nine elements at locations [i+1, j+/-1, k+/-1] become the nine elements at locations [i, j+/-1, k+/-1] in the next loop iteration (when i = i+1). In such cases, explicit calculation and copying of a partial result between temporary variables can help the compiler generate better code.

- Many compilers will pad arrays and structures to improve the alignment of their elements, but if the compiler is unable or fails to do so, the programmer might try doing so explicitly in the declaration of those data structures. In general, declaring elements of C structs in order from largest to smallest is best.

- The same rule of thumb applies to local variable declarations in functions. Declaration in order from largest to smallest usually improves the chances of favorable alignment and layout in memory.

- For parallel applications, avoid having separate data items fall into the same 64 byte cacheline since this can create a false sharing condition that causes the cacheline to thrash between the unshared caches of each core. Explicit padding by the programmer or flags to provide hints to the compiler are possible ways to alleviate this.

- Avoid repeatedly dereferencing pointers in a function. Particularly for C code where the compiler may not know at compile time whether different pointers will alias (point to) the same address at runtime, this can result in many more loads and stores than desired. Frequently compilers will provide flags to tell the compiler it is safe to assume no such

aliasing exists. Barring that, or just to make it more explicit, a programmer might consider dereferencing the pointer once at the start of the function, placing a working copy into a local variable, and copying it back at the end of the function.

## Methodology for Gathering Performance Data

Except where otherwise noted, we analyzed benchmark performance on a dual-core Cray XT3<sup>™</sup> system (Jaguar at ORNL) and a prototype Cray XT4<sup>™</sup> system using data collected from the AMD Opteron<sup>™</sup> hardware performance counters. CrayPAT<sup>™</sup> was used to instrument the benchmark codes to gather runtime performance statistics for our evaluation. The following section describes how to use CrayPAT<sup>™</sup> and the basic methodology used to gather these statistics.

## Using CrayPAT™ to Gather Runtime Statistics

The Cray Performance Analysis Tools (CrayPAT<sup>™</sup>) were used to record the hardware efficiency of the application benchmarks. These tools are provided on all Cray XT3s<sup>™</sup> and provide a simple interface to hardware counter and other instrumentation data. Users are able to load the CrayPAT<sup>™</sup> environment model, rebuild their code, instrument the executable with the pat\_build command, and receive reports from their application runs. CrayPAT<sup>™</sup> captures performance data without the need for source code modifications. Event tracing was used to gather data during these experiments. Tracing records events at function entry and exit points, rather than interrupting execution periodically to capture events. Event tracing is added to an executable by the pat\_build command, provided that the craypat module was loaded when the source was compiled. Loading the craypat module for compilation is necessary to ensure that the needed debugging headers remain in the object files. Because CrayPAT<sup>™</sup> is able to leverage hardware-level performance counters, by means of the Performance API (PAPI) library, only minimal overhead is added to the user's application.

Because application tracing can produce enormous amounts of data, CrayPAT<sup>™</sup> uses runtime summarization by default. Rather than storing the data for each function on each process, CrayPAT<sup>™</sup> instead stores the data in aggregate. Summarization also ignores function parameter and return values, as well as stack information. While all of this information is valuable, especially when debugging program performance, it is unnecessary for the purposes of this report. The aggregate hardware counter data provides a representative look at memory and cache performance across the entire application execution.

The Opteron<sup>™</sup> processor architecture has four 48-bit hardware event counters, each of which can be used to monitor a variety of different events. For this reason, CrayPAT<sup>™</sup> defines nine sets of commonly used hardware counters, which are grouped by function. Two groups of hardware counters (groups 1 and 2) were used in these experiments to understand the cache and memory performance. The first group records total floating point operations, L1 data cache accesses, L1 data cache misses, and TLB misses. The second group records L1 and L2 data cache accesses, cache refills from L2 cache, and cache refills from system memory. Because MPI use can negatively influence each of the recorded metrics, the executables were instrumented in such a way that MPI functions were removed from the metrics. The results cited in Table 2, therefore, only include user code.

| PAT_HWPC_EVENT_SET 1: (FP, LS, L1 misses, & TLB misses) |                                                                       |  |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| PAPI_FP_OPS                                             | Floating point operations                                             |  |  |  |  |  |

| PAPI_L1_DCA                                             | Accesses to level 1 data cache                                        |  |  |  |  |  |

| DC_MISS                                                 | Total level 1 data cache misses                                       |  |  |  |  |  |

| PAPI_TLB_DM Translation lookaside buffer misses         |                                                                       |  |  |  |  |  |

| PAT_HWPC_EVENT_SET 2: (L                                | _1 & L2 data accesses & misses)                                       |  |  |  |  |  |

| PAPI_L1_DCA                                             | Accesses to level 1 data cache                                        |  |  |  |  |  |

| DC_L2_REFILL_MOESI                                      | Total data cache refills from level 2 cache to level 1 cache.         |  |  |  |  |  |

| DC_SYS_REFILL_MOESI                                     | Total data cache refills from system memory/level 2 data cache misses |  |  |  |  |  |

| BU_L2_REQ_DC                                            | Accesses to level 2 data cache                                        |  |  |  |  |  |

Table 2. Explanation of hardware counter events.

### **Example Application Report**

As an example of how each program was analyzed, this section will show and interpret reports for a single application. As was already explained, each application was profiled so that user and MPI functions are considered separately. In the report, this creates three major data sessions: Totals for program, User, and MPI. As the names imply, the Totals section is the complete data from the program execution, User includes only user functions, and MPI includes only MPI functions. Within the User and MPI sections, there is a breakdown of the most pertinent functions from each group. Below is an example of a program totals section for a report using hardware counters group 1.

```

Totals for program

_____

100.0%

Time%

100.0%

Cum.Time%

100.0%

Time

6732.607664

Calls

162397731109

PAPI_TLB_DM

659.911M/sec

4441480049284 misses

PAPI_L1_DCA

86841.249M/sec

584478099205200 ops

PAPI_FP_OPS

14501.875M/sec

97603713650150 ops

DC_MISS

1193.517M/sec

8032871839125 ops

User time

6730.420 secs

17499092506162 cycles

Time%

100.0%

Utilization rate

HW FP Ops / Cycles

5.58 ops/cycle

HW FP Ops / User time 14501.875M/sec 97603713650150 ops 4.4%peak

HW FP Ops / WCT 14497.163M/sec

Computation intensity

0.17 ops/ref

LD & ST per TLB miss

LD & ST per Dl miss

Dl cache hit ratio

LD & ST per Dl miss

LD & ST per Dl miss

LD & ST per Dl miss

Dl cache hit ratio

ST per Dl miss

Dl cache hit ratio

ST per Dl miss

Dl cache hit ratio

ST per Dl miss

ST p

98.6%

D1 cache hit ratio

% TLB misses / cycle

0.4%

```

Each report section shows how much time was spent in that section and the percentage of total execution time. For the Totals section, this is obviously 100% of the execution time. Below these metrics is the total number of function calls. The next four metrics are the hardware counters included in counter group 1, PAPI\_TLB\_DM (translation look-aside buffer misses), PAPI\_L1\_DCA (L1 cache accesses), PAPI\_FP\_OPS (floating point operations), and DC\_MISS (data cache misses), and their counter values. It is important to remember that these values are the aggregate from every MPI task and not from a single CPU. The next item is another measure of execution time,

this one derived from the hardware performance counters. Below that are several useful metrics derived from the counter data. For example, HW FP Ops / User time is the common megaflop count for the program, in this case 14.5 GF or about 4.4% of the peak performance. The remaining derived metrics will be explained shortly. Below is a USER section from a report for hardware counter group 2.

| USER                   |                                                                |

|------------------------|----------------------------------------------------------------|

|                        | 100.0%                                                         |

| Cum.Time%              | 100.0%                                                         |

| Time                   | 6724.668036                                                    |

|                        | 162396953744                                                   |

| PAPI L1 DCA 8689       | 0.056M/sec 584116763286676 ops                                 |

| DC L2 REFILL MOESI     | 1191.189M/sec 8007744664830 ops                                |

| DC SYS REFILL MOESI    | 155.048M/sec 1042309740361 ops                                 |

| BU_L2_REQ_DC 125       | 6.872M/sec 8449296500998 req                                   |

| User time 6722.        | 6.872M/sec 8449296500998 req<br>481 secs 17478450934102 cycles |

| Utilization rate       |                                                                |

| L1 Data cache misses   | 1346.237M/sec 9050054405191 misses                             |

|                        | 64.54 ops/miss                                                 |

| D1 cache hit ratio     | 98.5%<br>560.41 ops/miss                                       |

| LD & ST per D2 miss    | 560.41 ops/miss                                                |

| D2 cache hit ratio     | 87.7%                                                          |

| L2 cache hit ratio     |                                                                |

| Memory to D1 refill    | 155.048M/sec 1042309740361 lines                               |

| Memory to D1 bandwidth | 9463.401MB/sec 66707823383104 bytes                            |

| L2 to Dcache bandwidth | 72704.398MB/sec 512495658549120 bytes                          |

The example above is similar to the previous one, except it only includes data from user functions. This report is especially useful when MPI functions are considered separately, as they were in this example. Notice that for this report the specific hardware counters have changed. They are now PAPI\_L1\_DCA (L1 data cache accesses), DC\_L2\_REFILL\_MOESI (L1 refills from L2 cache), DC\_SYS\_REFILL\_MOESI (L2 refills from system memory), and BU\_L2\_REQ\_DC (L2 data cache requests). This will, of course, change the derived metrics.

These two different reports include several important metrics derived from the raw hardware counter data. The *computational intensity* metric shows how many operations are executed for every memory reference. If this number is large, then a lot of computation is done for every trip to memory, but if it is small, then the program is not reusing the items it fetches from memory. In the Totals report above, the computation intensity is 0.17, which means that for all the time spent fetching from memory, only one-fifth of that time is being used for calculations. It is desirable to have a computational intensity above 1, and the larger, the better. The LD & ST per TLB miss and LD & ST per D1 miss are similar metrics, showing the number of load and store operations per TLB and L1 data cache misses. As with the computation intensity metric, larger numbers are better.

The next two metrics to focus on are the D1 cache hit ratio and % TLB miss/cycle. The D1 cache hit ratio shows how many memory references were found in cache. The hit ratio is affected by cache-line reuse and prefetching, so it can and should be a high percentage. It is impossible to have 100% of all data references hit cache, but a well-written code should be able to achieve a cache hit ratio very near 100%. This metric can usually be improved over the most naïve implementation by using techniques described below. The opposite is true for the

percentage of TLB misses per cycle. Because TLB misses are an extremely expensive operation, it is important that the program have as few TLB misses as possible. This metric essentially shows the chance that any given operation results in an expensive TLB miss. It is critical to program performance to keep this metric below 1%. The Users example contains several more load/store operations per miss and miss ratio metrics, which should be interpreted as already explained, and also cache and memory bandwidth measures.

## Application Performance on AMD Multicore Processors

The first step in understanding and mitigating multicore bottlenecks is determining whether we actually have a problem to start with! In this section, we examine the impact of memory bandwidth contention on the performance of application kernels (represented by the NAS Parallel Benchmarks run in serial mode) and full applications. Not all applications suffer equally from the move to dual core. Next, we use STREAM and APEX-MAP microbenchmarks to show that memory bandwidth contention is the primary source of performance loss when moving from single- to dual-core systems. The conclusion is that many applications are not limited by memory bandwidth and that remedies for memory bandwidth contention will be beneficial only for those codes that are provably dependent on memory bandwidth.

## **NERSC-5 SSP Applications**

NERSC uses the SSP (Sustained System Performance) performance metric to assess the performance of HPC systems. The SSP uses a set of applications derived from the NERSC workload to predict the effective *sustained* performance delivered to real scientific workloads rather than focusing on the *peak* performance that is reflected in the LINPACK benchmark. In this section, we look at the effect of dual-core processors on the processing efficiency of the NERSC SSP applications.

The medium NERSC-5 application benchmarks were profiled on dual-core XT3<sup>™</sup> and XT4<sup>™</sup> hardware using CrayPAT<sup>™</sup>, as described in the previous sections. Since we are only interested in single-node performance for this report, the results exclude the performance characteristics of the MPI sections. All applications except CAM were run on 64 processors, with CAM running on 54. The applications were run in both serial and virtual node mode (single and dual core) and also using small and large pages.

Before discussing the applications in detail, we note that the hardware performance counter data collected does not indicate a clear source of the dual core penalty in regards to the cache and TLB subsystems. That is, the operations per TLB or cache miss are virtually unchanged on going to dual core in every case. The counter data does have a predictive value, in that applications with good ratios show little performance decrease on going to dual core. This is only to be expected given the discussion in previous sections, and our conclusion is that if each core is using less of a shared resource such as memory bandwidth, less contention can occur.

Regarding the merits of using small or large pages, however, the hardware performance counter data is conclusive. In general, runs utilizing large pages show an increased number of TLB misses and decreased performance on both single and dual core. Again, this is clearly explained from our understanding of the hardware.

#### MILC

The benchmark code MILC represents part of a set of codes written by the MIMD Lattice Computation (MILC) collaboration to study quantum chromodynamics (QCD), the theory of the strong interactions of subatomic physics. Strong interactions are responsible for binding quarks into protons and neutrons and holding them all together in the atomic nucleus. MILC performs simulations of four-dimensional SU(3) lattice gauge theory on MIMD parallel machines. The test case for the data shown here is for a lattice size of  $32^4$  with two trajectories of five steps each. MILC uses inlined SSE assembly code for some routines to aggressively perform software prefetching.

From the data in Table 3, we can see that small pages outperform large pages by a slight margin on both the XT3<sup>TM</sup> and XT4<sup>TM</sup>, due to a modest reduction in TLB misses. The dual core penalty is significant on both the XT3<sup>TM</sup> and XT4<sup>TM</sup>; MILC has the largest penalty of all the applications studied. Using small pages, MILC runs 44% and 43% slower on the dual-core XT3<sup>TM</sup> and XT4<sup>TM</sup> systems, respectively. From the TLB and cache miss ratios, we see very little spatial or temporal locality in the memory references generated by the MILC application. The ratios are uniformly low for both small and large pages. This is to be expected due to the type of scattered memory addressing that is performed in this application. Even so, the ratios seem at odds with the high computational intensity. Significant work has been done to include software prefetch instructions and SSE instructions in many of the kernels, and we conjecture that the effect of these optimizations may be skewing the composite hardware counter results.

|                          | Small       | Pages | Large Pages |       |  |

|--------------------------|-------------|-------|-------------|-------|--|

| XT3 <sup>™</sup>         | Single Dual |       | Single      | Dual  |  |

| Wall Clock Time          | 160         | 230   | 166         | 232   |  |

| Sustained MFLOPS         | 69370       | 48402 | 67138       | 47976 |  |

| Percent of Peak          | 21%         | 15%   | 20%         | 14%   |  |

| Computational Intensity  | 2.1         | 2.1   | 2.1         | 2.1   |  |

| References/TLB Miss      | 308         | 309   | 68          | 68    |  |

| References/D1 Cache Miss | 16          | 16    | 16          | 16    |  |

| References/D2 Cache Miss | 32          | 32    | 31          | 31    |  |

| XT4 <sup>™</sup>         |             |       |             |       |  |

| Wall Clock Time          | 127         | 181   | 130         | 184   |  |

| Sustained MFLOPS         | 87840       | 61482 | 85447       | 60538 |  |

| Percent of Peak          | 26%         | 18%   | 26%         | 18%   |  |

| Computational Intensity  | 2.1         | 2.1   | 2.1         | 2.1   |  |

| References/TLB Miss      | 307         | 308   | 106         | 106   |  |

| References/D1 Cache Miss | 16          | 16    | 16          | 16    |  |

| References/D2 Cache Miss | 33          | 33    | 33          | 33    |  |

# Table 3. MILC performance on single-core and dual-core AMD Opteron™ processors using small and large pages.

#### GTC

GTC is a three-dimensional code used to study microturbulence in magnetically confined toroidal fusion plasmas via the particle-in-cell (PIC) method. It solves the gyro-averaged Vlasov equation in real space using global gyrokinetic techniques and an electrostatic approximation. The Vlasov equation describes the evolution of a system of particles under the effects of self-consistent electromagnetic fields. The test case studied here is 10 particles per cell and 2000 time steps.

In Table 4, we can see that small pages outperform large pages by almost 40%. This is the largest effect observed over all the applications studied here. The change in TLB miss ratio on going to large pages explains the very large performance hit; the number of TLB misses increases by a factor of almost 300. From closer inspection of the GTC trace data, the three routines most significant in terms of time consumed all contain loop constructs that address more than eight arrays, causing thrashing of the TLB. The dual core penalty is small, amongst the lowest of all the applications, at 4% slower when run with small pages. From the cache miss ratio, we see a reasonable amount of spatial or temporal locality in the memory references generated by the GTC application.

|                          | Small  | Pages | Large Pages |       |  |

|--------------------------|--------|-------|-------------|-------|--|

| XT3 <sup>™</sup>         | Single | Dual  | Single      | Dual  |  |

| Wall Clock Time          | 614    | 639   | 851         | 879   |  |

| Sustained MFLOPS         | 71219  | 68557 | 51584       | 49920 |  |

| Percent of Peak          | 21%    | 21%   | 16%         | 15%   |  |

| Computational Intensity  | 1.17   | 1.17  | 1.17        | 1.16  |  |

| References/TLB Miss      | 4858   | 4853  | 21          | 21    |  |

| References/D1 Cache Miss | 44     | 43    | 44          | 44    |  |

| References/D2 Cache Miss | 355    | 355   | 206         | 206   |  |

Table 4. GTC performance on single-core and dual-core AMD Opteron™ processors using small and large pages.

### PARATEC

The benchmark code PARATEC (PARAllel Total Energy Code) performs *ab initio* quantummechanical total energy calculations using pseudopotentials and a plane wave basis set. Total energy minimization of electrons is done with a self-consistent field (SCF) method. Force calculations are also done to relax the atoms into equilibrium positions. PARATEC uses an allband (unconstrained) conjugate gradient (CG) approach to solve the Kohn-Sham equations of density functional theory (DFT) and obtain the ground-state electron wavefunctions. In solving the Kohn-Sham equations using a plane wave basis, part of the calculation is carried out in Fourier space, where the wavefunction for each electron is represented by a sphere of points, and the remainder is in real space. Specialized parallel three-dimensional FFTs are used to transform the wavefunctions between real and Fourier space, and a key optimization in PARATEC is to transform only the non-zero grid elements. The test case used as input to collect data is bulk silicon with a unit cell containing 125 atoms, running a single SCF calculation. Data in Table 5 shows the performance of PARATEC on the XT3<sup>TM</sup> and XT4<sup>TM</sup>. Interestingly, on the XT3<sup>TM</sup>, small pages lead to marginally better performance, but the situation is reversed on the XT4<sup>TM</sup>. This is because the ratio of TLB misses running with small and large pages changes quite significantly (more than a factor of 4) according to the architecture. The major source of this change is improved large page TLB performance on the XT4<sup>TM</sup>. Given that the processor is identical on both these platforms, we assume that the performance difference is due to a newly installed version of the compiler and ACML library. The dual core penalty is small for both architectures, at 5% slower with small pages. The TLB and L2 cache miss ratios are good for both large and small pages, but the L1 cache miss ratio falls to around the average across all the applications.

|                          | Small  | Pages  | Large  | Pages  |

|--------------------------|--------|--------|--------|--------|

| XT3 <sup>™</sup>         | Single | Dual   | Single | Dual   |

| Wall Clock Time          | 593    | 622    | 598    | 630    |

| Sustained MFLOPS         | 221864 | 211696 | 220223 | 208938 |

| Percent of Peak          | 66.8   | 63.6   | 66.2   | 62.8   |

| Computational Intensity  | 1.51   | 1.51   | 1.51   | 1.51   |

| References/TLB Miss      | 6659   | 6670   | 1325   | 1309   |

| References/D1 Cache Miss | 61     | 61     | 61     | 61     |

| References/D2 Cache Miss | 1133   | 1129   | 1226   | 1222   |

| XT4 <sup>™</sup>         |        |        |        |        |

| Wall Clock Time          | 549    | 572    | 548    | 570    |

| Sustained MFLOPS         | 239915 | 230774 | 240621 | 231337 |

| Percent of Peak          | 72%    | 69%    | 72%    | 70%    |

| Computational Intensity  | 1.48   | 1.48   | 1.48   | 1.48   |

| References/TLB Miss      | 6749   | 6736   | 5643   | 5473   |

| References/D1 Cache Miss | 105    | 105    | 105    | 105    |

| References/D2 Cache Miss | 1139   | 1151   | 1241   | 1247   |

Table 5. PARATEC performance on single core and dual core AMD Opteron™ processors using small and large pages.

### CAM

The Community Atmosphere Model (CAM) is the atmospheric component of the Community Climate System Model (CCSM) developed at NCAR and elsewhere for the weather and climate research communities. Although generally used in production as part of a coupled system in CCSM, CAM can be run as a standalone (uncoupled) model as it is here. The NERSC benchmark runs CAM version 3.1 at D resolution (about 0.5 degree) using a finite volume dynamical core.

From the data shown in Table 6, we can see that small pages outperform large pages by a slight margin on the XT3<sup>TM</sup>, although on the XT4<sup>TM</sup> the difference in performance is almost nonexistent. As with PARATEC, the ratio of TLB misses running with small and large pages changes significantly (more than a factor of 2) according to the architecture. In this case, however, the change is due to both a performance improvement of large page TLB miss rate and

the decrease in small page TLB miss rate on the XT4<sup>™</sup>. Again, we believe the origin of this change is the upgraded compiler. The dual core penalty is significant, the second largest of all the applications, at 12% slower with small pages on the XT3<sup>™</sup>. However, this penalty drops to 10% on the XT4<sup>™</sup>. The TLB and cache miss ratios fall into the middle of the range when comparing all the applications.

|                          | Small  | Pages | Large Pages |       |  |

|--------------------------|--------|-------|-------------|-------|--|

| XT3 <sup>™</sup>         | Single | Dual  | Single      | Dual  |  |

| Wall Clock Time          | 1733   | 1937  | 1806        | 2002  |  |

| Sustained MFLOPS         | 30574  | 27357 | 29334       | 26464 |  |

| Percent of Peak          | 10.5   | 9.4   | 10.1        | 9.1   |  |

| Computational Intensity  | 0.56   | 0.56  | 0.55        | 0.55  |  |

| References/TLB Miss      | 2847   | 2851  | 172         | 183   |  |

| References/D1 Cache Miss | 33     | 33    | 33          | 33    |  |

| References/D2 Cache Miss | 518    | 513   | 545         | 536   |  |

| XT4 <sup>™</sup>         |        |       |             |       |  |

| Wall Clock Time          | 1216   | 1335  | 1215        | 1339  |  |

| Sustained MFLOPS         | 43584  | 39691 | 43599       | 39573 |  |

| Percent of Peak          | 13%    | 12%   | 13%         | 12%   |  |

| Computational Intensity  | 0.89   | 0.89  | 0.89        | 0.89  |  |

| References/TLB Miss      | 1913   | 1910  | 314         | 317   |  |

| References/D1 Cache Miss | 22     | 22    | 22          | 22    |  |

| References/D2 Cache Miss | 335    | 330   | 354         | 349   |  |

Table 6. CAM performance on single core and dual core AMD Opteron<sup>™</sup> processors using small and large pages.

### MADbench

The benchmark code MADbench is a stripped-down version of MADCAP (Microwave Anisotropy Dataset Computational Analysis Package). This package contains several computational tools developed for analysis of data from cosmic microwave background (CMB) experiments. The goal of these experiments is to extract the wealth of cosmology information embedded in the CMB that is related to the universe at an age of about 400,000 years after the Big Bang. Such experiments typically involve scanning a significant amount of the sky for long periods at very high resolution. The reduction of the resulting datasets, first to a pixelized sky map and then to an angular power spectrum, is extremely computationally intensive. The primary computational challenge is an out-of-core solution to a dense linear algebra problem on distributed matrices. The test case used here is 18,000 pixels with 24 bins operating in single gang mode.

The performance of MADBench is summarized in Table 7. For this application only, on the  $XT3^{TM}$ , running with large pages slightly outperforms running with small pages. Virtually identical performance between large and small page runs is observed on the  $XT4^{TM}$ . The dual core penalty is one of the smallest, at 3% slower with large pages on the  $XT3^{TM}$  and 2% slower on the  $XT4^{TM}$ . TLB and cache miss ratios are the best of all the applications on both  $XT3^{TM}$  and

XT4<sup>™</sup>, probably due to the main computational work being matrix-matrix multiplication, which is carried out via an optimized ACML<sup>™</sup> routine. Interestingly, TLB misses are vastly improved for large pages on the XT4<sup>™</sup>. This data point is the only occasion where the ratio of operations per TLB miss is better running with large pages than with small pages.

|                          | Small  | Pages  | Large Pages |        |  |

|--------------------------|--------|--------|-------------|--------|--|

| XT3 <sup>™</sup>         | Single | Dual   | Single      | Dual   |  |

| Wall Clock Time          | 1318   | 1336   | 1248        | 1291   |  |

| Sustained MFLOPS         | 219981 | 216986 | 232294      | 224640 |  |

| Percent of Peak          | 66%    | 65%    | 70%         | 68%    |  |

| Computational Intensity  | 1.73   | 1.7    | 1.72        | 1.72   |  |

| References/TLB Miss      | 7807   | 7880   | 3281        | 3265   |  |

| References/D1 Cache Miss | 122    | 124    | 121         | 121    |  |

| References/D2 Cache Miss | 2481   | 2348   | 2922        | 2880   |  |

| XT4 <sup>™</sup>         |        |        |             |        |  |

| Wall Clock Time          | 1248   | 1272   | 1236        | 1263   |  |

| Sustained MFLOPS         | 230868 | 226415 | 233129      | 228185 |  |

| Percent of Peak          | 69%    | 68%    | 70%         | 69%    |  |

| Computational Intensity  | 1.67   | 1.67   | 1.67        | 1.67   |  |

| References/TLB Miss      | 7911   | 7918   | 12521       | 12721  |  |

| References/D1 Cache Miss | 122    | 122    | 121         | 122    |  |

| References/D2 Cache Miss | 2407   | 2399   | 2989        | 2968   |  |

#### Table 7. MADBench performance on single core and dual core AMD Opteron™ processors using small and large pages.

### **GAMESS**

The benchmark code GAMESS (General Atomic and Molecular Electronic Structure System) performs various *ab initio* quantum chemistry simulations. Several kinds of SCF wavefunctions can be computed with correlation. Correlation corrections to these SCF wavefunctions include configuration interaction, second order perturbation theory, and coupled-cluster approaches, as well as the density functional theory approximation. A variety of molecular properties, ranging from simple dipole moments to frequency-dependent hyperpolarizabilities may be computed. Many basis sets are stored internally, together with effective core potentials, so all elements up to radon may be included in molecules. The two benchmarks used here test DFT energy and gradient, RHF energy, MP2 energy, and MP2 gradient.

From the data in Table 8, we can see that small pages outperform large pages by about 10%. The dual core penalty is minimal, one of the smallest of all the applications at 2% slower with small pages on the  $XT3^{TM}$ . The TLB and cache miss ratios are about average when compared across all the applications studied, except the TLB miss ratio for the small pages runs which is relatively small.

|                          | Small  | Pages | Large Pages |       |  |

|--------------------------|--------|-------|-------------|-------|--|

| XT3 <sup>™</sup>         | Single | Dual  | Single      | Dual  |  |

| Wall Clock Time          | 6573   | 6732  | 7087        | 7334  |  |

| Sustained MFLOPS         | 14976  | 14643 | 14310       | 13645 |  |

| Percent of Peak          | 5%     | 4%    | 4%          | 4%    |  |

| Computational Intensity  | 0.17   | 0.17  | 0.17        | 0.17  |  |

| References/TLB Miss      | 131    | 131   | 109         | 109   |  |

| References/D1 Cache Miss | 72     | 73    | 73          | 73    |  |

| References/D2 Cache Miss | 561    | 561   | 566         | 566   |  |

Table 8. GAMESS performance on single core and dual core AMD Opteron™ processors using small and large pages.

#### Analysis of NERSC-5 SSP

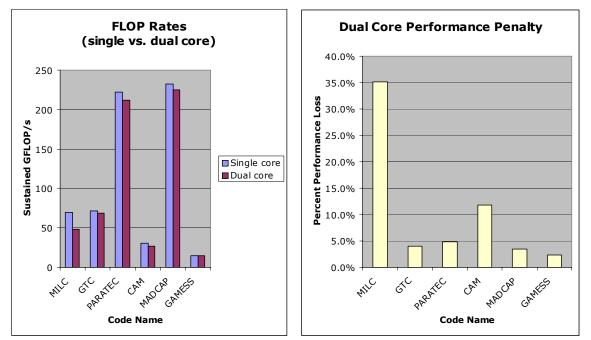

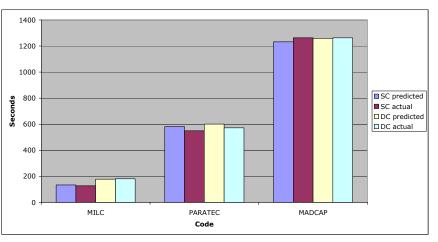

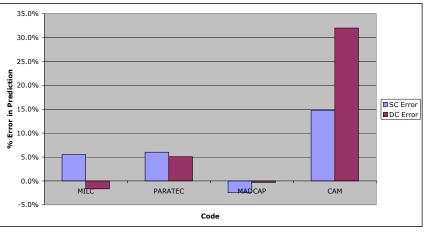

Figure 2 shows the impact of moving from single-core to dual-core processors on application performance. Overall, the majority of N5 SSP applications suffered very little from the move to dual-core processors. On average, the performance penalty of moving from single- to dual-core processors was on the order of 10%. This indicates that memory bandwidth is unlikely to be the bottleneck for application performance. MILC suffered the worst effects from the move to dual-core processors. In that case, the dominant portion of the MILC kernel is hand-coded in assembly, so it makes optimal use of memory bandwidth. It is interesting to point out that, except for MILC, the difference in performance between using large pages vs. small pages was actually greater than the performance impact of moving to dual cores. The importance of TLB page size was examined in detail in the discussion of the Opteron<sup>™</sup> architecture above.

Figure 2. NERSC SSP Performance on single-core vs. dual-core AMD Opteron™ processor. Except for MADCAP, small-page performance results were used. The average performance penalty for moving from single to dual core was 10.3%.

### **NAS Parallel Benchmarks**

Several of the NAS Parallel Benchmarks—CG, MG, SP, LU, and BT—were run in serial mode on the dual core for examining a worst case scenario comparison of packed and unpacked execution. The addressing characteristics of the kernels are as follows:

- BT: 5 x 5, stride

- SP: 5 x 5, stride

- LU: 5 x 5, stride

- MG: Contiguous

- CG: Indirect

#### Methodology

The latest 3.x.x version of the serial versions of the NAS benchmarks were built for the Class B problem size using -03 and -fastsse options using the Portland Group (PGI) compilers. Each applet/kernel is executed in a serial fashion, from a top level MPI wrapper with two MPI ranks. In order to run in this fashion, the code had to be slightly modified to facilitate our study. The modification is summarily:

```

<main program declarations>

mask=0

read(10,*)cpuflag

if (cpuflag.eq.1)mask(0)=1

if (cpuflag.eq.2)mask(1)=1

if (cpuflag.eq.3)mask(0)=1

if (cpuflag.eq.3)mask(1)=1

if (mask(my_mpi_rank).eq.1)then

<original serial code>

endif

call MPI_Barrier(MPI_COMM_WORLD, ierr)

call MPI_Finalize(ierr)

<original program end>

```

Each of the applications was executed on one dual core socket with two MPI ranks for values of cpuflag of 1, 2, and 3, yielding performance data for execution on core 0 and core 1 separately (single core runs) and core 0 and 1 simultaneously (dual core runs). Runs were also performed replacing the final barrier operation with an mpi\_abort while parking the non-executing core in a tight loop. No timing discrepancy was found between these two methods, indicating negligible effect from idle tasks parked in the barrier operation.

The data presented was generated on a Cray internal machine, "Seal," running Catamount v1.5.x using both 4 KB page size (small pages) and 2 MB pages (large pages) selected via the yod command. Seal is a Cray XT4<sup>™</sup> platform with the following node attributes:

- Sockets: 1

- **Processor:** AMD Opteron<sup>™</sup> 1218 (Rev F)

- Frequency: 2.6 GHz, peak floating point performance of 5.2 Gflops

- Memory: 667MHz DDR2, peak bandwidth of 10 GB/s (8 GB/s STREAM)

We note in contrast to the NERSC-5 SSP application tests, these NAS benchmarks are configured so that the tasks do not communicate with one another. This enables us to isolate our performance study to scalar performance without consideration of message-passing performance.

Execution times for the applications obtained are given in Table 9. In the table, single core runs are provided for each of the two cores independently, while dual core run timings are shown for each core from the same run.

|    | Single Core Runs |        |             |        | Dual Core Runs |        |             |        | Aver   | ages   |        |        |

|----|------------------|--------|-------------|--------|----------------|--------|-------------|--------|--------|--------|--------|--------|

|    | Large Pages      |        | Small Pages |        | Large Pages    |        | Small Pages |        | Large  | Pages  | Small  | Pages  |

|    | core 1           | core 2 | core 1      | core 2 | core 1         | core 2 | core 1      | core 2 | S/core | D/core | S/core | D/core |

| BT | 431.5            | 431.5  | 406.0       | 405.9  | 472.2          | 472.2  | 454.9       | 454.9  | 431.5  | 472.2  | 405.9  | 454.9  |

| SP | 359.6            | 359.5  | 327.8       | 327.9  | 468.3          | 468.3  | 456.9       | 456.9  | 359.5  | 468.3  | 327.9  | 456.9  |

| LU | 536.1            | 536.0  | 539.9       | 539.9  | 738.1          | 738.1  | 743.8       | 743.8  | 536.1  | 738.1  | 539.9  | 743.8  |

| CG | 189.3            | 189.2  | 188.2       | 188.1  | 208.7          | 208.7  | 206.8       | 206.8  | 189.3  | 208.7  | 188.2  | 206.8  |

| MG | 16.0             | 16.0   | 16.2        | 16.2   | 23.5           | 23.5   | 23.5        | 23.5   | 16.0   | 23.5   | 16.2   | 23.5   |

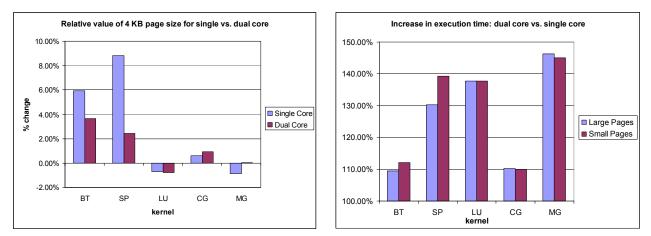

We compare the execution performance of the NAS benchmarks on single and dual-core processors. The effect of enabling small pages on both dual and single core execution of the kernels is shown in Table 10.

|    | Decrease<br>from Enabling | e in Time<br>g Small Pages | Time Increase<br>for Dual Core |             |  |

|----|---------------------------|----------------------------|--------------------------------|-------------|--|

|    | Single Core               | Dual Core                  | Large Pages                    | Small Pages |  |

| BT | 5.92%                     | 3.66%                      | 109.42%                        | 112.05%     |  |

| SP | 8.82%                     | 2.44%                      | 130.24%                        | 139.35%     |  |

| LU | -0.71%                    | -0.77%                     | 137.69%                        | 137.77%     |  |

| CG | 0.59%                     | 0.91%                      | 110.29%                        | 109.93%     |  |

| MG | -0.84%                    | 0.04%                      | 146.35%                        | 145.07%     |  |

Table 10. Performance penalties for using dual core for both small and large pages.

#### Analysis of NAS Benchmarks

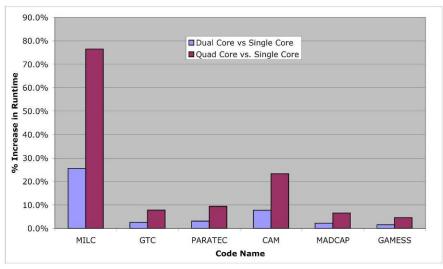

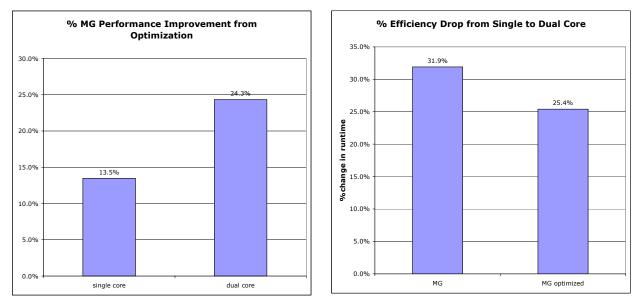

We see a range of effects from dual core execution ranging from 10% to 45%, with MG exhibiting the greatest effect and CG least (Figure 3). Of interest is that the enablement of small page sizes in execution has an apparently different effect on overall execution time of a given application depending upon whether it was executed in single or dual core mode. Applets exhibiting most sensitivity remain so in this regard. The trend appears to suggest that the effect of small pages is less pronounced when dual core mode is employed. The average degradation in execution time is approximately 27%, which is more significant than the typical performance drop on the NERSC-5 SSP applications. Notably, all NAS kernels exhibit greater overall flop rate in dual core mode.

Figure 3. NAS benchmark performance. The figures show the change in NAS kernel performance as a result of the move from single to dual core for both small pages and large pages.

### **Microbenchmarks and Probes**

While application benchmarks provide the most direct evidence of the effective performance that a given system architecture will deliver for a code, they also tend to be too complicated to infer the source of bottlenecks that result in performance differentiation. Microbenchmarks and probes are much simpler proxies that enable a more detailed study of specific architectural bottlenecks and behaviors that would otherwise be hopelessly intertwined when observed in a full-fledged application code. We will focus primarily on a handful of microbenchmarks that analyze the performance of the memory hierarchy with varying degrees of complexity and scope—STREAM, Membench, and Apex-MAP.

#### **STREAM**

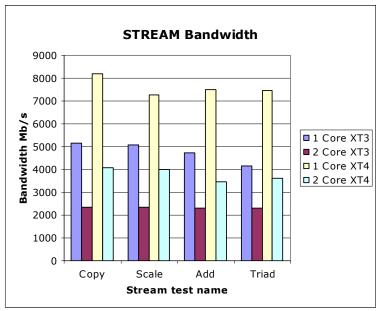

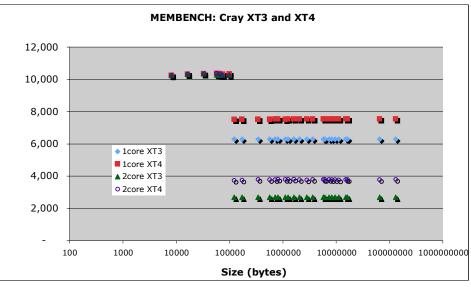

The STREAM benchmark is used to assess the effective bandwidth delivered by the memory subsystem. Table 11 and Figure 4 show STREAM performance on the Cray XT3<sup>™</sup> and Cray XT4<sup>™</sup> systems. The stream results used an array size of 53,687,091 elements, offset of 0 and a total memory requirement of 1228 MB (well outside of the L2 cache). The primary source of contention is the memory interface, which is shared between the two cores on chip.

|       | One Core XT3 <sup>™</sup> | One Core XT4 <sup>™</sup> | Two Core XT3 <sup>™</sup> | Two Core XT4 <sup>™</sup> |

|-------|---------------------------|---------------------------|---------------------------|---------------------------|

| Сору  | 5137                      | 8196                      | 2345                      | 4074                      |

| Scale | 5067                      | 7257                      | 2348                      | 4012                      |

| Add   | 4734                      | 7482                      | 2309                      | 3469                      |

| Triad | 4135                      | 7464                      | 2310                      | 3626                      |

Table 11. Observed memory bandwidth (Mb per second per core) for Cray XT3<sup>™</sup> and XT4<sup>™</sup> from STREAM benchmark.

Figure 4. Graphical depiction of STREAM performance.

#### Membench

The Membench test performs a STREAM-like copy operation to examine memory bandwidth limited performance, but sweeps over a range of buffer sizes. The benchmark was run on both the XT3<sup>™</sup> and XT4<sup>™</sup> systems. The XT3<sup>™</sup> uses the same performance processor cores as the XT4<sup>™</sup>, but contains slower DDR1 memory, whereas the XT4<sup>™</sup> uses DDR2 memory interfaces, which offer a much higher bandwidth.

Figure 5. Membench results for XT3™ and XT4™.

We can see clearly from Figure 5 that when the benchmark fits within the L2 cache, the Opteron<sup>™</sup> processors (both Rev-E on XT3<sup>™</sup> and Rev-F on XT4<sup>™</sup>) maintain constant

performance at 10+ GB/s due to the independent L2 caches. However, once the processors must go to main memory, the effective memory bandwidth per core is cut in half. For the XT3<sup>TM</sup>, Membench goes from 6 GB/s sustained per core to 2.8 GB/s sustained per core. For the XT4<sup>TM</sup>, the performance drops from 7.5 GB/s for single core down to 3.9 GB/s per core when running on both cores.

This makes it clear that the primary source of bandwidth contention for the AMD processors is bandwidth on the memory interface. Otherwise, the independent L2 caches ensure that both cores can operate without interfering with one another for independent cache-resident data.

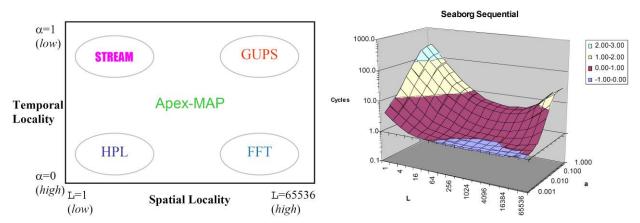

#### Apex-MAP

Apex-MAP (Memory Access Probe) is a synthetic benchmark that was designed to trace out a richer variety of application memory access patterns than benchmarks such as STREAM, Membench, or Cachebench are capable of producing. Whereas STREAM and Membench only deal with unit-stride memory access patterns, Apex-MAP (as shown in Figure 6) provides access patterns that vary in both temporal locality (the  $\alpha$  parameter) and spatial locality (the L parameter). The  $\alpha$  parameter is expressed as an exponent to a power distribution for the memory addresses that varies from 0 to 1, where 0 represents a high degree of spatial locality in the memory accesses and 1 represents a uniform random access that spans memory space. The L parameter simply refers to the length of the contiguous data access, which varies from 1 to 64 K words of memory. These two parameters can be varied continuously to trace out a 2D map of memory subsystem performance for a broad range of memory access patterns. More details can be found in the SC2005 paper describing Apex-MAP's capabilities (http://crd.lbl.gov/DOEresources/SC05/ApexMap\_EStrohmaier.pdf).

Figure 6. Apex-MAP traces out a 2D space of memory access patterns characterized by their spatial and temporal locality. The spatial locality, L, describes the size of contiguous accesses to a given memory location. The temporal locality,  $\alpha$ , is an exponent for a power law distribution of memory accesses. The diagram on the left shows how the memory access patterns of various benchmarks correspond to the continuous 2D space traced out by Apex-MAP. The diagram on the right shows a typical Apex-MAP plot of the performance of a Power3 microprocessor on the NERSC-3/Seaborg system. The performance (vertical direction) is given in terms of cycles per memory access.

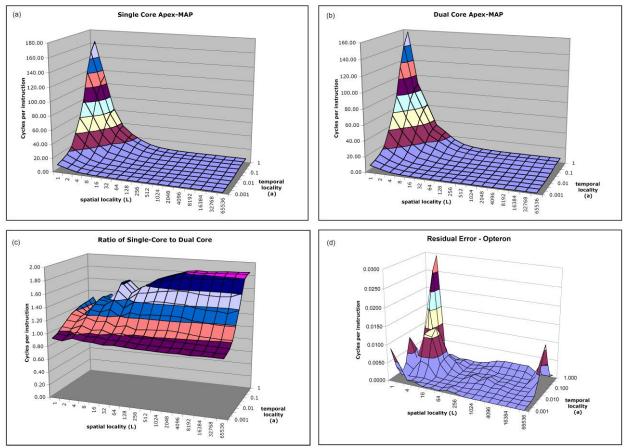

The serial version of Apex-MAP was run on the ORNL Jaguar system, which has dual-core 2.6 GHz Rev-E Opteron<sup>™</sup> processors. A single copy of Apex-MAP was run on each node for the

unpacked (single-core) case, and two copies of serial Apex-MAP were run for the packed (dual-core) case.

Figure 7. Apex-MAP results for AMD Opteron<sup>™</sup> processors on XT3<sup>™</sup>.

Figures 7a and 7b show the Opteron<sup>™</sup> processors' response to the different memory access patterns presented by Apex-MAP. Figure 7c shows the difference between the single-core and dual-core performance. It points out quite clearly that the dual-core processor performance is cut nearly exactly in half when the two cores have an access pattern that is primarily bandwidth bound. However, when the memory access pattern causes performance to be bounded by latency, there is very little performance penalty for running with both cores. So the degree to which code performance suffers from moving from single core to multi-core is dependent on how much of the code is in fact bandwidth bound. As we will see from the application results, it is not clear that many codes are indeed in the bandwidth bound regime.

Erich Strohmaier created a simple linear model for the response of the memory subsystem based only on the bandwidth and latencies to memory and to the L2 cache. In Figure 7d, we see the residual error between the performance predicted by this simple model and the actual Apex-MAP performance. We can see across the entire parameter space, the very simple model correctly predicts the memory response except in the case with the lowest spatial and temporal locality. The error is likely due to the fact that the model does not account for branch mispredicts, TLB misses, and much lower memory efficiency for the random accesses across the entire memory space. What this means is that the predicted dual-core performance across a wide range of memory access patterns is correctly accounted for using the simplest possible model for memory performance—namely, that the effective latency of the memory subsystem and bandwidth + latency for the L2 cache remains the same regardless of how many cores are used, but the main memory bandwidth is cut in half. This result assures us that there are unlikely to be additional sources of contention in the processor design aside from the memory bandwidth contention.

## **Extrapolating to Quad-Core Performance**

We observe from the AMD architectural discussion that when excluding messaging performance, the primary source of contention when moving from single core to dual core is memory bandwidth. The testing with STREAM and Membench microbenchmarks confirms this assumption, as the performance of the 2.6 GHz AMD cores only becomes differentiated when the data sizes become larger than the L2 cache and must go to main memory. Finally, the analysis with Apex-MAP shows that a simple performance model that presumes only that memory bandwidth is cut in half when processors access main memory is highly accurate in predicting dual-core performance for a wide variety of memory access patterns. Therefore, investigation of more complex models for dual-core performance is unlikely to yield higher-fidelity results.

With these conclusions in mind, we go back to the task of extrapolating the performance of the NERSC benchmarks on quad-core systems. We begin by enumerating the assumptions of our model:

- 1. The only source of performance difference between single- and dual-core runs is memory bandwidth contention.

- 2. The 2.6 GHz RevE and RevF AMD cores execute code at roughly the same performance in the absence of memory bandwidth contention.

- 3. We can therefore break execution time into the portion that is stalled on shared resources (memory bandwidth) and the portion that is stalled on non-shared resources (everything else).

- 4. Under this circumstance, we can use the timing difference from single- to dual-core runs to compute the fraction of execution time spent in memory bandwidth contention.

- 5. We can then extrapolate the quad-core performance by assuming the time spent in the execution component remains the same, but the time spent in memory bandwidth contention will increase proportional to the reduction in effective memory bandwidth per core.

We began by testing the above assumption using the XT3<sup>™</sup> performance data to predict the effective performance on the XT4<sup>™</sup>. The XT4<sup>™</sup> in this test operates at the same clock frequency as the XT3<sup>™</sup>, but the DDR2-667 memory subsystem is 30% faster than the DDR1-400 MHz memory of the XT4<sup>™</sup>. Starting with the MILC data:

- The execution time for single-core runs on the XT3<sup>™</sup> is 160 seconds, and the time spent in dual-core is 230 seconds.

- The STREAM benchmarks indicate that the memory bandwidth for dual core is approximately half that of the single core, so if the five assumptions above hold true, we should expect execution time to obey the relationship:

- single core: core\_exec\_time + bandwidth\_contention\_time = 160 s

- $\circ$  dual core: core\_exec\_time + 2\*bandwidth\_contention\_time = 230 s