### UNIVERSITY OF CALIFORNIA

Los Angeles

Layout Synthesis for Quantum Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Bochen Tan

### ABSTRACT OF THE DISSERTATION

Layout Synthesis for Quantum Computing

by

#### Bochen Tan

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2024 Professor Jingsheng Jason Cong, Chair

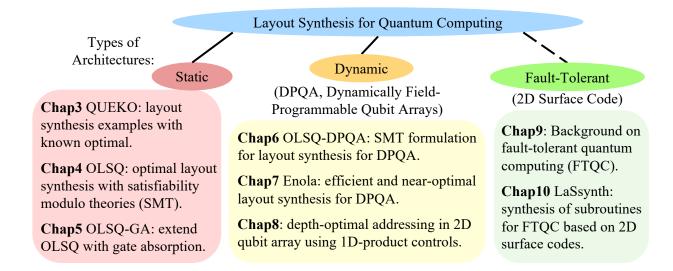

Quantum computers are expected to surpass conventional computers in tasks like integer factoring and quantum system simulation. In quantum programming, entangling operations between qubits are crucial. However, the program qubits are mapped to physical qubits within a quantum computing architecture that often features restricted connectivity, meaning that entangling operations can only be applied between specific pairs of qubits. As a result, it is essential to determine the map from program qubits to physical qubits throughout the computation. Additionally, it may be necessary to introduce new operations to ensure the quantum program conforms to the connectivity constraints. This challenge is known as layout synthesis for quantum computing. In this dissertation, we explore layout synthesis for quantum architectures, focusing on static architectures primarily based on superconducting circuits, as well as dynamic architectures based on neutral atoms. Given that fault tolerance is required for large-scale quantum computing, we also investigate program synthesis for a promising fault-tolerant quantum architecture based on surface codes.

The dissertation of Bochen Tan is approved.

Miryung Kim

Jens Palsberg

Chee Wei Wong

Jingsheng Jason Cong, Committee Chair

University of California, Los Angeles 2024

To my family

# TABLE OF CONTENTS

| 1 | Intr | oducti | ion                                                                    | 1  |

|---|------|--------|------------------------------------------------------------------------|----|

|   | 1.1  | Conce  | epts in Gate-Based Quantum Computing                                   | 1  |

|   |      | 1.1.1  | Quantum States                                                         | 2  |

|   |      | 1.1.2  | Quantum Gates                                                          | 4  |

|   |      | 1.1.3  | Quantum Circuits                                                       | 8  |

|   | 1.2  | Status | s of Quantum Computing Hardware                                        | 13 |

|   |      | 1.2.1  | Superconducting Circuits                                               | 15 |

|   |      | 1.2.2  | Trapped Ions                                                           | 18 |

|   |      | 1.2.3  | Neutral Atoms                                                          | 19 |

|   | 1.3  | Layou  | t Synthesis for Static Quantum Architectures                           | 19 |

|   |      | 1.3.1  | Problem Statement                                                      | 22 |

|   |      | 1.3.2  | NP-Hardness Results                                                    | 25 |

|   |      | 1.3.3  | Previous Work                                                          | 27 |

|   | 1.4  | The C  | Challenge of Layout Synthesis for Dynamic Quantum Architectures        | 30 |

|   | 1.5  | The C  | Challenge of Layout Synthesis for Fault-Tolerant Quantum Architectures | 32 |

| 2 | Ove  | erview |                                                                        | 37 |

|   | 2.1  | The M  | Ieasure-Improve Process in Layout Synthesis for Static Quantum Archi-  |    |

|   |      | tectur | es                                                                     | 38 |

|   |      | 2.1.1  | Measuring Optimality with QUEKO                                        | 40 |

|   |      | 2.1.2  | Closing the Optimality Gap with OLSQ                                   | 41 |

|   |      | 2.1.3  | Exploring Larger Solution Space with OLSQ-GA                           | 42 |

|              | 2.2           |        | Quantum Architectures                                                 | 42 |

|--------------|---------------|--------|-----------------------------------------------------------------------|----|

|              |               | 2.2.1  | Axiomatic Formulation of the Dynamically Field-Programmable Qubit     |    |

|              |               | 2.2.1  | Arrays Architecture and its Layout Synthesis with OLSQ-DPQA           | 44 |

|              |               | 2.2.2  | Refined Formulation Enabling Efficient and Near-Optimal Layout Syn-   |    |

|              |               |        | thesis for Dynamically Field-Programmable Qubit Arrays with Enola     | 47 |

|              |               | 2.2.3  | Formulation of Addressing 2D Qubit Arrays with 1D-Product Controls    | 48 |

|              | 2.3           | Synthe | esis of Subroutines for Surface-Code Fault-Tolerant Quantum Architec- |    |

|              |               | tures  | with LaSsynth                                                         | 48 |

| 3            | $\mathbf{QU}$ | EKO: ( | Optimality Benchmarks for Layout Synthesis for Static Quantum         |    |

| $\mathbf{A}$ | •             |        | 3                                                                     | 50 |

|              | 3.1           | QUEK   | O Benchmarks Construction                                             | 50 |

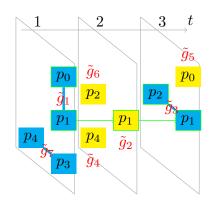

|              |               | 3.1.1  | Backbone Construction Phase                                           | 51 |

|              |               | 3.1.2  | Sprinkling Phase                                                      | 55 |

|              |               | 3.1.3  | Scrambling Phase                                                      | 55 |

|              |               | 3.1.4  | Output                                                                | 56 |

|              | 3.2           | Optim  | ality Study with QUEKO                                                | 56 |

|              |               | 3.2.1  | Experimental Setup                                                    | 56 |

|              |               | 3.2.2  | Experimental Results                                                  | 61 |

| 4            | OLS           | SQ: Op | otimal Layout Synthesis for Static Quantum Architectures              | 64 |

|              | 4.1           | Oppor  | tunities in Layout Synthesis Formulation                              | 67 |

|              | 4.2           | Our A  | pproach                                                               | 68 |

|              |               | 4.2.1  | Preprocessing                                                         | 69 |

|   |     | 4.2.2          | Encoding Variables                                        | 69         |

|---|-----|----------------|-----------------------------------------------------------|------------|

|   |     | 4.2.3          | Constraints                                               | 70         |

|   |     | 4.2.4          | Objectives                                                | 72         |

|   |     | 4.2.5          | Complexity Analysis                                       | 73         |

|   |     | 4.2.6          | Remark on the Optimality of OLSQ                          | 74         |

|   |     | 4.2.7          | TB-OLSQ: Rethinking Time Coordinates                      | 74         |

|   |     | 4.2.8          | QAOA-OLSQ: Removing False Dependencies                    | 76         |

|   | 4.3 | Evalua         | ation                                                     | 78         |

|   |     | 4.3.1          | OLSQ versus Previous Optimal Approaches                   | 79         |

|   |     | 4.3.2          | TB-OLSQ versus Heuristic Approaches                       | 85         |

|   |     | 4.3.3          | QAOA-OLSQ                                                 | 85         |

| 5 | OLS | SO-CA          | a: Optimal Layout Synthesis with SWAP Gate Absorption for |            |

|   |     |                | um Architectures                                          | 88         |

|   | 5.1 | "Free          | Lunch" for Layout Synthesis: SWAP Absorption              | 88         |

|   | 5.2 | Formu          | ulation of OLSQ-GA                                        | 92         |

|   |     | 5.2.1          | Variables                                                 | 92         |

|   |     | 5.2.2          | Constraints                                               | 93         |

|   | 5.3 | Evalua         | ation of OLSQ-GA                                          | 95         |

|   | 5.4 | Soluti         | on Space Reduction                                        | 99         |

|   |     | 5.4.1          | Analysis on Optimal Mapping Solutions                     | 99         |

|   |     |                |                                                           |            |

|   |     | 5.4.2          | Implementing Alternating Matchings Pattern                | 100        |

|   |     | 5.4.2<br>5.4.3 |                                                           | 100<br>102 |

| 6  | OLS   | Q-DPQA: Layout Synthesis for Dynamically Field-Programmable Qubit     |   |

|----|-------|-----------------------------------------------------------------------|---|

| Aı | rrays | Based on Satisfiability Modulo Theories                               | 4 |

|    | 6.1   | The DPQA Architecture                                                 | 4 |

|    |       | 6.1.1 Atom Trapping                                                   | 5 |

|    |       | 5.1.2 Array Movements                                                 | 5 |

|    |       | 5.1.3 Quantum Gates                                                   | 7 |

|    |       | 5.1.4 Error Source                                                    | 8 |

|    |       | 5.1.5 Atom Transfer                                                   | 8 |

|    |       | 5.1.6 Universality                                                    | 8 |

|    | 6.2   | Discretization of the Solution Space                                  | 9 |

|    | 6.3   | Optimal Compilation with SMT                                          | 2 |

|    |       | 3.3.1 Variables                                                       | 2 |

|    |       | 3.3.2 Constraints                                                     | 5 |

|    |       | 3.3.3 Software Implementation                                         | 1 |

|    |       | 6.3.4 Evaluation                                                      | 4 |

|    | 6.4   | Hybrid Approach                                                       | 6 |

|    | 6.5   | Handling Generic Quantum Circuits                                     | 2 |

| 7  | Eno   | a: Efficient and Near-Optimal Layout Synthesis for Dynamically Field- |   |

|    |       | nmable Qubit Arrays                                                   | 7 |

|    | 7.1   | Motivation: Fidelity Analysis                                         | 7 |

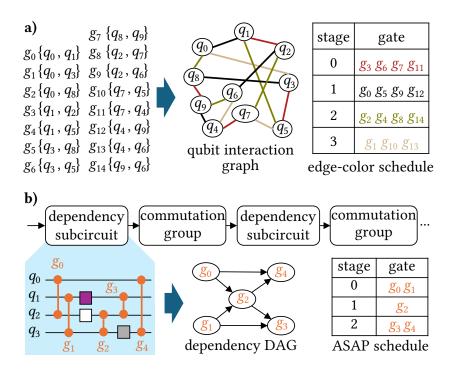

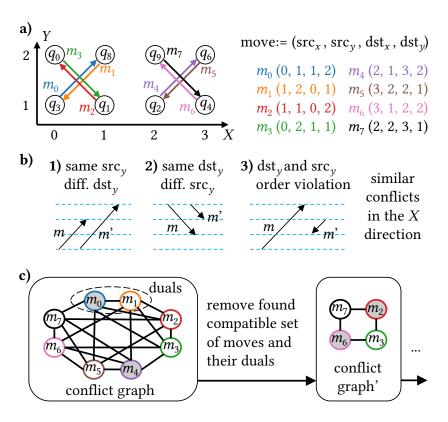

|    | 7.2   | Misra-Gries Algorithm for Edge Coloring                               |   |

|    | 7.3   | Scheduling: Edge Coloring                                             |   |

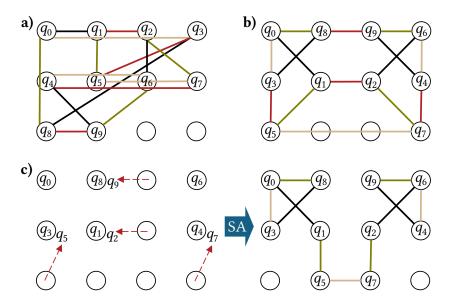

|    | 7.4   | Placement: Simulated Annealing                                        |   |

|    |       |                                                                       |   |

|   | 7.5  | Routin  | ng: Independent Set                                        | 148 |

|---|------|---------|------------------------------------------------------------|-----|

|   | 7.6  | Evalua  | ation                                                      | 151 |

|   |      | 7.6.1   | Impact of Different Settings in Enola                      | 151 |

|   |      | 7.6.2   | Quality Comparison with Previous Works                     | 152 |

|   |      | 7.6.3   | Runtime Scaling of Enola                                   | 156 |

| 8 | Qul  | oit Ado | dressing in Dynamically Field-Programmable Qubit Arrays    | 157 |

|   | 8.1  | Backg   | round                                                      | 158 |

|   | 8.2  | Algori  | thm                                                        | 161 |

|   |      | 8.2.1   | SMT Formulation                                            | 162 |

|   |      | 8.2.2   | Heuristics                                                 | 163 |

|   | 8.3  | Evalua  | ation                                                      | 166 |

|   |      | 8.3.1   | Benchmark Construction                                     | 166 |

|   |      | 8.3.2   | Results                                                    | 167 |

|   | 8.4  | EBMF    | F in the Context of Fault-Tolerant Quantum Computing       | 170 |

|   | 8.5  | NP-Ha   | ardness Result of the DPQA Routing Problem                 | 172 |

| 9 | Intr | oducti  | ion to Quantum Error Correction and Fault-Tolerant Quantum | n   |

| C | ompı | ıting   |                                                            | 174 |

|   | 9.1  | Mathe   | ematical Background                                        | 174 |

|   |      | 9.1.1   | Pauli Group                                                | 175 |

|   |      | 9.1.2   | Stabilizer Group                                           | 177 |

|   |      | 9.1.3   | Clifford Group                                             | 178 |

|   |      | 9.1.4   | ZX Calculus                                                | 180 |

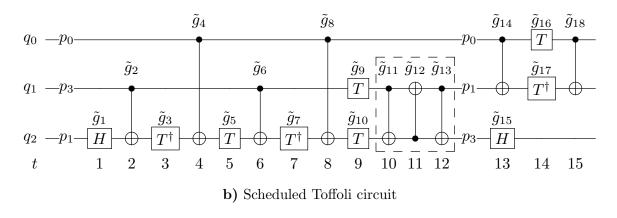

|   | 0.2  | Ouant   | um Error Correction with Surface Codes                     | 189 |

|        | 9.2.1    | Code Construction                                             | 182         |

|--------|----------|---------------------------------------------------------------|-------------|

|        | 9.2.2    | Decoding Errors                                               | 184         |

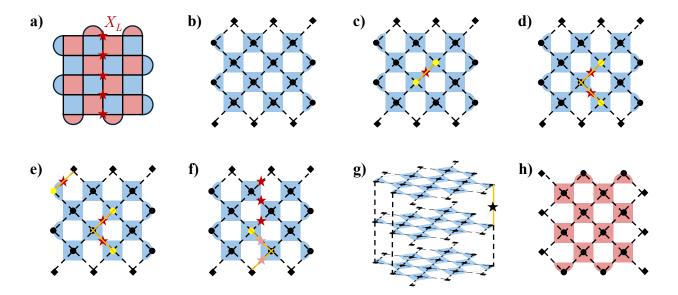

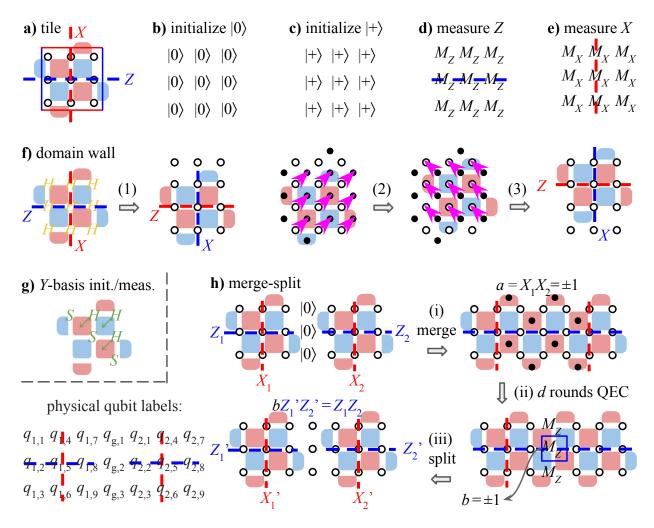

| 9.3    | Fault-   | Tolerant Quantum Computing with Surface Codes                 | 187         |

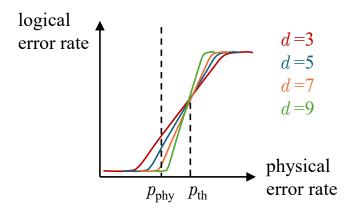

|        | 9.3.1    | Fault-Tolerant Operations                                     | 189         |

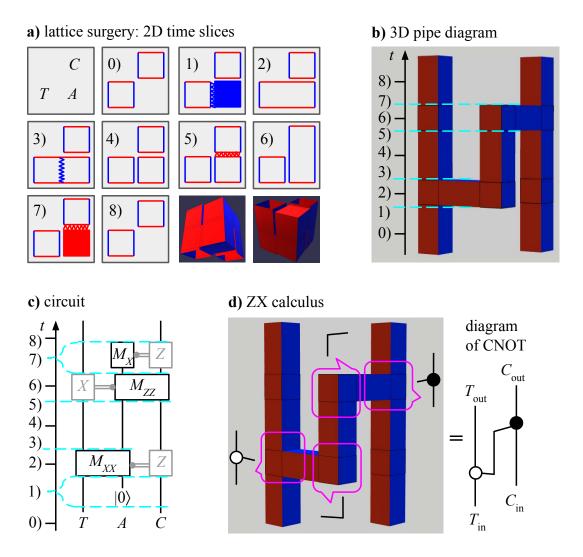

|        | 9.3.2    | Fault-Tolerant Logical Block                                  | 193         |

|        | 9.3.3    | Distillation Factory                                          | 200         |

| 10 Las | Ssynth:  | Representation and Synthesis of Subroutines for Fault-Toleran | .t          |

| Quant  | um Ar    | chitectures Based on Surface Codes                            | <b>20</b> 4 |

| 10.1   | Formu    | lation                                                        | 209         |

|        | 10.1.1   | Structural Variables                                          | 209         |

|        | 10.1.2   | Validity Constraints                                          | 212         |

|        | 10.1.3   | Correlation Surface Variables                                 | 214         |

|        | 10.1.4   | Functionality Constraints                                     | 215         |

| 10.2   | 2 Softwa | are Implementation                                            | 218         |

| 10.3   | 8 Evalua | ation                                                         | 221         |

|        | 10.3.1   | Methodology of Graph State Generation Evaluation              | 224         |

|        | 10.3.2   | Methodology of Majority Gate Evaluation                       | 225         |

|        | 10.3.3   | Methodology of T-Factory Evaluation                           | 225         |

|        | 10.3.4   | Observations on Runtime                                       | 227         |

| 10.4   | l Relate | d Works                                                       | 228         |

| 11 Co  | nclusio  | n and Outlook                                                 | 230         |

| Dofors | magg     |                                                               | 999         |

|        |          |                                                               |             |

## LIST OF FIGURES

| 1.1  | An example of unitary quantum program/circuit                          | 8  |

|------|------------------------------------------------------------------------|----|

| 1.2  | Examples of general circuits                                           | 11 |

| 1.3  | Scaling of the number of physical qubits in recent years               | 14 |

| 1.4  | Coupling graphs of some existing superconducting quantum architectures | 16 |

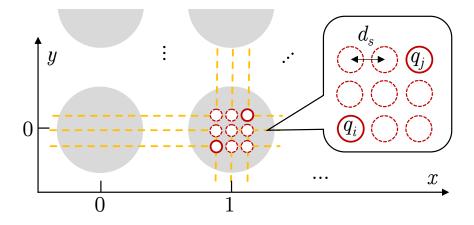

| 1.5  | The dynamically field-programmable qubit arrays (DPQA) architecture    | 20 |

| 1.6  | KAK decomposition                                                      | 21 |

| 1.7  | Toffoli circuit                                                        | 22 |

| 1.8  | Layout synthesis for the Toffoli circuit on a 5-qubit architecture     | 23 |

| 1.9  | A hypothetical dynamic architecture                                    | 31 |

| 1.10 | Layout synthesis for the hypothetical dynamic architecture             | 31 |

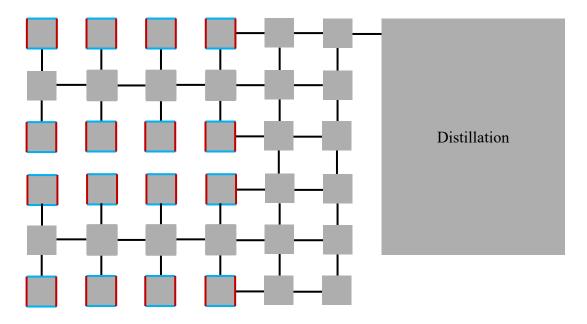

| 1.11 | Fault-tolerant quantum computing based on surface codes                | 34 |

| 2.1  | Roadmap of this dissertation                                           | 38 |

| 2.2  | The placement problem in classical circuit design                      | 39 |

| 2.3  | SWAP absorption                                                        | 42 |

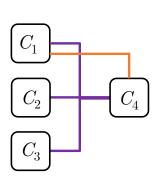

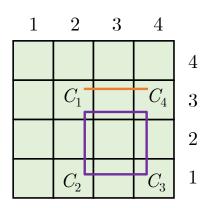

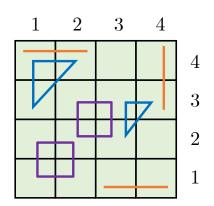

| 2.4  | Operations in dynamically field-programmable qubit arrays              | 45 |

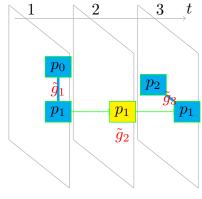

| 3.1  | QUEKO construction                                                     | 54 |

| 3.2  | Examples of coupling graphs for quantum architectures                  | 57 |

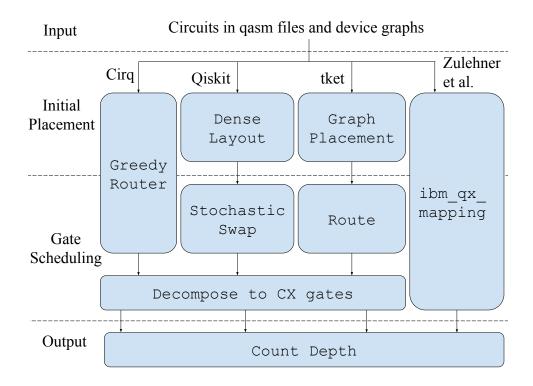

| 3.3  | Workflow of the optimality experiments using QUEKO                     | 59 |

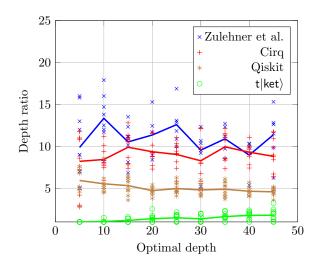

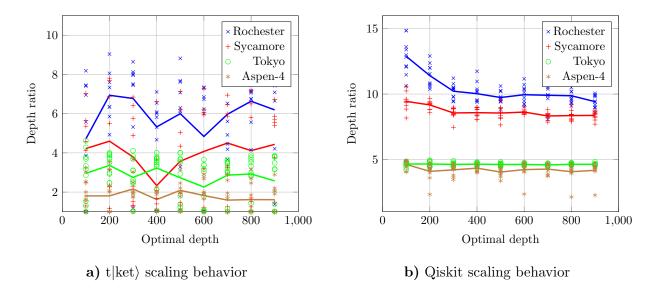

| 3.4  | Performance of layout synthesis tools on $B_{\rm NTF}$                 | 61 |

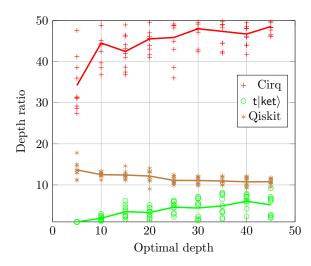

| 3.5  | $t ket\rangle$ and Qiskit performance on $B_{SS}$                      | 62 |

| 3.6  | $t ket\rangle$ and Qiskit performance on $B_{IGD}$                     | 63 |

| 4.1 | Circuit diagram for quantum adder                                                  | 65  |

|-----|------------------------------------------------------------------------------------|-----|

| 4.2 | Coupling graphs of some quantum architectures                                      | 65  |

| 4.3 | OLSQ layout synthesis result for the quantum adder circuit                         | 66  |

| 4.4 | Immediate dependencies in the quantum adder circuit                                | 67  |

| 4.5 | The quantum adder circuit in transition-based model                                | 75  |

| 4.6 | Sketch of the QAOA circuit                                                         | 77  |

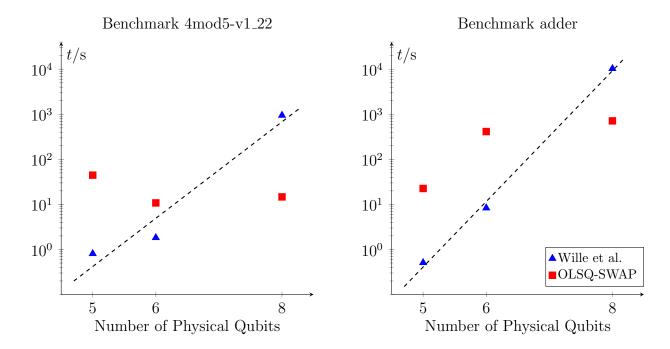

| 4.7 | Runtime scaling of Wille et al. [WBZ19] and OLSQ-SWAP                              | 80  |

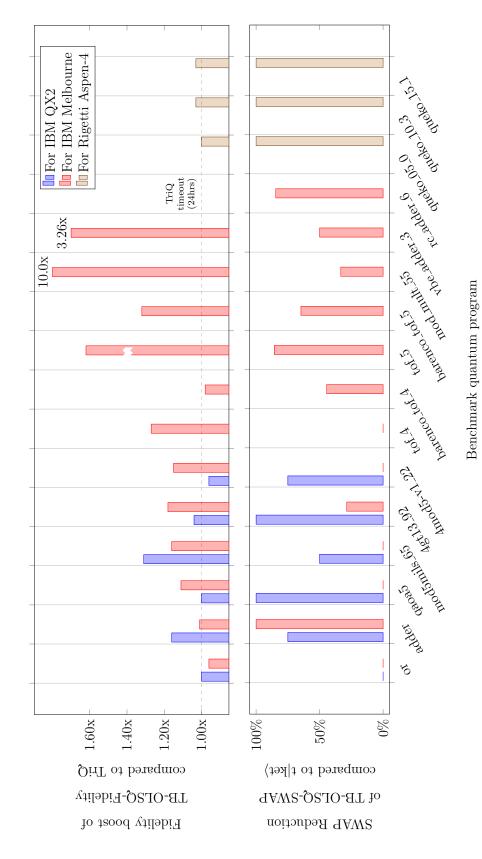

| 4.8 | Evaluation of TB-OLSQ, t ket> [SDC20], and TriQ [MLM19]                            | 82  |

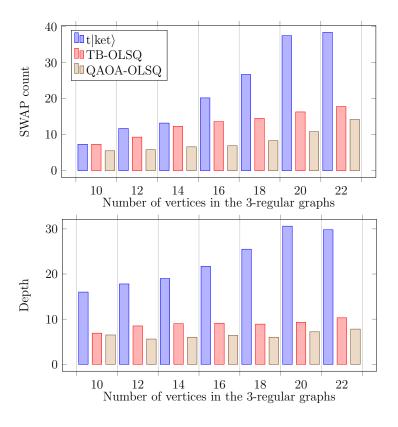

| 4.9 | Evaluation of QAOA-OLSQ and t ket> [SDC20]                                         | 86  |

| 5.1 | Example layout synthesis problem                                                   | 89  |

| 5.2 | Layout synthesis solutions of 5-qubit chemical simulation on a linear architecture | 90  |

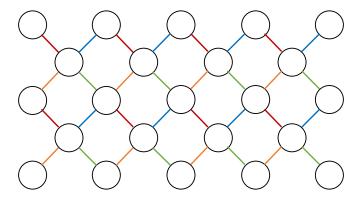

| 5.3 | Part of the Google Sycamore architecture                                           | 96  |

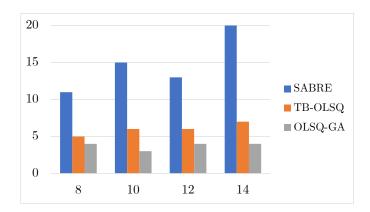

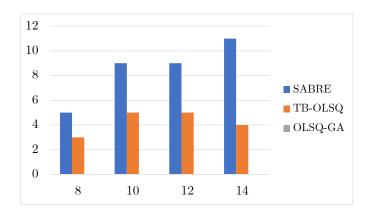

| 5.4 | Depth results by SABRE, TB-OLSQ, and OLSQ-GA                                       | 96  |

| 5.5 | SWAP count results by SABRE, TB-OLSQ, and OLSQ-GA                                  | 97  |

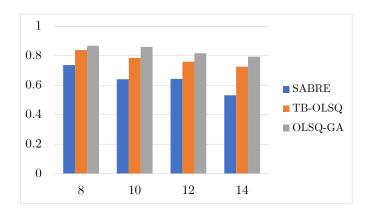

| 5.6 | Fidelity results by SABRE, TB-OLSQ, and OLSQ-GA                                    | 97  |

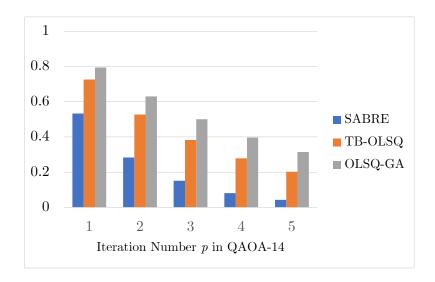

| 5.7 | Fidelity of multiple iterations of QAOA-14 by SABRE, TB-OLSQ, and OLSQ-GA          | 99  |

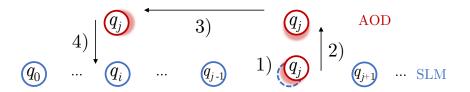

| 6.1 | Universal quantum computing on DPQA with one AOD trap and one SLM row              | 109 |

| 6.2 | Discretization of space into interaction sites                                     | 110 |

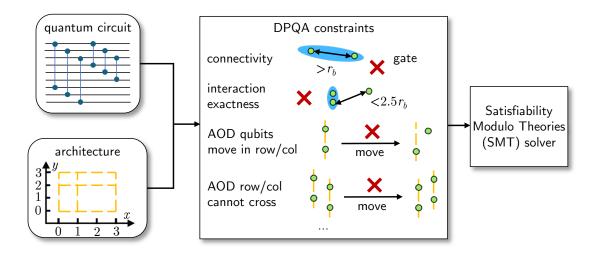

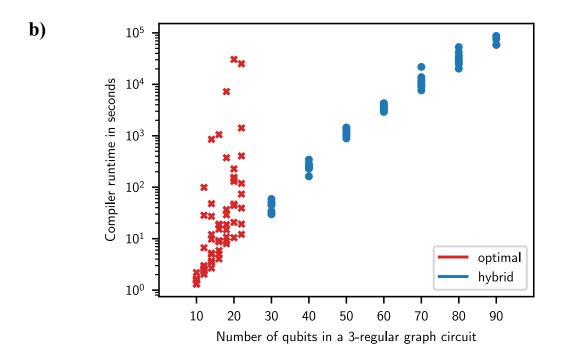

| 6.3 | Illustration of the OLSQ-DPQA approach                                             | 113 |

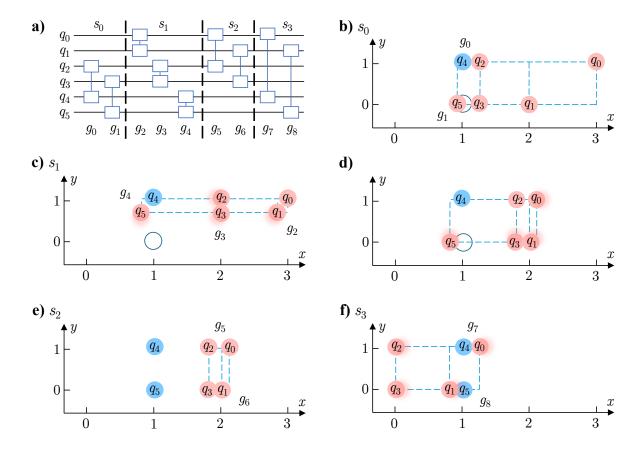

| 6.4 | A compiled program on DPQA                                                         | 116 |

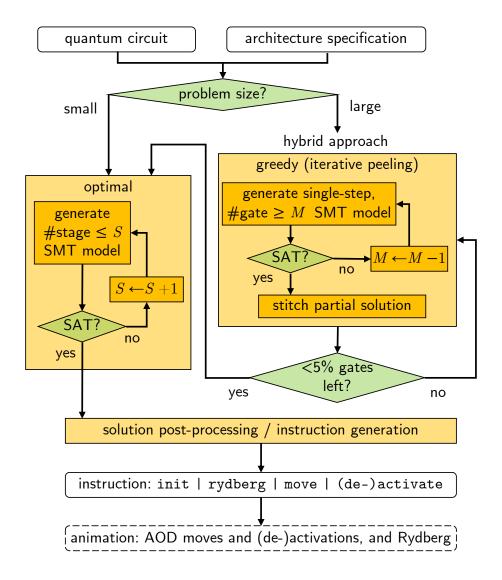

| 6.5 | Workflow of OLSQ-DPQA                                                              | 122 |

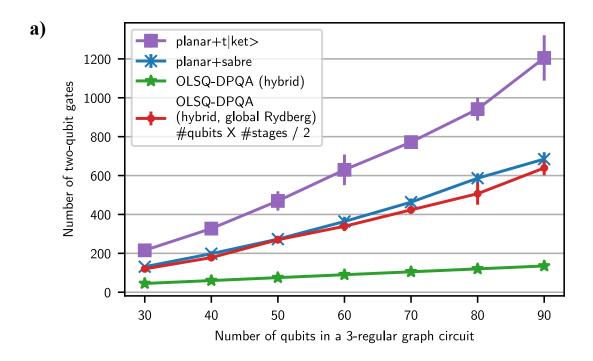

| 6.6 | Evaluation of the optimal layout synthesis in OLSO-DPOA                            | 126 |

| 0.7 | One of the largest benchmarks we are able to compile with the hybrid approach |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | in OLSQ-DPQA                                                                  | 128 |

| 6.8 | Evaluation of the greedy-optimal hybrid approach in OLSQ-DPQA                 | 130 |

| 6.9 | Handling generic circuits in OLSQ-DPQA                                        | 133 |

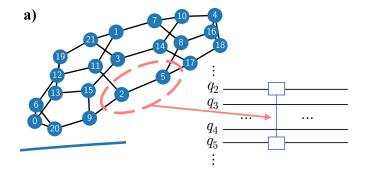

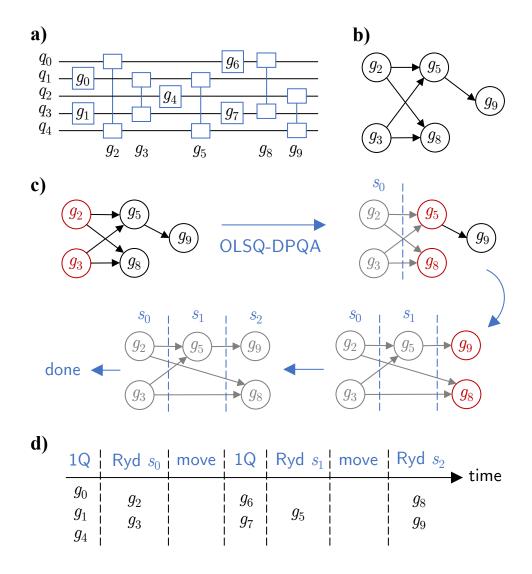

| 7.1 | OLSQ-DPQA and Enola error breakdown                                           | 138 |

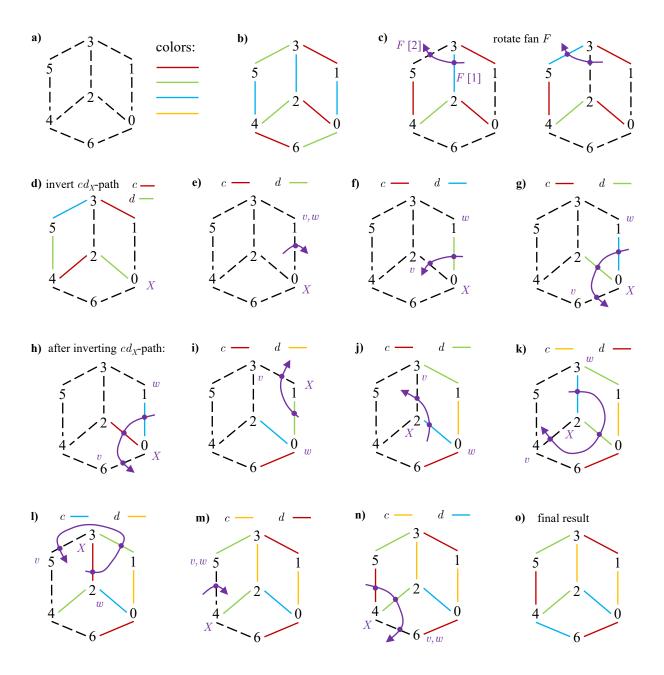

| 7.2 | Misra-Gries algorithm                                                         | 141 |

| 7.3 | Scheduling in Enola                                                           | 144 |

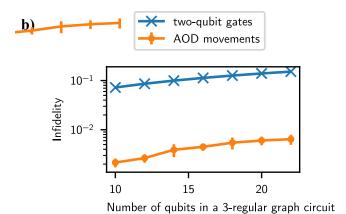

| 7.4 | Placement in Enola                                                            | 146 |

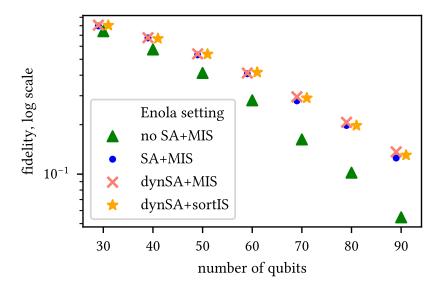

| 7.5 | Routing in Enola                                                              | 149 |

| 7.6 | Decoherence fidelity term of different settings in Enola on 3-regular MaxCut  |     |

|     | QAOA circuits                                                                 | 152 |

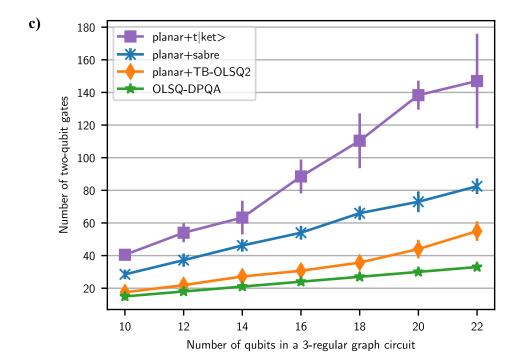

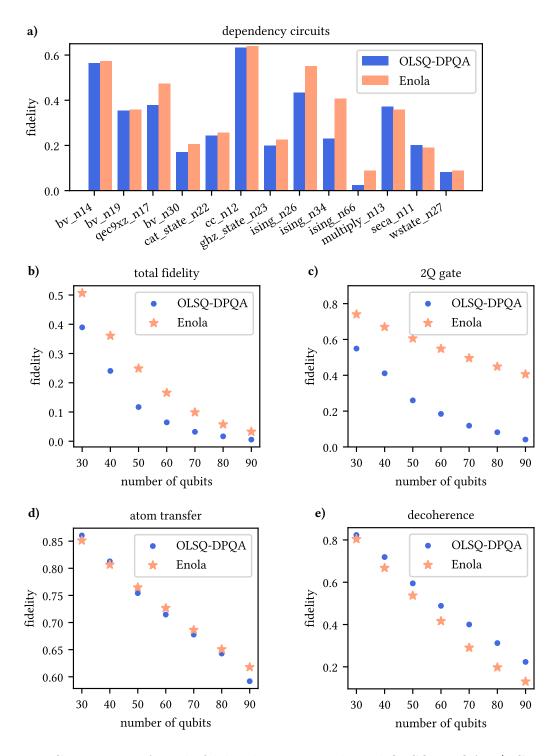

| 7.7 | Comparison of result fidelity between Enola and OLSQ-DPQA                     | 153 |

| 7.8 | Comparison of two-qubit gate fidelity term on 3-regular MaxCut QAOA circuits  |     |

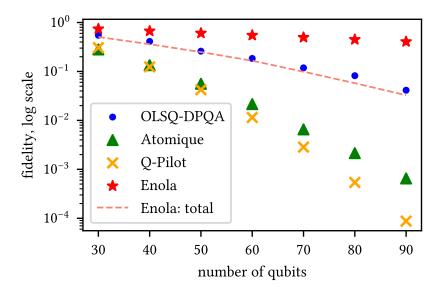

|     | between Enola, OLSQ-DPQA, Atomique, and Q-Pilot                               | 154 |

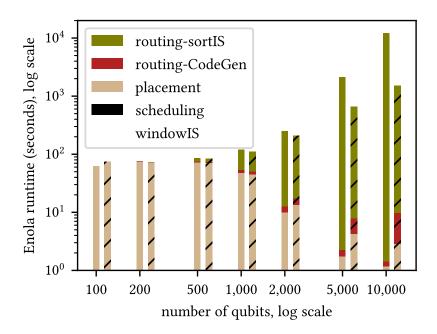

| 7.9 | Enola runtime scaling on 3-regular MaxCut QAOA circuits                       | 155 |

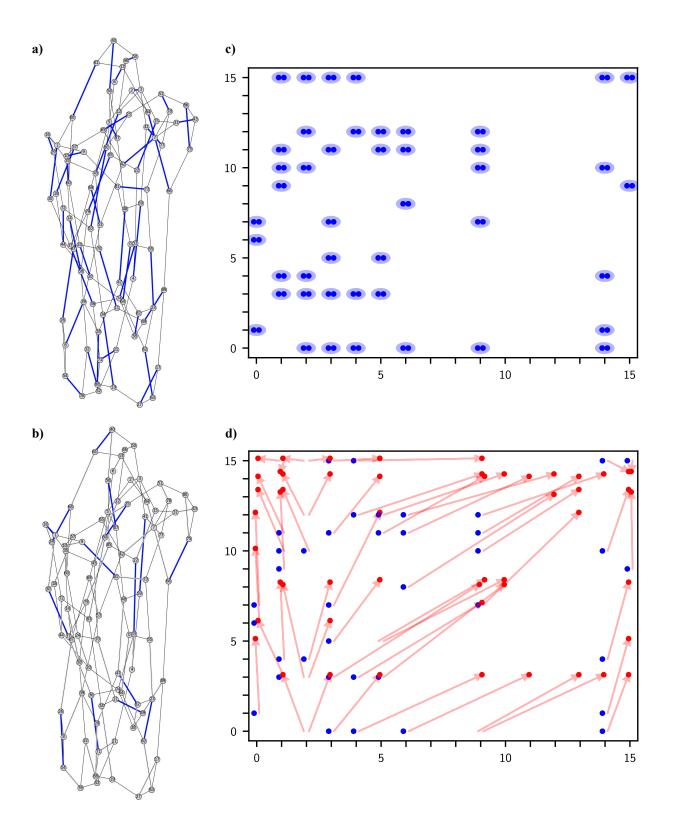

| 8.1 | Rectangular addressing in neutral atom arrays                                 | 158 |

| 8.2 | Problems equivalent to depth-optimal rectangular addressing                   | 160 |

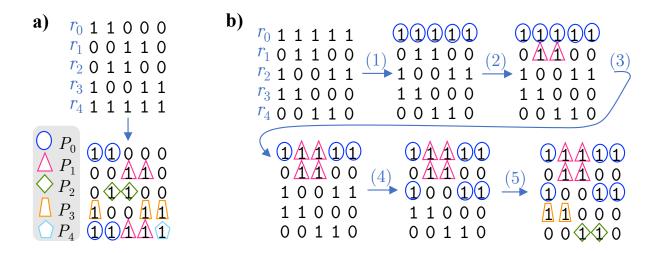

| 8.3 | Two trials of running the row packing heuristic                               | 165 |

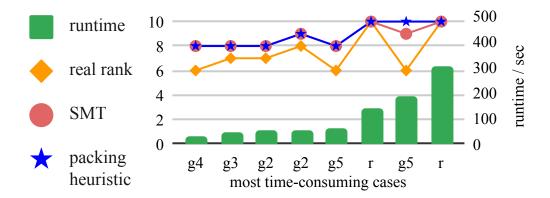

| 8.4 | The most time-consuming cases of exact binary matrix factorization in our ex- |     |

|     | periments                                                                     | 169 |

| 8.5 | Rectangular addressing in fault-tolerant quantum computing                    | 171 |

| 8.6 | NP-hardness of DPQA routing                                                   | 173 |

| 9.1 | Stabilizer flows of representative Clifford gates                             | 179 |

| 9.2   | ZX calculus                                                                                 | 180  |

|-------|---------------------------------------------------------------------------------------------|------|

| 9.3   | ZX derivation including measurements and feed-forward gates                                 | 181  |

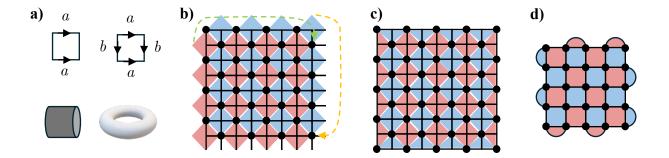

| 9.4   | Construction of Kitaev's torus code, the surface code, and the rotated surface code         | e183 |

| 9.5   | Decoding for surface codes                                                                  | 186  |

| 9.6   | Threshold theorem                                                                           | 188  |

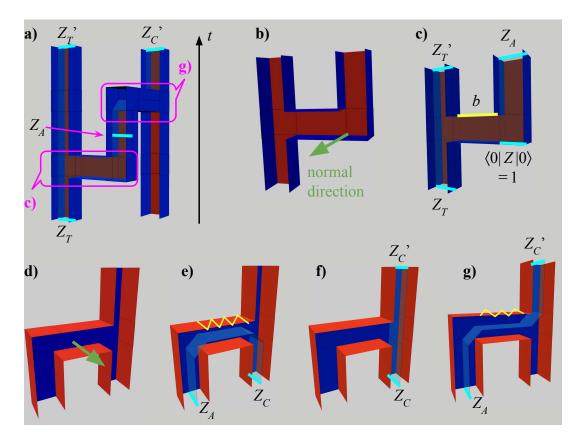

| 9.7   | Surface code operations                                                                     | 191  |

| 9.8   | Logical CNOT in different representations                                                   | 194  |

| 9.9   | Examples of correlation surfaces                                                            | 198  |

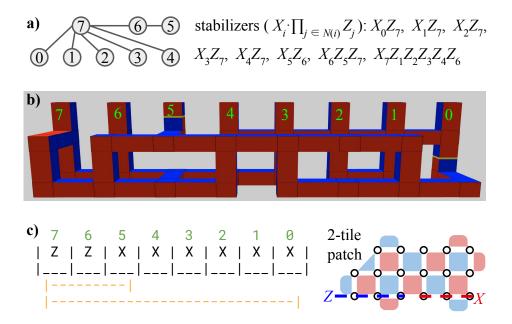

| 9.10  | Graph state                                                                                 | 200  |

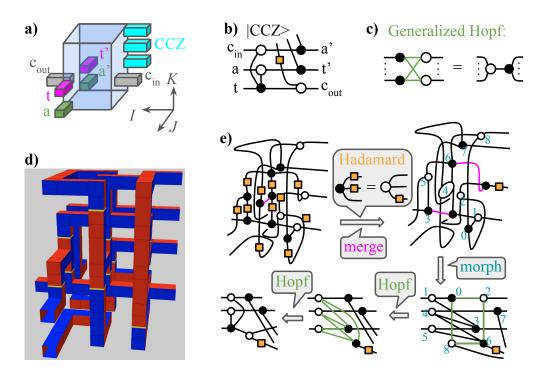

| 9.11  | Majority gate optimization                                                                  | 201  |

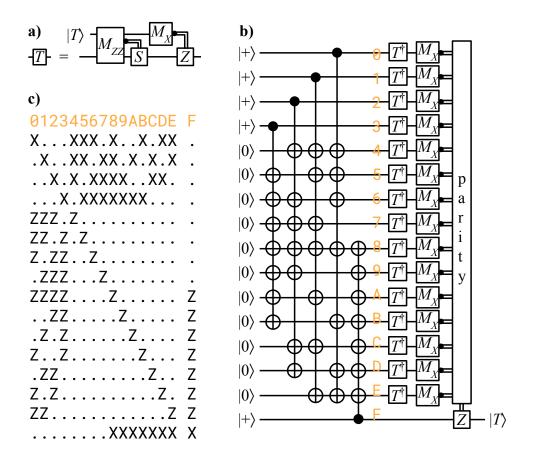

| 9.12  | Fault-tolerant $T$                                                                          | 202  |

| 9.13  | An example fault-tolerant architecture layout                                               | 203  |

| 10.1  | Lattice-surgery subroutine (LaS)                                                            | 205  |

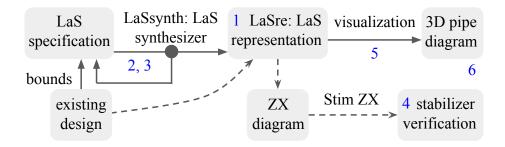

| 10.2  | Overview of LaSsynth contributions                                                          | 207  |

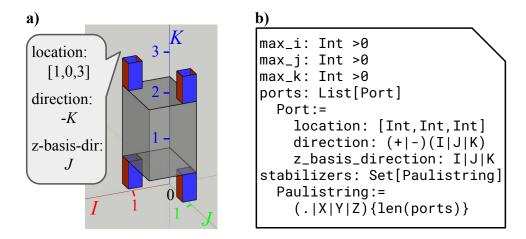

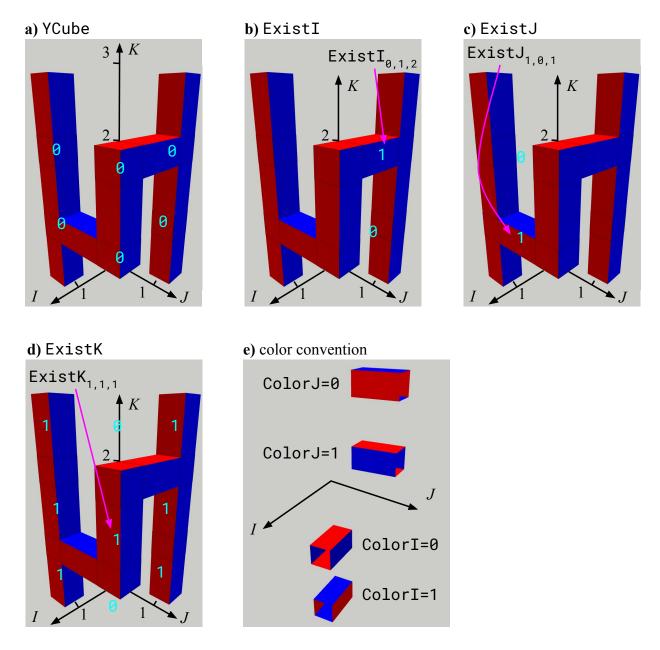

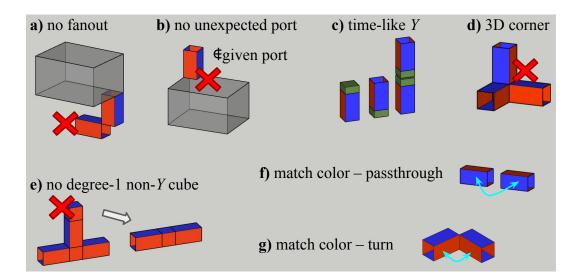

| 10.3  | Structural variables in LaSsynth                                                            | 210  |

| 10.4  | Validity constraints in LaSsynth                                                            | 212  |

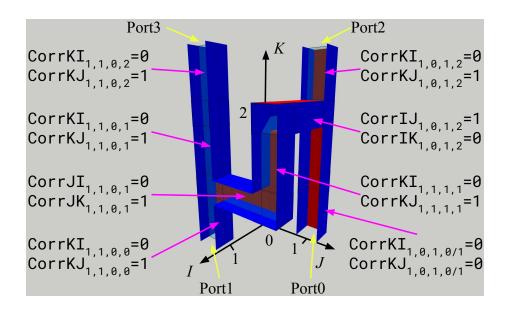

| 10.5  | Correlation surface variables in LaSsynth                                                   | 215  |

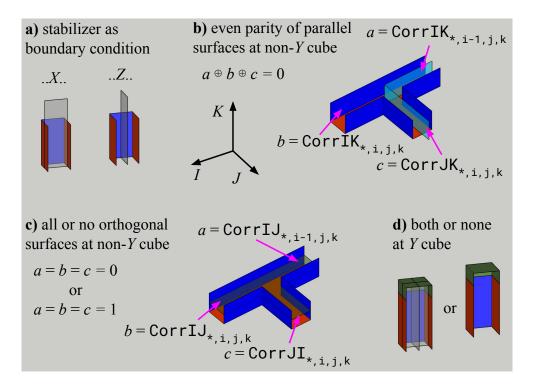

| 10.6  | Functionality constraints in LaSsynth                                                       | 217  |

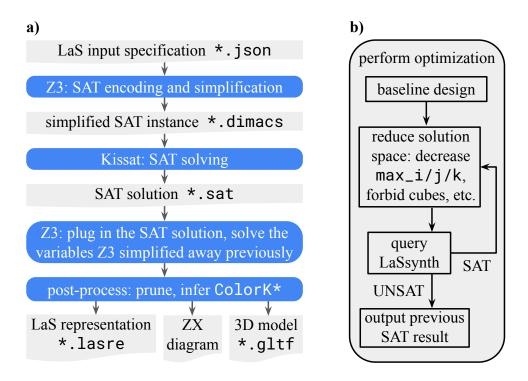

| 10.7  | Software implementation of LaSsynth                                                         | 220  |

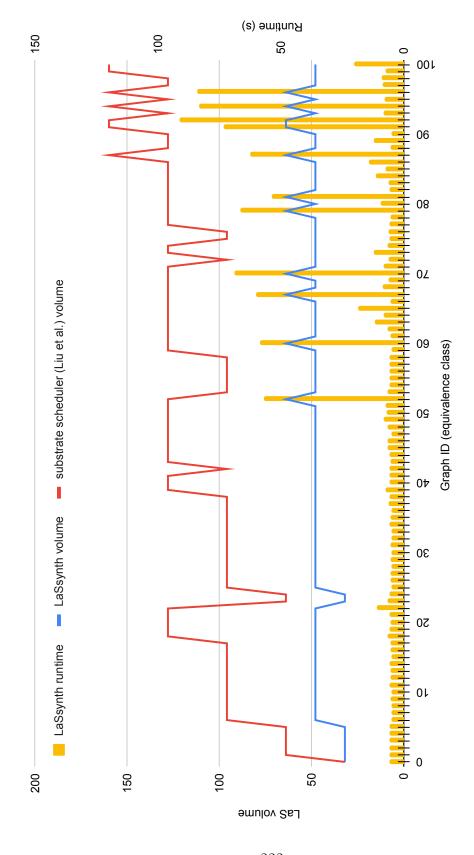

| 10.8  | LaS volume and LaSsynth runtime for 8-qubit graph state generation                          | 222  |

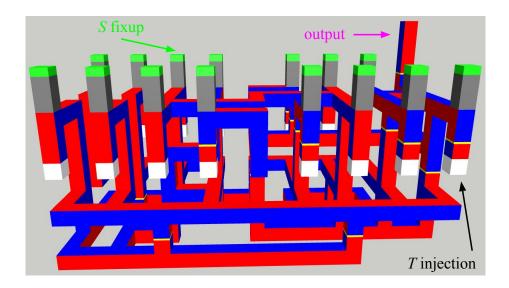

| 10.9  | Pipe diagram of a 15-to-1 T-factory with $9 \times 4 \times 4.5$ spacetime volume generated |      |

|       | with LaSsynth                                                                               | 226  |

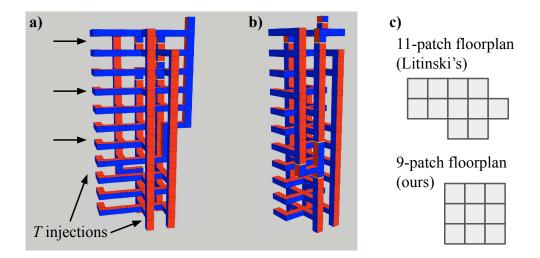

| 10.10 | 0T-factory assuming no classical delay for injections                                       | 227  |

# LIST OF TABLES

| 4.1  | Complexity of OLSQ and related works                                            | 73  |

|------|---------------------------------------------------------------------------------|-----|

| 4.2  | Evaluation of OLSQ                                                              | 81  |

| 4.3  | Evaluation of TB-OLSQ                                                           | 83  |

| 4.4  | Evaluation of QAOA-OLSQ                                                         | 87  |

| 5.1  | OLSQ-GA speedup with extra constraints                                          | 101 |

| 6.1  | OLSQ-DPQA variable values in Figure 6.4                                         | 117 |

| 6.2  | OLSQ-DPQA results on QASMBench [LSK22]                                          | 135 |

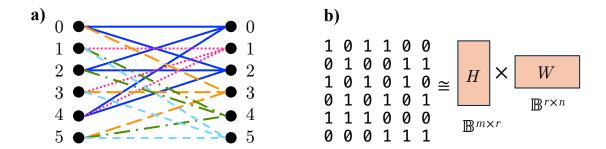

| 8.1  | Percentage of cases finding an optimal exact binary matrix factorization by row | 160 |

|      | packing and a trivial heuristic                                                 | 108 |

| 9.1  | Commutators and anticommutators of Pauli matrices                               | 176 |

| 10.1 | Size and runtime of LaSsynth for presented non-Clifford designs                 | 228 |

#### ACKNOWLEDGMENTS

I am extremely grateful to my PhD advisor, Prof. Jason Cong, for guiding the direction of my research and providing countless practical suggestions.

I would also like to thank the other members in my PhD committee, Prof. Miryung Kim, Prof. Jens Palsberg, and Prof. Chee Wei Wong, for shaping this dissertation.

I am also grateful to other colleagues listed below.

- Dolev Bluvstein, Prof. Mikhail D. Lukin, Dr. Harry Hengyun Zhou, and Wan-Hsuan Lin for collaboration on various topics in neutral atom based quantum computing, which yields Chapter 6 and Chapter 7;

- Wan-Hsuan Lin, Jason Kimko, Dr. Nikolaj S. Bjørner, Michael Lo, and Chengdi Cao for collaboration on the layout synthesis for static quantum architectures [LKT23];

- Prof. Murphy Yuezhen Niu, Craig Gidney, Dr. Noah Shutty, and Dr. Sergio Boixo for guidance during a research project at Google on fault-tolerant quantum computing [TNG24], which yields Chapter 10;

- Dr. Hanrui Wang, Pengyu Liu, Yilian Liu, Dr. Jiaqi Gu, Prof. David Z. Pan, Prof. Umut A. Acar, and Prof. Song Han for collaboration on layout synthesis for neutral atom arrays [WTL24, WLT24];

- Wan-Hsuan Lin and Prof. Murphy Yuezhen Niu for collaboration on domain-specific quantum architectures [LTN22];

- Hanyu Wang for collaboration on logic synthesis of quantum circuits [WTC24a, WTC24b];

- Shuohao Ping for collaboration on exact binary matrix factorization [TPC24], which yields Chapter 8;

- Dr. Atefeh Sohrabizadeh, Wan-Hsuan Lin, Madelyn Cain, Dr. Sheng-Tao Wang, and Prof. Mikhail D. Lukin for collaboration on the graph neural network based performance prediction for quantum optimization of maximum independent set [SLT24];

- Prof. Guojie Luo and Prof. Hong Guo at Peking University for the recommendation to the PhD program;

- Dr. Yunong Shi and Dr. Eric M. Kessler for guidance during an internship at Amazon Web Services;

- Dr. Kevin Krsulich, Dr. Thomas Alexander, and Dr. Michael B. Healy for guidance during an internship at International Business Machines;

- Prof. Weiwen Jiang for the invitation to an ICCAD '21 special session [TC21a] and the invitation to a DAC '22 tutorial;

- Dr. Rasit O. Topaloglu for the invitation of contributing a chapter to the book *Design Automation of Quantum Computers* [TC23] and the editorial efforts;

- Prof. Giovanni De Micheli for the invitation to a DATE '24 focus session [TPC24];

- Dr. Zhiding Liang for the invitation to an ICCAD '24 special session [SLT24];

- Staffs at the UCLA computer science department, especially Alexandra Luong, Joseph Brown, and Helen Tran, for the assistance during my course of study;

- Marci Baun for the editorial suggestions on various manuscripts;

- Co-workers in the VAST lab during my time, i.e. Dr. Young-Kyu Choi, Dr. Jie Wang, Dr. Weikang Qiao, Dr. Zhe Chen, Dr. Yuze Chi, Dr. Atefeh Sohrabizadeh, Karl Marrett, Dr. Licheng Guo, Jason Lau, Michael Lo, Mrunal Patel, Suhail Basalama, Dr. Linghao Song, Wan-Hsuan Lin, Stéphane Pouget, Neha Prakriya, Jason Kimko, Chengdi Cao, Dr. Lorenzo Ferretti, Zijian Ding, Zifan He, Jake Ke, Cristian Tirelli, and Hanyu Wang.

- Others that provided valuable advice including Prof. Peipei Zhou, Prof. Chen Zhang, and Prof. Zhiru Zhang.

I acknowledge funding from Intel, NEC, Synopsys, and AWS under the Center for Domain-Specific Computing (CDSC) Industrial Partnership Program, and additionally, NSF grant 2313083.

#### VITA

- 2015–2019 B.S. Electrical Engineering, Peking University.

- 2019–2022 M.S. Computer Science, University of California, Los Angeles.

#### **PUBLICATIONS**

- **B. Tan** and J. Cong. "Optimality Study of Existing Quantum Computing Layout Synthesis Tools." *IEEE Transactions on Computers* **70**(9):1363–1373, 2021.

- B. Tan and J. Cong. "Optimal Layout Synthesis for Quantum Computing." ICCAD 2020.

- **B. Tan** and J. Cong. "Optimal Qubit Mapping with Simultaneous Gate Absorption." ICCAD 2021.

- W.-H. Lin, **B. Tan**, M. Y. Niu, J. Kimko, and J. Cong. "Domain-Specific Quantum Architecture Optimization." *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, **12**(3):624–637, 2022.

- **B. Tan** and J. Cong. "Layout Synthesis for Near-Term Quantum Computing: Gap Analysis and Optimal Solution." In R. O. Topaloglu, editor, *Design Automation of Quantum Computers*, pp. 25–40, Springer International Publishing, Cham, 2023.

- **B. Tan**, D. Bluvstein, M. D. Lukin, and J. Cong. "Qubit Mapping for Reconfigurable Atom Arrays." ICCAD 2022.

- W.-H. Lin, J. Kimko, **B. Tan**, N. Bjørner, and J. Cong. "Scalable Optimal Layout Synthesis for NISQ Quantum Processors." DAC 2023.

- **D. B. Tan**, D. Bluvstein, M. D. Lukin, and J. Cong. "Compiling Quantum Circuits for Dynamically Field-Programmable Neutral Atoms Array Processors." *Quantum* 8:1281, 2024.

- H. Wang\*, **D. B. Tan**\*, P. Liu, Y. Liu, J. Gu, J. Cong, and S. Han "Q-Pilot: Field Programmable Qubit Array Compilation with Flying Ancillas." DAC 2024.

- H. Wang, P. Liu, **D. B. Tan**, Y. Liu, J. Gu, D. Z. Pan, J. Cong, U. A. Acar, and S. Han "Atomique: A Quantum Compiler for Reconfigurable Neutral Atom Arrays." ISCA 2024.

- **D. B. Tan**, M. Y. Niu, and C. Gidney. "A SAT Scalpel for Lattice Surgery: Representation and Synthesis of Subroutines for Surface-Code Fault-Tolerant Quantum Computing." ISCA 2024.

- D. B. Tan, S. Ping, and J. Cong. "Depth-Optimal Addressing of 2D Qubit Array with 1D Controls Based on Exact Binary Matrix Factorization." DATE 2024.

- **D. B. Tan**, W.-H. Lin, and J. Cong. "Compilation for Dynamically Field-Programmable Qubit Arrays with Efficient and Provably Near-Optimal Scheduling." ASP-DAC 2025.

- H. Wang, **D. B. Tan**, and J. Cong. "Quantum State Preparation Circuit Optimization Exploiting Don't Cares." ICCAD 2024.

# CHAPTER 1

# Introduction

Over the past few decades, information technology has greatly benefited from Moore's law and Dennard scaling: as semiconductor transistors shrink, more can be packed into a computing chip, enabling larger chips that consume the same amount of power per unit area while also running faster. However, as transistor sizes approach the physical limits, drastic innovations are required to continue advancing computing capabilities.

One major direction is quantum computing, as there are problems—such as integer factoring—which are widely believed to be unsolvable with polynomially many classical operations but can be solved with polynomially many quantum operations [Sho94]. This has driven rapid advancements in scaling up quantum computing hardware which leads to the focus of this dissertation: layout synthesis for quantum computing.

At a high level, quantum registers in real quantum computers have limited connectivity—a constraint too nuanced for programmers to handle directly. Layout synthesis addresses this challenge by determining how quantum data move within the quantum computer, ensuring that quantum algorithms can be executed correctly.

# 1.1 Concepts in Gate-Based Quantum Computing

For the purposes of this dissertation, only basic concepts in quantum computing are required. Readers seeking more in-depth background can refer to textbooks on quantum computing and quantum information, such as [NC10].

### 1.1.1 Quantum States

A qubit (quantum bit) is in a quantum state  $|\psi\rangle$  represented by a vector with unit norm in the two-dimensional complex vector space

$$|\psi\rangle = \begin{pmatrix} \alpha \\ \beta \end{pmatrix} \text{ with } |\alpha|^2 + |\beta|^2 = 1.$$

(1.1)

We can decompose the vector with the standard basis

$$|\psi\rangle = \begin{pmatrix} \alpha \\ \beta \end{pmatrix} = \alpha \begin{pmatrix} 1 \\ 0 \end{pmatrix} + \beta \begin{pmatrix} 0 \\ 1 \end{pmatrix} = \alpha |0\rangle + \beta |1\rangle.$$

(1.2)

We use the *ket* notation  $|0\rangle$  and  $|1\rangle$  to represent *basis states*, which correspond to the basis vectors. The coefficients of basis states,  $\alpha$  and  $\beta$ , are dubbed *amplitudes*. In contrast, a bit is either 0 or 1, but cannot be a linear combination, i.e., *superposition*, of 0 and 1.

However, we cannot directly access the amplitudes of a quantum state in general. The only way we can extract information from a qubit is by measurements. When we prepare  $\alpha|0\rangle + \beta|1\rangle$  and measure it in basis  $\{|0\rangle, |1\rangle\}$ , we always receive either 0 or 1. The probability of receiving 0 and 1 are  $|\alpha|^2$  and  $|\beta|^2$ , respectively. If we receive 0, the qubit switches to state  $|0\rangle$  after the measurement; if we receive 1, the qubit switches to state  $|1\rangle$  after the measurement. Thus, a measurement "collapses" the superposition to one of the basis states. Mathematically, the collapse projects the state onto basis states and normalize it, i.e., scaling the vector so that the norm is 1.

A global phase is a complex number with unit norm, i.e.,  $e^{i\theta}$ . A global phase does change the measurement probabilities since they are squared norms of amplitudes, which means the global phase will cancel out, e.g.,  $|\alpha e^{i\theta}|^2 = |\alpha|^2$ .

The basis  $\{|0\rangle, |1\rangle\}$  is known as the *computational basis* but we can use other bases in the measurement, e.g., the Hadamard basis  $|\pm\rangle := (|0\rangle \pm |1\rangle)/\sqrt{2}$ . Then, after the measurement, the state can be either in  $|+\rangle$  or  $|-\rangle$ . The probability of getting  $|+\rangle$  and  $|-\rangle$  are respectively

$$|\langle +|\psi\rangle|^2 = \left|\frac{\left(1 \quad 1\right)}{\sqrt{2}} \cdot \begin{pmatrix} \alpha \\ \beta \end{pmatrix}\right|^2 = \frac{|\alpha+\beta|^2}{2}, \ |\langle -|\psi\rangle|^2 = \left|\frac{\left(1 \quad -1\right)}{\sqrt{2}} \cdot \begin{pmatrix} \alpha \\ \beta \end{pmatrix}\right|^2 = \frac{|\alpha-\beta|^2}{2}, \ (1.3)$$

where  $\langle +|$  called 'bra +' is the Hermitian conjugate of  $|+\rangle$ . In the matrix form, Hermitian conjugate is the transpose of complex conjugate, so a bra, being the conjugate of a ket, corresponds to a row vector. Thus, the product of a bra and a ket,  $\langle \psi | \phi \rangle$ , is a complex number, which quantifies the overlap between the two. The braket notation  $\langle \psi | \phi \rangle$  is just the inner product in the vector space,  $\langle \psi, \phi \rangle$ . The vector form of  $|+\rangle$  in the Hadamard basis is  $[1,0]^T$  (where the superscript T means transpose) because  $|+\rangle = 1 \cdot |+\rangle + 0 \cdot |-\rangle$ . This is the same as the vector form of  $|0\rangle$  in the computational basis. (We use brackets in the vector instead of parentheses to signify that it is associated with the Hadamard basis.) Similarly, the vector form of  $|-\rangle$  in the Hadamard basis is the same with the vector form of  $|1\rangle$  in the computational basis. When the basis is not specified, usually it is the computational basis and measurements are also in the computational basis.

A quantum state of a larger system consisting of n qubits is a vector with unit norm in the  $2^n$  dimensional complex vector space. For instance, a general two-qubit state is

$$|\phi\rangle = \begin{pmatrix} \alpha \\ \beta \\ \gamma \\ \lambda \end{pmatrix} = \alpha \begin{pmatrix} 1 \\ 0 \\ 0 \\ 0 \end{pmatrix} + \beta \begin{pmatrix} 0 \\ 1 \\ 0 \\ 0 \end{pmatrix} + \gamma \begin{pmatrix} 0 \\ 0 \\ 1 \\ 0 \end{pmatrix} + \lambda \begin{pmatrix} 0 \\ 0 \\ 0 \\ 1 \end{pmatrix} = \alpha |0\rangle |0\rangle + \beta |0\rangle |1\rangle + \gamma |1\rangle |0\rangle + \lambda |1\rangle |1\rangle, (1.4)$$

where the basis vectors are 4-dimensional. By writing several kets consecutively, we mean their tensor product and neglect the symbol  $\otimes$  for convenience. A general tensor product state of two individual qubits,  $|\psi_0\rangle$  and  $|\psi_1\rangle$ , is

$$|\psi_{1}\rangle|\psi_{0}\rangle := |\psi_{1}\rangle \otimes |\psi_{0}\rangle = \begin{pmatrix} \alpha \\ \beta \end{pmatrix} \otimes \begin{pmatrix} \alpha' \\ \beta' \end{pmatrix} = \begin{pmatrix} \alpha \begin{pmatrix} \alpha' \\ \beta' \end{pmatrix} \\ \beta \begin{pmatrix} \alpha' \\ \beta' \end{pmatrix} \end{pmatrix} = \begin{pmatrix} \alpha\alpha' \\ \alpha\beta' \\ \beta\alpha' \\ \beta\beta' \end{pmatrix}, \tag{1.5}$$

where the tensor product is computed by multiplying the operand after the  $\otimes$  to each element in the operand before the  $\otimes$ . By combining Equation 1.2 and Equation 1.5, we can verify that our definition of two-qubit computational basis states is consistent with the vectors in Equation 1.4, e.g.,  $|0\rangle|0\rangle$  is indeed  $(1,0,0,0)^T$ .

A general two-qubit state, Equation 1.4, does not necessarily have the product form in Equation 1.5. This means that there are many two-qubit states where the qubits cannot be considered individuals. In this case, the two qubits are *entangled*.

With multi-qubit states, it is common to omit the normalization factor for convenience during computations. For instance, if we measure the first qubit in Equation 1.4 and the measurement yields 0, we typically express the resulting state as  $|0\rangle(\alpha|0\rangle + \beta|1\rangle$ ). Technically, the state should be normalized as  $|0\rangle\left(\frac{\alpha}{\sqrt{|\alpha|^2+|\beta|^2}}|0\rangle + \frac{\beta}{\sqrt{|\alpha|^2+|\beta|^2}}|1\rangle\right)$ , but this can be cumbersome, particularly if there are further computational steps. (Note that  $\sqrt{|\alpha|^2+|\beta|^2}$  might not equal 1; instead, it is the total state norm,  $\sqrt{|\alpha|^2+|\beta|^2+|\gamma|^2+|\lambda|^2}$ , that equals 1.) Therefore, we often skip normalization in intermediate steps and apply it only at the end of the computation to simplify the expressions. This approach is especially useful when we encounter zeros, such as  $\langle 1|0\rangle$ , where normalization is not applicable. By ignoring normalization at first, we maintain uniformity in mathematical expressions, and the terms with zeros can be dropped in the end.

#### 1.1.2 Quantum Gates

A quantum gate transforms an input state to an output state. Since general quantum states are complex vectors with unit norms, a general transform between states only needs to preserve the norm. Such transforms are *unitary*. The quantum state of n qubits has dimension  $2^n$ , so the quantum gates are in the unitary group  $U(2^n)$ . For example, some

common single-qubit gates are X, H, S, and T. † means Hermitian conjugation.

$$X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, \ Z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}, \ H = \frac{\sqrt{2}}{2} \begin{pmatrix} 1 & 1 \\ 1 & -1 \end{pmatrix},$$

$$S = \begin{pmatrix} 1 & 0 \\ 0 & i \end{pmatrix}, \ S^{\dagger} = \begin{pmatrix} 1 & 0 \\ 0 & -i \end{pmatrix}, \ T = \begin{pmatrix} 1 & 0 \\ 0 & e^{i\pi/4} \end{pmatrix}, \ T^{\dagger} = \begin{pmatrix} 1 & 0 \\ 0 & e^{-i\pi/4} \end{pmatrix}.$$

(1.6)

Some common two-qubit gates are CZ, CNOT, and SWAP.

$$CZ = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & -1 \end{pmatrix}, CNOT = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix}, SWAP = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}. (1.7)$$

The CNOT (controlled-NOT) gate, operates by leaving the second qubit unchanged when the first qubit is in the  $|0\rangle$  state, and by applying an X gate (which flips the amplitudes) to the second qubit when the first qubit is in the  $|1\rangle$  state. Thus, CNOT is also known as CX (controlled-X). Mathematically, the effect of a CNOT can be expressed as:

$$\text{CNOT}\left[|0\rangle(\alpha'|0\rangle+\beta'|1\rangle)\right] = |0\rangle(\alpha'|0\rangle+\beta'|1\rangle), \text{ CNOT}\left[|1\rangle(\alpha'|0\rangle+\beta'|1\rangle)\right] = |1\rangle(\beta'|0\rangle+\alpha'|1\rangle). \tag{1.8}$$

Thus, the first qubit is typically referred to as the control qubit, and the second as the target qubit. However, it is important to note that the CNOT gate does not simply "do nothing" to the control qubit, especially when the control qubit is in a superposition. This is a key difference between the quantum CNOT gate and classical gates. To illustrate, consider applying a CNOT gate to a product two-qubit state (Equation 1.5):

$$\begin{pmatrix}

1 & 0 & 0 & 0 \\

0 & 1 & 0 & 0 \\

0 & 0 & 0 & 1 \\

0 & 0 & 1 & 0

\end{pmatrix}

\begin{pmatrix}

\alpha \alpha' \\

\alpha \beta' \\

\beta \alpha' \\

\beta \beta'

\end{pmatrix} = \begin{pmatrix}

\alpha \alpha' \\

\alpha \beta' \\

\beta \beta' \\

\beta \alpha'

\end{pmatrix} \neq \begin{pmatrix}

\alpha \\

\beta

\end{pmatrix} \otimes \begin{pmatrix}

\beta' \\

\alpha'

\end{pmatrix} = \begin{pmatrix}

\alpha \beta' \\

\alpha \alpha' \\

\beta \beta' \\

\beta \alpha'

\end{pmatrix}.$$

(1.9)

The CNOT gate flips the lower half of the state vector. As a result, the vector after applying the CNOT gate is different from the tensor product of the original control state and the flipped target state. In general, the state after a CNOT no longer has a product form, indicating that the qubits are entangled by the CNOT.

We present another interesting aspect of the CNOT gate by changing the basis. The Hadamard basis we have introduced  $|\pm\rangle$  can transform to and from the computational basis  $\{|0\rangle, |1\rangle\}$  by, no surprise, the Hadamard gate (H in Equation 1.6). Since  $\{|0\rangle, |1\rangle\}$  are eigenvectors of Z and  $|\pm\rangle$  are eigenvectors of X, they are also called Z basis and X basis, respectively. Let us consider the matrix form of the CNOT gate in the X basis:

$$(H \otimes H)^{\dagger} \cdot \text{CNOT} \cdot (H \otimes H) =$$

Recall that  $|+\rangle = [1,0]^T$  and  $|-\rangle = [0,1]^T$  in X basis. Let us apply the CNOT gate to some product states:

$$\begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix} = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}, \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} 1 \\ 0 \\ 1 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix}. \tag{1.11}$$

We can observe that the effect of the CNOT gate in the X basis is: when the second qubit is in the state  $|+\rangle$ , nothing happens; when the second qubit is in the state  $|-\rangle$ , the first qubit is flipped from  $|+\rangle$  to  $|-\rangle$ . Thus, if we consider the action of CNOT in the X basis, we should call the second qubit as the control qubit and the first qubit as the target qubit. The roles of control and target is reversed compared to the case in the Z basis! This further implies that we cannot interpret the CNOT gate in a classical sense.

Given all these gates, a natural question is: are they sufficient? NAND gates are sufficient for universal classical computing. It turns out that CNOT and the generic single-qubit gate below are sufficient for universal quantum computing [NC10]

$$U_3(\theta, \phi, \lambda) := \begin{pmatrix} \cos(\theta/2) & -e^{i\lambda}\sin(\theta/2) \\ e^{i\phi}\sin(\theta/2) & e^{i\lambda+i\phi}\cos(\theta/2) \end{pmatrix}.$$

(1.12)

We call  $U_3$  a parametrized gate or a programmable gate. It is actually a family of gates which can be instantiated to specific gates by assigning values to the parameters, e.g.,  $U_3(\theta = \pi/2, \lambda = \pi, \phi = 0)$  is just H. There are other universal quantum gate sets, but we refrain from exhibiting them here since they are irrelevant for now.

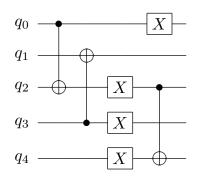

Another important gate is CCNOT, or Toffoli. It flips the last qubit with X if the first two qubits are in  $|11\rangle$ ; otherwise, it does nothing. The projector to  $|11\rangle$  is  $|11\rangle\langle 11|$ : applying it to a quantum state  $|\phi\rangle$ , the  $\langle 11|$  first produces the amplitude which is the "overlap" of  $|\phi\rangle$  and  $\langle 11|$ . Then, the amplitude is multiplied to  $|11\rangle$  for the component of  $|11\rangle$  inside  $|\phi\rangle$ . The projector of the subspace orthogonal to  $|11\rangle$  is  $I\otimes I-|11\rangle\langle 11|$ . Therefore, the matrix form of CCNOT is

$$\text{CCNOT} = (I \otimes I - |11\rangle\langle 11|) \otimes I + |11\rangle\langle 11| \otimes X = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \end{pmatrix}. \quad (1.13)$$

Similarly, the matrix form of CNOT can also be derived from the projector description: CNOT=  $|0\rangle\langle 0| \otimes I + |1\rangle\langle 1| \otimes X$  where the first qubit is the control, and the second qubit is the target. In general, any Boolean logic circuit can be first expanded to a Boolean

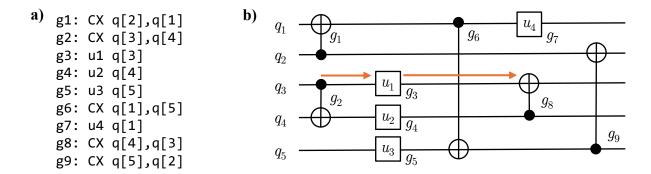

Figure 1.1: An example of unitary quantum program/circuit. **a)** A quantum program consisting of 9 gates on 5 program qubits. **b)** Circuit diagram of the quantum program. Each horizontal wire is a program qubit. Time goes from left to right. The arrow means a dependency chain  $(g_2, g_3, g_8)$ .

reversible circuit, for which Toffoli is sufficient, and the Toffoli gates can be decomposed into single-qubit and two-qubit gates.

An important relation between two gates is *commutation*. If the result of first applying gate 0 followed by gate 1 is the same as the result of applying them in the reversed order, we say these two gates commute. If two gates act on disjoint qubits, they always commute. For gates acting on the same qubit, it is nontrivial to judge in general. T and CZ commute because they are both diagonal matrices; but X and H do not commute, since  $XH \neq HX$ .

### 1.1.3 Quantum Circuits

A quantum algorithm manipulates a set of qubits with quantum gates. Most notably, Shor's algorithm can factor a number N with O(polylog N) quantum gates, whereas the best known classical algorithm needs  $\Theta(N)$  operations [Sho94]. The readers can refer to a recent survey [DMB23] for a comprehensive list of quantum algorithms.

Quantum algorithms can be expressed in many forms, some very abstract. For our purposes, it suffices to conceptualize them as *quantum programs* written in some quantum computing instruction set. For example, in Figure 1.1a, there are several single-qubit and

two-qubit gates on five program qubits. A quantum program is often visualized as a quantum circuit, like the one in Figure 1.1b. The terms 'quantum program' and 'quantum circuit' are used interchangeably throughout this dissertation. In a circuit diagram, each program qubit is depicted as a horizontal wire, and as time progresses from left to right, gates on the wire are applied to this qubit. In our example,  $u_1$ ,  $u_2$ ,  $u_3$ , and  $u_4$  are instances of  $U_3$  (Equation 1.12), each black dot represents the control qubit of a CNOT (Equation 1.7), and each  $\oplus$  symbolizes the target qubit of a CNOT.

While a quantum circuit does not explicitly schedule the gates, it does encode their relative order. In our example, there are three gates  $g_2$ ,  $g_3$ , and  $g_8$  that act sequentially on  $g_3$ . This means  $g_3$  must follow  $g_2$ , and  $g_8$  must follow  $g_3$ . We refer to this type of relative ordering as a dependency. When multiple dependencies are linked head-to-tail, they form a dependency chain. For instance,  $(g_2, g_3, g_8)$  is a dependency chain of length 3.

It is possible to partition a circuit into layers so that, within each layer, a qubit is involved in at most one gate. If two gates have a dependency, they cannot be placed in the same layer, but some flexibility remains. For example,  $g_3$  could be placed in the same layer as  $g_5$  or  $g_6$ . The minimum number of layers in a quantum circuit is referred to as its *depth*, which corresponds to the length of the longest dependency chain. The *width* of a circuit is simply the number of qubits.

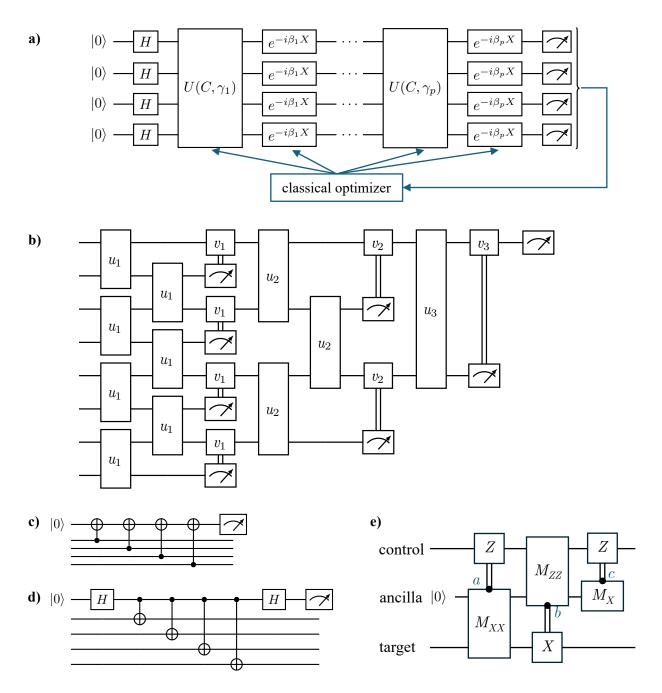

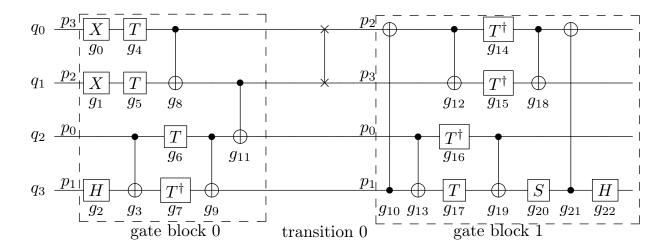

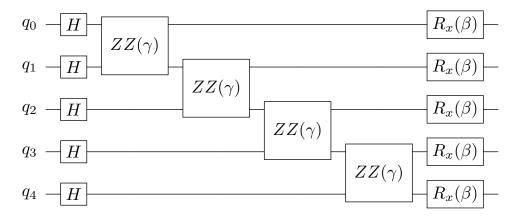

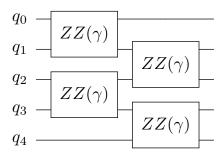

Since the unitary gates belong to the unitary group, multiplying them according to the order specified in a circuit results in a unitary transformation, which we term a unitary circuit. However, a general quantum circuit includes components beyond unitary gates. For example, Figure 1.2a illustrates a circuit for the quantum approximate optimization algorithm (QAOA) [FGG14], where H,  $U(C,\gamma)$ , and  $e^{-i\beta X}$  are unitary. This circuit also includes qubit initializations represented by  $|0\rangle$  and measurements indicated by the meter symbols. Additionally, this algorithm features an outer layer optimization loop: based on the measurement results, a classical optimizer tunes the parameters ( $\beta$ s and  $\gamma$ s) in the quantum circuit and reruns it. Such quantum circuits with tunable parameters are referred to as

variational quantum circuits.

Measurements can occur not only at the end of a circuit but also in the middle, i.e., mid-circuit readouts. Figure 1.2b depicts a quantum convolutional neural network (QCNN) [CCL19] circuit, where the  $u_i$ s are unitary gates. In this example, mid-circuit readouts apply feed-forward gates: if the outcome of the measurement is 1, a corresponding single-qubit gate,  $v_i$ , is applied. This type of circuit is referred to as a dynamic circuit because the operations implemented on the quantum computer depend on measurement results known only at runtime. In contrast, the QAOA circuit parameters are determined by a classical optimizer before each execution of the circuit.

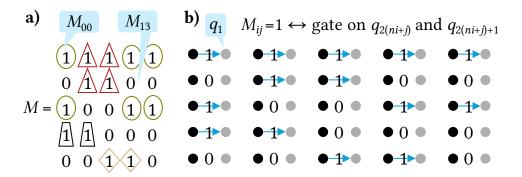

Another important family of circuits is the parity measurement circuit. When all qubits are measured, as in Figure 1.2a, the quantum state is projected onto the computational basis  $(|0...0\rangle, |0...1\rangle, ..., |1...1\rangle)$ . However, sometimes the goal is to measure only the parity of a subset of qubits, which differs from measurement in the computational basis. For instance, measuring a Bell state  $|\Phi^+\rangle:=(|00\rangle+|11\rangle)/\sqrt{2}$  in the computational basis collapses the superposition to either  $|00\rangle$  or  $|11\rangle$ . Conversely, measuring the parity of the two qubits does not collapse the superposition, as both  $|00\rangle$  and  $|11\rangle$  have even parity, preserving the state  $|\Phi^{+}\rangle$  after the measurement. A parity measurement circuit is illustrated in Figure 1.2c. An ancilla qubit (the top wire) is used to collect the parity. For each qubit whose parity is to be measured, a CNOT gate is applied, controlled by this qubit and targeting the ancilla. The ancilla is initialized to  $|0\rangle$  and each CNOT flips the ancilla if the controlling qubit is  $|1\rangle$ . An even number of flips cancels out, leaving the ancilla state as the parity of the other qubits, which is then measured at the end. This circuit measures the parity of four qubits in the Zbasis. A similar circuit for measuring parity in the X basis is shown in Figure 1.2d. Several arguments can explain why this circuit measures the X parity. One elegant approach uses the insight from Equation 1.11: in the X basis, the roles of control and target in a CNOT are reversed. The initialization followed by an H gate equates to an initialization in the X basis into  $|+\rangle$ ; similarly, the final measurement preceded by an H gate equates to a measurement

Figure 1.2: Examples of general circuits. **a)** Quantum approximate optimization algorithm circuit with initializations, parameterized unitary gates, measurements, and an outer layer classical optimizer. **b)** Quantum convolutional neural network circuit with mid-circuit readouts and feed-forward gates. **c)** Z-parity, **d)** X-parity measurement circuit. **e)** A CNOT implemented with measurements and feed-forward gates. a, b, and c are measured results.

in the X basis. In the interim, the four reversed CNOTs collect the X parity to the ancilla qubits because, in the X basis, the roles of control and target are reversed.

Figure 1.2e displays a quantum circuit equivalent to a CNOT gate, implemented using parity measurements and feed-forward single-qubit gates, which is useful because parity measurements are native to certain quantum architectures (Section 9.3.1). Demonstrating that this circuit functions as a CNOT is more elegantly done via ZX calculus, detailed in Section 9.1.4. However, we present a proof using previously introduced concepts, utilizing bit variables a, b, and c to denote the measurement results. The subscripts C, T, and A stand for the control, target, and ancilla qubits, respectively. If a=0, the XX parity measurement projects the state onto the even parity subspace. The projector is expressed as  $\frac{II+XX}{2}$  because for a state  $|\psi\rangle$  in the even parity subspace,  $XX|\psi\rangle = |\psi\rangle$ , so  $\frac{II+XX}{2}|\psi\rangle = |\psi\rangle$ . Conversely, if  $|\phi\rangle$  is in the odd parity subspace,  $XX|\phi\rangle = -|\phi\rangle$ , so the projector to the odd parity subspace is  $\frac{II-XX}{2}$ . In summary, the XX measurement is expressed as  $(I_TI_A + (-1)^a X_T X_A)/2$ . Feedforward gates are conditionally activated based on the measurement results a, b, and c, such as applying  $Z_c^a$ : if the parity is even (a=0), nothing is done; otherwise, a Z gate is applied the control qubit. The final measurement of the ancilla is denoted by  $\langle +|_A Z_A^c\rangle$ : a result of c=0 leads to a  $|+\rangle$  state; otherwise, it results in  $|-\rangle$ .

$$(\langle +|_{A}Z_{A}^{c}Z_{C}^{c}I_{T}) \cdot \left(\frac{I_{C}I_{A} + (-1)^{b}Z_{C}Z_{A}}{2}X_{T}^{b}\right) \cdot \left(\frac{I_{T}I_{A} + (-1)^{a}X_{T}X_{A}}{2}Z_{C}^{a}\right) |0\rangle_{A}$$

$$\stackrel{(1)}{=} \left(\langle +|_{A}Z_{A}^{c}Z_{C}^{c}X_{T}^{b} + (-1)^{b}\langle +|_{A}Z_{A}^{c+1}Z_{C}^{c+1}X_{T}^{b}\right) \cdot (Z_{C}^{a}I_{T}|0\rangle_{A} + (-1)^{a}Z_{C}^{a}X_{T}|1\rangle_{A})$$

$$\stackrel{(2)}{=} \langle +|_{Z}^{c}|0\rangle Z_{C}^{a+c}X_{T}^{b} + (-1)^{b}\langle +|_{Z}^{c+1}|0\rangle Z_{C}^{a+c+1}X_{T}^{b}$$

$$+ (-1)^{a}\langle +|_{Z}^{c}|1\rangle Z_{C}^{a+c}X_{T}^{b+1} + (-1)^{a+b}\langle +|_{Z}^{c+1}|1\rangle Z_{C}^{a+c+1}X_{T}^{b+1}$$

$$\stackrel{(3)}{=} Z_{C}^{a+c}X_{T}^{b} + (-1)^{b}Z_{C}^{a+c+1}X_{T}^{b} + (-1)^{a+c}Z_{C}^{a+c}X_{T}^{b+1} + (-1)^{a+b+c+1}Z_{C}^{a+c+1}X_{T}^{b+1}$$

$$\stackrel{(4)}{=} \begin{cases} II + ZI + IX - ZX & \text{if } a + c = 0 \text{ and } b = 0 \\ ZI + II - ZX + IX & \text{if } a + c = 1 \text{ and } b = 0 \\ IX - ZX + II + ZI & \text{if } a + c = 0 \text{ and } b = 1 \\ ZX - IX - ZI - II & \text{if } a + c = 1 \text{ and } b = 1 \end{cases}$$

In step (1), the first two expressions are combined, and the third is multiplied by  $|0\rangle_A$ . Constants are ignored for simplicity. Step (2) expands and simplifies the terms, so that all the ancilla terms are combined. In step (3), we compute the ancilla terms to numbers, e.g.,  $\langle +|Z^c|1\rangle = (-1)^c$ . This results in a sum of four terms each defined by measurement results. We observe a and c always appear as a+c, leading to the expansion in step (4), which presents the cases for possibilities of a+c and b. Note that  $II+ZI+IX-ZX=(I+Z)I+(I-Z)X=|0\rangle\langle 0|\otimes I+|1\rangle\langle 1|\otimes X$  is a CNOT. Thus, all four possible outcomes correspond to a CNOT, demonstrating that the described circuit functions as a CNOT. The case of a+c=b=1 includes a global phase of -1, which is irrelevant to the functionality.

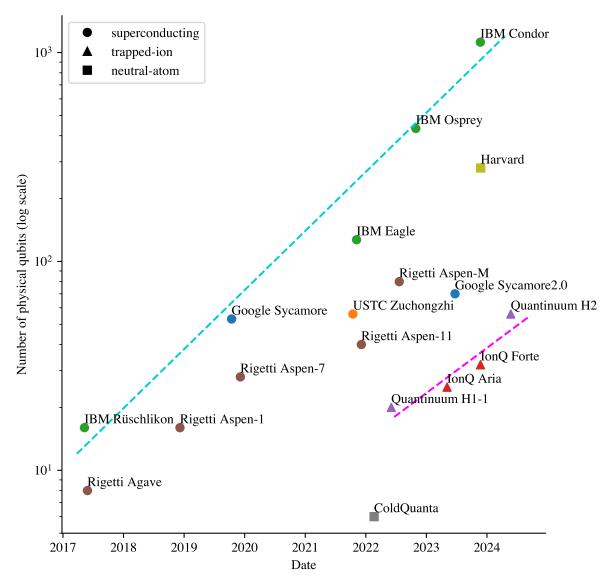

## 1.2 Status of Quantum Computing Hardware

Since the discovery of quantum algorithms with potential runtime advantages over classical algorithms, significant progress has been made in scaling up quantum computing hardware to run these algorithms. In Figure 1.3, we present data showing the number of physical qubits (on a logarithmic scale) versus the release dates of quantum computers in recent years. While this collection does not capture all existing quantum computers, the data reveal that the maximum number of physical qubits has roughly grown exponentially, i.e., linear in a logarithmic scale.

The scale of a quantum computer, characterized by the number of physical qubits, is not the only metric that matters; the quality of qubits and quantum gates is also crucial. However, as long as the scale increases, we encounter growing complexity in compilation, as researchers aim to run increasingly larger quantum circuits on the hardware.

In classical computers, bits are generally encoded as voltage and can be easily "cloned" from one location on the chip to another through electric wires. Gates are physical entities that produce new bits based on the input bits. In contrast, in most quantum computing platforms, qubits themselves are physical entities. Moving qubits is much more complex than

Sources of data are as follows. Google Sycamore: [AAB19], Google Sycamore2.0: [MVM23], USTC Zuchongzhi: [WBC21], IBM Osprey: https://link.aps.org/doi/10.1103/PhysRevLett.127.180501, IBM Eagle: https://www.ibm.com/quantum/bl og/127-qubit-quantum-processor-eagle, IBM Condor: https://www.ibm.com/quantum/blog/quantum-roadmap-2033, IBM Rüschlikon: https://uk.newsroom.ibm.com/2017-05-17-IBM-Builds-Its-Most-Powerful-Universal-Quantum-Computing-Processors, IonQ Aria: https://aws.amazon.com/blogs/quantum-computing/amazon-braket-launches-ionq-aria-with-built-in-error-mitigation/, IonQ Forte: https://ionq.com/news/ionqs-most-powerful-quantum-system-ionq-forte-now-available-through-the, Quantinuum H2: https://www.quantinuum.com/news/quantinuums-h-series-hits-56-physical-qubits-that-are-all-to-all-connected-and-departs-the-era-of-classical-simulation, Quantinuum H1-1: https://www.quantinuum.com/news/quantinuum-completes-hardware-upgrade-achieves-20-fully-connected-qubits, Harvard: [BLS24], ColdQuanta: [GSS22], All Rigetti data points: https://www.rigetti.com/what-we-build.

Figure 1.3: Scaling of the number of physical qubits in recent years.

moving classical bits because quantum states cannot be cloned [WZ82, Die82]. Multi-qubit gates are not physical entities but joint operations on multiple qubits, requiring these qubits to be moved to adjacent locations.

In this section, we introduce three leading quantum computing platforms: superconducting circuits, trapped ions, and neutral atoms. This section is not intended to be an all-inclusive review of these platforms. Additionally, significant progress has also been made on other platforms, such as nuclear magnetic resonance (NMR) [LBP16], semiconductor spins [BLP23], and nitrogen-vacancy (NV) centers [PM21]. We shall not go into details on these platforms since they have not yet matched the scale or quality achieved by the first three platforms.

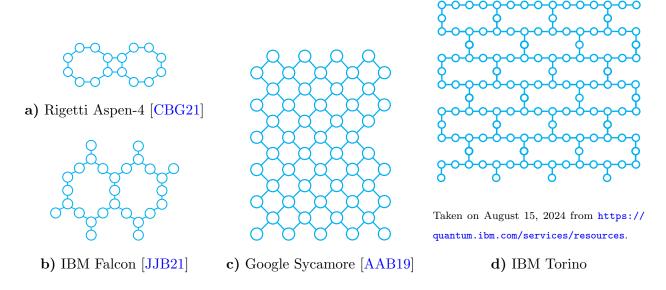

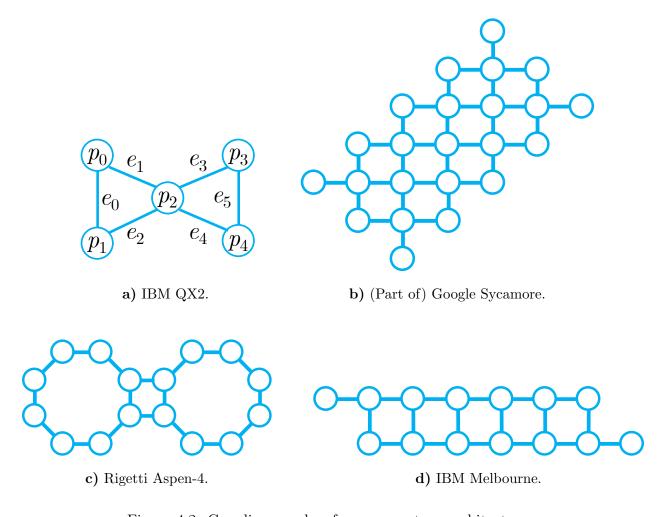

### 1.2.1 Superconducting Circuits

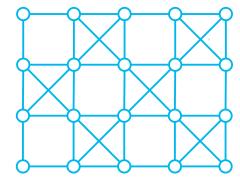

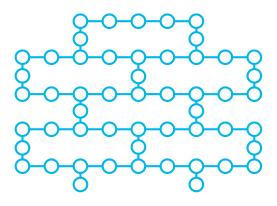

A superconducting quantum architecture can be represented by a *coupling graph*. A few examples are shown in Figure 1.4 including a recent IBM chip, Torino. In these graphs, each node represents a physical qubit, and each edge represents a *coupler* between two qubits. For instance, Torino has 133 qubits connected in a heavy-hexagon connectivity [CZY20]. The qubits and couplers are constructed from nanofabricated circuit components, resulting in a fixed coupling graph, which is why this type of architecture is referred to as *static*.

During operation, the chip must be cooled to near absolute zero temperature, in the milli-Kelvin regime, so that certain components become superconducting, allowing the quantum effects to emerge. Each qubit is connected to several control lines that extend from room temperature to the cryogenic environment. Single-qubit gates are applied by sending signals through these control lines. In current architectures, these control lines are independent. This independence allows for the simultaneous application of different single-qubit gates to any arbitrary set of qubits. However, this paradigm may need to change in the future, as it is not feasible to cool down the large number of control wires required [ALF17]. As a result, individual qubits might no longer be independently and simultaneously addressable.

Figure 1.4: Coupling graphs of some existing superconducting quantum architectures.

Multi-qubit gates are crucial for quantum algorithms. In superconducting circuits, only two-qubit gates are typically engineered. To perform such a gate, the two qubits must be adjacent on the coupling graph. By sending signals through the control lines of the two qubits and the coupler, a two-qubit entangling gate is executed. When two qubits are not adjacent, they cannot perform a direct two-qubit gate because there is no coupler to mediate their interaction. To resolve this issue, a SWAP gate (Equation 1.7) can be used to logically exchange the quantum data between two physical qubits. By performing a series of SWAP gates, two qubits can be brought adjacent on the coupling graph, allowing the desired two-qubit entangling gate to be applied.

In classical circuit design, gate fidelity is rarely a concern because fabrication processes are very mature to ensure that gates almost never produce errors under specified working conditions (one error in  $\sim 10^{27}$  operations [SRA11]). However, quantum states are much more fragile, so quantum computing requires careful attention to fidelity.

There are various sources of noise in quantum computing, with decoherence being one of the most significant. Quantum data in a qubit degrade over time. The metric that

quantifies this "lifetime" of a qubit is known as the decoherence time. Calibration data for quantum computers usually provides two values,  $T_1$  and  $T_2$ , corresponding to different types of decoherence. We use the smaller of these two as the decoherence time. Ideally, quantum algorithms should complete within a fraction of the decoherence time, as fidelity decreases rapidly when this limit is approached.

The number of gate layers that can be applied depends on the ratio of gate duration to decoherence time. For example, IBM's Torino chip has 133 qubits with a median decoherence time of 119 us. The gate duration is 68 ns, allowing for over a thousand layers of gates. There are, however, several caveats to this estimation. 1) Measuring qubits at the end of a computation takes significantly longer than applying gates—for instance, Torino requires 1.56 us for measurements, though this is still small compared to the decoherence time. 2) Apart from decoherence, other types of noise listed in the next paragraph further limit the scale of circuits that can be run reliably. 3) To satisfy the connectivity constraints between qubits, additional gates like SWAPs may need to be inserted into the circuit, which further reduces the feasible circuit size.

In addition to decoherence, other types of noise affect operations on physical qubits, including single-qubit gates, two-qubit entangling gates, and SPAM (state preparation and measurement). Within SPAM, state preparation typically just involves cooling the qubits for a sufficient period of time, so the primary concern is the fidelity of measurements. Generally, for superconducting circuits, measurements have lower fidelity than two-qubit entangling gates, which in turn have lower fidelity than single-qubit gates. For instance, the mean error rates for measurements, two-qubit gates, and single-qubit gates on the Torino chip are 1.89%, 0.315%, and 0.0312%, respectively. In superconducting circuits, running gates in parallel can reduce fidelity due to crosstalk between circuit components. When all two-qubit gates are executed simultaneously, the fidelity of each gate corresponds to the EPLG (error per layered gate) [MHP23]. For Torino, the EPLG is 0.662%, significantly higher than the

<sup>&</sup>lt;sup>1</sup> All Torino data are taken on August 15, 2024 from https://quantum.ibm.com/services/resources.

0.315% error rate for isolated two-qubit gates.

#### 1.2.2 Trapped Ions

Compared to superconducting circuits, trapped-ion based quantum computers generally feature fewer qubits but higher gate fidelity. For example, Quantinuum H2 boasts 56 qubits with a typical SPAM error rate of 0.15%, a two-qubit gate error rate of 0.15%, and a single-qubit gate error rate of 0.003%. The H2 utilizes a fabricated chip with numerous electrodes forming a 'race track'-shaped trapping electrical potential, along which the ions can be moved [MBA23]. Unlike superconducting circuits, the quantum states of ions do not require a cryogenic environment, thus eliminating the need for cooling the chip to the milli-Kelvin regime.

The number of gate layers that can be executed is influenced not only by decoherence time and gate durations but also by the need to shuttle ions together for two-qubit gates, as these movements are relatively slow. Quantinuum has implemented a physical swap protocol that rotates two ions by 180 degrees to permute their order on the track. To simplify programming, their system presents an all-to-all connectivity to the user, while the backend automatically generates the necessary physical swaps. They define a depth-1 circuit time as the sum of 1) time required to swap the qubits from a previous permutation to the current one, 2) time to apply a layer of arbitrary single-qubit gates, and 3) time to apply a layer of two-qubit gates in the current permutation. The typical memory error per qubit at depth-1 circuit time is 0.05%, indicating the possibility of running over a thousand layers of gates with overhead associated with connectivity constraints considered.

The relatively limited scale compared to superconducting circuits is due to the fact that trapped ion chips are currently only one-dimensional because of the constraints of trapping technology. For further scaling, a promising approach is the quantum charge-coupled device

<sup>&</sup>lt;sup>2</sup>All Quantinuum H2 data are taken on August 18, 2024, from the data sheet available at https://www.quantinuum.com/hardware/h2.

(QCCD) [KMW02] that lays out gate zones in 2D planes, allowing ions to shuttle between them. Given that large-scale 2D ion trap architectures are still under development, and hardware providers currently manage connectivity constraints internally, we do not focus on trapped ions in this dissertation.

#### 1.2.3 Neutral Atoms

Recently, neutral atoms trapped in arrays of optical tweezers have emerged as a promising platform for quantum computing. These systems are readily scalable, with up to 280 qubits demonstrated at Harvard [BLS24], and further significant increases in system size are anticipated. The Harvard machine reports error rates of 0.2% for measurements, 0.5% for two-qubit gates, and 0.08% for single-qubit gates.

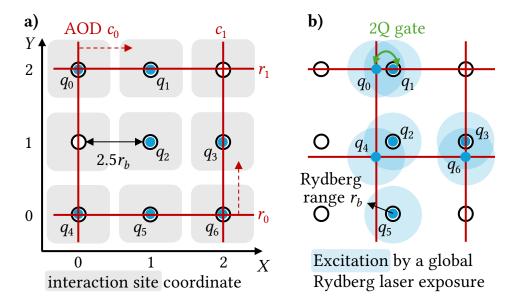

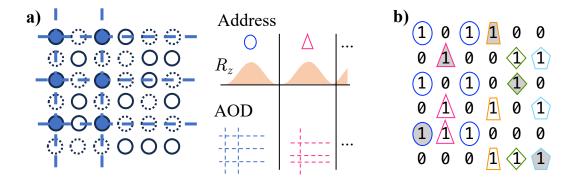

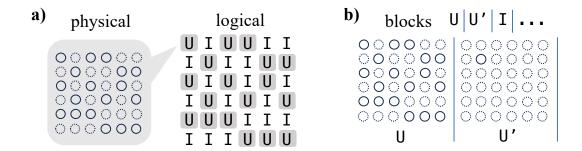

The architecture, known as dynamically field-programmable qubit arrays [BLS22, TBL22, TBL24, TLC24], features reconfigurable qubit connectivity that can be dynamically altered during computation, as depicted in Figure 1.5. This flexibility is achieved using a 2D grid of acousto-optic deflector (AOD) traps that can move within the plane, with the ability to adjust their spacing. Given the qubits' decoherence time of 1.5 s and assuming that each layer of gates involves five movements taking typically 200 us each [BLS22], this architecture could potentially support running over a thousand gate layers. However, gate fidelity and the variable duration of rearrangements for different layers must be considered to get an accurate estimation.

#### 1.3 Layout Synthesis for Static Quantum Architectures

As discussed in the previous section, various quantum computing platforms exhibit distinct connectivity constraints among their qubits. The central focus of this dissertation, layout synthesis, aims to transform quantum programs to ensure they can be executed under these connectivity constraints.

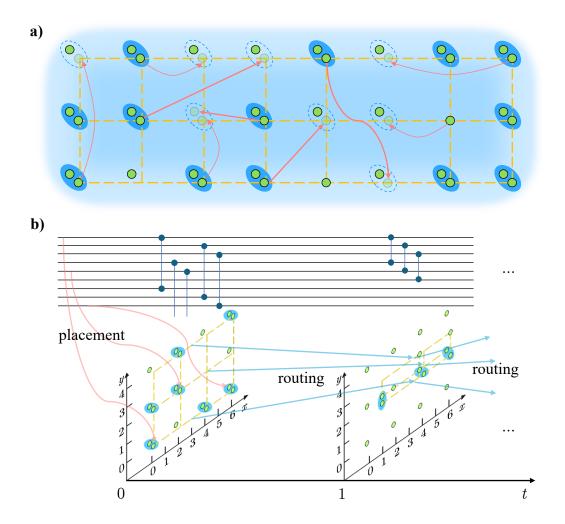

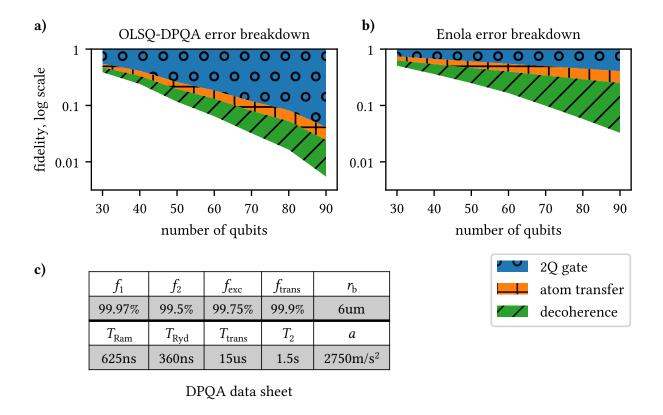

Figure 1.5: The dynamically field-programmable qubit arrays (DPQA) architecture. a) Non-local connectivity of DPQA. Atoms are kept in traps generated by a 2D acousto-optic deflector (AOD, dashed grid) and a spatial light modulator (SLM, all others). Entangling two-qubit gates are enabled by a Rydberg laser illuminating the plane (glow). Only when two atoms are within the Rydberg blockade range  $r_b$  can they perform an entangling gate (pairs in colored ovals). We can change the location of AOD atoms, and transfer atoms between AOD and SLM traps [BTM07] in the middle of computation (each arrow corresponding to some AOD reconfiguration). Through such reconfigurations, new non-local connectivities are established (oval dashes), i.e., different pairs of atoms can now perform entangling gates. (This caption continues on the next page.)

(previous page) b) Structure of compiled results. We discretize space by prescribing interaction sites shown as the proximity of integer points in the plane. The distance between sites is sufficient to suppress Rydberg interaction strengths [BLS22, EBK23] so the two-qubit entangling gates can only take place within sites. A compiler places the qubits in the quantum circuit to atoms in SLM or AOD at a specific interaction site in the beginning of execution. The time is discretized by setting stages when two-qubit gates are performed. After each stage, some AOD movements and atom transfers serve as routing for the gates executed at the next stage.

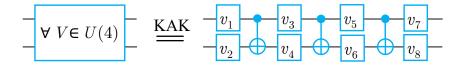

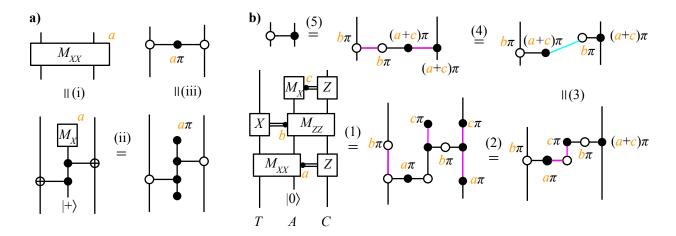

Figure 1.6: KAK decomposition. For any V that is a 4-by-4 unitary matrix, the corresponding two-qubit gate can be decomposed into 3 CNOTs and 8 single-qubit gates.

Before engaging in layout synthesis, it is essential to confirm that the quantum circuit is expressed using the native gate set of the hardware. Gates not included in this set must be decomposed into a series of executable gates from the set. Most near-term quantum algorithms, fortunately, are primarily composed of single-qubit and two-qubit gates. Moreover, canonical decompositions exist for any arbitrary two-qubit gate into single-qubit unitaries and CNOTs [VW04, PCS20], as depicted in Figure 1.6. Other important multi-qubit gates in quantum computing also have efficient decompositions [BBC95]. These decompositions are similar to *logic synthesis* in electronic design automation.

We posit that layout synthesis presents a more formidable challenge than gate decomposition. This stems from the observation that while the native gates are determined by the fundamental physics underlying the quantum computing platform, the design of coupling graphs offers greater flexibility. Indeed, the native gate set of IBM quantum computers has remained largely unchanged since the inception of their cloud-based quantum computing

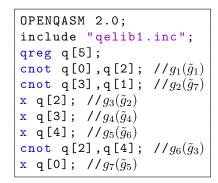

```

OPENQASM 2.0;

include "qelib1.inc";

qreg q[3]; // Initiate

3 logical qubits

h q[2]; //g_1

cnot q[1], q[2]; //g_2

tdg q[2]; //g_3

cnot q[0], q[2]; //g_4

t q[2]; //g_5

cnot q[1], q[2]; //g_6

tdg q[2]; //g7

cnot q[0], q[2]; //g_8

t q[1]; //g_9

t q[2]; //g_{10}

cnot q[0], q[1]; //g_{11}

h q[2]; //g_{12}

t q[0]; //g_{13}

tdg q[1]; //g_{14}

cnot q[0], q[1]; //g_{15}

```

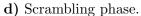

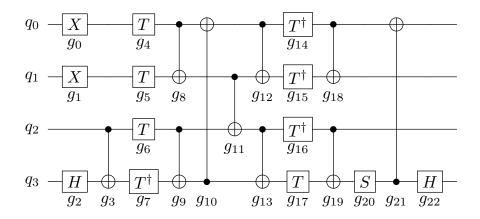

b) Toffoli circuit diagram.

a) Toffoli program.

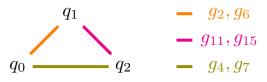

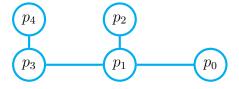

c) Qubit interaction graph of Toffoli.

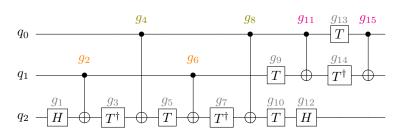

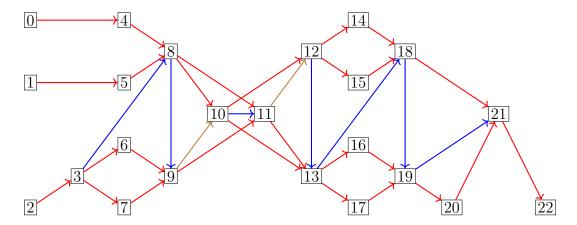

Figure 1.7: Toffoli circuit. Single-qubit gates are colored gray. Identical two-qubit gates applied at different times have the same color, e.g.,  $g_2$  and  $g_6$  are orange because they are both  $CNOT(q_1, q_2)$  but at different times.

service, as the core qubit technology has not changed drastically. However, quantum computers featuring vastly different coupling graphs have been introduced over recent years, as evidenced by the variations shown in Figure 1.4.

#### 1.3.1 Problem Statement

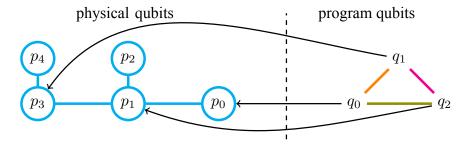

A static architecture, such as superconducting circuits, has fixed connectivity between qubits, represented by a coupling graph G = (P, E). For illustrative purposes, consider a small 5-qubit architecture displayed on the left of Figure 1.8a. In this graph, each vertex represents a physical qubit, and each edge allows the application of two-qubit entangling gates between connected vertices. We address the layout synthesis problem for the Toffoli circuit depicted in Figure 1.7b on the 5-qubit architecture, which comprises 9 single-qubit gates and 6 two-

a) Initial placement for Toffoli circuit

Figure 1.8: Layout synthesis for the Toffoli circuit on a 5-qubit architecture.

qubit gates. Here, the cardinality |g| = 1 if g is a single-qubit gate and |g| = 2 if it is a two-qubit gate. The notation  $g \cup g'$  and  $g \cap g'$  represent the sets of qubits involved in g or g' and in both g and g', respectively. For instance, in Figure 1.7b,  $q_1, q_2 \in g_2$ ,  $q_0 \in g_{13}$ , and  $|g_4| = |g_6| = 2$ .

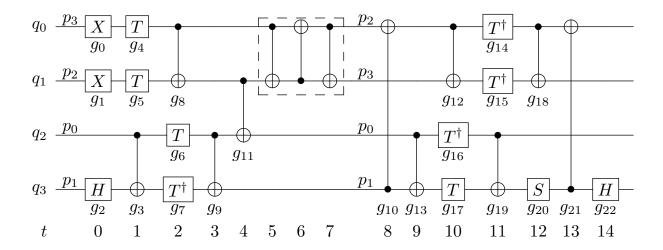

Layout synthesis has to produce an *initial placement*, which maps program qubits to physical qubits, a *gate scheduling*, which records the execution time of gates, and possibly some SWAP gates to adhere to connectivity constraints.

The initial placement is a map  $\pi_0: Q \to P$  to facilitate subsequent gate scheduling. By constructing a qubit interaction graph from all the two-qubit gates as shown in Figure 1.7c, we can determine if this graph can be embedded into the coupling graph so that there is no need for further transformations in gate scheduling. Typically, not all two-qubit gates can

be directly mapped to edges in the coupling graph due to topological differences, such as the absence of triangles in the coupling graph but presence in the qubit interaction graph. Nonetheless, a valid initial placement is depicted in Figure 1.8a where  $\pi_0(q_0) = p_0$ ,  $\pi_0(q_1) = p_3$ , and  $\pi_0(q_2) = p_1$ .

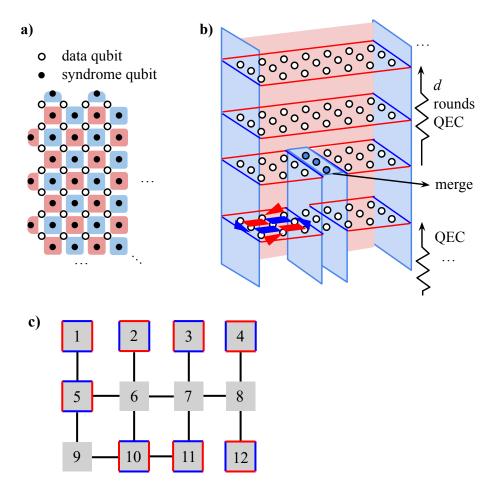

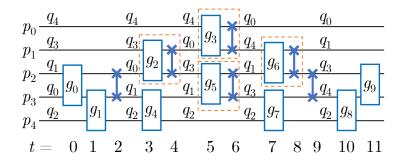

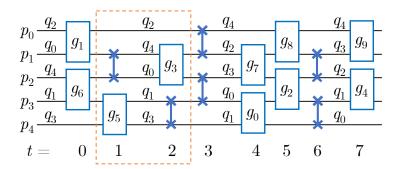

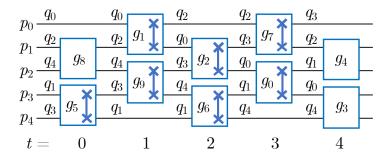

Gate scheduling determines the spacetime coordinates  $(t_j, x_j)$  for each gate, indicating when and where gates are applied. Single-qubit gates are assigned to a physical qubit, while two-qubit gates are assigned to an edge in the coupling graph. SWAP gates are strategically placed to ensure all two-qubit gates are executable. Since only SWAP gates are inserted and all the input gates are contained in the scheduled gate list, the functionality of input circuit remains unchanged after the layout synthesis process. An example of valid, though not necessarily optimal, gate scheduling is shown in Figure 1.8b. Time coordinates for all gates are indicated at the bottom, with space coordinates derived from the mapping, e.g.,  $x_1 = p_1$ ,  $x_2 = (p_3, p_1)$ , and so forth. The three CNOTs  $\tilde{g}_{11}$ ,  $\tilde{g}_{12}$ , and  $\tilde{g}_{13}$  perform a SWAP operation, adjusting the qubit mapping to enable the execution of subsequent gates like  $\tilde{g}_{14}$  and  $\tilde{g}_{18}$ . (We use tilde to denote that a gate is scheduled.)

Below, we provide a formal definition of layout synthesis for static quantum architectures.

**Input** A coupling graph G = (P, E) and a list of quantum gates  $g_1...g_M$  acting on program qubit set Q. All the input gates are in the native gate set of the architecture. Program qubits are less or equal than physical qubits, i.e.,  $|Q| \leq |P|$ .