# A Single-Phase PFC Rectifier With Wide Output Voltage and Low Frequency Ripple Power Decoupling

Yonglu Liu, Student Member, IEEE, Yao Sun, Member, IEEE, Mei Su, Min Zhou, Qi Zhu, and Xing Li

*Abstract*<sup>4</sup>—This paper proposes a single-phase PFC rectifier to achieve high power factor, wide output voltage range, and ripple power decoupling without using electrolytic capacitors. It consists of two parts: power factor correction (PFC) circuit and output voltage regulation circuit. The load side is involved in both parts, which is different from the regular two-stage conversion structure. The proposed rectifier can be directly applied to low voltage cases due to the wide output voltage range. And the decoupling capacitor voltage stress. Besides, the low frequency ripple power buffer is implemented without a dedicated power-buffering controller. This paper firstly introduces the circuit structure, operation principles, and control method. Then, the system design consideration is given. Finally, the effectiveness of the proposed topology is verified by the simulations and experimental results.

*Index Terms*—Active power decoupling, closed-loop control, low frequency ripple power, PFC, wide output voltage.

### I. INTRODUCTION

The grid-connected current in single-phase power supplies is mandatory to be sinusoidal waveform and high power factor (PF) to achieve high conversion efficiency and meet harmonic standards like IEC 61000-3-2 [1]. The simplest PFC converters are composed of a diode rectifier and a dc/dc circuit [2, 3], and used in various applications such as light-emitting diode (LED) drivers [4], electric vehicle chargers [5], and the electronic ballast [6].

However, the inherent ripple power at twice the line frequency is injected into the load side when doing ac-dc power conversion, which causes a low frequency output voltage ripple. That degrades the system performances, for example, generating low-frequency flicker of LED [4, 7, 8] and causing overheating of the battery [9, 10]. Usually large electrolytic capacitors are used to restrict the ripple within allowable limit, which is simple and easy to implement. However, that is adverse to reliability and power density [11, 12]. For examples,

the relative low lifetime of electrolytic capacitors (<20,000 hours [13]) cannot match with the long lifetime (80,000–100,000 hours [14]) of LED devices.

1

Alternatively, active power decoupling method is an effective approach to cope with the low frequency ripple power [15-17]. Its basic idea is to divert the low frequency ripple power into a small capacitor, which allows a large voltage fluctuation, with employing the decoupling circuit. Therefore, the bulky electrolytic capacitor can be replaced with a small film or ceramic capacitor. Originally, the simple dc/dc circuit plays the role of the decoupling circuit. They are merged into the original converter in series [18, 19] or parallel [20-22]. This kind of decoupling concept is easy to implement because the decoupling circuit and original circuit work independently. However, usually a lot of active and passive components are involved. To reduce cost and volume, the integrated decoupling circuit topologies, in which active switches and/or passive components are shared between the decoupling circuit and original circuit, seem more popular [23-29].

Those two decoupling concepts are also applied for PFC rectifiers [30-36]. In [30-32] a buck-boost dc/dc converter is paralleled with the load to buffer the low frequency ripple power. Then, the flicker-free electrolytic capacitor-less LED driver is achieved. And in [31] the decoupling capacitor voltage also serves as a high voltage dc bus of a rear inverter. By combining the three-terminal cell with a diode rectifier in different ways, two kinds of PFC rectifier with power decoupling capability are obtained [33, 34]. The three-terminal cell consists of one capacitor, one diode, two switches, and an inductor. According to the location of the inductor, they can be respectively viewed as a buck rectifier [33] and a buck-boost rectifier [34]. In both of them the PFC circuit and the decoupling circuit are merged, which improves the component usage and makes the converter compact and cost-effective. However, the decoupling capacitor voltage is high (greater than the peak grid voltage in [33] and greater than the sum of the peak grid voltage and output voltage in [34]). Moreover, a relative large input filter may be required due to discontinuous current before the diode rectifier. In [30-34] only one decoupling capacitor is used to buffer the low frequency ripple power. While in [35] and [36] two decoupling capacitors are used and they also play the role of the output filter. In [35] only the lower capacitor is involved to achieve PFC and the power can only transferred from the lower capacitor to the upper one. So the ripple power cannot be decoupled completely and a 21.5% current ripple still exists. The proposed circuit in [36] is

<sup>&</sup>lt;sup>1</sup>Manuscript received December 20, 2016; revised May 15, 2017; accepted July 21, 2017. This work was supported in part by the National Natural Science Foundation of China under Grants 51677195 and 61622311, in part by Natural Science Foundation of Hunan Province of China under Grant 2016JJ1019, and in part by Hunan Provincial Innovation Foundation for Postgraduate. Corresponding Author: Yao Sun.

Yonglu Liu, Yao Sun, Mei Su, Min Zhou, and Qi Zhu are with are with the School of Information Science and Engineering, Central South University, Changsha 410083, China (e-mail: liuyonglu@csu.edu.cn; yaosuncsu@gmail.com; sumeicsu@mail.csu.edu.cn; minzhou@csu.edu.cn, csu\_zhuqi@163.com).

X. Li is with the College of Electrical and Information Engineering, Hunan University, Changsha 410082, China (e-mail: lxhnu@hnu.edu.cn).

obtained by replacing the dc-link capacitor in the boost PFC rectifier with a symmetrical half-bridge circuit. As the power can flow between the two capacitors bi-directionally, the complete power decoupling is fulfilled. However, the proposed circuit is not suitable for low voltage applications. One reason is the boost PFC rectifier can only output a high dc voltage. Another reason is the required decoupling capacitor voltage is relatively large to guarantee the decoupling capacitor voltage is not beyond the dc voltage.

To achieve wide output voltage and low decoupling capacitor voltage stress, a new type of PFC rectifier is proposed in this paper. It consists of a classic boost PFC circuit and an output voltage regulation circuit. As the decoupling capacitor is in series with the dc bus the proposed circuit shows a series power buffer structure, like the topologies proposed in [33] and [34]. But the constraint on the decoupling capacitor voltage is weaker and the minimum decoupling capacitor voltage can be less than the peak grid voltage. In the adopted closed-control strategy, the output voltage is regulated by controlling the output voltage regulation circuit, and the PFC and the averaged decoupling capacitor voltage are in the charge of the PFC circuit. Besides, the PFC control and the output voltage regulation are independent. That control idea achieves a fast output voltage regulation as well as a high power factor [37]. In addition, the low frequency ripple power buffer is implemented without a dedicated power-buffering controller.

The rest of the paper is arranged as follows: Section II introduces the topology of the proposed converter. Section III presents the operation principles and the controller design. Section IV gives the design consideration. Simulations and experimental results are provided in Section V. Finally, Section VI gives the conclusion.

#### II. PROPOSED CIRCUIT AND OPERATION STATES

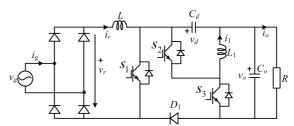

Fig. 1 outlines the proposed circuit topology composed of a boost PFC circuit (consisting of the diode rectifier, inductor L, switch  $S_1$ , and diode  $D_1$ ) and an output voltage regulation circuit. The output voltage regulation circuit includes switches  $S_2$  and  $S_3$ , film capacitors  $C_d$  and  $C_o$ , and inductor  $L_1$ .  $C_d$  is series with the dc bus to buffer the low frequency ripple power and  $C_o$  is to filter high frequency switching harmonics.  $S_1$  and  $S_2$  work without interference, and  $S_2$  and  $S_3$  work complementarily.

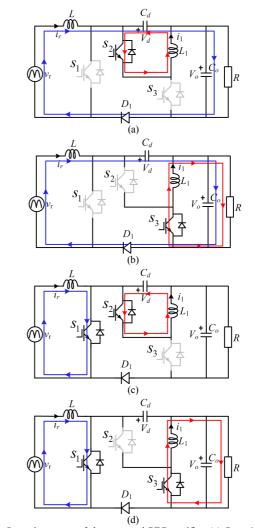

There are four switching states, as shown in Fig. 2. And  $v_r$  represents the rectified output voltage. When the switch  $S_1$  is turned off (states 1 and 2), the current  $i_r$  flows through the decoupling capacitor  $C_d$  as well as the load. That means part of the energy in the grid is directly transferred to the load and the rest into  $C_d$ . When the switch  $S_1$  is turned on (states 3 and 4), the current  $i_r$  is bypassed, and the diode  $D_1$  is reverse-biased to avoid the short circuit. As to the output voltage regulation circuit, when the switch  $S_2$  is turned on (states 1 and 3), the current  $i_1$  flows through the decoupling capacitor  $C_d$ . When switch  $S_2$  is turned off (states 2 and 4), the current  $i_1$  flows through the load. The whole circuit is something like a Sepic PFC circuit. The output voltage can be wide and its polarity is positive.

2

Fig. 1. Proposed circuit topology with wide output voltage and power decoupling capability.

Fig. 2. Operating states of the proposed PFC rectifier. (a) State 1 ( $S_1$ =OFF,  $S_2$ =ON,  $S_3$ =OFF). (b) State 2 ( $S_1$ =OFF,  $S_2$ =OFF,  $S_3$ =ON). (c) State 3 ( $S_1$ =ON,  $S_2$ =ON,  $S_3$ =OFF). (d) State 4 ( $S_1$ =ON,  $S_2$ =OFF,  $S_3$ =ON).

#### III. CIRCUIT ANALYSIS AND CONTROLLER DESIGN

This section is to introduce the circuit analysis and the controller design. Assumes that the converter operates in a continuous current mode (CCM) in both input and output inductors, the grid voltage is pure sinusoidal, all the components are ideal and lossless, and the switching voltage ripples are negligible during the switching period  $T_s$ .

# A. Modeling and Analysis

0885-8993 (c) 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

According to the Fig. 2, the state space average model is formulated as follows:

$$L\frac{di_r}{dt} = v_r - v_d - v_o + d_1\left(v_d + v_o\right)$$

(1)

$$C_d \frac{dv_d}{dt} = d_1 i_r - d_2 i_1 \tag{2}$$

$$L_1 \frac{di_1}{dt} = d_2 \left( v_d + v_o \right) - v_o \tag{3}$$

$$C_{o}\frac{dv_{o}}{dt} = d_{1}\dot{i}_{r} + d_{2}\dot{i}_{1} - i_{o}$$

(4)

where  $d_1$  and  $d_2$  represent the duty cycles of switches  $S_1$  and  $S_2$  and

$$d_1 + d_1 = 1$$

$d_2 + d_2 = 1$

Assume that the steady-state rectified output voltage  $v_r$  and the inductor current  $i_r$  are:

$$v_r = V \left| \cos(\omega t) \right| \tag{5}$$

$$i_{x} = I \left| \cos(\omega t) \right| \tag{6}$$

where V and I are the peak values of  $v_r$  and  $i_r$ ; and  $\omega$  is the angular frequency of the grid voltage. According to (1) and (6), the steady-state expression for  $d_1$

$$d_1 = \frac{1}{v_d + v_o} [v_d + v_o - v_r - \operatorname{sgn}(\cos(\omega t)) \cdot \omega L \sin(\omega t)]$$

(7)

where sgn() is the sign function. Generally, the last term on the right side of (7) is so small that it can be ignored [32, 38]. Then (7) is simplified to

$$d_1 = 1 - \frac{v_r}{v_d + v_o} \tag{8}$$

Similarly, according to (3) the steady-state expression for  $d_2$  is obtained as follows

$$d_2 = \frac{v_o}{v_o + v_d} \tag{9}$$

According to (5), (8) and (9), the relation between  $v_o$  and  $v_r$  is expressed as

$$v_o = \frac{d_2}{d_1'} v_r. \tag{10}$$

In theory  $d_2 / d_1$  could be any positive value. Then the converter has a wide output voltage range.

The power at the grid side  $P_{ac}$  is given as

$$P_{ac} = v_r i_r = \underbrace{VI/2}_{P_o} + \underbrace{VI/2\cos(2\omega t)}_{\tilde{P}}.$$

(11)

where  $\tilde{p}$  is the ripple power and  $P_o$  is the load power.

Suppose that the ripple power is buffered by the capacitor  $C_d$ , and then

$$C_d \frac{dv_d}{dt} v_d = \tilde{p} \tag{12}$$

By integrating both sides of (12) with respect to time, the decoupling capacitor voltage  $v_d$  can be expressed as:

$$v_d = \sqrt{\overline{v}_d^2 + \frac{P_o \sin(2\omega t)}{\omega C_d}}$$

(13)

where  $\overline{v}_d$  is the dc component. Then, the average current flowing through the capacitor  $C_d$  is

$$i_{d} = \frac{\tilde{p}}{v_{d}} = \frac{P_{o}\cos(2\omega t)}{\sqrt{\frac{1}{v_{d}^{2}} + \frac{P_{o}\sin(2\omega t)}{\omega C}}}.$$

(14)

Subtracting (2) from (4) leads to

$$i_1 = i_o - i_d \,. \tag{15}$$

3

$i_1$  can be positive or negative. If  $v_d$  is high enough,  $i_d$  can be always less than  $i_o$ . Then,  $i_1$  will be always positive and the switch  $S_3$  can be replaced with a diode.

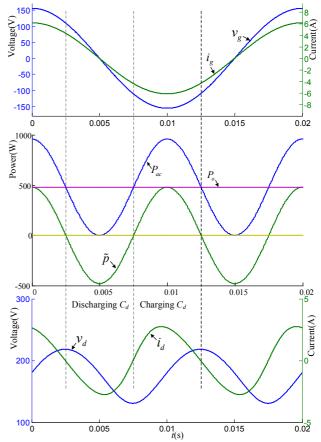

The time domain waveforms of the grid voltage/current, power distribution, voltage  $v_d$ , and average current  $i_d$  are shown in Fig. 3 using the parameters in this paper. It can be seen that the low ripple power is buffered by the capacitor  $C_d$ . Then,  $C_d$  is charging when  $\tilde{p} > 0$  and discharging when  $\tilde{p} \le 0$ .

Fig. 3. Time domain waveforms of the grid voltage  $v_g$ , grid current  $i_g$ , power distribution, voltage  $v_d$ , and current  $i_d$ .

### B. Controller Design

Two independent control loops are designed to achieve PFC, ripple power decoupling, decoupling capacitor voltage regulation, and output voltage regulation. The adopted control idea is well stated in [25, 31, 32, 34, 38, 39]. So this paper only gives a brief introduce to it.

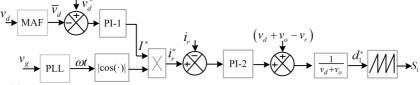

The first control loop is to control the current  $i_r$  (grid current  $i_g$ ) and the control scheme is shown in Fig. 4. It is completed by controlling the switch  $S_1$ . The phase information of the current reference is obtained by using a digital phase locked loop (PLL). In this way, the reference signal is always proportional to the grid voltage, which is to achieve the PFC. The amplitude of current reference is obtained according to the error of the averaged decoupling capacitor voltage [38, 39],

Fig. 4. Control scheme for the grid current.

Fig. 5. Control scheme for the output voltage.

$$I^{*} = (k_{p1} + \frac{k_{i1}}{s})(\overline{v}_{d}^{*} - \overline{v}_{d}).$$

(16)

where  $k_{pl}$  and  $k_{il}$  are the proportional term and the integral gain.  $\bar{v}_d$  is obtained by a moving average filter (MAF) in implementation. Finally, the current reference  $i_r^*$  is obtained as

$$i_{r}^{*} = I^{*} |\cos(\omega t)|.$$

(17)

To track  $l_r^*$ , according to (8), the control output  $d_1^*$  is designed as

$$d_1^* = \frac{(k_{p2} + \frac{\kappa_{i2}}{s})(i_i^* - i_i)}{v_d + v_o} + \frac{v_d + v_o - v_r}{v_d + v_o}$$

(18)

where  $k_{p2}$  and  $k_{i2}$  are the proportional and integral gains. The second term in (18) is a feed-forward to improve the dynamic response.

The second control loop is for output voltage regulation. The control block is shown in Fig. 5. It is achieved by controlling switches  $S_2$  and  $S_3$ . The classical dual-loop control strategy is used. The output voltage error is sent into PI-3 compensator and its output is taken as the inner loop current reference  $l_i^*$ . To track  $l_i^*$ , according to (9), the control output  $d_2^*$  is designed as

$$d_2^* = \frac{(k_{p4} + \frac{k_{i4}}{s})(i_1^* - i_1)}{v_d + v_o} + \frac{v_o}{v_d + v_o}$$

(19)

where  $k_{p4}$  and  $k_{i4}$  are the proportional and integral gains. The second term in (19) is a feed-forward

Note that once the output voltage  $v_o$  and the rectified current  $i_r$  are well regulated the ripple power will be fully absorbed by the decoupling capacitor  $C_d$ . That control idea is called automatic-power-decoupling (APD) control in [39]. Its highlight is no extra dedicated power-buffering controller is required. In addition, other controllers, such as the adaptive voltage control [31] and the dual-loop control structure with parallel-connected multi-resonant-bank-enhanced voltage loop [38], can be used to achieve a better control performance with increasing the control complexity.

## IV. SELECTION OF COMPONENTS

# A. Selection of $C_d$

Considering the limitations  $0 \le d_1$ ,  $d_2 \le 1$  the following constraint is obtained,

$$v_r \le v_d + v_o. \tag{20}$$

Solving (20) leads to

$\sqrt{\left(v_r - v_o\right)^2 - \frac{P_o \sin(2\omega t)}{\omega C_d}} \le \overline{v_d} \cdot$ (21)

4

Then, the lower limit of  $\overline{v}_d$  could be chosen as follows:

$$\overline{v}_{d} \geq \begin{cases} \sqrt{\left(V - v_{o}\right)^{2} + \frac{P}{\omega C_{d}}, v_{o} \leq V}, \\ \sqrt{\frac{P}{\omega C_{d}}}, v_{o} > V \end{cases}$$

(22)

Suppose that the permissible maximum voltage on semiconductors and passive components is  $V_{max}$ , the upper limit of  $\bar{v}_d$  is similarly obtained,

$$\bar{v}_d \le \sqrt{V_{max}^2 - \frac{P_o}{\omega C_d}} \,. \tag{23}$$

To guarantee  $\bar{v}_d$  has a solution, according to (22) and (23) the following constraint should be met.

$$V_{max} \ge \begin{cases} \sqrt{\left(V - v_o\right)^2 + \frac{2P}{\omega C_d}}, v_o \le V \\ \sqrt{\frac{2P}{\omega C_d}}, v_o > V \end{cases}$$

(24)

Then, the voltage stress of capacitor  $C_d$  is

L

$$v_{dmax} = \sqrt{\overline{v}_d^2 + \frac{P_o}{\omega C_d}} \,. \tag{25}$$

(26)

Considering  $\overline{v}_d$  being equal to its lower limit, the minimum  $C_d$  is

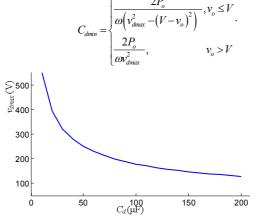

Fig. 6. Voltage stress versus the value of  $C_d$ .

In practice  $\bar{v}_d$  should be selected with a proper margin to ensure (22) is always satisfied. By adopting the parameters in this paper, the curve of the voltage stress against the capacitor  $C_d$  is shown in Fig. 6. As seen, the voltage stress decreases with the increase of the capacitance. Considering the tradeoff between the voltage stress and the capacitance,  $C_d$  is selected to

be 90 µF.

# B. Selection of L

Inductor *L* is selected according to the limit of the switching ripple. Since the switching frequency is much higher than the fundamental frequency, the average current of  $i_r$  over each switching period is assumed to be constant. Then the peak-peak switching ripple of the inductor current  $i_r$  is given as

$$\Delta i_{r} = \frac{d_{1}v_{r}}{f_{s}L} = \frac{v_{r}\left(v_{d} + v_{o}\right) - v_{r}^{2}}{f_{s}L\left(v_{d} + v_{o}\right)}$$

(27)

where  $f_s$  is the switching frequency. Then, L can be selected by

$$L \ge \frac{v_r \left(v_d + v_o\right) - v_r^2}{\Delta i_r f_s \left(v_d + v_o\right)} = \frac{v_r \left(1 - \frac{v_r}{\left(v_d + v_o\right)}\right)}{\Delta i_r f_s}.$$

(28)

In addition, L should be much smaller than  $V/(I\omega)$  to avoid a large phase shift and then degrading the PF.

## C. Selection of $L_1$

Similarly, the peak–peak switching current ripple of the inductor current  $i_1$  can be determined as

$$\Delta i_1 = \frac{v_d d_2}{f_s L_1} = \frac{v_d v_o}{f_s L_1 \left(v_d + v_o\right)}$$

(29)

The maximum value of the ripple current appears at  $v_{dmax}$ . Then,  $L_1$  can be selected according to

$$L_{1} \geq \frac{\nu_{o}}{\Delta i_{1} f_{s} \left(1 + \frac{\nu_{o}}{\nu_{dmax}}\right)}$$

(30)

From (28) and (30), the voltage  $v_d$  are expected to be small from the view of reducing the ripple currents and, hence, the size of the inductor.

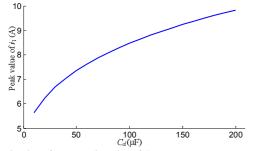

Another interesting phenomenon is that according to (15), the current rating of  $L_1$  is not only related to the load power, but also the load current  $i_o$  and the decoupling capacitor  $C_d$ . For example, the peak value of  $i_1$  increases with the increase of  $C_d$ , as shown in Fig. 7, which is plotted using the parameters in this paper. However, the slope decreases with the increase of  $C_d$ . That should be paid attention when determining the current rating.

Fig. 7. Peak value of  $i_1$  versus the value of  $C_d$ .

#### D. Selection of $C_o$

$C_o$  is only used to filter high switching harmonics. To reduce its voltage ripple,  $S_1$  is turned on during the subinterval  $(1-d_1, 1)T_s$  and  $S_2$  is turned on during the subinterval  $(0, d_2)T_s$  in each switching period. Then the peak–peak switching ripple of  $v_o$  is determined as

$$\begin{cases} \Delta v = \begin{cases} \max(0, \Delta v_1, \Delta v_2) - \min(0, \Delta v_1, \Delta v_2), d_1 + d_2 < 1\\ \max(0, \Delta v_3, \Delta v_4) - \min(0, \Delta v_3, \Delta v_4), d_1 + d_2 \ge 1 \end{cases} \\ \Delta v_1 = \frac{T_s d_2}{C_o} (i_r - i_o), \Delta v_2 = \Delta v_1 + \frac{T_s (1 - d_1 - d_2)}{C_o} (i_r + i_1 - i_o), \\ \Delta v_3 = \frac{T_s (1 - d_1)}{C_o} (i_r - i_o), \Delta v_4 = \Delta v_3 + \frac{T_s (d_1 + d_2 - 1)}{C_o} (-i_o). \end{cases}$$

(31)

5

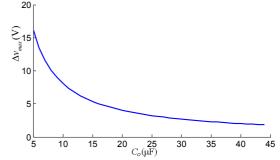

Clearly, the analytic solution of the maximum voltage ripple  $\Delta v_{max}$  is hard to obtain. Then, the numerical analysis is adopted. With using specific parameters in this study the curve of  $\Delta v_{max}$  against the capacitor  $C_o$  is shown in Fig. 8. It can be used to determine the value of  $C_o$  according to the voltage ripple limit.

Fig. 8. Maximum value of the voltage ripple  $\Delta v_{max}$  versus the value of  $C_o$ .

# E. Semiconductor Device

1

The threshold voltages across active switches and diodes are evaluated by the related maximum voltage. The averaged current and the square of the rms current over the mains period are evaluated by [40]

$$I_{avg} = \frac{1}{2\pi} \int_0^{2\pi} i_{T_awg} d\phi$$

(32)

$$r_{\rm rms}^2 = \frac{1}{2\pi} \int_0^{2\pi} i_{T\_rms}^2 d\phi$$

(33)

where

$$i_{T_{avg}} = \frac{1}{T_{s}} \int_{0}^{T_{s}} i(\varphi, t_{\mu}) dt_{\mu} = d(\varphi) i(\varphi) ,$$

$$i_{T_{avg}}^{2} = \frac{1}{T_{s}} \int_{0}^{T_{s}} i^{2}(\varphi, t_{\mu}) dt_{\mu} = d(\varphi) i^{2}(\varphi) ,$$

$\varphi = \omega t$ ,  $d(\varphi)$  is the duty ratio, and  $i(\varphi)$  is the current flowing through the switch or the diode.

For the diode rectifier, the voltage stress is the amplitude of the grid voltage (V). Diodes switch at the grid frequency to conduct current  $i_r$  and the current stresses of each diode are calculated as

$$I_{D_{r}_{-}avg} = \frac{1}{4\pi} \int_{0}^{2\pi} i_{r} d\phi = \frac{I}{\pi}$$

(34)

$$I_{D_{r}-rms}^{2} = \frac{1}{4\pi} \int_{0}^{2\pi} i_{r}^{2} d\varphi = \frac{I^{2}}{4}.$$

(35)

For the switch  $S_1$  and the diode  $D_1$ , they work complementarily. The voltage stress is both  $(v_{dmax} + v_o)$ . Both of them conduct current  $i_r$  and the current stresses are derived as

$$I_{D_{1-avg}} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{1} \dot{i}_{r} d\phi$$

=  $\frac{P_{o}}{2\pi} \int_{0}^{2\pi} \frac{1 + \cos(2\phi)}{v_{o} + \sqrt{\overline{v_{d}^{2}} + \frac{P_{o}\sin(2\phi)}{\omega C_{d}}}} d\phi$  (36)

$$I_{D_{1-}rms}^{2} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{1}\dot{l}_{r}^{2}d\phi$$

$$= \frac{P_{o}}{2\pi} \int_{0}^{2\pi} \frac{I|\cos(\phi)|(1+\cos(2\phi))}{V_{r} + \sqrt{V_{r}^{2} + \frac{P_{o}\sin(2\phi)}{V_{r}}}}d\phi$$

(37)

$$I_{S_{1}\_avg} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{1} i_{r} d\varphi$$

$$= \frac{1}{2\pi} \int_{0}^{2\pi} I \left| \cos(\varphi) \right| - \frac{P_{o} \left( 1 + \cos(2\varphi) \right)}{v_{o} + \sqrt{\overline{v}_{d}^{2}} + \frac{P_{o} \sin(2\varphi)}{\omega C_{d}}} d\varphi$$

$$I_{S_{1}\_rms}^{2} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{1} i_{r}^{2} d\varphi$$

(38)

$$=\frac{1}{2\pi}\int_{0}^{2\pi} \left(I\cos(\varphi)\right)^{2} - \frac{2P_{o}I\left|\cos(\varphi)\right|^{3}}{v_{o} + \sqrt{\overline{v}_{d}^{2}} + \frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}d\varphi$$

For switches  $S_2$  and  $S_3$ , they work complementarily. The voltage stress is both  $(v_{dmax}+v_o)$ . Both of them conduct current  $i_1$  and the current stresses are calculated as

$$I_{S_{2}\_avg} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{2} \left| \dot{i}_{1} \right| d\varphi$$

$$= \frac{1}{2\pi} \int_{0}^{2\pi} \frac{v_{o}}{v_{o} + \sqrt{\overline{v}_{d}^{2} + \frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}} \left| \dot{i}_{o} - \frac{P_{o}\cos(2\varphi)}{\sqrt{\overline{v}_{d}^{2} + \frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}} \right| d\varphi$$

$$I_{S_{2}\_rms}^{2} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{2}\dot{i}_{r}^{2} d\varphi$$

(40)

$$= \frac{1}{2\pi} \int_{0}^{2\pi} \frac{v_o}{v_o + \sqrt{\overline{v}_d^2 + \frac{P_o \sin(2\varphi)}{\omega C_d}}} \left( i_o - \frac{P_o \cos(2\varphi)}{\sqrt{\overline{v}_d^2 + \frac{P_o \sin(2\varphi)}{\omega C_d}}} \right)^2 d\varphi$$

$$(41)$$

$$I_{S_{3}\_avg} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{2}i_{1}^{1} d\psi$$

$$= \frac{1}{2\pi} \int_{0}^{2\pi} \frac{\sqrt{\overline{v_{d}}^{2} + \frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}}{v_{o} + \sqrt{\overline{v_{d}}^{2} + \frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}} \left| i_{o} - \frac{P_{o}\cos(2\varphi)}{\sqrt{\overline{v_{d}}^{2} + \frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}} \right| d\varphi$$

$$I_{S_{1}\_evgs}^{2} = \frac{1}{2\pi} \int_{0}^{2\pi} d_{2}i_{1}^{2} d\varphi$$

$$42)$$

$$=\frac{1}{2\pi}\int_{0}^{2\pi}\frac{\sqrt{\overline{v}_{d}^{2}}+\frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}{v_{o}+\sqrt{\overline{v}_{d}^{2}}+\frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}\left(i_{o}-\frac{P_{o}\cos(2\varphi)}{\sqrt{\overline{v}_{d}^{2}}+\frac{P_{o}\sin(2\varphi)}{\omega C_{d}}}\right)^{2}d\varphi$$

(43)

Using the parameters in this paper, the voltage and current stresses by calculation and simulation are summarized in Table I. As seen, the theoretical and simulation results are consistent with each other. Table I provides a basis for the selection of the semiconductor devices.

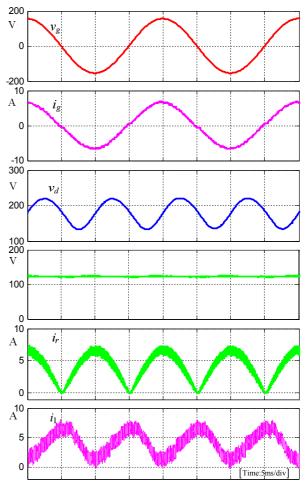

Fig. 9. Steady-state simulation waveforms of the grid voltage  $v_{g}$ , grid current  $i_{g}$ , capacitor voltage  $v_d$ , load voltage  $v_o$ , inductor current  $i_r$ , and inductor current  $i_1$ .

# V. SIMULATIONS AND EXPERIMENTAL RESULTS

# A. Simulations

In order to verify the correctness of the theoretical analysis before, simulations under ideal conditions are carried out in Matlab/Simulink environment. The circuit was designed for 110 V<sub>rms</sub> ac-input, 120 V dc-output, 30- $\Omega$  load resistance, and runs at  $f_s$ =20 kHz. *L* and *L*<sub>1</sub> are 3 mH and 1.5 mH. The values of  $C_d$  and  $C_o$  are 90 µF and 20 µF, respectively. The dc component of  $v_d$  is set to be 180 V with considering proper margin.

| VOLTAGE AND CURRENT STRESSES |                    |                     |                   |                     |                        |                     |  |  |  |  |

|------------------------------|--------------------|---------------------|-------------------|---------------------|------------------------|---------------------|--|--|--|--|

| Device                       | Voltage stress (V) |                     | Current stress    | (average/A)         | Current stress (RMS/A) |                     |  |  |  |  |

|                              | Theoretical value  | Simulation<br>value | Theoretical value | Simulation<br>value | Theoretical value      | Simulation<br>value |  |  |  |  |

| $D_r$                        | 155.56             | 156.5               | 1.96              | 1.99                | 3.08                   | 3.19                |  |  |  |  |

| $D_1$                        | 338.35             | 342                 | 1.63              | 1.64                | 2.92                   | 3.02                |  |  |  |  |

| $S_1$                        | 338.35             | 342                 | 2.29              | 2.36                | 3.24                   | 3.39                |  |  |  |  |

| $S_2$                        | 338.35             | 342                 | 1.63              | 1.64                | 2.84                   | 2.86                |  |  |  |  |

| $S_3$                        | 338.35             | 342                 | 2.37              | 2.41                | 3.42                   | 3.47                |  |  |  |  |

TABLE I Voltage and Current Stresses

6

Fig. 9 shows the steady-state simulation results. As can be observed, the input current  $i_g$  is sinusoidal and in phase with the input voltage  $v_g$ . The PF is 0.998 and the THD is 3.36%. The output voltage  $v_o$  is flat because the ripple power is diverted to the capacitor  $C_d$ . Therefore, the voltage  $v_d$  swings at twice the grid frequency. Its minimum value is about 137 V, which is less than the peak value of the gird voltage (156 V).

# B. Experiments

A prototype was built to verify the feasibility of the proposed circuit topology and control scheme. The control algorithm of the converter is realized by a universal control board which consists of a digital signal processor TMS320F28335 and a field programmable gate array FPGA EP2C8T144C8N. The circuit parameters are the same as those using in the simulation. Considering a proper margin for the overvoltage due to the turn-off, the selected insulated-gate bipolar transistors and diodes are IKW50N65H5 (650V, 50A) from INFINEON and IXYS DSEP 30-06BR (600V, 30A) from IXYS, respectively.

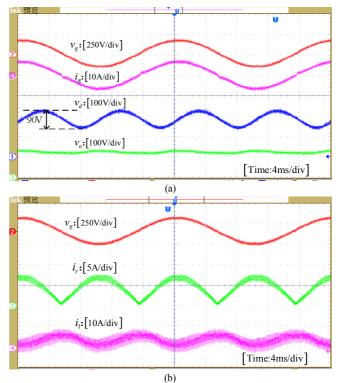

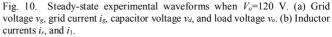

Fig. 10 shows the steady-state experimental waveforms with 120 V output voltage. As seen, the experimental results are in good agreement with the simulation results. Fig. 11 shows the experimental waveforms with 70 V output voltage. Good input and output performances are still obtained. The peak-peak value of the decoupling capacitor voltage is reduced to 35 V due to the ripple power is reduced. The percentage of the harmonics versus its dc component is shown in Fig. 12. It is clear that in both cases the rms of the second harmonic voltage (100 Hz) is small (ratio to the dc component is 3.4% (1.31%) with 120 V (70 V) output voltage). To realize the same voltage ripple level with large electrolytic capacitors, the required capacitance is 1.1 mF (2.9 mF). Therefore, the reliability and the power density are improved with the proposed circuit.

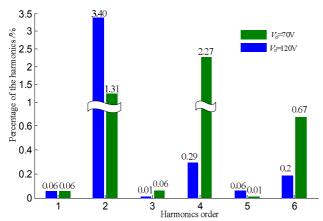

Fig. 13 shows the gate-emitter voltages of switches  $S_1$  and  $S_2$ , inductor current  $i_r$ , and inductor current  $i_1$ . At the zero crossing of the grid voltage, the duty ratio of switch  $S_1$  is close to one and at the peak value point it is about 0.5. The drive signal of  $S_1$  varies in a wide range to track the grid current reference. While, the duty ratio of  $S_2$  is always about 0.4, which is helpful to avoid narrow pulse.

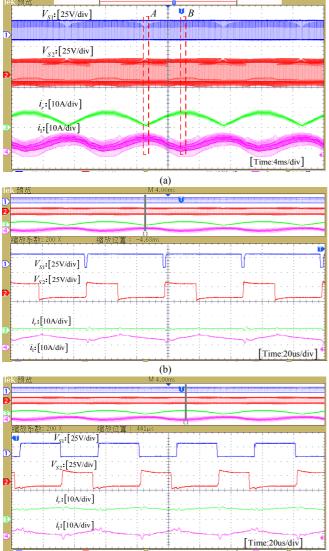

Fig. 14 shows the dynamic response of the system. In Fig. 14(a) the load voltage reference is changed from 70 V to 120 V suddenly. As seen, the output voltage tracks its reference quickly. And the fluctuation range of  $v_d$  increases accordingly due to the increased ripple power. Fig. 14(b) shows the opposite transient process.

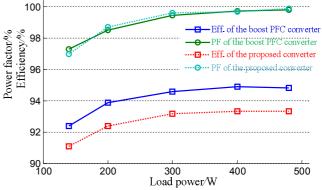

Fig. 15 shows the efficiency and the grid current PF as a function of the load power. The tests have been done with a fixed load resistance and the output voltage varies from 65 V to 120 V. For the proposed converter, the peak efficiency can be 93.32% and the PF is above 0.97 within the overall power range. However, the efficiency is lower than that of the classical boost PFC rectifier and the extra power losses are mainly introduced by the output voltage regulation circuit.

7

Fig. 11. Steady-state experimental waveforms when  $V_o$ =70 V. (a) Grid voltage  $v_g$ , grid current  $i_g$ , capacitor voltage  $v_d$ , and load voltage  $v_o$ . (b) Inductor currents  $i_r$ , and  $i_1$ .

(c)

Fig. 13. Experimental waveforms of gate-emitter voltages, inductor currents  $i_r$  and  $i_1$  when the output voltage is 120V (the load power is 480 W). (a) Waveforms of  $V_{s1}$ ,  $V_{s2}$ ,  $i_r$ , and  $i_1$ . (b) Zoom-in waveforms of point A. (c) Zoom-in waveforms of point B.

8

Fig. 14. Dynamic experimental waveforms. (a) Step-up load change from 70 V to 120 V. (b) Step-down load change from 120 V to 70 V.

Fig. 15. System efficiency and PF of the proposed circuit.

# C. Comparison

Table II gives a comparison between different PFC converters with power decoupling function. The term of "Added semiconductor devices" is a result compared with the classic boost PFC rectifier. It can be found that all the existing methods add extra semiconductor devices and an extra capacitor to buffer the low frequency ripple power. But the proposed circuit doesn't cost more compared to most other decoupling circuits. Note that the components used in the proposed circuit is identical to those in [36]. But the proposed method has a wider output voltage. On the other hand, the decoupling capacitor voltage in the proposed circuit is flexible and can be smaller than the peak grid voltage. However, in [32-34] the decoupling capacitor voltage has to be larger than the peak grid voltage. Overall, the proposed decoupling circuit can be competitive by a comprehensive consideration of cost, voltage stress, and the scope of the output voltage.

| COMPARISON BETWEEN DIFFERENT PFC POWER DECOUPLING CIRCUITS |              |                                    |                                   |            |                                                      |                         |  |  |  |

|------------------------------------------------------------|--------------|------------------------------------|-----------------------------------|------------|------------------------------------------------------|-------------------------|--|--|--|

| Decoupling<br>circuit                                      | Power rating | Decoupling<br>component<br>(Value) | Added<br>semiconductor<br>devices | Efficiency | Constraint of the<br>decoupling capacitor<br>voltage | Output voltage<br>range |  |  |  |

| Ref. [30]                                                  | 35 W         | 1 Capacitor<br>(20uF)              | 2 Mosfets                         | 87%        | $v_o < v_d < V_{max}$                                | $0 \leq v_o$            |  |  |  |

| Ref. [32]                                                  | 2 kW         | 1 Capacitor<br>(20uF)              | 3 IGBTs+ 1<br>diode               | 93%        | $ v_g  \leq v_d \leq V_{max}$                        | $0 \le v_o$             |  |  |  |

| Ref. [33]                                                  | 750 W        | 1 Capacitor<br>(100uF)             | 1 Mosfet                          | 96.4%      | $ v_g  \leq v_d \leq V_{max}$                        | $0 < v_o < V/2$         |  |  |  |

| Ref. [34]                                                  | 100 W        | 1 Capacitor<br>(15uF)              | 1 Mosfet                          | 93.5%      | $( v_g +v_o) \leq v_d \leq V_{max}$                  | $0 \leq v_o$            |  |  |  |

| Ref. [35]                                                  | 75 W         | 2 Capacitors<br>(68uF, 6.8uF))     | 1 Mosfet+1<br>Diode               | 91%        | $0 < v_d < v_o$                                      | $0 \leq v_o$            |  |  |  |

| Ref. [36]                                                  | 1 kW         | 2 Capacitors<br>(90uF)             | 2 IGBTs                           | 92.1%      | $0 < v_d < v_o/2$                                    | V <vo< td=""></vo<>     |  |  |  |

| In this paper                                              | 480 W        | 1 Capacitor<br>(90uF)              | 2 IGBTs                           | 93.3%      | $( v_g -v_o) \leq v_d \leq V_{max}$                  | $0 \le v_o$             |  |  |  |

TABLE II Arison Between Different PFC Power Decoupling Circu

#### VI. CONCLUSION

This paper proposed a single-phase PFC rectifier consisting of a PFC circuit and a buck-boost output voltage regulation circuit. Some highlights of the proposed rectifier includes: high power factor (0.99 at rated load power), wide output voltage range, flexible control due to utilizing two independent control loops, and having no electrolytic capacitors in the power stage (E-cap-less structure). In addition, the ripple power is buffered without a dedicated power-buffering controller. A laboratory prototype was built to verify the effectiveness of the proposed circuit topology. The results indicate that the proposed circuit can be a good candidate for volume-critical and lifetime-critical applications.

#### References

- Electromagnetic Compatibility (EMC), Part 3-2: Limits—Limits for Harmonic Current Emissions, Int. Std. IEC 61000-3-2, 2005.

- [2] B. Singh, B. N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, and D. P. Kothari, "A review of single-phase improved power quality AC-DC converters," *IEEE Trans. Ind. Electron.*, vol. 50, no. 5, pp. 962–981, Oct. 2003.

- [3] C. K. Tse, M. H. L. Chow and M. K. H. Cheung, "A family of PFC voltage regulator configurations with reduced redundant power processing," *IEEE Trans. Power Electron.*, vol. 16, no. 6, pp. 794-802, Nov. 2001.

- [4] B. Lehman and A. J. Wilkins, "Designing to mitigate effects of flicker in LED lighting: Reducing risks to health and safety," *IEEE Power Electronics Magazine*, vol. 1, no. 3, pp. 18–26, Sept. 2014.

- [5] M. Yilmaz and P. T. Krein, "Review of battery charger topologies, charging power levels and infrastructure for plug-in electric and hybrid vehicles," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2151–2169, May 2013.

- [6] S. Y. Hui, S. Li, X. H. Tao, W. Chen, and W. M. Ng," A novel passive offline LED driver with long lifetime," *IEEE Trans. Power Electron.*, vol. 25, no. 10, pp. 2665–2672, Oct. 2010.

- [7] W. Chen and S. Y. R. Hui, "Elimination of an electrolytic capacitor in AC/DC light-emitting diode (LED) driver with high input power factor and constant output current," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1598–1607, Mar. 2012.

[8] P. T. Krein and R. S. Balog, "Cost-effective hundred-year life for singlephase inverters and rectifiers in solar and LED lighting applications based on minimum capacitance requirements and a ripple power port," in *Proc. IEEE Appl. Power Electron. Conf.*, Washington, DC, USA, Feb. 2009, pp. 620–625.

9

- [9] H. Kim and K. G. Shin, "DESA: Dependable, efficient, scalable architecture for management of large-scale batteries," *IEEE Trans. Ind. Informat.*, vol. 8, no. 2, pp. 406–417, May 2012.

- [10] F. Lacressonniere, B. Cassoret, and J. F. Brudny, "Influence of a charging current with a sinusoidal perturbation on the performance of a lead-acid battery," in *Proc. IEE Elect. Power Appl.*, vol. 152, no. 5, pp. 1365–1370, Sep. 2005.

- [11] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: challenges design tools and opportunities", *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17-26, Jun. 2013.

- [12] H. Wang and F. Blaabjerg, "Reliability of capacitors for DC-link applications in power electronic converters—An overview," *IEEE Trans. Ind. Appl.*, vol. 50, no. 5, pp. 3569–3578, Sep./Oct. 2014.

- [13] B. Karanayil, V. Agelidis, and J. Pou, "Performance evaluation of three-phase grid-connected photovoltaic inverters using electrolytic or polypropylene film capacitors," *IEEE Trans. Sustainable Energy*, vol. 5, no. 4, pp. 1297–1306, Oct. 2014

- [14] Useful Life: Understanding LM-80, Lumen maintenance, and LED fixture lifetime. (2010). [Online]. Available: http://www.colorkinetics. com/support/whitepapers/LEDLifetime.pdf http://unruw.colorkinetics.com/decol/EDLifetime.pdf

- http://www.colorkinetics.com/Learn/docs/LEDLifetime.pdf

- [15] Y. Sun, Y. Liu, M. Su, W. Xiong, and J. Yang, "Review of active power decoupling topologies in single-phase systems," *IEEE Trans. Power Electron.*, vol.31, no.7, pp.4778-4794, Jul. 2016.

- [16] H. Hu, S. Harb, N. Kutkut, L. Batarseh, and Z. J. Shen, "A review of power decoupling techniques for microinverters with three different decoupling capacitor locations in PV systems," *IEEE Trans. Power Electron*, vol. 28, no. 6, pp. 2711–2726, Jun. 2013.

- [17] Z., Qin, Y., Tang, P. C., Loh, and F., Blaabjerg, "Benchmark of ac and dc active power decoupling circuits for second-order harmonic mitigation in kilowatt-scale single-phase inverters", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 1, pp. 15–25, Mar. 2016.

- [18] H. Wang, H. S. H. Chung, and W. Liu, "Use of a series voltage compensator for reduction of the DC-link capacitance in a capacitor-supported system," *IEEE Trans. Power Electron.*, vol. 29, no. 3, pp. 1163–1175, Mar. 2014.

- [19] H. Han, Y. Liu, Y. Sun, M. Su, and W. Xiong, "Single-phase current source converter with power decoupling capability using a

series-connected active buffer," *IET Power Electron.*, vol. 8, no. 5, pp. 700–707. May 2015.

- [20] P. T. Krein, R. S. Balog, and M. Mirjafari, "Minimum energy and capacitance requirements for single-phase inverters and rectifiers using a ripple port," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4690–4698, Nov. 2012.

- [21] X. Cao, Q. Zhong, and W. Ming, "Ripple eliminator to smooth dc-bus voltage and reduce the total capacitance required," *IEEE Trans. Power Electron.*, vol. 62, no. 4, pp. 2224–2235, Apr. 2015.

- [22] R. Wang, F. Wang, D. Boroyevich, R. Burgos, R. Lai, P. Ning, and K. Rajashekara, "A high power density single-phase PWM rectifier with active ripple energy storage," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1430–1443, May 2011.

- [23] H. Li, K. Zhang, H. Zhao, S. Fan, and J. Xiong, "Active power decoupling for high-power single-phase PWM rectifiers," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1308–1319, Mar. 2013.

- [24] B. Ge, Y. Liu. Singh, H. Abu-Rub, R. S-Balog, and F. Peng, "An active filter method to eliminate dc-side low-frequency power for single-phase quasi-z source inverter," *IEEE Trans. Ind. Electron.*, vol. 63, no. 8, pp. 4838-4848, Apr. 2016.

- [25] Y. Sun, Y. Liu, M. Su, X. Li, and J. Yang, "Active power decoupling method for single-phase current source rectifier with no additional active switches," *IEEE Trans. Power Electron.* vol. 31, no. 8, pp. 5644 - 5654, Aug. 2016.

- [26] Y. Tang and F. Blaabjerg, "A component-minimized single-phase active power decoupling circuit with reduced current stress to semiconductor switches," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 2905–2910, Jun. 2015.

- [27] W. Cai, L. Jiang, B. Liu, and C. Zou, "A power decoupling method based on four-switch three-port DC/DC/AC converter in dc microgrid," *IEEE Trans. Ind. Appl.*, vol. 51, no. 1, pp. 336–343, Jan./Feb. 2015.

- [28] I. Serban, "Power decoupling method for single-phase H-bridge inverters with no additional power electronics," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 4805–4813, Aug. 2015.

- [29] G. R. Zhu, S. C. Tan, Y. Chen, and C. K. Tse, "Mitigation of low-frequency current ripple in fuel-cell inverter systems through waveform control," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 779–792, Feb. 2013.

- [30] S. Wang, X. Ruan, K. Yao, S.-C. Tan, Y. Yang, and Z. Ye, "A flicker free electrolytic capacitor-less AC-DC led driver," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4540–4548, Nov. 2012.

[31] J. H, X. Ruan, and L. Zhang, "Adaptive voltage control for bidirectional

- [31] J. H, X. Ruan, and L. Zhang, "Adaptive voltage control for bidirectional converter in flicker-free electrolytic capacitor-less ac-dc led driver," *IEEE Trans. Ind. Electron.*, vol. 64, no. 1, pp. 320–324, Jan. 2017.

- [32] Y. Tang, D. Zhu, C. Jin, P. Wang, and F. Blaabjerg, "A three-level quasi two-stage single-phase PFC converter with flexible output voltage and improved conversion efficiency," *IEEE Trans. Power Electron.*, vol. 30,no. 2, pp. 717–726, Feb. 2015.

- [33] Y. Ohnuma and J. I. Itoh, "A novel single-phase buck PFC ac-dc converter with power decoupling capability using an active buffer," *IEEE Trans. Ind. Appl.*, vol. 50, no. 3, pp. 1905–1914, May/Jun. 2014.

- [34] S. Li, W. Qi, S.-C. Tan, and S. Y. R. Hui, "A single-stage two-switch PFC rectifier with wide output voltage range and automatic ac ripple power decoupling," *IEEE Trans. Power Electron.*, vol. 32, no. 9, pp. 6971-6982, Sep. 2017.

- [35] D. Camponogara, D. Ribeiro Vargas, M. A. Dalla Costa, J. M. Alonso, J. Garcia, and T. Marchesan, "Capacitance reduction with an optimized converter connection applied to LED drivers," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 184–192, Jan. 2015.

- [36] Y. Tang, F. Blaabjerg, P. C. Loh, C. Jin, and P. Wang, "Decoupling of fluctuating power in single-phase systems through a symmetrical half bridge circuit," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 1855–1865, Apr. 2015.

- [37] M. Mellincovsky, V. Yuhimenko, M. M. Peretz and A. Kuperman, "A novel approach to active DC link capacitance reduction for single phase power factor correction circuits," *in Proc. PEMD*, Glasgow, Scotland, 19-21 Apr., 2016.

- [38] M. Mellincovsky, V. Yuhimenko, M. M. Peretz and A. Kuperman, "Low-Frequency DC link ripple elimination in power converters with reduced capacitance by multiresonant direct voltage regulation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 2015–2023, Mar. 2017.

- [39] S. Li, S. W. Qi, S.-C. Tan, and S. Y. R. Hui, "Enhanced automatic-power-decoupling control method for single-phase ac-to-dc converters," *IEEE Trans. Power Electron.*, 2017. to be published.

[40] T. Nussbaumer, M. Baumann, and J. W. Kolar, "Comprehensive design of a three-phase three-switch buck-type PWM rectifier," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 551–562, Mar. 2007.

Yonglu Liu (S'16) was born in Chongqing, China, in 1989. He received the B.S. and M.S. degrees in electrical engineering from Central South University, Changsha, China, in 2012 and 2015, respectively. He is now pursuing Ph.D. degree in electrical engineering, Central South University, Changsha, China.

His research interests include matrix converter and AC/DC converter.

His research interests include matrix converter, micro-grid and wind energy conversion system.

**Mei Su** was born in Hunan, China, in 1967. She received the B.S. degree in Automation, in 1989, M.S. and Ph.D. degrees in electric engineering, in 1992 and 2005 respectively, all from the School of Information Science and Engineering, Central South University.

Since 2006, she has been a Professor with the School of Information Science and Engineering, Central South University. Her research interests include matrix converter, adjustable speed drives, and wind energy conversion system.

Min Zhou was born in Hunan, China, in 1993. He received the B.S. degree in automation, in 2016 from Xiangtan University, Xiangtan, China. He is currently working toward the M.S. degree in electrical engineering, Central South University, Changsha, China.

His research interests include matrix converter and ac/dc converters.

**Qi Zhu** was born in Anhui Province, China, in 1993. He received the B.S. degree in electrical engineering and automation from Central South University, Changsha, China, in 2014. He is currently working toward the Ph.D. degree in electrical engineering.

His research interests include matrix converters and wireless power transmission.

Xing Li was born in Hunan, China, in 1988. She received the B.S. degree in Automation, in 1989, M.S. and Ph.D. degrees in electric engineering, in 2009 and 2014 respectively, all from the School of Information Science and Engineering, Central South University. She is currently an Assistant Professor with the College of Electrical and Information Engineering, Hunan University, China.

Her research interests include power electronic converter and wind energy conversion system.