## UNIVERSITY OF CALIFORNIA

Los Angeles

Charge-Trap Transistors for Neuromorphic Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Xuefeng Gu

2018

© Copyright by

Xuefeng Gu

2018

#### ABSTRACT OF THE DISSERTATION

#### Charge-Trap Transistors for Neuromorphic Computing

by

### Xuefeng Gu

# Doctor of Philosophy in Electrical and Computer Engineering University of California, Los Angeles, 2018

Professor Subramanian Srikantes Iyer, Chair

As the demand for energy-efficient cognitive computing keeps increasing, the conventional von Neumann architecture becomes power/energy prohibitive. Brain-inspired, or neuromorphic computing has been extensively investigated in the past three decades because of its distributed memory/processors and massive connectivity, which promise low-power operation. One critical device in such a system is the synapse – a local memory which stores the connectivity between neurons. Many devices, such as resistive memory, phase-change memory, ferroelectric field-effect-transistor, and flash memory, have been suggested as candidates for analog synapses. In this work, the use of a CMOS-only and manufacturing-ready candidate – the charge-trap transistor (CTT), is investigated.

The analog programming characteristics of CTTs most pertinent to neuromorphic applications will first be investigated. In particular, the analog retention, the fine-tuning of individual CTTs, the spike-timing dependent plasticity, the weight-dependent plasticity, and the device variation

will be discussed. The implications learned from this part serve as the basic understanding for subsequent chapters using CTTs for neuromorphic applications.

Next, two algorithms for unsupervised learning, namely, winner-takes-all (WTA) clustering and temporal correlation detection, are investigated, using CTTs as the analog synapses. For each algorithm, the feasibility of hardware implementation using CTTs as the analog synapses is first studied and system performance evaluated using experimentally measured CTT characteristics. Experimental demonstration is then presented using custom-built CTT arrays in the 22 nm fully depleted silicon-on-insulator (SOI) technology.

Finally, the use of CTTs for analog synapses in an inference engine is considered. The finetuning of CTT weights in an array setting is first examined as it is anticipated to be different from that of discrete devices because of the half-selection and thermal disturbance by adjacent cells. The achieved standard deviation of the difference between the target and the actually programmed weight is as low as 6% of the dynamic range. The programmed CTT array is then used as a dot product engine, the key to an inference engine. Implications of the imperfect array programming in the accuracy of an inference engine are then discussed. This dissertation of Xuefeng Gu is approved.

Jason C. S. Woo

Sudhakar Pamarti

Achuta Kadambi

Janakiraman Viraraghavan

Subramanian Srikantes Iyer, Committee Chair

University of California, Los Angeles

2018

To my wife Peiyun and daughter Xi-Mu

# **Table of Contents**

| ABSTRACT OF THE DISSERTATION                                                                                                                                                                                                                                        | ii    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Acknowledgements                                                                                                                                                                                                                                                    | viii  |

| List of Figures                                                                                                                                                                                                                                                     | X     |

| List of Tables                                                                                                                                                                                                                                                      | xviii |

| VITA                                                                                                                                                                                                                                                                | xix   |

| 1. Introduction                                                                                                                                                                                                                                                     | 1     |

| 1.1 Background of neuromorphic computing                                                                                                                                                                                                                            | 1     |

| 1.2 Overview of existing efforts in neuromorphic computing                                                                                                                                                                                                          | 4     |

| 1.3 Existing analog synapses                                                                                                                                                                                                                                        | 7     |

| 1.4 CTT basics                                                                                                                                                                                                                                                      |       |

| 1.5 Value propositions of CTT: Motivation                                                                                                                                                                                                                           |       |

| 1.6 Dissertation organization                                                                                                                                                                                                                                       |       |

|                                                                                                                                                                                                                                                                     |       |

| 2. Characterization of CTT for Analog Synapses                                                                                                                                                                                                                      |       |

| <ul><li>2. Characterization of CTT for Analog Synapses</li><li>2.1 Use of CTTs as Analog Synapses</li></ul>                                                                                                                                                         |       |

|                                                                                                                                                                                                                                                                     |       |

| 2.1 Use of CTTs as Analog Synapses                                                                                                                                                                                                                                  |       |

| <ul><li>2.1 Use of CTTs as Analog Synapses</li><li>2.2 Device characteristics in 22nm fully depleted SOI</li></ul>                                                                                                                                                  |       |

| <ul> <li>2.1 Use of CTTs as Analog Synapses</li> <li>2.2 Device characteristics in 22nm fully depleted SOI</li> <li>2.2.1 Programming and erase behavior</li> </ul>                                                                                                 |       |

| <ul> <li>2.1 Use of CTTs as Analog Synapses</li> <li>2.2 Device characteristics in 22nm fully depleted SOI</li> <li>2.2.1 Programming and erase behavior</li></ul>                                                                                                  |       |

| <ul> <li>2.1 Use of CTTs as Analog Synapses</li> <li>2.2 Device characteristics in 22nm fully depleted SOI</li> <li>2.2.1 Programming and erase behavior</li> <li>2.2.2 Tunability offered by the N-well</li> <li>2.2.3 Analog retention and fine-tuning</li> </ul> |       |

| <ul> <li>2.1 Use of CTTs as Analog Synapses</li> <li>2.2 Device characteristics in 22nm fully depleted SOI</li></ul>                                                                                                                                                |       |

| <ul> <li>2.1 Use of CTTs as Analog Synapses</li> <li>2.2 Device characteristics in 22nm fully depleted SOI</li></ul>                                                                                                                                                |       |

| <ul> <li>2.1 Use of CTTs as Analog Synapses.</li> <li>2.2 Device characteristics in 22nm fully depleted SOI</li></ul>                                                                                                                                               |       |

| 3.1.2 Simulation results with CTT characteristics                |    |

|------------------------------------------------------------------|----|

| 3.1.3 Experimental demonstration                                 |    |

| 3.2 Temporal correlation detection                               |    |

| 3.2.1 Background                                                 |    |

| 3.2.2 Simulation results with CTT characteristics                | 51 |

| 3.2.3 Experimental demonstration                                 | 60 |

| 4. CTTs in An Inference Engine                                   | 64 |

| 4.1 Implementation of fully connected neural networks using CTTs | 64 |

| 4.2 Fine-tuning of CTT weights                                   | 67 |

| 4.3 Dot product engine using a CTT array                         |    |

| 4.4 Consideration of imperfections: effect of weight variation   | 75 |

| 4.5 Comparison with other analog memory devices                  |    |

| 5. Conclusions and Future Prospects                              | 82 |

| 5.1 Conclusions                                                  | 82 |

| 5.2 Future prospects                                             | 83 |

| References                                                       | 85 |

## Acknowledgements

I would first like to thank my advisor and lifetime mentor, Prof. Subramanian Iyer, for his tremendous support and guidance. This work would not have been possible without his gracious help over the years. I am grateful to the numerous discussions we had regarding research, work, and life. I am so fortunate to have this extraordinary teacher instill in me the strong work ethic, the freedom of thinking, and a way of life.

I also greatly appreciate the help and encouragement I received from my committee members, Prof. Jason Woo, Prof. Sudhakar Pamarti, Prof. Achuta Kadambi, and Prof. Janakiraman Viraraghavan. In particular, the countless discussions I had with Prof. Pamarti and Prof. Viraraghavan during the tapeout are tremendously helpful.

I have been lucky to have worked with collaborators from the industry. Their perspectives have benefited me a lot. In particular, I would like to thank Toshiaki Kirihata, Dan Berger, Norm Robson, Navneet Jain, Juhan Kim, Maciej Wiatr, and Laks Vanamurthy from GlobalFoundries, and John Barth from Invecas.

At UCLA, I enjoyed great company from all my CHIPS friends. I received a lot of help from my colleagues in the smaller NeuroCTT team: Zhe Wan, Steven Moran, Premsagar Kittur, Faraz Khan, and Jonathan Cox. Also thanks to those we have helped me one way or the other: Adeel Bajwa, Boris Vaisband, Amir Hanna, Siva Jangam, Arsalan Alam, Meng-Hsiang Liu, among many others. We are lucky to have Kyle Jung in CHIPS, who meticulously takes care of everything we need in many aspects.

I would like to thank Deeona Columbia for her great patience when helping me, and Ryo Arreola for his effort in the administrative procedures. I would also like to thank Minji Zhu for his technical support in some of the experiments.

In the seven months that I spent in IBM East Fishkill, I had the opportunity to work with and learn from many wonderful colleagues: Jang Sim, Yongchun Xin, Cheng-Yi Lin, Yang Yang, Xiang Chen, Qintao Zhang, Geng Wang, Ravikumar Ramachandran, Sami Rosenblatt, among many others. I would also like to thank Tom Koscal from GlobalFoundies for his help in setting up the characterization platform in the early stage of this project.

On the personal side, I enjoy great friendship with so many: Dingkun Ren, Li Du, Yuan Du, Yubo Wang, Ti-Wen Lin, Luyao Xu, Rui Zhu, among many others.

In the end, I would like to thank my family. My parents Xianghe and Ling supported me selflessly when I needed it the most. My wife Peiyun has always been by my side at *our* toughest times, for which I am forever grateful. We have accomplished this together. To my beloved daughter Xi-Mu, your coming to this world is the best gift I have ever received, and I cherish every single moment with you. For a while, it was your smile that kept me going.

## **List of Figures**

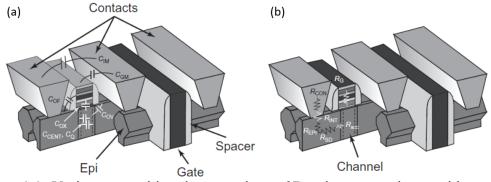

**Figure 1.1** Various parasitic elements in a 3D trigate transistor with epitaxial source/drain. Adapted from [1].

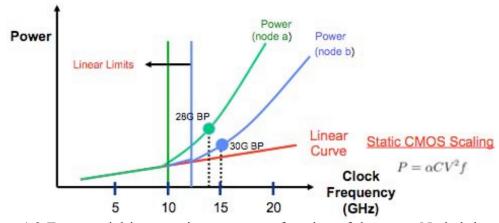

**Figure 1.2** Exponential increase in power as a function of data rate. Node b is smaller than node a. Also shown are the linear power limits of static logic circuits. Adapted from [2].

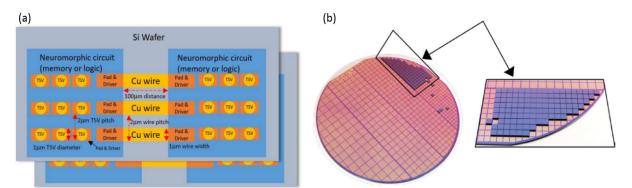

Figure 1.3 (a) The schematic of the interconnect within a 3D-WSI system. Adapted from [3]. (b)

Si-dielets bonded onto a Si-IF with 100 µm inter-dielet distance. Adapted from [4].

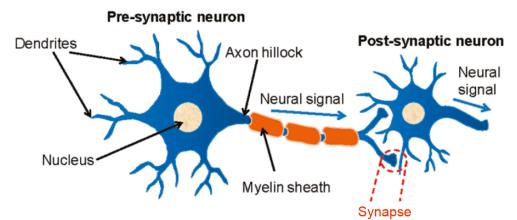

Figure 1.4 Illustration of the neuron structure and the synapse between neurons.

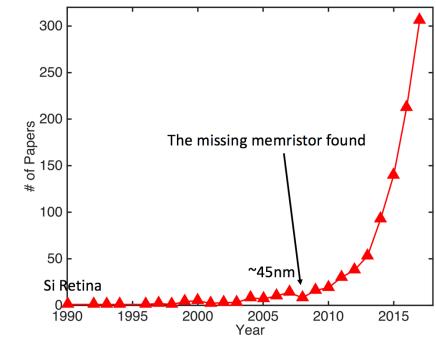

**Figure 1.5** Interest in neuromorphic or brain-inspired computing in the past three decades. Web of Science search criteria: Neuromorphic Computing OR Brain-inspired Computing.

**Figure 1.6** (a) The typical switching characteristics of a bipolar TiN/HfOx/AlOx/Pt memristor cell showing binary memristance states. (b) Different memristance states can be obtained by using different set compliance current. Adapted from [36].

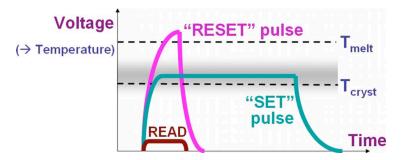

Figure 1.7 Operating mechanism of a phase change memory [37].

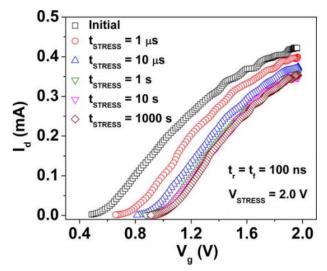

**Figure 1.8** Single-pulse transfer characteristics measured after different gate stress conditions. Adapted from [56].

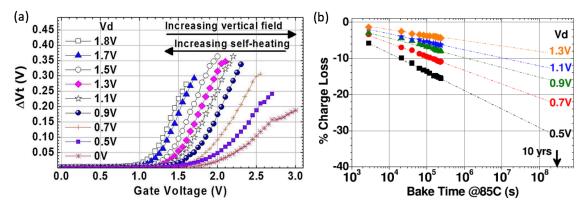

Figure 1.9 High-k charge-trapping phenomenon with a drain bias. (a) PVRS measurement for different drain biases. (b) Higher drain biases during programming not only increases  $\Delta V_T$ , but also improves retention. Adapted from [57].

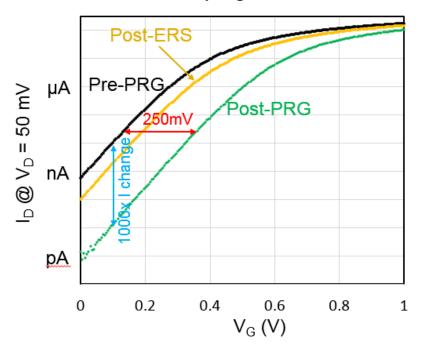

Figure 2.1 Transfer characteristics of a CTT before and after programming, and also after erase.  $\Delta V_T$  of 250 mV and a corresponding subthreshold current change of 1000× can be achieved.

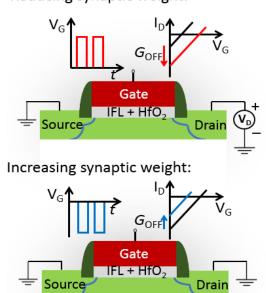

**Figure 2.2** Illustration of the use of subthreshold current as the synaptic weight and the pulsing schemes to reduce or increase the weight.

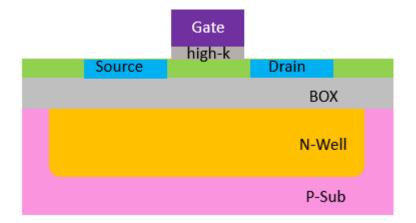

Figure 2.3 Structure of the super-low-V<sub>T</sub> CTT under characterization.

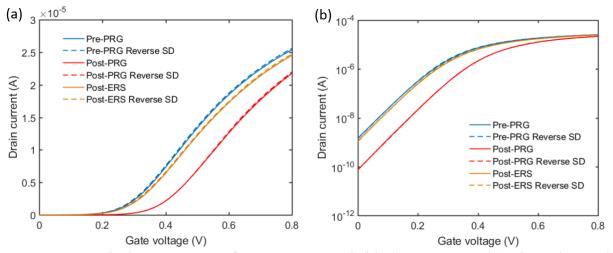

Figure 2.4 Typical I<sub>D</sub>-V<sub>G</sub> curves for unprogrammed (blue), programmed (red), and erased (yellow)

CTT. Dashed curves are measured with source and drain flipped. W/L=170nm/20nm.

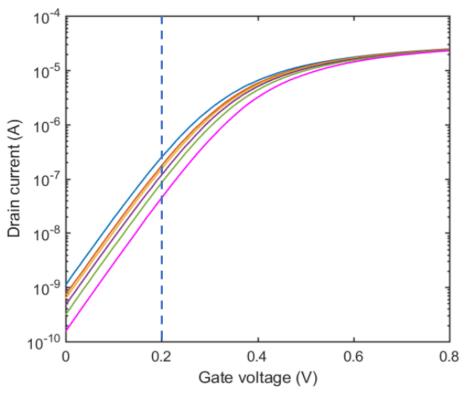

Figure 2.5 I<sub>D</sub>-V<sub>G</sub> curves of CTT at multiple intermediate states.

Figure 2.6 Subthreshold swing of CTT as the device is programmed.

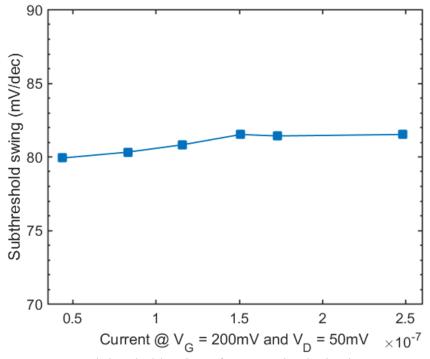

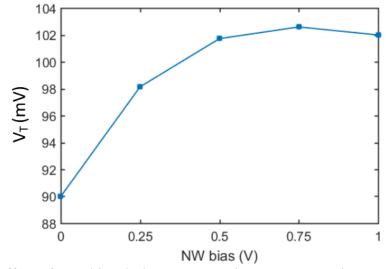

Figure 2.7 Effect of NW on device  $V_T$ . (a)  $I_D$ - $V_G$  curves for different NW biases. (b)  $\Delta V_T$  as a function of  $V_{NW}$ .

**Figure 2.8** Effect of NW bias during programming.  $\sim 13\% \Delta V_T$  improvement can be achieved with a 0.5 V NW bias.

**Figure 2.9** Analog retention characteristic for two memristors. (a) TiN/HfO<sub>x</sub>/AlO<sub>x</sub>/Pt cell [36]. (b) WO<sub>x</sub> cell [63].

**Figure 2.10** Analog retention characteristic of CTT. The CTT is programmed by 315 50- $\mu$ s gate pulses with the voltage increasing from 1 V to 2.57 V in 5 mV increment. The drain current is measured at V<sub>G</sub> = 200 mV and V<sub>D</sub> = 50 mV for one hour after each 15-pulse segment. The zoom-in of three circles is shown in Fig. 2.11.

**Figure 2.11** The current recovery for 1 hour after programming for different current levels. (a) the 1<sup>st</sup>, (b) the 11<sup>th</sup>, and (c) the 21<sup>st</sup> segment in Fig. 2.10, corresponding the different colors.

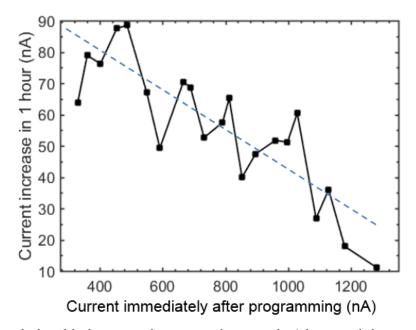

**Figure 2.12** The relationship between the current increase in 1 hour and the current immediately after programming.

**Figure 2.13** (a) The programmed current (after 1 hour) vs. the target current, with overprogramming of the CTT according to Eq. (2.1). (b) The standard deviation of the current measured in the last minute of 1 hour vs. the target current. It can be seen that the current is very stable after 1 hour.

Figure 2.14 Typical spike-timing dependent plasticity exhibited by synapses [64].

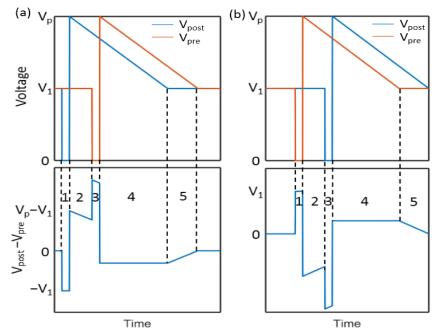

**Figure 2.15** Pulsing scheme to demonstrate STDP in CTT. (a) The connection: the pre-synaptic signal is connected to the source of the CTT, the post-synaptic signal is connected to the gate of the CTT, and the drain is biased at a constant voltage. (b) The pulsing scheme: The voltage first drops to 0 from  $V_1$  for a period of  $t_1$ , returns to  $V_p$  and then gradually decays to  $V_1$  again.

Figure 2.16 Detailed breakdown of the applied pre- and post-synaptic pulses when (a) the post-synaptic neuron fires before the pre-synaptic one ( $\Delta t = t_{pre} - t_{post} > 0$ ), and (b) the post-synaptic neuron fires after the pre-synaptic one ( $\Delta t < 0$ ).

**Figure 2.17** Boxplot of the STDP behavior when  $V_p = 2.3$  V.

**Figure 2.18** Spike-timing dependent plasticity exhibited by CTT. Solid lines are exponential curves fitted to Eq. (2.2).

**Figure 2.19** Configurations of the CTT in the (a) LTD and (b) LTP regimes. (c) Reversible and reproducible device conductance change through four cycles.

**Figure 2.20** (a) The weight-dependent plasticity when five trapping/detrapping pulses are applied in the LTD/LTP regimes, respectively. (b) Fitted curves when pulses of different widths are applied.

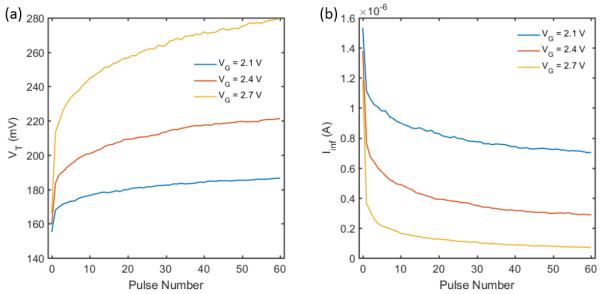

**Figure 2.21** The evolution of average (a)  $V_T$  and (b)  $I_{inf}$  with the number of programming pulses, for different gate programming voltage. Each programming pulse is 500-µs long and the total programming time is 30 ms.

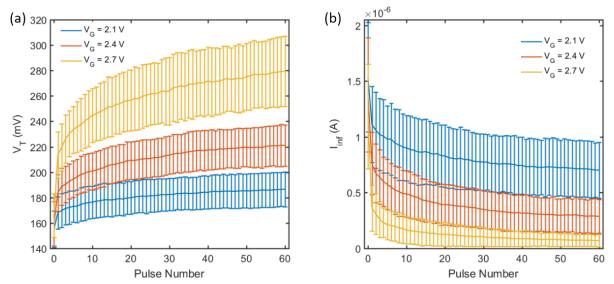

**Figure 2.22** Statistics of (a)  $V_T$  and (b)  $I_{inf}$  with the number of programming pulses, for different gate programming voltage. Each programming pulse is 500- $\mu$ s long and the total programming time is 30 ms.

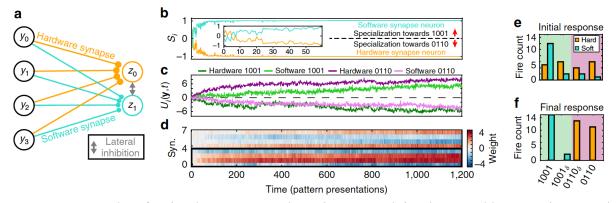

**Figure 3.1** Results of a simple  $4 \times 2$  WTA clustering network implemented by memristors and software [66]. (a) The structure of the WTA network. Four input neurons correspond to the four bits in a pattern, and two output neurons correspond to two clusters. (b) Evolution of the

"specialization" function which indicates the quality of the clustering. (c) The evolution of membrane potentials as the network is trained. (d) Evolution of the synaptic weights. (e) and (f) Clustering results before (e) and after (f) training. "δ" indicates a one-bit-flipped version of the pattern.

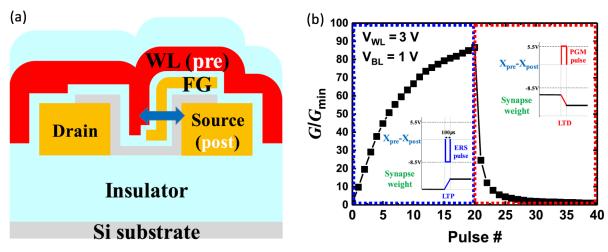

**Figure 3.2** Device structure and LTP/LTD characteristics exhibited by a TFT-like NOR flash cell [67]. (a) Schematic of the device structure and the connection of pre- and post-synaptic signals that cause a weight update. (b) LTP/LTD characteristics.

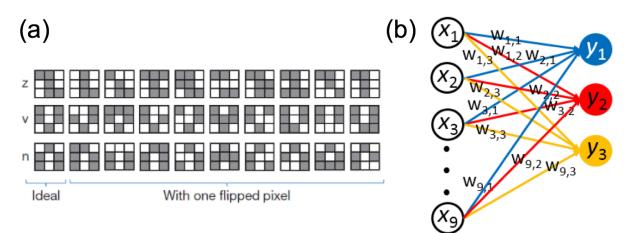

**Figure 3.3** (a) The patterns to be clustered: stylized letters z, v, n and noisy versions of them. Reproduced from [68]. (b) The 9×3 WTA network. Output neurons of different colors correspond to different categories. Adapted from [65].

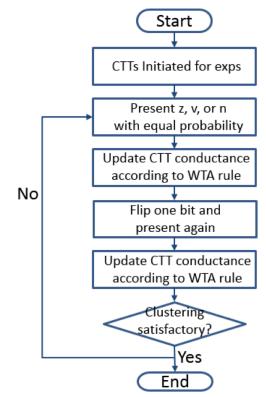

Figure 3.4 Flow chart for WTA network training.

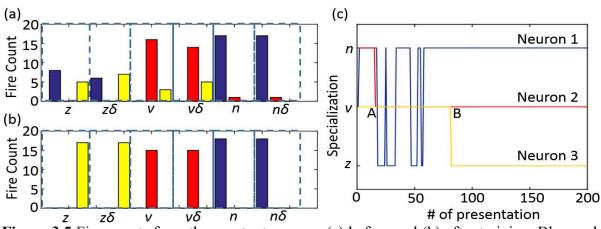

**Figure 3.5** Fire counts from three output neurons (a) before and (b) after training. Blue, red, yellow: output neurons 1, 2, and 3. "" denotes a noisy version. (c) The evolution of the output neuron specializations as the network is trained. Adapted from [65].

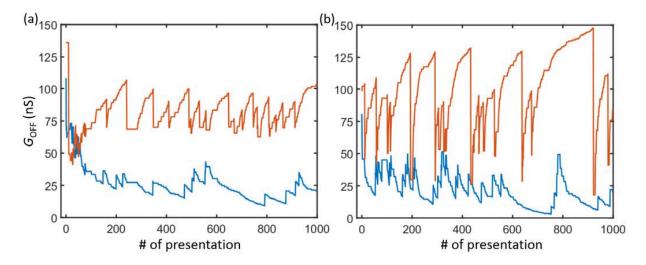

**Figure 3.6** An example of the evolution of synaptic weights  $G_{1,1}$  (blue) and  $G_{2,1}$  (red) for different programming times: (a) Two pulses are applied for LTD/LTP, and (b) Five pulses are applied for LTD/ LTP. Adapted from [65].

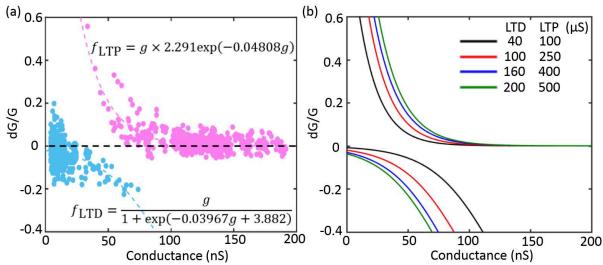

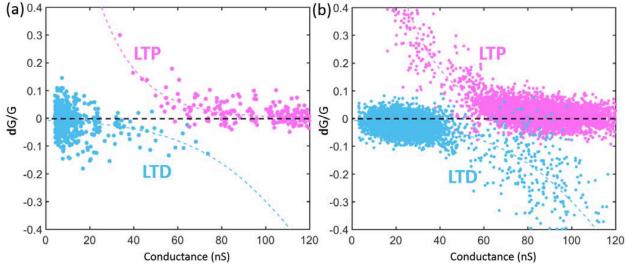

**Figure 3.7** (a) Experimentally measured and (b) Empirically determined relative conductance change as a function of the conductance itself in the LTP and LTD regimes. The algorithm converges with the variation shown in Fig. (b). Adapted from [65].

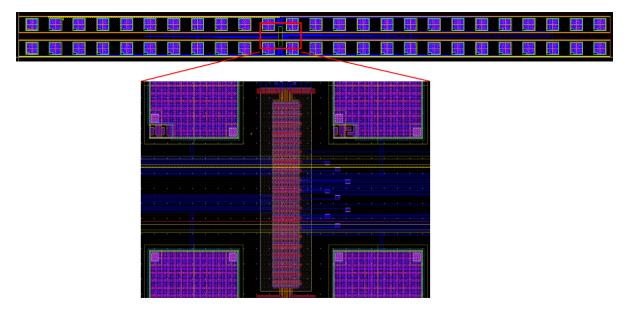

**Figure 3.8** The standalone CTT array and two rows of 25×1 scribe line monitor (SLM) pads used to directly access all terminals of each CTT individually.

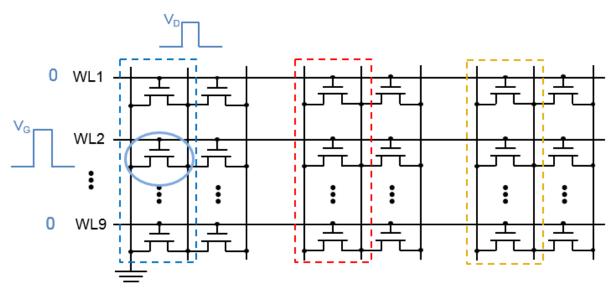

**Figure 3.9** Use of the standalone array for demonstration of the WTA network. Three columns are selected corresponding to three neurons of different colors. Also shown is the pulse configuration when a CTT (Row 2, Colum 1) is programmed.

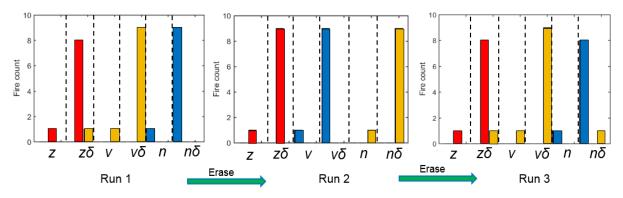

Figure 3.10 Clustering results of the three trial runs.

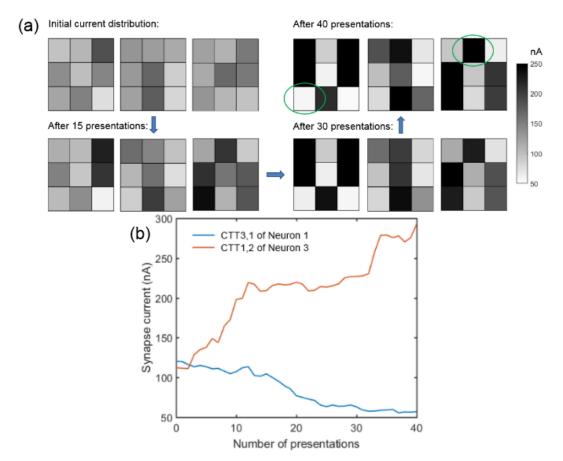

**Figure 3.11** (a) The evolution of the synaptic weights. (b) Detailed look at the weight evolution of two CTTs circled by green in Fig. (a).

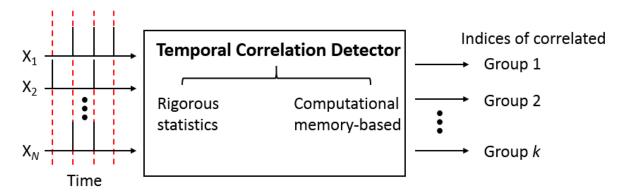

Figure 3.12 Schematic illustration of the temporal correlation detection problem.

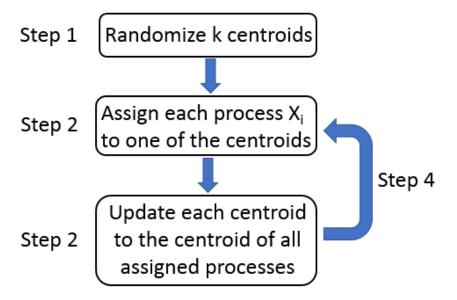

**Figure 3.13** Flow chart of a simplified *k*-means clustering algorithm. The process is usually repeated multiple times to find an optimal solution.

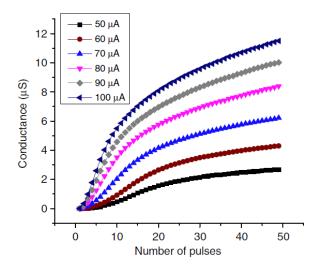

Figure 3.14 Mean and standard deviation of the PCM used in [70] when the SET current is 100  $\mu$ A.

**Figure 3.15** Amplitude- and pulse-number-dependent programming behavior exhibited by PCM used in [70]. Each point on the curves is an average from 10,000 devices.

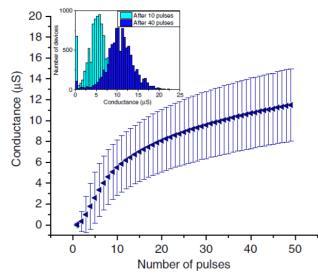

Figure 3.16 CTT conductance as a function of the number of programming pulses. Black dots: experiment; blue curve: empirically fitted curve. Here, the pulse is fixed at 20  $\mu$ s, V<sub>G</sub> = 2.6 V, and V<sub>D</sub> = 1.2 V.

**Figure 3.17** A black-and-white image used for the demonstration of temporal correlation detection with CTT. Black pixels correspond to correlated processes while white pixels correspond to uncorrelated ones.

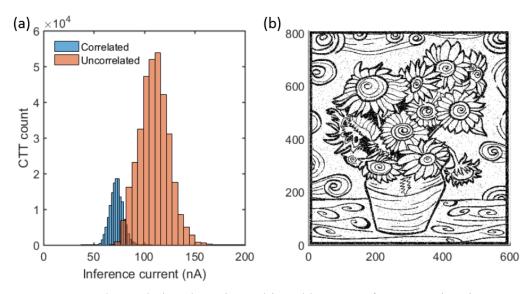

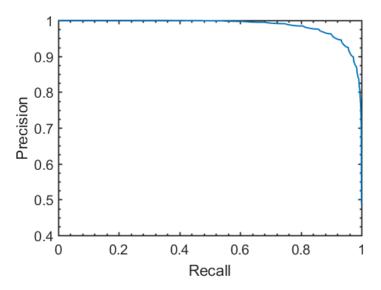

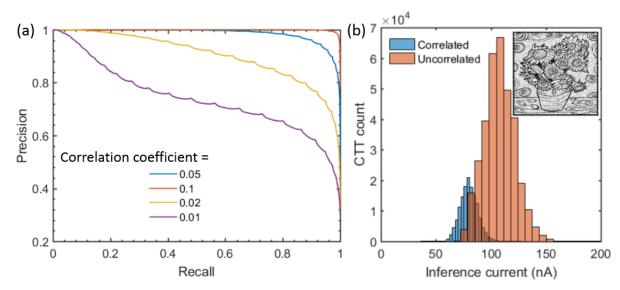

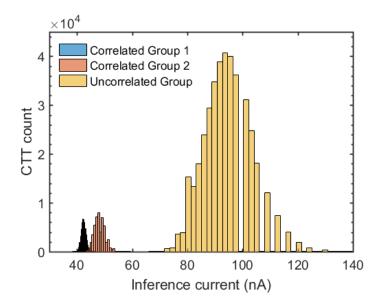

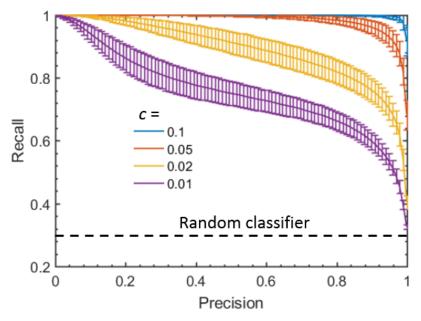

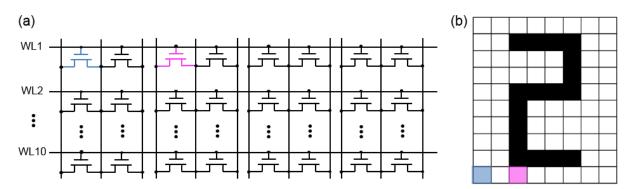

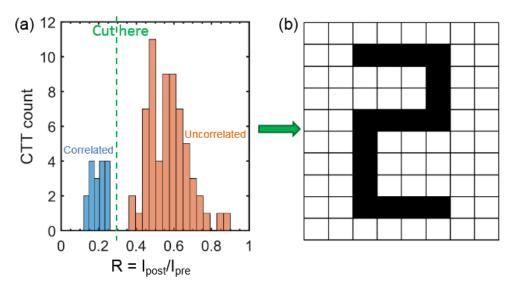

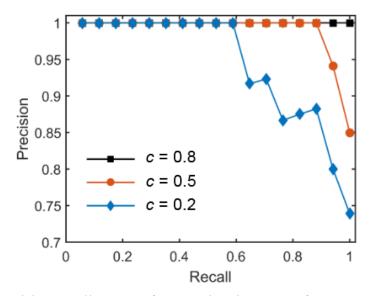

Figure 3.18 Temporal correlation detection achieved by CTT after 1,000 time instances when c = 0.05. (a) The separation of CTT inference currents between correlated and uncorrelated processes. (b) The reconstructed image when a threshold inference current of 80.5 nA is used by the classifier. Figure 3.19 Precision-recall curve of the detector in Fig. 3.18(a). Figure 3.20 (a) Precision-recall curves for different correlation coefficients: 0.1 (red), 0.05 (blue), 0.02 (yellow), and 0.01 (purple). (b) The histogram of inference currents for correlated and uncorrelated processes when c = 0.02. The inset shows the reconstructed image at a recall of 0.9.

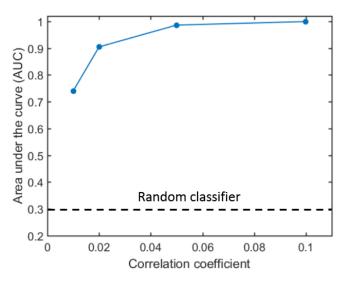

**Figure 3.21** Area under the curve (AUC) of the precision-recall curves in Fig. 3.20(a) as a function of the correlation coefficient. The dashed line is the performance of a random classifier.

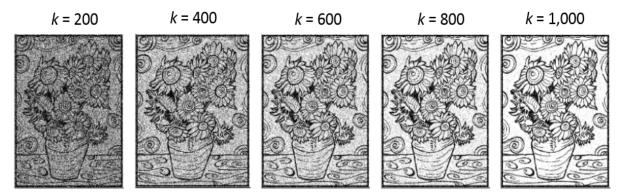

Figure 3.22 The evolution of the reconstructed image (at recall = 0.9) at different time instances k = 200, 400, 600, 800, and 1,000. Improving fidelity can be observed.

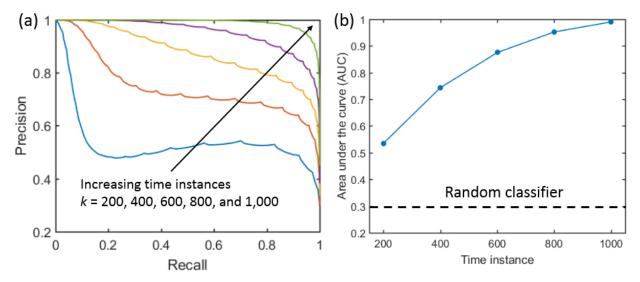

Figure 3.23 (a) The precision-recall curves at different time instances k = 200, 400, 600, 800, and 1,000. (b) AUC of the curves in Fig. (a). The dashed line is the performance of a random classifier. Here, p = 0.1 and c = 0.05.

Figure 3.24 An example of the detection of two correlated groups and an uncorrelated one. The correlation coefficient for the two correlated groups are 0.8 and 0.4, respectively. It is clear that the inference currents corresponding to the CTTs belonging to the three groups are well separated. Figure 3.25 Statistics of the precision-recall curves for different correlation coefficients c = 0.1, 0.05, 0.02, and 0.01. Solid lines are average for 1,000 runs and the error bars indicate the standard deviation.

**Figure 3.26** The configuration for the demonstration of temporal correlation detection using the standalone array. Each CTT corresponds to a binary random process. The correlated processes are indicated by black pixels in Fig. (b).

Figure 3.27 (a) The distribution of current ratio after 400 time instances when c = 0.8. (b) The reconstructed pattern using R = 0.3 as the threshold.

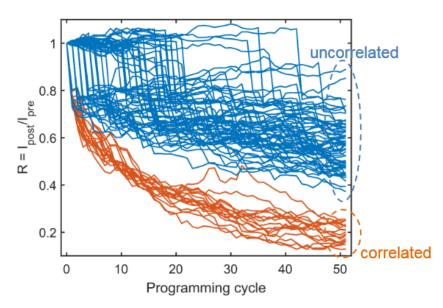

Figure 3.28 The evolution of the current ratio  $R = I_{post}/I_{pre}$  for the correlated and uncorrelated groups.

Figure 3.29 The precision-recall curves after 400 time instances, for c = 0.8, 0.5, and 0.2.

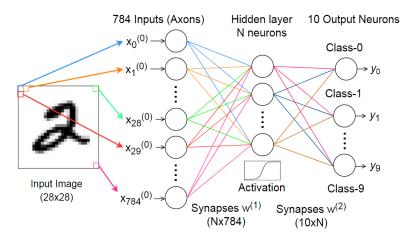

Figure 4.1 A fully connected neural network.

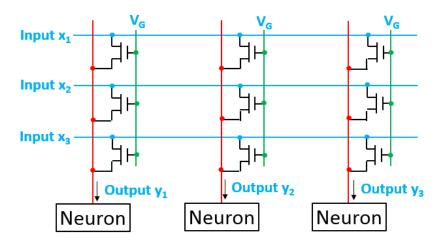

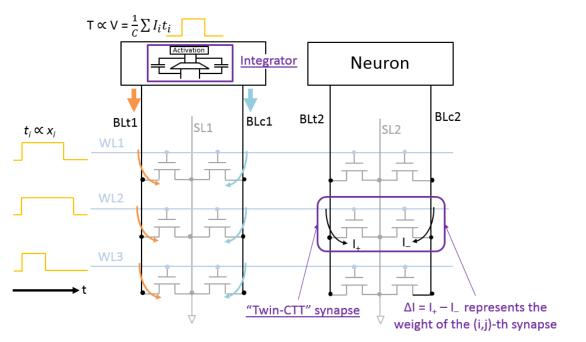

**Figure 4.2** Illustration of the hardware implementation of a fully connected neural network using the amplitude of drain voltage as inputs.

**Figure 4.3** Illustration of the hardware implementation of a fully connected neural network using the pulse width as inputs.

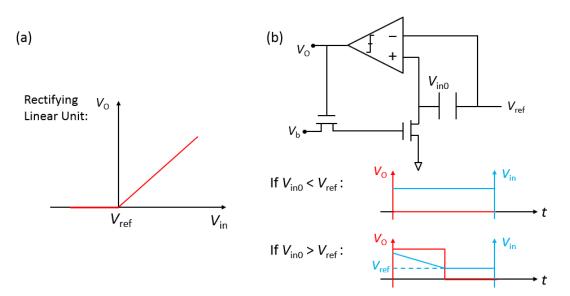

**Figure 4.4** (a) The rectifying linear unit (ReLU) as the activation function. (b) Schematic illustration of the simple implementation of ReLU.

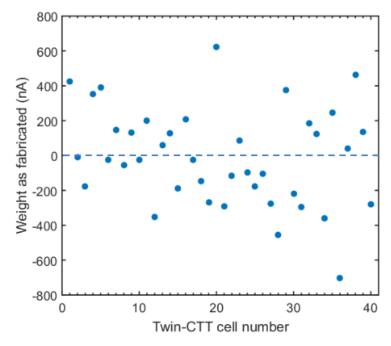

Figure 4.5 The initial weights (at  $V_{GS} = 200 \text{ mV}$  and  $V_{DS} = 50 \text{ mV}$  bias) of an as-fabricated twin-CTT array.

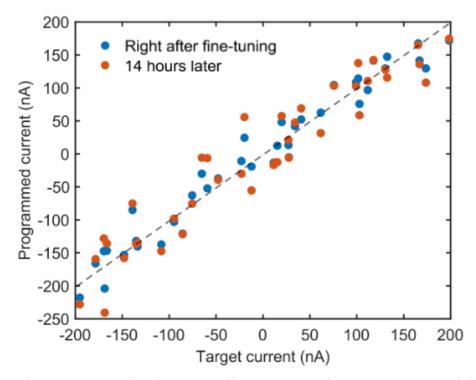

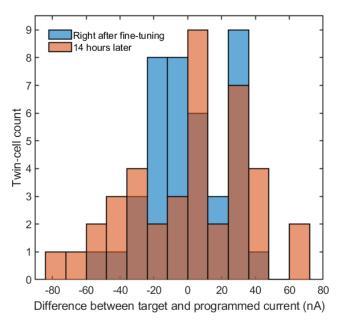

**Figure 4.6** The programmed twin-CTT cell current vs. the target current, right after 22 programming-tuning cycles (blue) and 14 hours later.

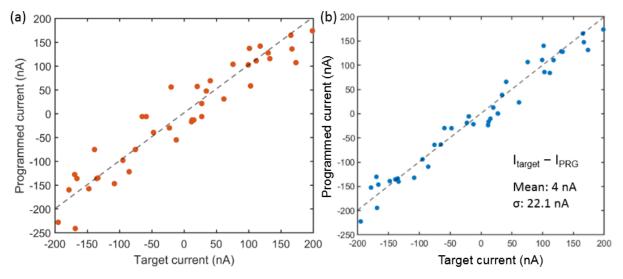

**Figure 4.7** The histogram of the difference between the programmed current and target current, right after fine-tuning and 14 hours later.

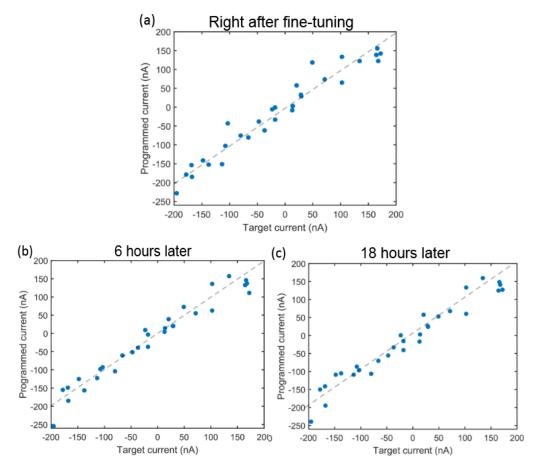

**Figure 4.8** The programmed vs. target current, (a) 14 hours after fine-tuning, and (b) after applying 8 extra programming pulses after the 14 hours.

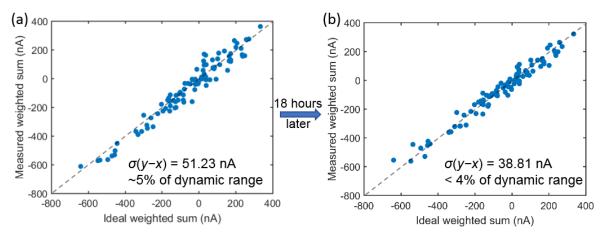

**Figure 4.9** The programmed vs. target current with CTT over-programming, (a) right after finetuning, (b) 6 hours after fine-tuning, and (c) 18 hours after fine-tuning.

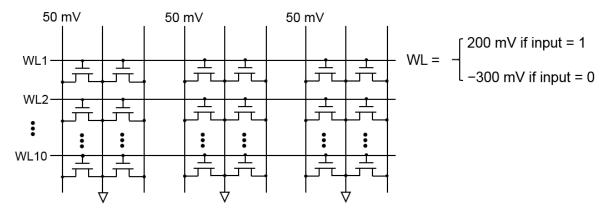

Figure 4.10 The configuration to measure column currents.  $V_G = 200 \text{ mV}$  is applied when input is 1 and  $V_G = -300 \text{ mV}$  when the input is 0.

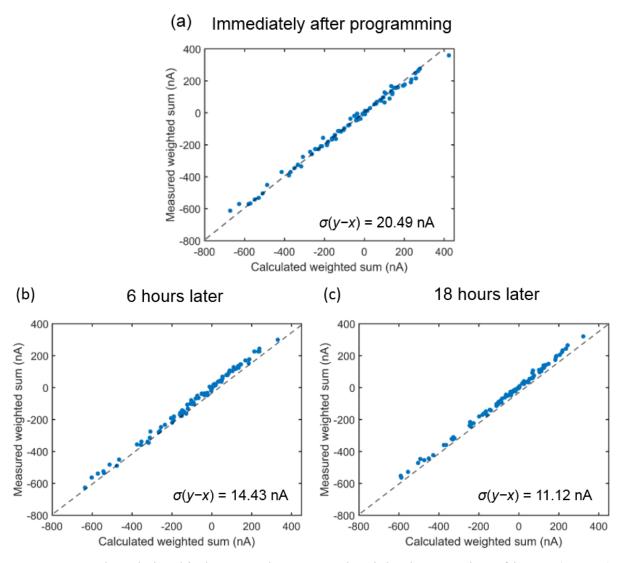

**Figure 4.11** The relationship between the measured weighted summation of inputs (current) and the ideal one.

**Figure 4.12** The relationship between the measured weighted summation of inputs (current) and the calculated one (using individual CTT currents). (a) Immediately after fine-tuning, (b) 6 hours later, and (c) 18 hours later.

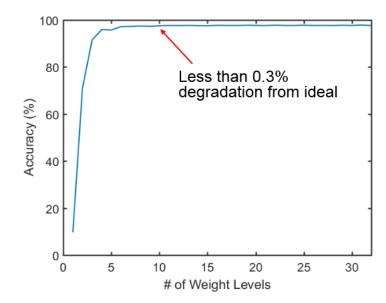

Figure 4.13 The relationship between the classification accuracy and the number of discrete weight levels.

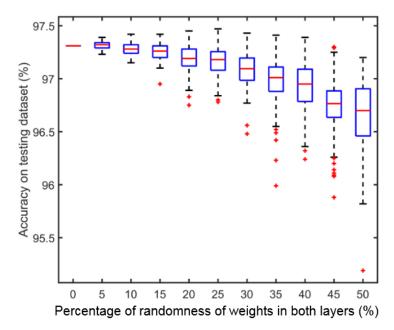

Figure 4.14 The degradation of MNIST classification accuracy as the variation in weights increases.

Figure 4.15 The structure of the GoogLeNet with the last fully connected layer highlighted [73].

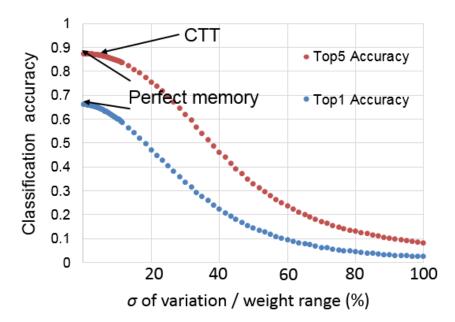

**Figure 4.16** The degradation of the Top 5 and Top 1 accuracy as the variation in the weights increases.

## **List of Tables**

**Table 1.1** A summary of important parameters of some existing neuromorphic systems. Adapted from [18].

**Table 1.2** Examples of material systems used for resistive and phase-change memory. Adapted

with modification from [44].

Table 1.3 A summary of prototype CTT-based multi-time programmable memory (MTPM).

Adapted from [60].

**Table 2.1** Parameters from the fitted Equation (2.2).

Table 4.1 Summary of the fine-tuning (with CTT over-programming) statistics of 30 twin-CTT cells.

**Table 4.2** Summary of the programming accuracy of the CTT, eFlash, and memristor.

**Table 4.3** Summary of the energy efficiency of the CTTs and other analog memory devices.

# VITA

| September 2007 – June 2011 Bachelor of Engineering, Southeast Universit | September 2007 – June 2011 | Bachelor of Engineering, Southeast University |

|-------------------------------------------------------------------------|----------------------------|-----------------------------------------------|

|-------------------------------------------------------------------------|----------------------------|-----------------------------------------------|

- September 2011 March 2013 Master of Science, University of California, Los Angeles

- May 2016 December 2016 IBM Systems, Hopewell Junction, NY

•

March 2013 – December 2018 Ph.D., University of California, Los Angeles

## 1.1 Background of neuromorphic computing

Over the past four decades, the size of transistors has been scaled by over three orders of magnitude. This is mainly fueled by the need to reduce cost. Interestingly, the scaling of transistors has also been the driving force of the ever-increasing system performance and functionality. However, as the transistor size has been pushed close to the manufacturing limit (production of 7 nm technology has begun by TSMC and Samsung as of the writing of this dissertation), several key challenges present themselves. First, from the device perspective, the parasitic capacitance and resistance has increased dramatically due to the ever-shrinking feature size (Fig. 1.1). In fact, some argue that the parasitic elements might be the most critical challenge for sub-10-nm nodes [1]. Second, from the system perspective, because the number of interconnects *between* chips has not scaled as much (only 3–4 times), the data-fetching between chips (say, between the CPU and the memory) using high-speed serializer-deserializer (SerDes) consumes a significant portion of the power budget and occupies a large area (Fig. 1.2). Finally, the increasing non-recurring engineering (NRE) cost has also made scaling devices alone a less attractive solution.

Figure 1.1 Various parasitic elements in a 3D trigate transistor with epitaxial source/drain. (a) Capacitance, (b) Resistance. Adapted from [1].

**Figure 1.2** Exponential increase in power as a function of data rate. Node b is smaller than node a. Also shown are the linear power limits of static logic circuits. Adapted from [2].

An architecture change has long been considered necessary to keep improving the system performance without further shrinking the transistors. For example, three-dimensional (3D) wafer-scale integration (3D-WSI) and silicon interconnect fabric (Si-IF) targeting heterogeneous integration are being actively pursued (Fig. 1.3) [2–4]. While these approaches address the interconnect issue to some degree, the fundamental problem – the need for high-speed communication between different components of a system, remains.

**Figure 1.3** (a) The schematic of the interconnect within a 3D-WSI system. Adapted from [3]. (b) Si-dielets bonded onto a Si-IF with 100  $\mu$ m inter-dielet distance. Adapted from [4].

Despite all these efforts, the state-of-the-art systems, using CPU and/or GPU, can barely compete with humans in many cognitive tasks, not to mention the tremendously more space and

power required by those systems. In this regard, the human brain is a remarkable cognitive device. While occupying a volume of only two liters and consumes merely 20 W, it performs many tasks such as image recognition and speech processing amazingly well.

Compared to the conventional von Neumann computing architecture, the main features of the human brain are its distributed memory and processor, and massive connectivity between them. In a human brain, there are  $\sim 10^{11}$  neurons (the processor) and  $\sim 10^{14}$  synapses (the connection between neurons which stores the connectivity). As shown in Fig. 1.4, each neuron receives input signals from its dendrites and sends an output signal through its axon. Between the axon of a neuron and the dendrite of the next neuron is a structure called synapse which stores the "connectivity" between the two neurons. When a neuron receives a pre-synaptic signal, its membrane potential is updated according to the synaptic strength, and when a certain threshold is reached, the neuron fires – sending a spike to the next neuron – and returns to its rest state.

**Figure 1.4** Illustration of the neuron structure and the synapse between neurons. Adapted from [42].

Unlike most computers which separate the memory from the CPU and constantly ferry data between the two, the brain stores and processes information locally, and as a result promises massively parallel processing capability with little power consumption. Therefore, brain-inspired neuromorphic computing systems are considered a strong candidate to *complement* conventional von-Neumann computers in many cognitive tasks [5-10].

## 1.2 Overview of existing efforts in neuromorphic computing

The concept of neuromorphic computing can be dated back to the 1950s and gained momentum in the 1980s when a group of researchers in Caltech began looking into the possibility of building electronic circuits to mimic how various parts of the body work [11-13]. Since then, efforts have focused on building hardware inspired by the human brain, including, but not limited to, the Neurogrid [14], the HRL SyNAPSE [15], the SpiNNaker [16, 17], and the IBM TrueNorth [9]. Table 1.1 summarizes some of the key aspects of these systems and a more comprehensive survey can be found in [18].

| System    | # of neurons | # synapses/neuron       | Synapse<br>implementation | Learning<br>rule | Power  |

|-----------|--------------|-------------------------|---------------------------|------------------|--------|

| Neurogrid | 1,048,576    | 6×10 <sup>9</sup> total | SRAM                      | None             | 2.7 W  |

| SpiNNaker | 1,000        | 1,000                   | SRAM                      | Any              | 1 W    |

| SyNAPSE   | 576          | 128                     | Memristor                 | STDP             | 130 mW |

| TrueNorth | 1,048,576    | 256                     | SRAM                      | None             | 63 mW  |

**Table 1.1** A summary of important parameters of some existing neuromorphic systems. Adapted from [18].

These systems can be categorized based on their purposes: to simulate a large-scale neuromorphic system (ultimately at the scale of the human brain), or to solve cognitive problems more efficiently with brain-inspired architecture. The first category, which Neurogrid and SpiNNaker belong to, aims at building a platform for neuroscientists to perform biological realtime simulations with much less power compared to conventional computers, understand how the brain works, and potentially build intelligent machines. For example, Neurogrid uses a few watts to simulate a million neurons in real time whereas a personal computer uses a few hundred watts to simulate 2.5 million neurons 9,000 times slower than real time [14].

What is more relevant to this dissertation is the second category, which tries to solve real-world cognitive tasks with brain-inspired neural networks. HRL SyNAPSE and IBM TrueNorth belong to this category. The HRL SyNAPSE adopts the CMOS technology to emulate all neural and synaptic computations and memristor technology for high-density analog synapse storage [15]. The IBM TrueNorth, on the other hand, exclusively relies on the CMOS technology. Built on Samsung's 28-nm technology, and fully capable of running convolutional neural networks, the chip has 5.4 billion transistors with 4096 neuro-synaptic cores interconnected via an intrachip network that integrates 1 million programmable spiking neurons and 256 million configurable synapses. Although the sizes of these systems are not comparable to human brains, it is interesting to note that they can already perform some cognitive tasks at biological real time and a much lower power compared to conventional von Neumann architectures. For example, when neurons fire on average at 20 Hz and have 128 active synapses, the total measured power of TrueNorth was 72 mW, corresponding to 26 pJ per synaptic event (considering total energy). This is 176,000 times more energy efficient compared with an optimized simulator running the exact same network on a modern general-purpose microprocessor, and 769 times more energy efficient compared with a state-of-the-art multiprocessor neuromorphic approach running a similar network [9].

Note that the IBM TrueNorth utilizes ternary synaptic weights (0 and  $\pm 1$ ) stored in SRAM. This has at least two drawbacks. First, due to the coarse precision of synaptic weights, a largerscale network is required for competitive accuracy. Second, since it requires six transistors to store one bit of information in SRAM, the synapses end up occupying ~ 30% area of the chip. These problems can be addressed by using analog memory for the synapses, as is the case in HRL SyNAPSE where memristive devices are used.

Indeed, since the publication of "*The missing memristor found*" in 2008 [19], the interest in neuromorphic, or brain-inspired computing, has skyrocketed (Fig. 1.5). A lot of research has focused on the characterization of various analog synaptic devices including resistive memory, phase-change memory, magnetic memory, ferroelectric FETs, flash memory, etc., and their applications in neuromorphic computing [20–24]. In the next Section, we will review the representative device characteristics of some of these analog memory devices, which leads to the discussion of a new device (in Sections 1.4 and 1.5) that will be studied in this dissertation: the charge-trap transistors (CTTs).

**Figure 1.5** Interest in neuromorphic or brain-inspired computing in the past three decades. Web of Science search criteria: Neuromorphic Computing OR Brain-inspired Computing.

## **1.3 Existing analog synapses**

A memristor is the fourth fundamental passive circuit element (besides the resistor, the capacitor, and the inductor) predicted by Leon Chua from symmetry arguments in 1971 [25]. The behavior of a memristor can be described with two simple equations [19]:

$$v = R(w,i)i \tag{1.1}$$

$$dw/dt = f(w,i) \tag{1.2}$$

where *w* is a set of state variables, and *f* and *R* are functions of time. Note from Eq. (1.2) that, the state variable *w* depends on the history of the current flowing through the device, making the resistance *R* also dependent on the current's history. Although such nonlinear device characteristics hold great promise to provide very valuable circuit functionalities–for example, high-density electronic resistance switches–no direct connection was found between the mathematics and the physical properties of any practical system for almost four decades. This gap was closed by a group of researchers from HP Labs in 2008 [19]. Using a simple analytical example, the authors showed that, memristance arises naturally in nanoscale systems in which solid-state electronic and ionic transport are coupled under an external bias voltage, paving the path for extensive memristor research in the past decade [26–35].

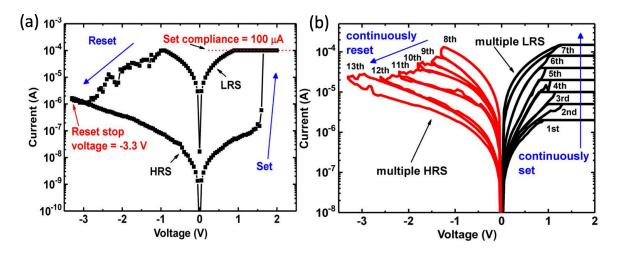

Fig. 1.6 shows the typical switching characteristics of a bipolar TiN/HfOx/AlOx/Pt memristor cell. In Fig. 1.6(a), the device first goes through a SET process where the voltage gradually increases from 0 to 2 V, with a current compliance of 100  $\mu$ A enforced. The current starts to increase very rapidly at about 1.6 V, and the device is programmed to a low resistance state. The device then goes through a RESET process (with a voltage of as high as –3.3 V) to return to its original state. The compliance current during the SET process can be utilized to control the state

the memristor is programmed to. In Fig. 1.6(b), compliance currents of 1–200  $\mu$ A are used in different SET processes, resulting in seven intermediate resistance states.

**Figure 1.6** (a) The typical switching characteristics of a bipolar TiN/HfOx/AlOx/Pt memristor cell showing binary memristance states. (b) Different memristance states can be obtained by using different set compliance current. Adapted from [36].

Phase-change memory (PCM), which exploits the resistance difference between the crystalline and amorphous phases, is another memristive device [37, 38]. As shown in Fig. 1.7, to RESET the device, a high enough current is necessary to melt the material and a rapid quenching is required to keep the material in the amorphous state; to SET the device, a lower current is used for a longer time to allow time for recrystallization [37].

Figure 1.7 Operating mechanism of a phase change memory [37].

Although resistive memristors and PCM have the potential to be used for high-density analog synapses, they have a main drawback: the added material and process complexities (Table 1.2).

This adds a significant cost especially for small-scale memory. Furthermore, the implications of adding these materials into a conventional CMOS process is yet to be fully understood.

| Synapse Type     | Material System                                            |  |

|------------------|------------------------------------------------------------|--|

|                  | TiO <sub>x</sub> /HfO <sub>x</sub> [36]                    |  |

| Pagistina mamaru | PCMO [39]                                                  |  |

| Resistive memory | TiO, [40]                                                  |  |

|                  | WO <sub>x</sub> [41]                                       |  |

| Phase-change     | Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> [Kuzum 42] |  |

| memory           | $Si_{164}Sb_{325}Te_{51.1}[43]$                            |  |

**Table 1.2** Examples of material systems used for resistive and phase-change memory. Adapted with modification from [44].

Besides two-terminal memristors, floating-gate transistors have received increasing interest recently. For example, using a commercial 180-nm NOR flash memory technology, Guo *et al.* reported a prototype inference engine which can classify a Modified National Institute of Standards and Technology (MNIST) handwritten digit in less than 1  $\mu$ s with an energy consumption of ~ 20 nJ. Both numbers are more than three orders of magnitude better than those of the 28-nm IBM TrueNorth digital chip for the same task at a similar fidelity [45]. There are also a few startup companies which are promoting floating-gate transistors for low-power artificial intelligence (AI) applications [46, 47]. However, the downsides of flash-memory-based analog synapses are also evident: additional processes are required, and the device are not logic-voltage compatible. For example, in [45], about 30% of the total active area is occupied by level shifters because of the high operating voltage.

We have in this Section briefly reviewed a few popular candidates for analog synapses. The goal is to understand the limitations of these approaches, which are summarized below:

- CMOS process compatibility: new materials and processes are most of the time inevitable, regardless of the technology.

- CMOS logic-voltage compatibility: high voltage is typically required for the flash memory.

If a CMOS-compatible (or ideally, CMOS-only) analog memory device exists, and the device can be programmed with logic-compatible voltages, these problems can all be addressed. Fortunately, such a device does exist – any logic transistor with a high-k-metal-gate in advancednode technologies will suffice. The charge-trapping phenomenon in the high-k gate dielectric can be exploited for memory applications. The transistors to be used this way are called charge-trap transistors (CTTs). In the next two Sections, we will first describe the operating mechanism of CTTs, and then discuss the value propositions of CTTs for analog synapse applications.

## 1.4 CTT basics

Around 2000s, the relentless device scaling finally led to a very thin gate oxide in transistors, resulting in unacceptably high gate leakage through SiO<sub>2</sub>. High-dielectric-constant materials, i.e. high-k materials, were therefore proposed to provide the transistors with the same ON-current while not significantly reducing the gate-oxide thickness [48–50]. An undesirable feature of these high-k dielectrics however, is that there are inherent oxygen vacancies in the material, acting as the charge-trapping centers. When devices are biased at a high gate voltage for a prolonged time, these oxygen vacancies will trap electrons in them and gradually increase the threshold voltage ( $V_T$ ) of the device (Fig. 1.8). In other words, the  $V_T$  changes with time and is unstable. This effect is traditionally known as the bias temperature instability (BTI), a nuisance that is to be eliminated for an ideal process [51–56]. Moreover, because it is a universal feature of high-k gate dielectrics, virtually all advanced-node technologies beyond 32 nm have this problem.

**Figure 1.8** Single-pulse transfer characteristics measured after different gate stress conditions. Adapted from [56].

However, it has recently been demonstrated that, the charge-trapping phenomenon by the oxygen vacancies in HfO<sub>2</sub> gate dielectric, when utilized properly, can be used as a mechanism for nonvolatile memory applications [57–60]. It is found that, if a drain bias is present when the gate pulse is being applied, the charge-trapping behavior can be stabilized. Fig. 1.9 shows the V<sub>T</sub> change in a pulsed voltage ramp sweep (PVRS) measurement for different drain biases, where 10-ms gate programming pulses with increasing amplitude are applied [57]. In Fig. 1.9(a), we can observe that the maximum  $\Delta V_T$  one can obtain first increases with an increasing V<sub>D</sub> and then decreases after a certain V<sub>D</sub> (~ 1.3 V in this case) because the device is easier to breakdown [61]. Furthermore, Fig. 1.9(b) shows the improved retention at a higher V<sub>D</sub> during programming. The extrapolated charge loss after ten years when the device is baked at 65 °C is less than 10% at a programming V<sub>D</sub> of 1.3 V, whereas it is as much as over 30% at a programming V<sub>D</sub> of 0.5 V. This behavior is drastically different from BTI, where the  $\Delta V_T$  is a few tens of mV and vanishes when the gate bias is removed. This behavior has been carefully studied and attributed to the high channel temperature during programming, which significantly reduces the capture/emission times of deep traps. After the

programming pulses are removed, the device rapidly cools down, leaving those filled deep traps a long time to de-trap, and hence resulting in a long retention time.

**Figure 1.9** High-k charge-trapping phenomenon with a drain bias. (a) PVRS measurement for different drain biases. (b) Higher drain biases during programming not only increases  $\Delta V_T$ , but also improves retention. Adapted from [57].

Taking advantage of this self-heating-enhanced charge-trapping behavior in HfO<sub>2</sub>, GlobalFoundries has recently commercialized CTTs for digital multi-time programmable memory. Table 1.3 summarizes some of the products that have been prototyped in different technology nodes [60]. Note that the CTT technology has been demonstrated in both planar and FinFET nodes, bulk and SOI substrates alike.

**Table 1.3** A summary of prototype CTT-based multi-time programmable memory (MTPM). Adapted from [60].

| Technology              | 32nm SOI                           | 22nm SOI                          | 14nm FinFET bulk               |

|-------------------------|------------------------------------|-----------------------------------|--------------------------------|

| Cell                    | $0.109\mu m^2$ with 1.2nm Gox NMOS | $0.144 \mu m^2$ with 1nm Gox NMOS | $0.1411 \mu m^2$ with FIN NMOS |

| Macro density           | 80Kb                               | 64Kb                              | 40Kb                           |

| Density/mm <sup>2</sup> | $\sim 2$ Mb/mm <sup>2</sup>        | $\sim 2.5 Mb/mm^2$                | $\sim 1.3 Mb/mm^2$             |

| Activation energy       | $\sim 1.35 eV$                     | $\sim 2.4 \mathrm{eV}$            | $\sim 1.6 eV$                  |

| Design-assist circuits  | Yes                                | No                                | Yes                            |

| Number of cells / BL    | 256                                | 256                               | 128                            |

| Sacrificial WLs and BLs | Yes                                | No                                | Yes                            |

| Redundant WLs and BLs   | Yes                                | No                                | Yes                            |

## **1.5 Value propositions of CTT: Motivation**

It should be clear by now that, the CTT is a good candidate and worth exploring for analog synapses in various neuromorphic computing systems targeting fast and low power cognitive tasks. Compared to other analog synapse alternatives, CTTs possess the following advantages:

- It is CMOS-only. Unlike resistive/phase-change RAM or flash technology, no extra materials or processes are necessary. This has an obvious advantage: the development cost of the technology is very low – any advanced-node logic transistors can be used as CTTs straight out of the fab, and existing IP designs in an older node can be easily ported to a new node.

- It is a three-terminal device, providing flexibility in the control of the device and avoiding the use of access transistors for two-terminal emerging memory devices.

- It only uses logic compatible voltage below 2.5 V. This is a significant advantage especially compared to flash-based analog synapses.

However, one thing to keep in mind is that the CTT is not a high-density memory device because a relatively wide device (>  $\sim 200$  nm) is required for efficient charge-trapping to take place. From the cost perspective, this limits the memory size to a few tens of MBs (see Rows 1–3 in Table 1.3 for examples), which is enough to implement most of the neural networks. Therefore, it is practical to build very useful hardware using CTT-based analog synapses.

## 1.6 Dissertation organization

In this Chapter, we have provided a brief overview on the background of neuromorphic computing, pointed out that there are different types of neuromorphic systems based on their purposes: to simulate the brain or to perform fast and low power cognitive tasks, and revealed that analog synapses are essential for the second-type neuromorphic system because of their capability of enabling in-memory computation and relatively high density compared to SRAM. Various analog synaptic devices, including resistive and phase-change RAM, as well as flash memory, are discussed. CTTs are then introduced for their apparent advantages of being CMOS-only and logic-voltage-compatible. The operating mechanism of CTTs, namely, the charge-trapping phenomenon

enhanced and stabilized by a drain bias during programming, is described. CTT value propositions and the motivation of this dissertation are discussed.

In Chapter 2, we will discuss the analog programming characteristics of CTTs most pertinent to neuromorphic applications. In particular, the analog retention, fine-tuning of individual CTTs, the spike-timing dependent plasticity, and the weight-dependent plasticity are discussed. Variation of CTTs is also characterized using a custom-built CTT array.

In Chapter 3, two algorithms for unsupervised learning, namely, winner-takes-all (WTA) clustering and temporal correlation detection, are investigated, using CTTs as the analog synapses. For each algorithm, the background is first reviewed, and implementations using other analog synapse alternatives are discussed. The implementation using CTTs as the analog synapses is then studied and system performance evaluated using experimentally measured CTT characteristics. Experimental demonstrations of both algorithms are then presented using custom-built CTT arrays.

In Chapter 4, the use of CTTs as analog synapses in an inference engine is studied. We first consider the configuration of using CTTs for a fully connected neural network. The fine-tuning of CTT weights in an array setting is studied since it is anticipated to be different from that of discrete, standalone devices because of the half-selection, thermal disturbance by adjacent cells, etc. The robustness of the inference engine to weight variations is also discussed. In Section 4.5, the comparison between CTT and other analog memory devices is discussed.

Finally, the dissertation is concluded with an outlook of the future of CTT-based neuromorphic systems.

## 2.1 Use of CTTs as Analog Synapses

Besides being used as a multi-time-programmable memory where only two states are utilized, CTTs hold great potential for analog memory as well. This is primarily for two reasons: 1) The amount of trapped electrons in the high-k gate dielectric can be finely modified by applying lower and shorter programming pulses (compared to digital applications); and 2) CTT-based synapses can be operated in the subthreshold region, providing a large dynamic range with a relatively small change to  $\Delta V_T$ . For example,  $\Delta V_T$  of 250 mV can be readily achieved by applying a 10-ms trapping pulse with  $V_G = 2.8V$  and  $V_D = 1.5$  V, providing a subthreshold current change of more than 1000× (Fig. 2.1).

The CTT can be programmed and erased

**Figure 2.1** Transfer characteristics of a CTT before and after programming, and also after erase.  $\Delta V_T$  of 250 mV and a corresponding subthreshold current change of 1000× can be achieved.

After being programmed, a CTT can also be erased by a negative gate-to-source and gate-todrain voltage (Fig. 2.1), although not completely. This provides an extra degree of controllability in accurate programming of the device. In addition, this ability to be erased is desired for applications such as winner-takes-all (WTA) clustering which will be discussed in Chapter 3.

As shown in Fig. 2.2, when a weight is to be decreased, trapping pulses are applied to the gate of the CTT, increasing its  $V_T$  and therefore decreasing the weight; when a weight is to be increased, de-trapping pulses are applied, reducing its  $V_T$  and therefore increasing the weight.

Reducing synaptic weight:

Figure 2.2 Illustration of the use of subthreshold current as the synaptic weight and the pulsing schemes to reduce or increase the weight.

Using the CTTs this way as an analog synapse finds various applications in neuromorphic computing. In this Chapter, we will examine the spike-timing dependent plasticity and weight-dependent plasticity, which are required characteristic for adaptive learning and WTA clustering, respectively. The application of this configuration for an inference engine will be discussed in Chapter 4.

## 2.2 Device characteristics in 22nm fully depleted SOI

In this Section, CTT behavior is characterized in the 22nm fully depleted silicon-on-insulator (22FDX) technology. Specifically, super-low- $V_T$  transistors (a standard logic device offering) are characterized. The same device is used later in the experimental demonstration of unsupervised learning as well as a dot product engine for inference engines.

The device structure is schematically depicted in Fig. 2.3, where the gate-oxide is 1.25-nmthick, SOI is 6-nm-thick, and the BOX is 20-nm-thick. One notable feature is the N-well (NW), which provides an extra degree of tunability of  $V_T$ . In practice, NW is shared by an array of devices and is contacted by a via through locally etched BOX.

Caution must be taken when programming pulses are sent from the semiconductor parameter analyzer to the device. Because the cabling has a capacitance as large as 1 nF, and the wiring resistance from the pads to the device terminal can be as large as 100  $\Omega$ , ultrashort pulses should be avoided. Here, the shortest pulse is 20-µs long, ensuring a high fidelity of the actual voltage that is applied to the device terminals.

Figure 2.3 Structure of the super-low-V<sub>T</sub> CTT under characterization.

#### 2.2.1 Programming and erase behavior

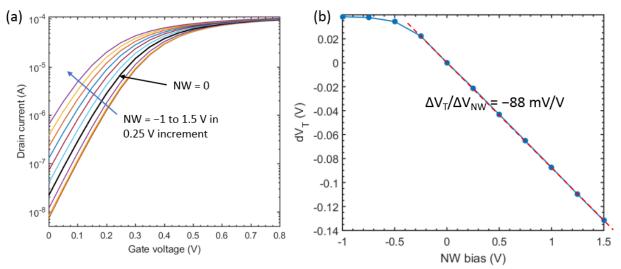

Fig. 2.4 shows the I<sub>D</sub>-V<sub>G</sub> curves of a CTT before programming, after programming, and after erase. During programming, a 10-ms, 2.6 V pulse is applied to the gate with  $V_D = 1.3$  V, resulting in 103 mV  $V_T$  shift ( $\Delta V_T$ ); during erase, a 30-ms, -2.8 V pulse is applied to the gate with both source and drain grounded. An important feature to note here is that, there is a ~10 mV  $\Delta V_T$  residual after erase. More negative  $V_G$  and longer erase time are necessary to reduce the  $V_T$  further. Measurements with source/drain reversed (dashed curves) do not show significant differences, indicating that the charge-trapping is not highly asymmetric along the channel direction.

**Figure 2.4** Typical  $I_D$ -V<sub>G</sub> curves for unprogrammed (blue), programmed (red), and erased (yellow) CTT. Dashed curves are measured with source and drain flipped. W/L=170nm/20nm.

Fig. 2.5 shows the  $I_D$ -V<sub>G</sub> curves of a CTT programmed to intermediate states. These states are achieved by applying lower and shorter gate voltage during programming. It is worth noting that, as the device is programmed, the subthreshold swing does not degrade (Fig. 2.6).

Figure 2.5 I<sub>D</sub>-V<sub>G</sub> curves of CTT at multiple intermediate states.

Figure 2.6 Subthreshold swing of CTT as the device is programmed.

### 2.2.2 Tunability offered by the N-well

As mentioned above, the super-low  $V_T$  CTT being studied here is a flip-well device, with an NW underneath the BOX. The device characteristics can be modified by the NW bias (Fig. 2.7) with a sensitivity of  $\Delta V_T / \Delta V_{NW} = -88 \text{ mV/V}$ . With regards to the application of CTT as an analog synapse, the NW bias can serve two purposes: 1) During programming, a positive bias reduces the  $V_T$  and therefore increases the channel current, improving the programming efficiency without raising the gate voltage; 2) After programming, NW bias can be used to collectively increase or decrease the synaptic weight without added complexity in the circuitry. We will focus on the first point here.

**Figure 2.7** Effect of NW on device  $V_T$ . (a)  $I_D$ - $V_G$  curves for different NW biases. (b)  $\Delta V_T$  as a function of  $V_{NW}$ .

Fig. 2.8 shows the effect of NW bias during programming. It is observed that the  $V_T$  increases more with a larger NW bias during programming (up to 12 mV, or 13%), and this improvement saturates for NW bias larger than 0.5 V.

Figure 2.8 Effect of NW bias during programming.  $\sim 13\% \Delta V_T$  improvement can be achieved with a 0.5 V NW bias.

### 2.2.3 Analog retention and fine-tuning

CTTs have been qualified as multi-time-programmable digital memory for 10 years at 105-125 °C. The relatively large V<sub>T</sub> difference (therefore current difference) is sensed by a slew sense amplifier. In the analog regime, however, the states are ideally continuous, making the quantification of retention more challenging.

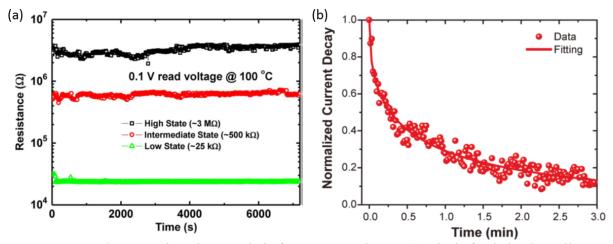

There have been a few reports on the analog retention behavior of other analog memory devices in the literature. Fig. 2.9 shows two examples of TiN/HfO<sub>x</sub>/AlO<sub>x</sub>/Pt and WO<sub>x</sub>, respectively. In Fig. 2.9(a), the device resistance can vary for more than 100% [36]; in Fig. 2.9(b), the device current decays significantly within a period of three minutes [63].

**Figure 2.9** Analog retention characteristic for two memristors. (a) TiN/HfO<sub>x</sub>/AlO<sub>x</sub>/Pt cell [36]. (b) WO<sub>x</sub> cell [63].

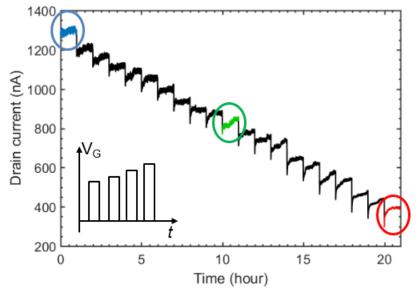

We show in Fig. 2.10 the retention of multiple analog states in CTT. Here, the device is programmed with a train of 315 50- $\mu$ s pulses. In these pulses, V<sub>G</sub> increases from 1 V to 2.57 V in 5 mV increment while V<sub>D</sub> is held at 1 V. The pulses are applied in 21 segments (each with 15 pulses) and the inference current at V<sub>G</sub> = 200 mV and V<sub>D</sub> = 50 mV is measured for one hour after each segment. Two features can be observed: First, after each segment of programming pulses, the inference current gradually increases within one hour, apparently due to de-trapping of trapped electrons; second, not all current increase resemble the shape of an exponential function, indicating that there is no single time constant.

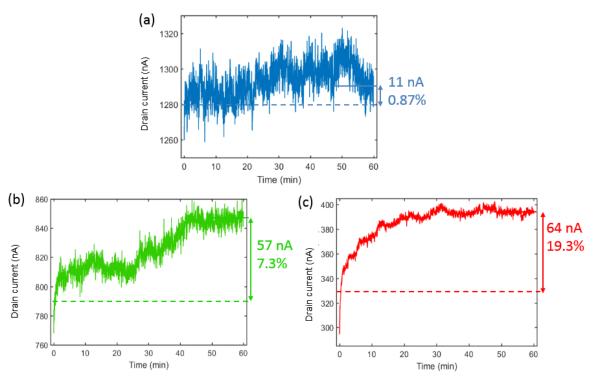

A detailed look at Fig. 2.10 reveals that, the lower current (or the higher  $V_T$ ) the CTT is programmed to, the more up-drift there is after programming. For example, when the CTT is programmed with 21 gate pulses from 1 V to 1.1 V (Fig. 2.11(a)), the current increase in one hour is only 0.87%; when the current is programmed to 330 nA using 315 gate pulses (Fig. 2.11(c)), the current increase in one hour is 64 nA, or 19.3%, corresponding to a V<sub>T</sub> recovery of approximately 7 mV. Although the 7 mV V<sub>T</sub> recovery is usually not an issue for digital memory applications, it may be of concern to analog memory since the current is changed significantly.

$I_D$  measured @  $V_G$  = 200 mV &  $V_D$  = 50 mV

**Figure 2.10** Analog retention characteristic of CTT. The CTT is programmed by 315 50- $\mu$ s gate pulses with the voltage increasing from 1 V to 2.57 V in 5 mV increment. The drain current is measured at V<sub>G</sub> = 200 mV and V<sub>D</sub> = 50 mV for one hour after each 15-pulse segment. The zoom-in of three circles is shown in Fig. 2.11.

**Figure 2.11** The current recovery for 1 hour after programming for different current levels. (a) the 1<sup>st</sup>, (b) the 11<sup>th</sup>, and (c) the 21<sup>st</sup> segment in Fig. 2.10, corresponding the different colors.

Fig. 2.12 shows the relationship between the current increase in 1 hour and the current immediately after programming. An approximate linear relationship is fitted to be

$$\Delta I = -0.075 \times I_{\rm RA} + 114.5 \,\,({\rm nA}) \tag{2.1}$$

where  $\Delta I$  is the current increase and  $I_{RA}$  is the current immediately after programming.

Figure 2.12 The relationship between the current increase in 1 hour and the current immediately after programming.

The implications of such analog retention behavior in accurately programming the analog memory are two-fold: First, the CTT needs be over-programmed; second, a block write-verify algorithm needs to be adopted: the CTTs in an array should be programmed one block at a time, and the verification of the inference current should take place after the block-write to allow for the stabilization of the current.

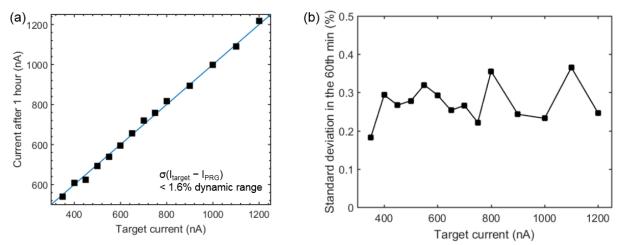

Using the fitted behavior in Eq. (2.1), a CTT is programmed to discrete target current levels from 1.2  $\mu$ A to 350 nA. For each target current, the device is over-programmed by the amount predicted by Eq. (2.1) and the current is measured after 1 hour. The relationship between the programmed current after 1 hour and the target current is shown in Fig. 2.13(a). It is clear that the

dots almost lie on the ideal y = x line, indicating a very good programming result. Indeed, the standard deviation of the difference between the programmed and the target current is less than 1.6% of the range of the target current.

**Figure 2.13** (a) The programmed current (after 1 hour) vs. the target current, with overprogramming of the CTT according to Eq. (2.1). (b) The standard deviation of the current measured in the last minute of 1 hour vs. the target current. It can be seen that the current is very stable after 1 hour.

Fig. 2.13(b) shows the standard deviation of the current measured in the last minute of 1 hour as a function of the target current. The current is stable regardless of the target current. In Section 4.3, the stability of the current after programming will be revisited in the array context.

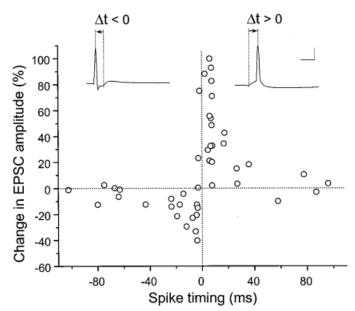

# 2.3 Spike-timing dependent plasticity (STDP)

The CTT can be employed to realize plastic synapses that possess spike-timing dependent plasticity (STDP) (Fig. 2.14) [64]. STDP is a key memory and learning mechanism in biological synapses: if the pre-synaptic neuron repeatedly fires right before the post-synaptic neuron does, the connectivity between the two neurons is strengthened (long-term potentiation, LTP); on the contrary, if the pre-synaptic neuron repeatedly fires right after the post-synaptic neuron does, the connectivity is weakened (long-term depression, LTD). In other words, the change in the connectivity between neurons depends on the timing-difference between pre- and post-synaptic

neurons. Since the  $V_T$  change after programming depends on the amplitude of the gate voltage, if a pulsing scheme can translate the timing difference to the amplitude, it should be able to demonstrate STDP in CTT. For example, in [36] and [42], discrete pulses are applied to the device to mimic the STDP characteristic. The idea is that, no pre- or post-synaptic pulse alone can significantly modify the state of the device, and only when the two pulses are simultaneously present can the device state be changed.

Figure 2.14 Typical spike-timing dependent plasticity exhibited by synapses [64].

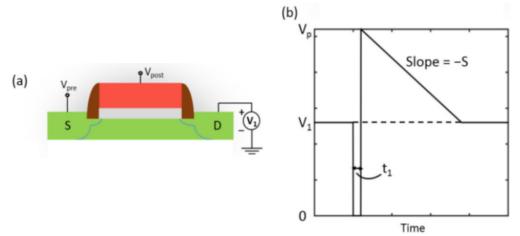

A similar pulsing scheme depicted in Fig. 2.15(b) is adopted here but the pulses are continuous instead of a train of discrete pulses in [36] and [42]. This makes circuit design much simpler. With this scheme, the pre-synaptic signal is connected to the source of the CTT, the post-synaptic signal is connected to the gate of the CTT, and the drain is biased at a constant voltage (Fig. 2.15(a)). The pre- and post-synaptic spikes take the same form: The voltage first drops to 0 from V<sub>1</sub> for a period of t<sub>1</sub>, returns to V<sub>p</sub> and then gradually decays to V<sub>1</sub> again with a slope of S (V/s).

Fig. 2.16 illustrates in detail how the change in the CTT channel conductance is modulated by the timing difference ( $\Delta t = t_{pre} - t_{post}$ ) between the two pulses, mimicking the STDP behavior. In

both cases ( $\Delta t > 0$  and  $\Delta t < 0$ ), the time segment 3 is the main programming pulse. For example, during time segment 3 in the LTD case ( $\Delta t = t_{pre} - t_{post} > 0$ , Fig. 2.16(a)), the source of the CTT (pre-synaptic signal) is grounded and a high voltage is applied to its gate (post-synaptic signal, whose amplitude decreases as  $\Delta t$  increases) while a drain voltage is being applied. The CTT is programmed to have a higher V<sub>T</sub> and therefore a smaller synaptic weight. Note that the amplitude of the gate pulse is V<sub>p</sub> – S $\Delta t$ , which, as  $\Delta t$  increases, decreases and results in a smaller weight change.

**Figure 2.15** Pulsing scheme to demonstrate STDP in CTT. (a) The connection: the presynaptic signal is connected to the source of the CTT, the post-synaptic signal is connected to the gate of the CTT, and the drain is biased at a constant voltage. (b) The pulsing scheme: The voltage first drops to 0 from  $V_1$  for a period of  $t_1$ , returns to  $V_p$  and then gradually decays to  $V_1$  again.

**Figure 2.16** Detailed breakdown of the applied pre- and post-synaptic pulses when (a) the post-synaptic neuron fires before the pre-synaptic one ( $\Delta t = t_{pre} - t_{post} > 0$ ), and (b) the post-synaptic neuron fires after the pre-synaptic one ( $\Delta t < 0$ ).

In the experiments, the CTT is first initialized with a program-erase cycle, and then incrementally programmed to an intermediate inference current of approximately 400 nA / 0.3  $\mu$ m before going through LTD and LTP cycles. The synaptic pulses as shown in Fig. 2.15(b) with V<sub>1</sub>= 1 V, t<sub>1</sub> = 1 ms, S = 1.3 V / 15 ms, and varying values of V<sub>p</sub> are generated by the waveform generator fast measurement unit (WGFMU) and applied to the CTT. For each timing-difference, the experiment is repeated 10 times to obtain the statistical behavior.

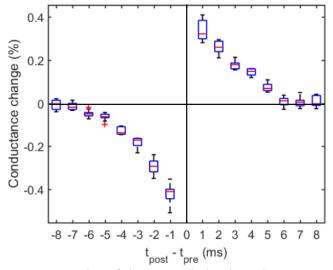

The boxplot of conductance change as a function of the spike timing-difference is shown in Fig. 2.17 for  $V_p = 2.3$  V. It is clear that there is cycle-to-cycle variation, partly due to the physical change in the CTT after each trial. It is also important to note that, as the pre- and post-synaptic pulses are separated by more than ~ 6 ms, the pulses have very small effect on the state of the CTT.

Figure 2.17 Boxplot of the STDP behavior when  $V_p = 2.3$  V.

The average of the conductance change as a function of the timing difference is shown in Fig. 2.18 for different values of  $V_p$  (2.3 V, 2.1 V, 1.9 V). It is observed that the conductance change at a given timing-difference, both in the LTP and LTD regimes, increases with the highest programming voltage  $V_p$ . A maximum conductance of 34% and – 42% is obtained in the LTP and LTD regimes, respectively, when  $V_p = 2.3V$ . To obtain a larger conductance change, higher  $V_p$  or longer  $t_1$  is required.

**Figure 2.18** Spike-timing dependent plasticity exhibited by CTT. Solid lines are exponential curves fitted to Eq. (2.2).

Fig. 2.18 also demonstrates the tunability of the STDP behavior through changing pulse parameters. The conductance change in both LTP and LTD can be fitted as:

$$\Delta G/G = A_{LTP, LTD} \times \exp\left(-|\Delta t|/\tau_{LTP, LTD}\right)$$

(2.2)

and the values of the fitting parameters  $A_{LTP, LTD}$  and  $\tau_{LTP, LTD}$  for different values of  $V_p$  are listed in Table 2.1. Both A and  $\tau$  increase as  $V_p$  increases. In practice,  $V_1$ ,  $t_1$ , and S can all be modified to obtain the desired STDP behavior.

| V <sub>p</sub> (V) | LTP   |        | LTD    |             |

|--------------------|-------|--------|--------|-------------|

|                    | A (%) | τ (ms) | A (%)  | $\tau$ (ms) |

| 2.3                | 52.25 | 2.588  | -66.47 | 2.306       |

| 2.1                | 33.21 | 2.258  | -52.01 | 1.904       |

| 1.9                | 28.26 | 1.437  | -41.77 | 1.304       |

Table 2.1 Parameters from the fitted Equation (2.2).

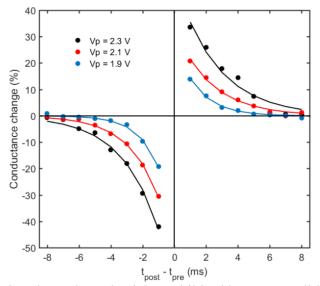

# 2.4 Weight-dependent plasticity

For many cases of unsupervised learning, for example winner-takes-all (WTA) clustering and temporal correlation detection, as will be discussed in Chapter 3, a device characteristic – the weight-dependent plasticity, is desired. It requires that the change of inference current (or channel conductance) be dependent on the conductance itself.

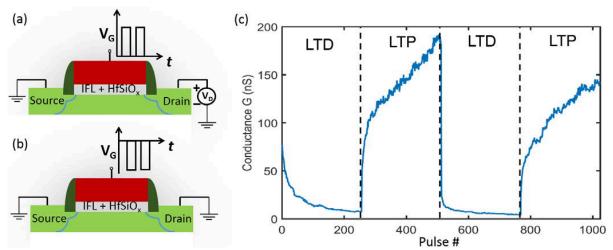

The subthreshold OFF-conductance ( $G_{OFF}$ ) of the CTT at  $V_{DS} = 50 \text{ mV}$  and  $V_{GS} = 0$  is used as the synaptic weight. In the LTD regime where the weight is to be decreased, a positive gate pulse is applied and electrons are trapped into HfSiO<sub>4</sub> through the interfacial layer (IFL), increasing  $V_{\tau}$  and decreasing  $G_{OFF}$  (Fig. 2.19(a)); in the LTP regime, a negative gate pulse is applied and trapped electrons tunnel back into the channel, decreasing  $V_{\tau}$  and increasing  $G_{OFF}$  (Fig. 2.19(b)). In the experiments, a CTT is first pre-programmed to an intermediate starting state by applying a gate

pulse of 2.5 V for 60  $\mu$  s with V<sub>p</sub> = 1.3 V. The device subsequently goes through four cycles: two LTD and two LTP cycles, with 256 trapping or detrapping pulses in each cycle. In the LTD cycle, G<sub>oFF</sub> is decreased by a 20- $\mu$ s, 2.5 V gate pulse with V<sub>p</sub> = 1.3 V; in the LTP cycle, G<sub>oFF</sub> is increased by a 50- $\mu$ s, - 2.6 V gate pulse with zero drain bias. The resulting G<sub>oFF</sub> is shown in Fig. 2.19(c) where a reversible and reproducible modification of synaptic weights can be observed. Over 200 levels are achieved for both LTP and LTD regimes with a fine resolution of less than 1 nS for LTP and 0.25 nS for LTD. As we will show later in Section 3.1.2, although the LTD has a smaller dynamic range, it will not affect the convergence of the learning algorithm.

Figure 2.19 Configurations of the CTT in the (a) LTD and (b) LTP regimes. (c) Reversible and reproducible device conductance change through four cycles.

We show in Fig. 2.20(a) the relative  $G_{oFF}$  change as a function of  $G_{oFF}$  itself when five trapping and detrapping pulses as specified above are applied. It is observed that, in the LTP regime, the relative  $G_{oFF}$  increase is smaller when the initial  $G_{oFF}$  is larger; on the contrary, in the LTD regime, the relative  $G_{oFF}$  reduction is larger when the initial  $G_{oFF}$  is larger. The curves corresponding to the LTP and LTD regimes are fitted to exponential and sigmoid functions, respectively, for different programming times (Fig. 2.20(b)). As expected, a longer programming time consistently leads to a larger  $G_{oFF}$  change because of the larger  $V_{T}$  change caused by more trapped/detrapped charge [58].

**Figure 2.20** (a) The weight-dependent plasticity when five trapping/detrapping pulses are applied in the LTD/LTP regimes, respectively. (b) Fitted curves when pulses of different widths are applied.

# 2.5 Variation of CTT

We have seen from Section 2.2.3 that the inference current of a CTT gradually increases after the device is programmed, and the increase is larger for a smaller target current. This makes the block write-verify process necessary when programming a CTT array to accurate weight values. In this Section, we show statistical results on the programming behavior of a custom-built twincell CTT array with 10 word lines (WLs) and 8 bitline (BLs) to further establish the necessity of the block write-verify approach.

In one programming cycle, 500- $\mu$ s programming pulses with V<sub>D</sub> = 1.2 V and varying V<sub>G</sub> (2.1 V, 2.4 V, and 2.7 V) are applied sequentially to the CTTs in the array. After each programming cycle, the inference current I<sub>inf</sub> of all CTTs in the array is measured at V<sub>G</sub> = 200 mV and V<sub>D</sub> = 50 mV. To suppress the channel current from other CTTs in the same column, -0.3 V is applied to their gates. The evolution of average V<sub>T</sub> and I<sub>inf</sub> with the number of programming pulses is shown in Fig. 2.21. As expected, both the V<sub>T</sub> increase and the I<sub>inf</sub> reduction are higher for a higher gate

programming voltage. The highest achievable  $\Delta V_T$  is 115 mV when the device is programmed for a total of 30 ms at  $V_G = 2.7$  V.

**Figure 2.21** The evolution of average (a)  $V_T$  and (b)  $I_{inf}$  with the number of programming pulses, for different gate programming voltage. Each programming pulse is 500-µs long and the total programming time is 30 ms.

**Figure 2.22** Statistics of (a)  $V_T$  and (b)  $I_{inf}$  with the number of programming pulses, for different gate programming voltage. Each programming pulse is 500-µs long and the total programming time is 30 ms.

Fig. 2.22 shows the average as well as the standard deviation of the  $V_T$  and  $I_{inf}$ . It is clear that there exists substantial device variation. When the  $I_{inf}$  of a device needs to be programmed to a specific value, for example when CTTs are used as synapses in an inference engine described in Chapter 4, although first-order estimate can be made to determine approximately how long a programming pulse is necessary, the  $I_{inf}$  needs to be verified after the pulse and a decision to apply or not apply another pulse is made.

As discussed in Section 1.1, by conducting in-memory computation, analog-synapse-based neuromorphic systems do not need to constantly fetch data between the memory and the CPU, therefore significantly reducing the power and time required. Various analog synapses have been explored in neuromorphic systems for both unsupervised learning and supervised learning.

In this chapter, two algorithms for unsupervised learning, namely, winner-takes-all (WTA) clustering and temporal correlation detection, are investigated, using CTTs as the analog synapses. It is shown that the algorithms can indeed be implemented with CTTs and are robust to device variations. Experimental demonstration of these algorithms using the custom-built CTT arrays is also discussed.

## 3.1 Winner-takes-all network

#### 3.1.1 Background

In this era of mass connectivity (social media, internet of things, etc.), a vast amount of data is being generated every day. However, 80% of these data is unstructured, making extracting valuable information out of them a very challenging task. One of the many ways to analyze the data is *clustering* – to categorize data into subgroups such that the data points within each group are "similar" to each other. Note that there is no universal definition of "similar", and the division of data might not be unique. A good example of clustering can be found in social media. People can be categorized into different "professions" according to who they interact with, what their topics of interest are, and even what they eat.

Various algorithms in software have been developed for clustering purposes, including winnertakes-all (WTA) and k-means clustering. These algorithms can also be implemented in hardware [66, 67]. For example, Serb *et al.*, in [66] reported a WTA network with TiO<sub>2</sub>-based memristors. In their work, a one-layer WTA network with four input neurons and two output neurons is constructed to cluster two simple four-bit binary patterns: 1001 and 0110, and noisy versions of them. The four synapses corresponding to one output neuron are implemented in software and the other four are implemented with memristors (Fig. 3.1(a)). Specialization functions are used to monitor the quality of clustering. As can be seen in Fig. 3.1(b), the two patterns are well separated after ~ 100 pattern presentations, even though there is significant device variation (Fig. 3.1(d)).