# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Logical Reasoning Techniques for Physical Layout in Deep Nanometer Technologies

Permalink https://escholarship.org/uc/item/9mv5653s

Author Park, Dong Won

Publication Date 2021

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SAN DIEGO

## Logical Reasoning Techniques for Physical Layout in Deep Nanometer Technologies

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

# Electrical Engineering (Computer Engineering)

by

Dong Won Park

Committee in charge:

Professor Chung-Kuan Cheng, Chair Professor Bill Lin, Co-Chair Professor Sujit Dey Professor Daniel Mertz Kane Professor Patrick Philip Mercier

2021

Copyright Dong Won Park, 2021 All rights reserved. The dissertation of Dong Won Park is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Co-Chair

Chair

University of California San Diego

2021

# DEDICATION

To my wife, Seolyn, my daughter, Siyul Stella, my son, Siwoo, and my family

# EPIGRAPH

Man proposes, God disposes.

# TABLE OF CONTENTS

| Signature Pa    | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .    | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Epigraph        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table of Con    | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| List of Figure  | six                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| List of Table   | xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Acknowledg      | ments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Vita            | XV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Abstract of the | e Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 1       | Introduction and Preliminaries11.1Integer Linear Programming (ILP) for Routing41.1.1Binarized/Undirected Multi-Commodity Network Flow theory61.2Boolean Satisfiability (SAT) for Detailed Routing71.2.1SAT Encodings for Boolean cardinality constraint81.2.2Boolean Constraint Propagation (BCP)91.2.3Minimal Unsatisfiable Subset (MUS)101.3Satisfiability modulo theories (SMT) for Standard Cell Layout111.3.1Breaking symmetry predicates121.4Preliminaries of Framework Configurations131.4.1On-grid Unidirectional Routing Graph: G(V, E)131.4.3Geometric variable for conditional design rules14 |

| Chapter 2       | Detailed Routing: Routability Analysis and Optimization Framework172.1Introduction182.1.1Related Works182.1.2Our Contributions202.2Routability Analysis Framework Preliminary212.2.1Grid-based Routing Graph: G(V, E)212.2.2Configuration of Constraint Formulation212.3Constraints Formulation222.3.1SAT-friendly ILP formulation232.3.2ILP-to-SAT Conversion28                                                                                                                                                                                                                                         |

|           |      | 2.3.3 SAT Formulation                                              |

|-----------|------|--------------------------------------------------------------------|

|           | 2.4  | Routability Analysis Framework                                     |

|           |      | 2.4.1 Overall Flow of Routability Analysis Framework               |

|           |      | 2.4.2 Complexity Analysis for SAT-based Framework                  |

|           |      | 2.4.3 An Example of Routability Analysis Result (ILP & SAT) . 40   |

|           | 2.5  | Experiments                                                        |

|           |      | 2.5.1 Experimental Setup                                           |

|           |      | 2.5.2 Improvement of Formulation Complexity                        |

|           |      | 2.5.3 Benchmark Information and Switchbox Generation 43            |

|           |      | 2.5.4 Experimental Results using Benchmark                         |

|           |      | 2.5.5 Scalability of the Routability Analysis Framework 44         |

|           | 2.6  | Conclusion         46                                              |

| Chapter 3 | Deta | iled Routing: Routability Diagnosis Framework                      |

| p         | 3.1  | Introduction                                                       |

|           | 3.2  | Routability Diagnosis Framework                                    |

|           | 5.2  | 3.2.1 Overall Flow of Routability Diagnosis Framework 50           |

|           |      | 3.2.2 MUS Extraction                                               |

|           |      | 3.2.3 Decision with Longest-path Search (DLS)                      |

|           |      | 3.2.4 Diagnosis Result Report                                      |

|           |      | 3.2.5         DRV Classification         57                        |

|           |      | 3.2.6 Application Scenarios using our frameworks                   |

|           | 3.3  | ••••••                                                             |

|           | 5.5  | 1                                                                  |

|           |      | 1 1                                                                |

|           |      |                                                                    |

|           | 2.4  | 3.3.3 Scalability of the Routability Diagnosis Framework 62        |

|           | 3.4  | Conclusion                                                         |

| Chapter 4 |      | dard Cell Synthesis: Simultaneous Transistor Placement and In-cell |

|           |      | ing                                                                |

|           | 4.1  | Introduction                                                       |

|           |      | 4.1.1 Related Works                                                |

|           |      | 4.1.2 Our Contributions                                            |

|           | 4.2  | Framework Preliminary                                              |

|           |      | 4.2.1 Overview of SP&R Framework                                   |

|           |      | 4.2.2 SMT (Satisfiability Modulo Theories)                         |

|           |      | 4.2.3 Multi-Objective Optimization                                 |

|           |      | 4.2.4 Cell Architecture                                            |

|           | 4.3  | Simultaneous Placement & Routing                                   |

|           |      | 4.3.1 Transistor Placement                                         |

|           |      | 4.3.2 In-Cell Routing                                              |

|           |      | 4.3.3 Dynamic Pin Allocation (DPA) 83                              |

|           | 4.4  | Experiments                                                        |

|              |      | 4.4.1          | Sequential vs. Simultaneous P&R                                | 86       |

|--------------|------|----------------|----------------------------------------------------------------|----------|

|              |      | 4.4.2          | Optimization for DFM and I/O pin accessibility                 | 86       |

|              |      | 4.4.3          | Experimental Statistics                                        | 87       |

|              | 4.5  | Conclu         | ision                                                          | 88       |

| Chapter 5    | Para | metric I       | OTCO through whole set of Standard Cell Library                | 91       |

| Chapter 5    | 5.1  |                |                                                                | 92       |

|              | 5.2  |                | ility Improvement of Standard Cell Automation                  | 94       |

|              | 5.2  | 5.2.1          | Constraints for Practical Design Features                      | 94       |

|              |      | 5.2.1          | Breaking Design Symmetry                                       | 94<br>97 |

|              |      | 5.2.2          |                                                                | 98       |

|              |      | 5.2.5<br>5.2.4 | Conditional Assignment                                         | 98<br>99 |

|              |      |                | Localization of the Routing Region                             |          |

|              | 5 0  | 5.2.5          | Cell Partitioning                                              | 100      |

|              | 5.3  |                | ments for Scalability Improvement                              | 102      |

|              |      | 5.3.1          | Experimental Results                                           | 102      |

|              | ~ ^  | 5.3.2          | Experimental Statistics of a Practical 7nm Cell Library        | 107      |

|              | 5.4  |                | rd-cell Scaling Framework                                      | 109      |

|              |      | 5.4.1          | Framework Overview                                             | 110      |

|              |      | 5.4.2          | Sub-7 <i>nm</i> Cell Architectures                             | 111      |

|              |      | 5.4.3          | Parametric Conditional Design Rules                            | 111      |

|              |      | 5.4.4          | Layout Synthesis with Guaranteed Pin-accessibility             | 112      |

|              | 5.5  | -              | ments for Standard-Cell Scaling Framework                      | 114      |

|              |      | 5.5.1          | Experimental Setup                                             | 114      |

|              |      | 5.5.2          | Experimental Results                                           | 115      |

|              | 5.6  | Conclu         | usion                                                          | 119      |

| Chapter 6    | Sum  | mary an        | d Future Work                                                  | 122      |

| 1            | 6.1  | •              | Summary                                                        | 122      |

|              | 6.2  |                | Directions                                                     | 123      |

|              |      | 6.2.1          | Routability-driven standard cell synthesis in extremely scaled | _        |

|              |      |                | technology nodes                                               | 124      |

|              |      | 6.2.2          | Concurrent refinement through simultaneous detailed-placement  |          |

|              |      | 5.2.2          | and detailed-routing                                           | 125      |

| Bibliography |      |                |                                                                | 126      |

| Dionography  | •••  |                |                                                                | 140      |

# LIST OF FIGURES

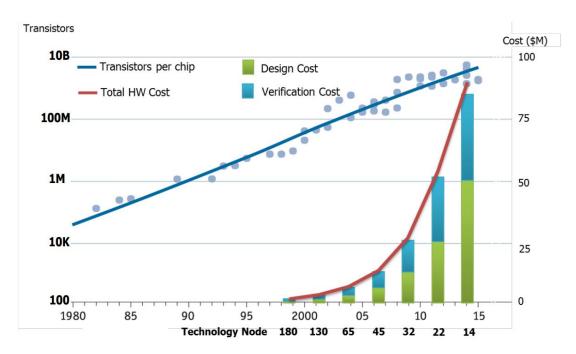

| Figure 1.1:  | Design technology crisis [1]                                                                                                                                                                                                       | 2          |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

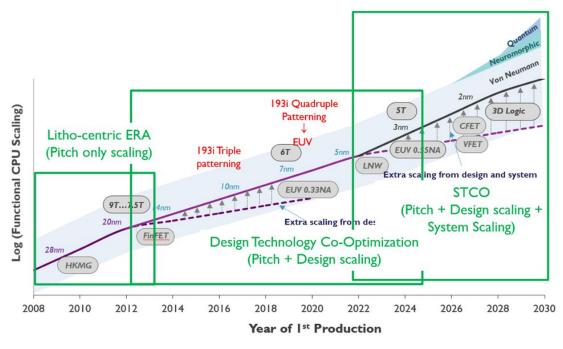

| Figure 1.2:  | Scaling road map [2]                                                                                                                                                                                                               | 2          |

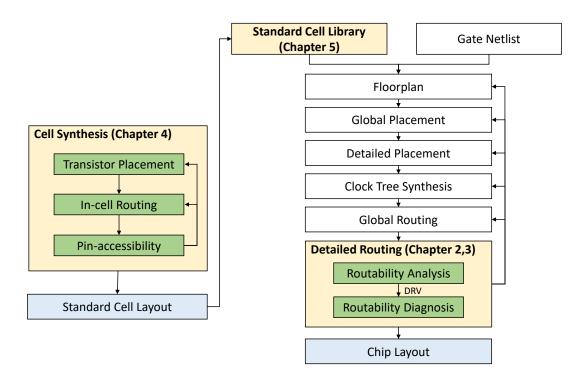

| Figure 1.3:  | Physical design stages and the targets of this dissertation                                                                                                                                                                        | 3          |

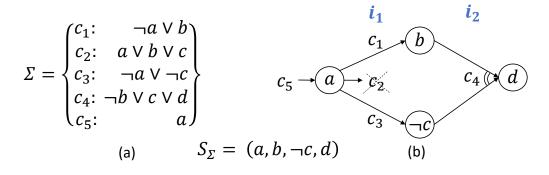

| Figure 1.4:  | An example of (a) SAT formula $\sum$ , and (b) the associated implication graph                                                                                                                                                    |            |

|              | through BCP.                                                                                                                                                                                                                       | 10         |

| Figure 1.5:  | An example of (a) infeasible SAT formula $\sum_U$ , and (b) the corresponding MUSes.                                                                                                                                               | 11         |

| Figure 1.6:  | An example of grid-based routing graph, $G(V, E)$                                                                                                                                                                                  | 14         |

| Figure 1.7:  | Supernodes. <i>PIN</i> 1 and <i>PIN</i> 2 respectively cover three and five vertices on <i>M</i> 1 layer (i.e., inner pin). Outer pins are connected to boundary vertices of                                                       |            |

|              | $G$ through Super Outer Node $(S_o)$                                                                                                                                                                                               | 15         |

| Figure 1.8:  | An example to determine geometric variable $g_{d,v}$                                                                                                                                                                               | 16         |

| Figure 2.1:  | Efforts to secure the pin accessibility during the PD procedure. Our SAT-<br>based routability analysis enables a fast and precise DRV assessment, and<br>routability diagnosis minimizes the ECO cost with precise suggestion for |            |

|              | DRV refinements.                                                                                                                                                                                                                   | 19         |

| Figure 2.2:  | Configuration of constraint formulation.                                                                                                                                                                                           | 22         |

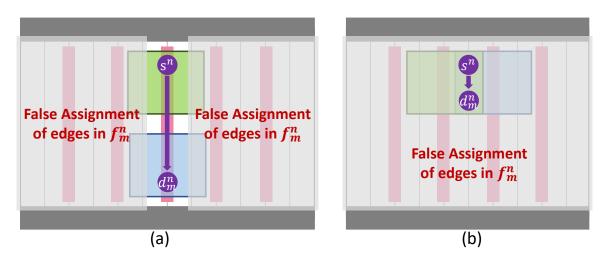

| Figure 2.3:  | An example of CFC constraint for pins (i.e., $v = s^n, d_m^n$ ). (a) CFC of virtual                                                                                                                                                |            |

|              | edges for inner pin. (b) CFC of virtual edges for outer pin.                                                                                                                                                                       | 24         |

| Figure 2.4:  | An example of CFC constraint for grid (a) no flow passes, (b) the flow of commodity <i>m</i> is connected between a pair of edges.                                                                                                 | 24         |

| Figure 2.5:  | An example of the minimum area rule.                                                                                                                                                                                               | 26         |

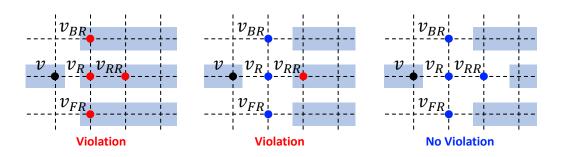

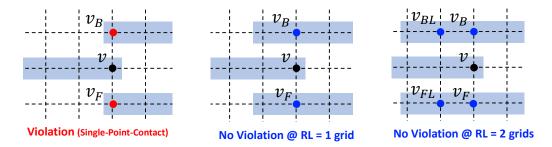

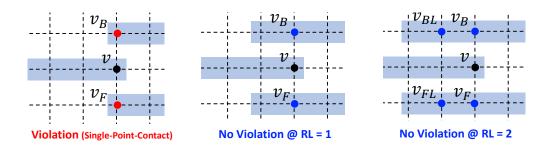

| Figure 2.6:  | An example of the end-of-line (EOL) spacing rule.                                                                                                                                                                                  | 27         |

| Figure 2.7:  | An example of the Parallel Run Length (PRL) rule                                                                                                                                                                                   | 27         |

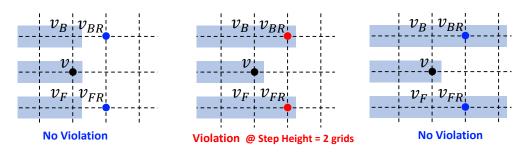

| Figure 2.8:  | An example of Step Height Rule (SHR) @ Step Height = 2 grids                                                                                                                                                                       | 28         |

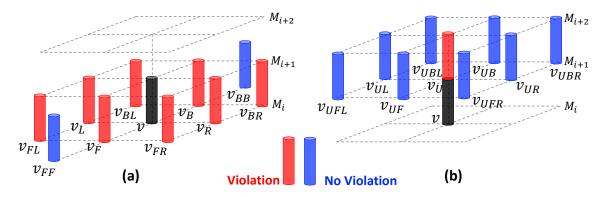

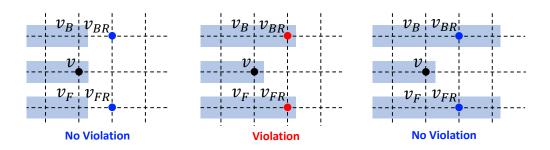

| Figure 2.9:  | VR rule. (a) via-to-via spacing rule. (b) stacked-via regulation                                                                                                                                                                   | 29         |

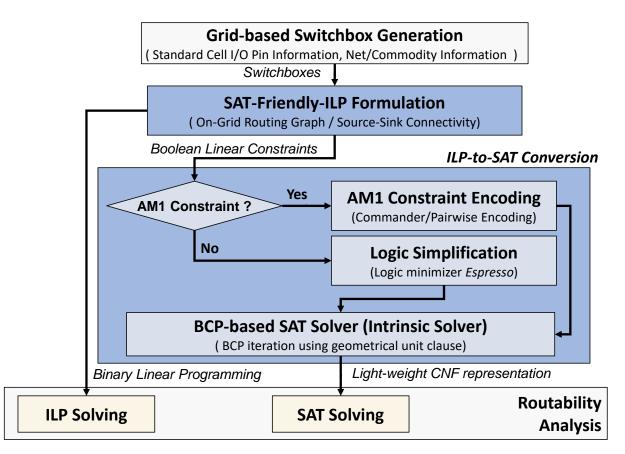

| Figure 2.10: | Overall flow of our routability analysis framework                                                                                                                                                                                 | 36         |

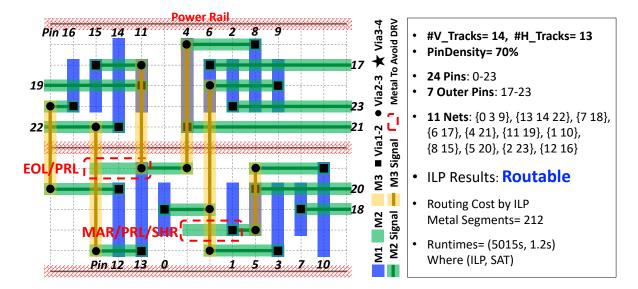

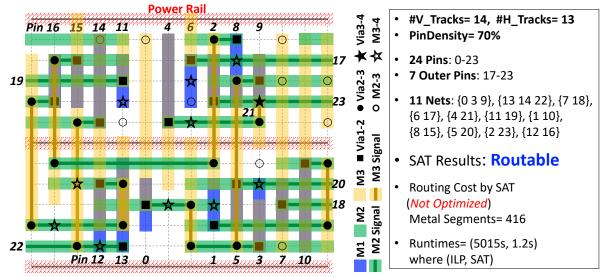

| Figure 2.11: | The ILP-based optimal routing solution ( $Cost = 212$ ). Four more metal                                                                                                                                                           |            |

| -            | segments are assigned to avoid DRC violations (red dotted circles).                                                                                                                                                                | 41         |

| Figure 2.12: | The SAT-based routing solution (Cost = $416$ ). The solution is not optimal,                                                                                                                                                       |            |

| C            | but takes only 0.02% of ILP's runtime.                                                                                                                                                                                             | 41         |

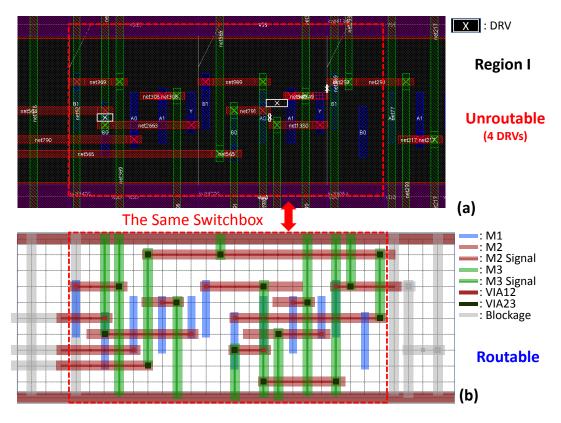

| Figure 2.13: | An example of switchbox from ISPD 2019 benchmark. (a) DRC violations                                                                                                                                                               |            |

| C            | from the industry routing tool. (b) Optimized routing solution generated by                                                                                                                                                        |            |

| 5. 0.14      | our framework (ILP).                                                                                                                                                                                                               | 44         |

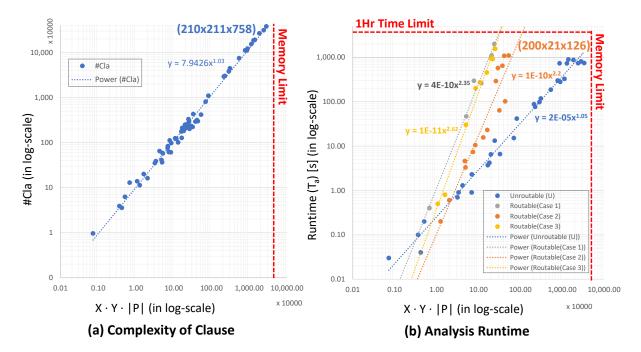

| Figure 2.14: | Scablablility of our routability analysis framework (in log-scale). (a) Complexity of clause. (b) Runtime $(T_a)$ .                                                                                                                | 46         |

| Eigener 2.1  | Owenell flow of own neutralility diagnosis                                                                                                                                                                                         | <b>F</b> 1 |

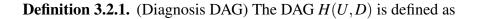

| Figure 3.1:  | Overall flow of our routability diagnosis. $\dots \dots \dots$                                                                     | 51         |

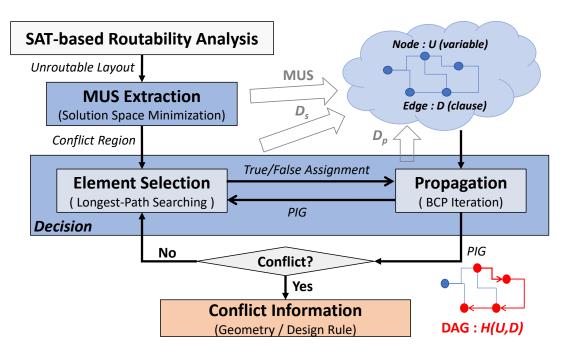

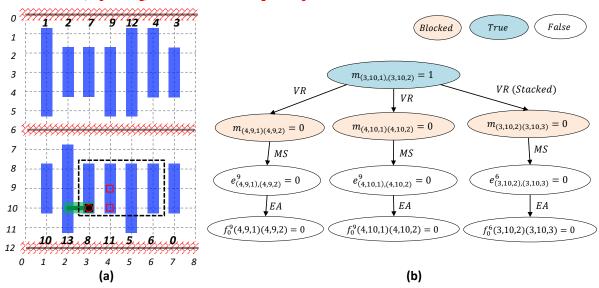

| Figure 3.2:  | An example of DRV explanation based on path length. (a) $2 @ (3,8,1)$ . (b) $1 @ (3,9,1)$ , (c) $4 @ (3,10,1)$ .                                                                                                                   | 53         |

| Figure 3.3:   | Elements selection for the propagation. (a) Elements for true assignment.<br>(b) Elements from via-to-via spacing/stacked-via regulation. (c) Vias in the |    |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|               | same pin. (d) In-layer Elements with the direction against true assignment                                                                                |    |

|               | for false assignment.                                                                                                                                     | 55 |

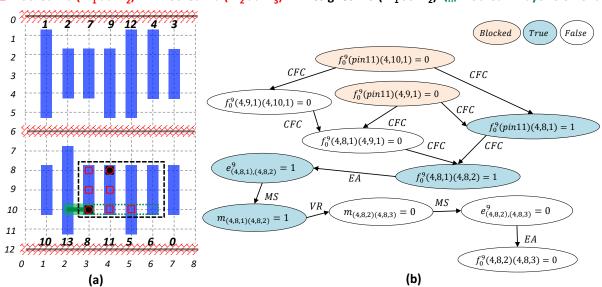

| Figure 3.4:   | An example of propagation with true assignment. (a) Propagation result. (b)<br>Some part of PIG.                                                          | 56 |

| Figure 3.5:   | An example of propagation with false assignment. (a) Propagation result. (b)<br>Some part of PIG for via-to-via spacing void.                             | 56 |

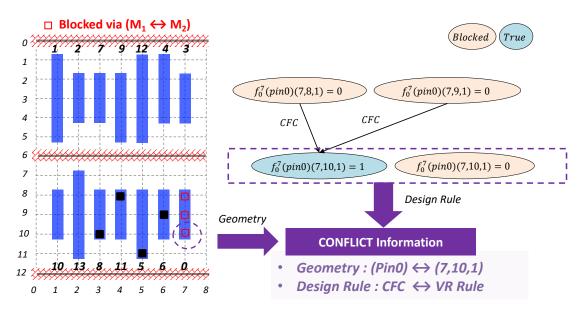

| Figure 3.6:   | An example of diagnosis result.                                                                                                                           | 57 |

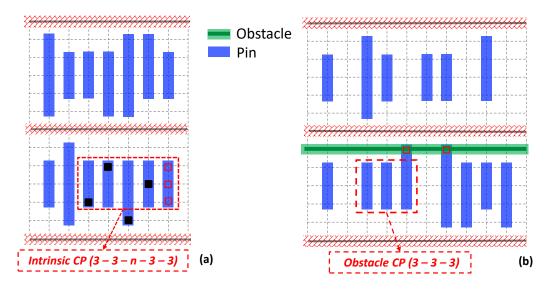

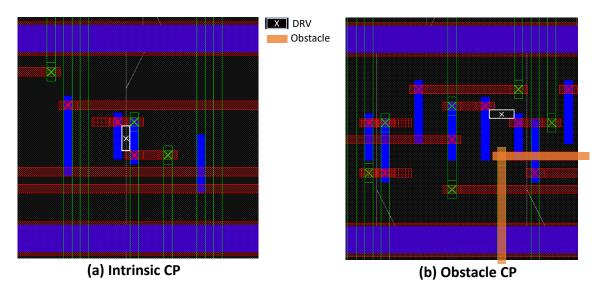

| Figure 3.7:   | Examples of Conflict Pin-shape (CP) type (VR = $\sqrt{2}$ ). (a) Intrinsic CP. (b)<br>Obstacle CP.                                                        | 58 |

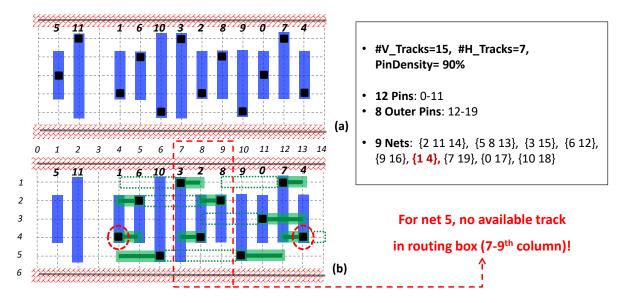

| Figure 3.8:   | An example of Routing Congestion (RC). (a) No violation in locating vias                                                                                  | 50 |

| I iguite 5.6. | between $M_1$ and $M_2$ . (c) Lack of routing tracks for net 5                                                                                            | 59 |

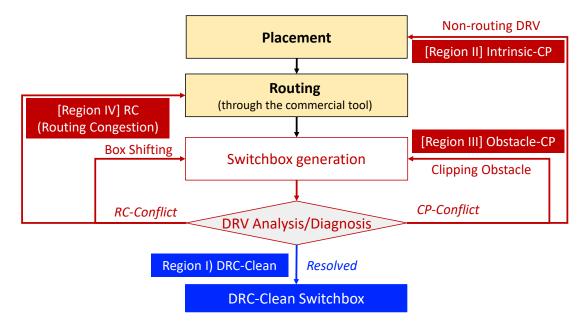

| Figure 3.9:   | Practical ECO scenarios using our frameworks. (Region I) DRC-Clean                                                                                        | 57 |

| I iguie 5.7.  | switchbox. (Region II) Non-routing DRV. (Region III) Switchbox regenera-                                                                                  |    |

|               | tion. (Region IV) Routing-related DRV                                                                                                                     | 59 |

| Figure 3.10:  |                                                                                                                                                           | 57 |

| 1 iguie 5.10. | (Region II). (b) Obstacle CP (Region III).                                                                                                                | 62 |

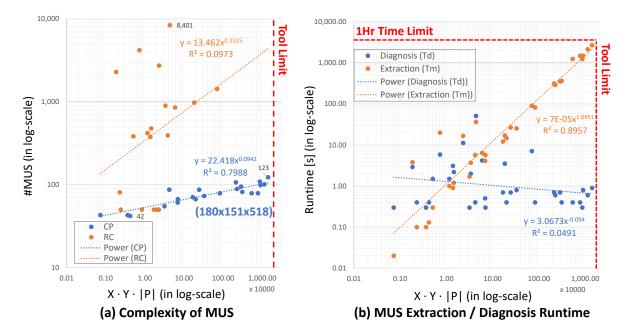

| Figure 3 11.  | Scablablility of our routability diagnosis framework (in log-scale). (a) Com-                                                                             | 02 |

| 119010 31111  | plexity of MUS. (b) Runtime $(T_m, T_d)$                                                                                                                  | 63 |

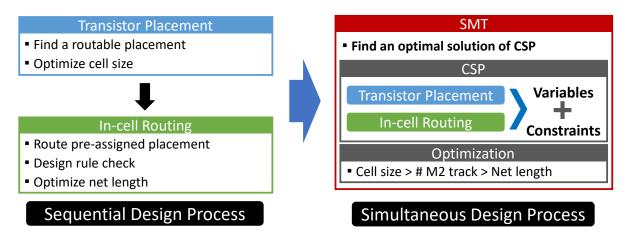

| Figure 4.1:   | Sequential vs. our proposed simultaneous cell design processes                                                                                            | 69 |

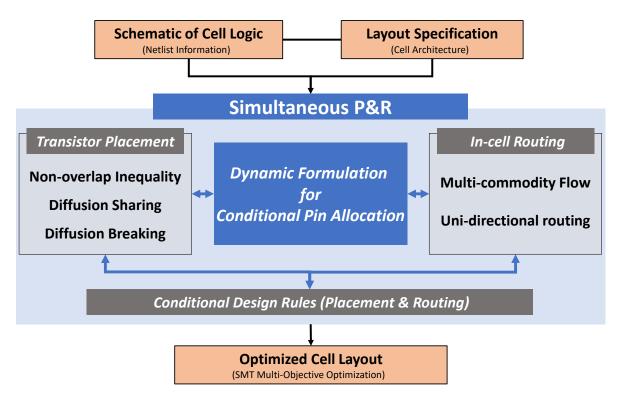

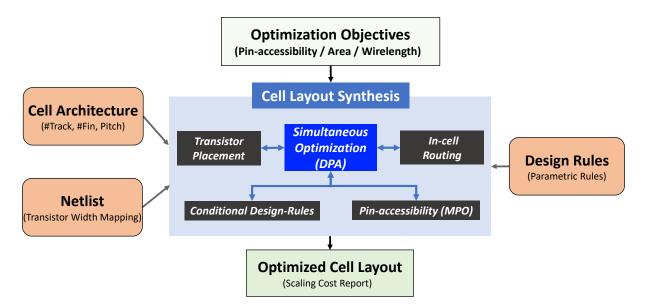

| Figure 4.2:   | The proposed Simultaneous <b>P&amp;R</b> framework                                                                                                        | 70 |

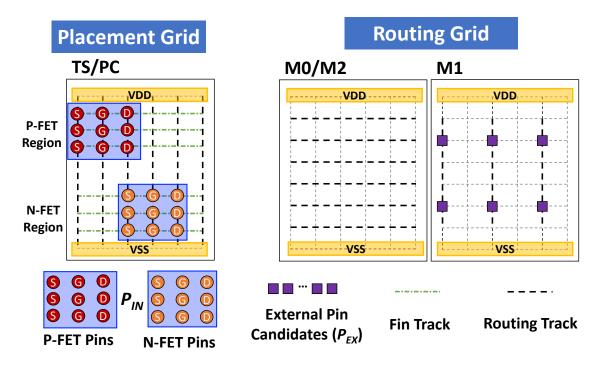

| Figure 4.3:   | Grid-based placement & 3-D routing graph.                                                                                                                 | 72 |

| Figure 4.4:   | Configuration of a FET with size of 3                                                                                                                     | 74 |

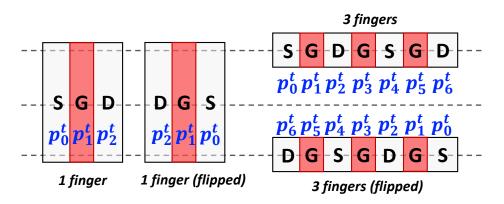

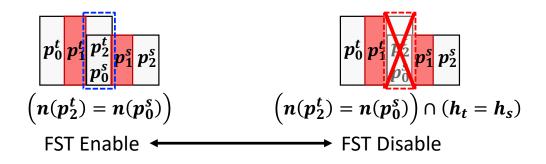

| Figure 4.5:   | Diffusion sharing (DS) with the FET size transition (FST) option.                                                                                         | 75 |

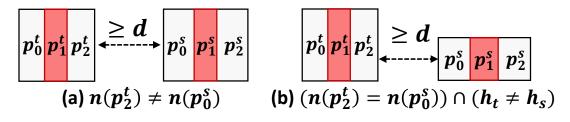

| Figure 4.6:   | Diffusion break (DB) (a) different net information, (b) different diffusion                                                                               |    |

| -             | heights with FST disable.                                                                                                                                 | 75 |

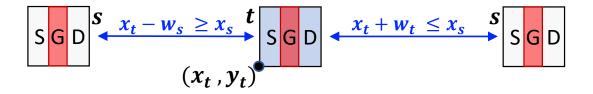

| Figure 4.7:   | Relative positions between two FETs                                                                                                                       | 75 |

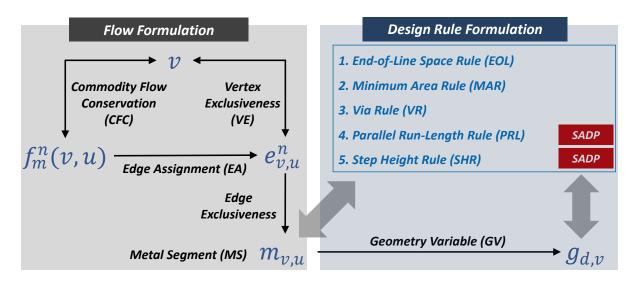

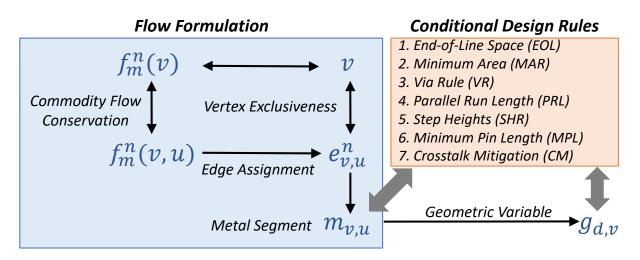

| Figure 4.8:   | Flow formulation with conditional design rules.                                                                                                           | 80 |

| Figure 4.9:   | Example of PRL (Parallel Run-Length) rule.                                                                                                                | 81 |

| Figure 4.10:  | Example of SHR (Step Heights Rule)                                                                                                                        | 82 |

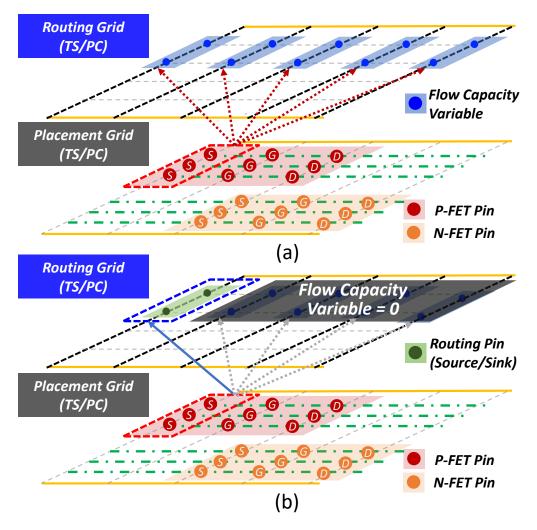

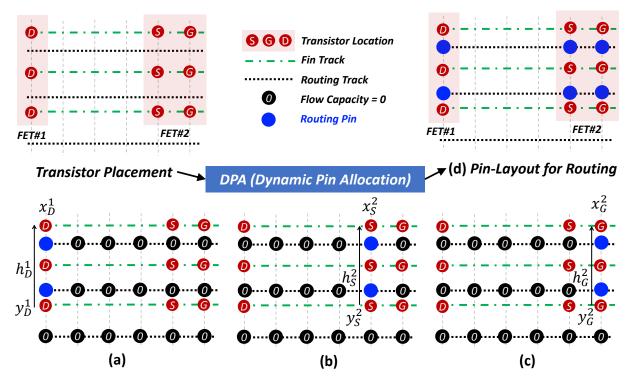

| Figure 4.11:  | Dynamic pin allocation (DPA) between placement and routing grids                                                                                          | 83 |

| Figure 4.12:  | An example of pin allocation through DPA. Capacity control for (a) drain pin                                                                              |    |

|               | of FET#1, (b) source pin of FET#2, and (c) gate pin of FET#2. (d) Selected                                                                                |    |

|               | pin-layout for routing.                                                                                                                                   | 85 |

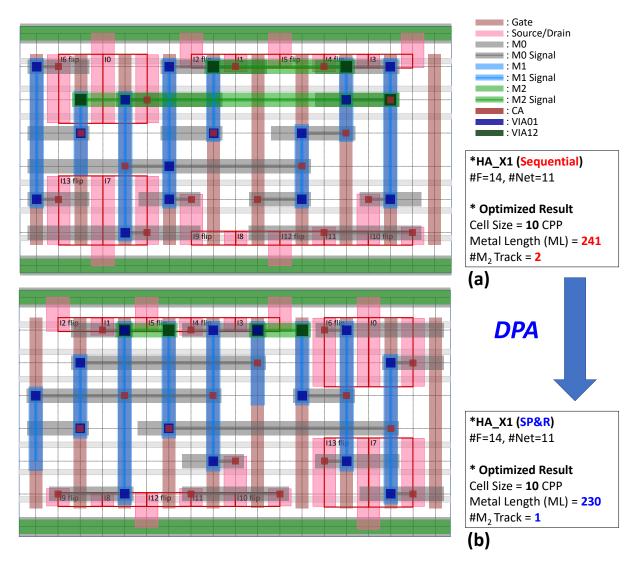

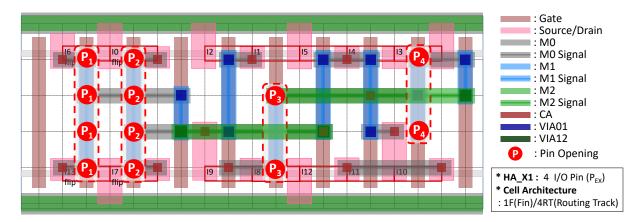

| Figure 4.13:  | The comparison between (a) sequential (ML=241, $\#M2=2$ ) and (b) simulta-                                                                                |    |

|               | neous P&R (the proposed $SP\&R$ ) (ML=230, #M2=1) using HA_X1                                                                                             | 87 |

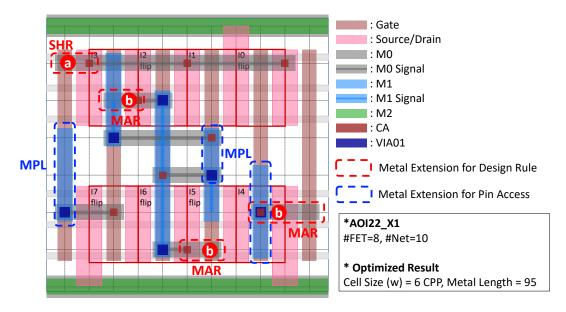

| Figure 4.14:  | An optimized cell layout for DFM and I/O pin accessibility                                                                                                | 88 |

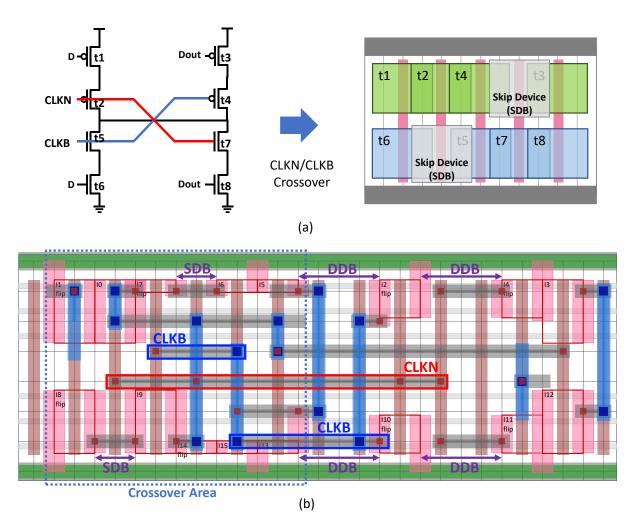

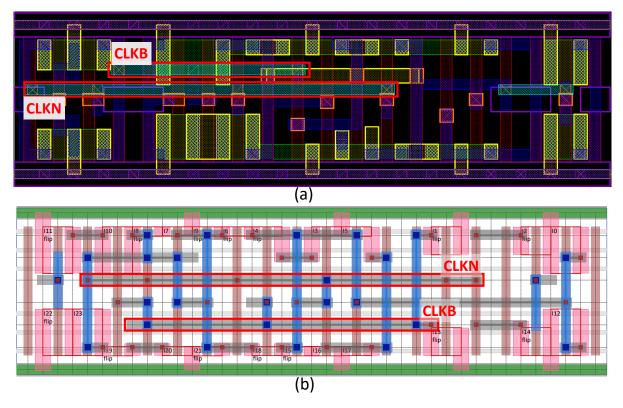

| Figure 5.1:   | Example of SDBs. (a) a crossover area (CLKN/CLKB), (b) the crossover area in DHLx1 layout.                                                                | 95 |

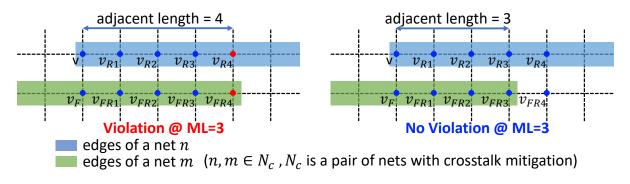

| Figure 5.2:   | Example of crosstalk mitigation (CM) rule.                                                                                                                | 96 |

| Figure 5.3:  | Layout of DFFHQNx1. (a) Layout from the standard cell library [3], dis-            | 07       |

|--------------|------------------------------------------------------------------------------------|----------|

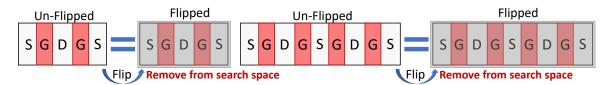

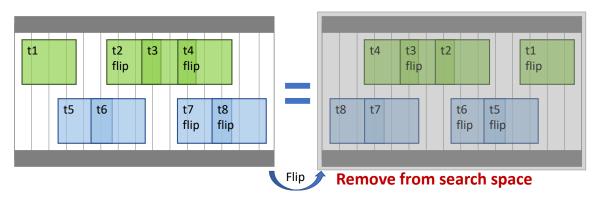

| Figure 5.4:  | played by a commercial tool [4]. (b) <i>SP&amp;R</i> 's layout generation          | 97<br>98 |

| Figure 5.5:  | Flipped case exclusion of whole cell design from search space.                     | 99       |

| Figure 5.6:  | Conditional assignment. (a) A commodity flow through the same gate col-            | ,,       |

| 119410 5.0.  | umn, and (b) a commodity flow through the DS.                                      | 99       |

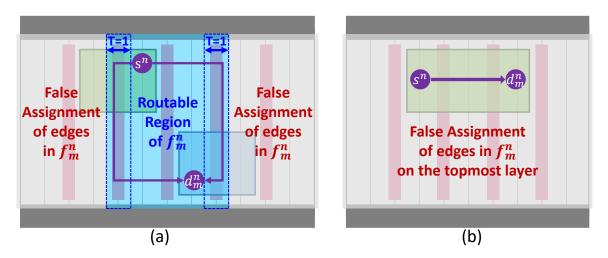

| Figure 5.7:  | Conditional Localization. (a) Localization of commodity flows with a toler-        |          |

| C            | •                                                                                  | 100      |

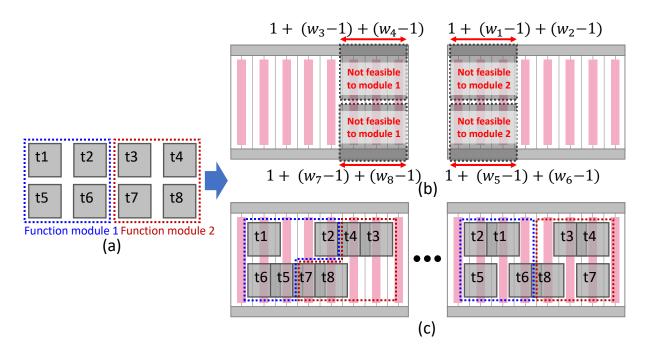

| Figure 5.8:  | Cell Partitioning. (a) Functional module partitioning. (b) Localization of the     |          |

| C            | placement area. (c) Examples of $SP\&R$ with cell partitioning                     | 101      |

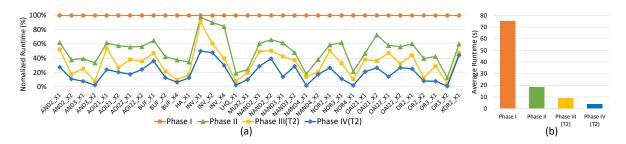

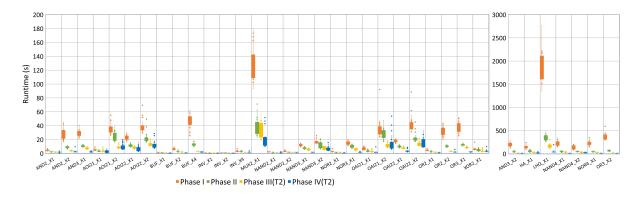

| Figure 5.9:  | Contributions of each scalability improvement phase for runtime reduction.         |          |

|              | (a) Normalized runtime. (b) Average runtime                                        | 104      |

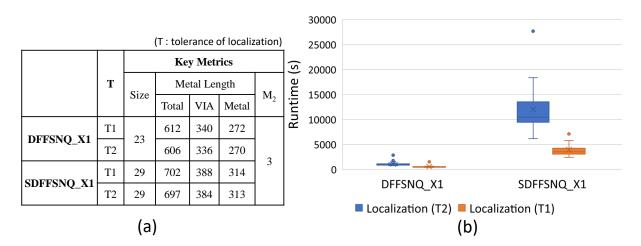

| Figure 5.10: | Statistical runtime visualization of combinational logic cells (21 random seeds).1 | 105      |

| Figure 5.11: | Large sequential cells. (a) Key metrics statistics. (b) Runtime variation          |          |

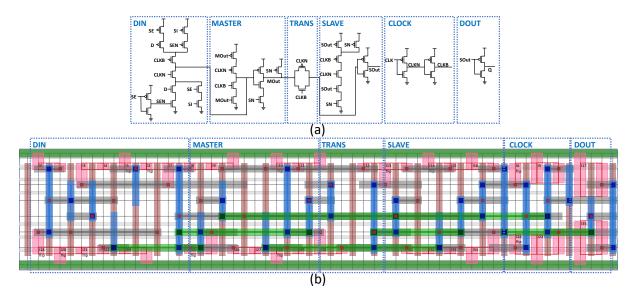

|              | depicted in box plots (21 random seeds)                                            | 105      |

| Figure 5.12: | SDFFSNQ_X1. The largest cell in this work (29 CPPs). (a) Function module           |          |

|              | partitioning. (b) The generated layout (6168 seconds)                              | 106      |

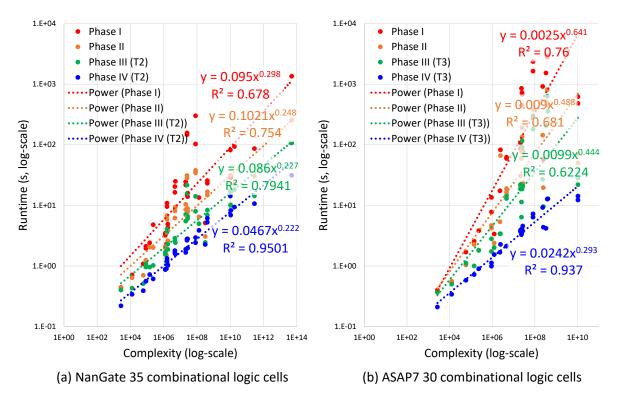

| Figure 5.13: | Scalability of SP&R framework for combinational cells (in log-scale) 1             | 107      |

| Figure 5.14: | An overview of Standard-cell Scaling Framework                                     | 110      |

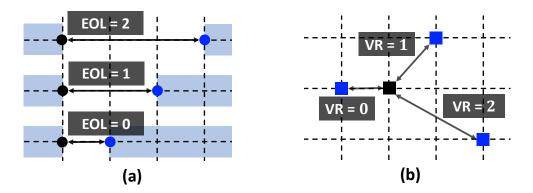

| Figure 5.15: | Examples of parametric design rules. (a) EOL. (b) VR. All number is in grid. 1     | 112      |

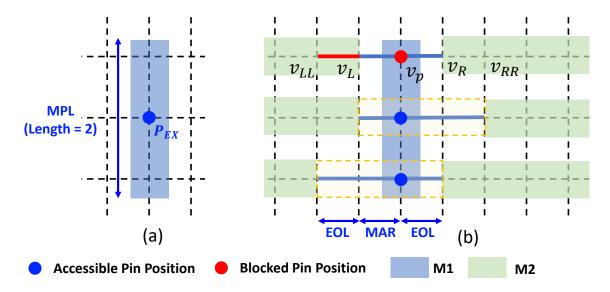

| Figure 5.16: | An example of conditional constraints for the pin-accessibility. (a) MPL rule      |          |

|              | with MAR=2. (b) MPO with EOL/MAR = $1/1$                                           | 113      |

| Figure 5.17: | An example of cell layout with guaranteed pin-accessibility: HA_X1 1               | 115      |

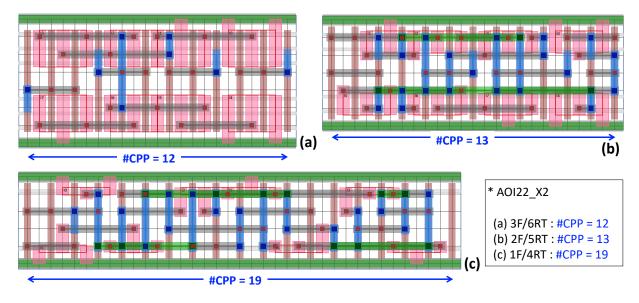

| Figure 5.18: | An example of standard-cell layout with scaled track number: AOI22_X2.             |          |

|              | (a) #CPP = 12 with 3F/6RT. (b) #CPP = 13 with 2F/5RT. (c) #CPP = 19 with           |          |

|              | 1F/4RT. We assume that CPP and MP are fixed                                        | 116      |

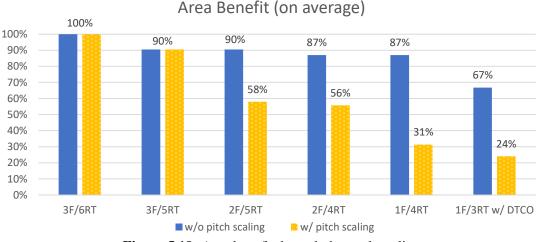

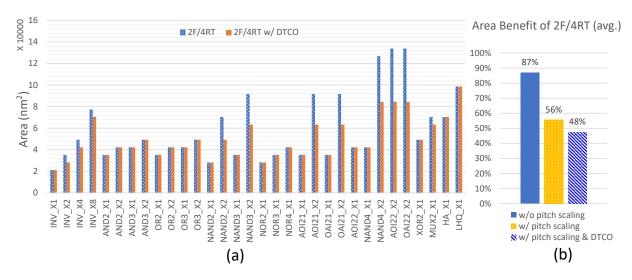

| Figure 5.19: | Area benefit through the track scaling                                             | 117      |

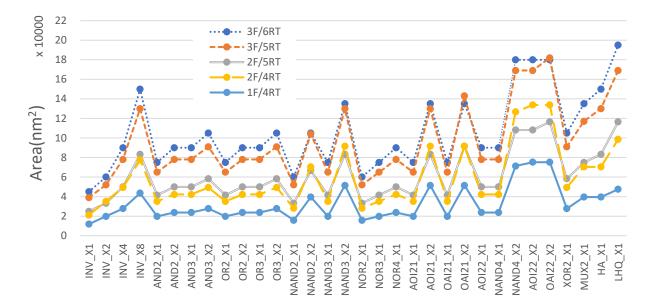

| Figure 5.20: | Area comparison between cell architectures with fixed design rules 1               | 118      |

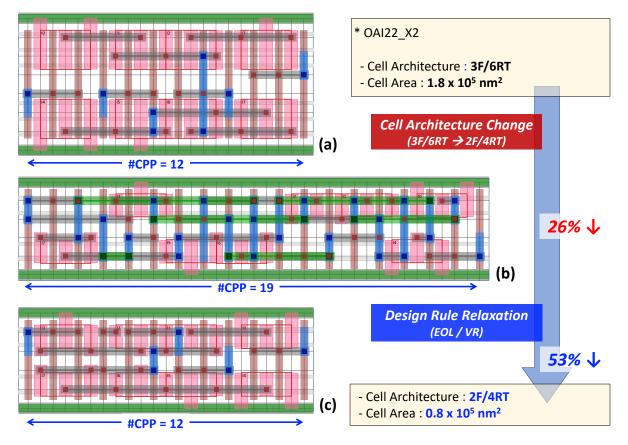

| Figure 5.21: | An example of DTCO: OAI22_X2. (a) Reference architecture. (b) Cell                 |          |

|              | architecture change( $3F/6RT \rightarrow 2F/4RT$ ). (c) Design rule relaxation 1   | 119      |

| Figure 5.22: | Area benefit from DTCO through the design rule relaxation (EOL/VR). (a)            |          |

|              | Statistics for each standard cell. (b) Area benefit on average by utilizing        |          |

|              | 2F/4RT architecture and DTCO                                                       | 120      |

# LIST OF TABLES

| Table 1.1:               | Notations for formulations in this dissertation.                                                                                                                                                                                                                                                                            | 5   |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1:<br>Table 2.2: | Constraint Characteristics                                                                                                                                                                                                                                                                                                  | 30  |

|                          | #Design_rules. $ P  =  T  +  N $ .                                                                                                                                                                                                                                                                                          | 38  |

| Table 2.3:               | Experimental results presenting the ILP-based optimization vs. the SAT-based routability analysis with comparison between [5] and our proposed framework.                                                                                                                                                                   | 42  |

| Table 2.4:               | Experimental results presenting the SAT-based routability analysis using benchmark.                                                                                                                                                                                                                                         | 45  |

| Table 3.1:               | Experimental results presenting the SAT-based routability analysis and diag-<br>nosis using benchmark.                                                                                                                                                                                                                      | 61  |

| Table 4.1:               | Experimental Statistics for SP&R framework                                                                                                                                                                                                                                                                                  | 89  |

| Table 5.1:               |                                                                                                                                                                                                                                                                                                                             | 103 |

| Table 5.2:               | Experimental results presenting the trade-off between scalability and key metrics in $SP\&R$ Framework                                                                                                                                                                                                                      | 103 |

| Table 5.3:               | <i>SP&amp;R</i> results of 142 combinational logic cells from ASAP7 library without FET separation: #Cell = the number of variants of each celltype in column 1, #FET / #NET = the minimum / maximum number of FETs / Nets, $M_2$ = the number of used <i>M</i> 2 tracks, Size/M <sub>2</sub> /Runtime are on average value | 108 |

| Table 5.4:               | <i>SP&amp;R</i> results of 23 sequential logic cells from ASAP7 library : #Cell = the number of variants of each cell in column 1, #FET / #NET = the number of                                                                                                                                                              | 109 |

| Table 5.5:               |                                                                                                                                                                                                                                                                                                                             | 111 |

| Table 5.6:               | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                     | 115 |

#### ACKNOWLEDGEMENTS

I would like to first thank my advisor, Prof. Chung-Kuan Cheng for his encouragement, support and guidance during my Ph.D. I am extremely grateful for his understanding in all aspects of my life, both research and life. I would like to also thank my committee members, Prof. Bill Lin, Prof. Sujit Dey, Prof. Daniel Kane, and Prof. Patrick Mercier for their feedback and discussions related to this Ph.D. work. I would like to thank Professor Namkyoo Park for his academical support and encouragement toward research. A special thanks to Dr. Bong Hyun You for his guidance and encouraging me to pursue a Ph.D during my entire career in Samsung Display. I learned many skills that helped me perform well in my research and work under his guidance.

I would like to thank all my lab colleges in VLSI lab for their active collaboration, help, and all the good memories. I would also like to give special thanks to Ilgweon Kang and Daeyeal Lee. I want to sincerely thank all support from Samsung Display. My research was made possible by funding from Samsung Scholarship.

Most importantly, I owe so much to my wife, Seolyn Ban, my daughter, Siyul Stella, my son, Siwoo, my parents and all my family. I would like to thank them for their endless love and support every day. I could overcome all the difficulties thanks to their understanding, patience, and love.

Chapters 2 and Chapters 3 contain materials from following publications: "Grid-based Framework for Routability Analysis and Diagnosis with Conditional Design Rules", by Dongwon Park, Daeyeal Lee, Ilgweon Kang, Chester Holtz, Sicun Gao, Bill Lin and Chung-Kuan Cheng, which appears in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, February 2020. "ROAD: Routability analysis and diagnosis framework based on SAT technique", by Dongwon Park, Ilgweon Kang, Yeseong Kim, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, which appears in International Symposium on Physical Design, April 2019. The dissertation author was the primary investigator and author of these papers. Chapters 4 contains materials from "SP&R: Simultaneous Placement and Routing framework for standard cell synthesis in sub-7nm", by Dongwon Park, Daeyeal Lee, Ilgweon Kang, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, which appears in IEEE/ACM Asia and South Pacific Design Automation Conference, January 2020. The dissertation author was the primary investigator and author of this paper.

Chapters 5 contains materials from following publications: "Standard-Cell Scaling Framework with Guaranteed Pin-Accessibility", by Chung-Kuan Cheng, Daeyeal Lee, and Dongwon Park, which appears in IEEE International Symposium on Circuits and Systems, October 2020. "SP&R: SMT-based Simultaneous Place-&-Route for Standard Cell Synthesis of Advanced Nodes", by Daeyeal Lee, Dongwon Park, Chiatung Ho, Ilgweon Kang, Hayoung Kim, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, which appears in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, November 2020. The dissertation author was the primary investigator and author of this paper.

### VITA

| 2003         | B. S. in Electrical Engineering, Seoul National University, Korea        |

|--------------|--------------------------------------------------------------------------|

| 2003-2006    | Application Software Engineer, Techserver Co., Korea                     |

| 2009         | M. S. in Electrical Engineering, Seoul National University, Korea        |

| 2009-2012    | Engineer, Samsung Electronics Co., Ltd, Korea                            |

| 2012-Present | Staff Engineer, Samsung Display Co., Ltd, Korea                          |

| 2021         | Ph. D. in Electrical Engineering, University of California San Diego, US |

### PUBLICATIONS

Chung-Kuan Cheng, Andrew B. Kahng, Hayoung Kim, Minsoo Kim, Daeyeal Lee, Dongwon Park, and Minkyu Woo, "PROBE2.0: A Systematic Framework for Routability Assessment from Technology to Design in Advanced Nodes", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, December 2020 (Under Revision) (Alphabetical Order)

Daeyeal Lee\*, Dongwon Park\*, Chiatung Ho, Ilgweon Kang, Hayoung Kim, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, "SP&R: SMT-based Simultaneous Place-&-Route for Standard Cell Synthesis of Advanced Nodes", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, November 2020 \*Contributed Equally

Chung-Kuan Cheng, Chiatung Ho, Daeyeal Lee, and Dongwon Park, "A Routability-Driven Complimentary-FET (CFET) Standard Cell Synthesis Framework using SMT", 2020 International Conference on Computer-Aided Design (ICCAD), November 2020 (Alphabetical Order)

Chung-Kuan Cheng, Daeyeal Lee, and Dongwon Park, "Standard-Cell Scaling Framework with Guaranteed Pin-Accessibility", *IEEE International Symposium on circuits and systems (ISCAS)*, October 2020 (Alphabetical Order)

Dongwon Park, Daeyeal Lee, Ilgweon Kang, Chester Holtz, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, "Grid-based Framework for Routability Analysis and Diagnosis with Conditional Design Rules", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, February 2020

Dongwon Park\*, Daeyeal Lee\*, Ilgweon Kang, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, "SP&R: Simultaneous Placement and Routing framework for standard cell synthesis in sub-7nm", *IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC)*, January 2020 \*Contributed Equally Dongwon Park, Ilgweon Kang, Yeseong Kim, Sicun Gao, Bill Lin, and Chung-Kuan Cheng, "ROAD : Routability Analysis and Diagnosis Framework Based on SAT Techniques", *International Symposium on Physical Design (ISPD)*, April 2019

Ilgweon Kang, Fang Qiao, Dongwon Park, Daniel Kane, Evangeline Fung Yu Young, Chung-Kuan Cheng, and Ronald Graham, "Three-dimensional Floorplan Representations by Using Corner Links and Partial Order", *ACM Transactions on Design Automation of Electronic Systems (TODAES)*, December 2018

Pengwen Chen, Chung-Kuan Cheng, Dongwon Park, and Xinyuan Wang, "Transient Circuit Simulation for Differential Algebraic Systems using Matrix Exponential", 2018 International Conference on Computer-Aided Design (ICCAD), November 2018 (Alphabetical Order)

Ilgweon Kang, Dongwon Park, Changho Han, and Chung-Kuan Cheng, "Fast and precise routability analysis with conditional design rules", *System Level Interconnect Prediction Workshop* (*SLIP*), June 2018

Chung-Kuan Cheng, Ronald Graham, Ilgweon Kang, Dongwon Park, and Xinyuan Wang, "Tree structures and algorithms for physical design", *International Symposium on Physical Design* (*ISPD*), Mar 2018 (Alphabetical Order)

Xiang Zhang, Dongwon Park, and Chung-Kuan Cheng, "Boosting off-chip interconnects through chip-to-chip capacitive coupled communication", *IEEE Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS)*, October 2017

BongHyun You, JaeHoon Lee, SeokHa Hong, Dongwon Park, HyunChang Kim, Deog-Kyoon Jeong, "Current Sensing Self-Compensation System for Gate Driving Circuit Employing Oxide TFTs", *Symposium Digest of Technical Papers (SID)*, May 2016

Bong Hyun You, Jae Sung Bae, Dongwon Park, Seok Ha Hong, Satoru Saito, Ju Tae Moon, "UD Resolution 240Hz LCD TV Display System with High Speed Driving", *Symposium Digest of Technical Papers (SID)*, June 2012

Bong Hyun You, Jae Sung Bae, Jai Hyun Koh, Dongwon Park, Heen Dol Kim, Kook Hwan Ahn, JiSun Kim, Seong Young Lee, SukWon Jung, Yun Jae Kim, Sung Tae Shin, SeokJin Han, Anthony Botzas, Sarah Hwang, Larissa Pan, MoonHwan Im, Candice Brown Elliott, "The Most PowerEfficient 11.6" Full HD LCD Using PenTile Technology for Notebook Application", *Symposium Digest of Technical Papers (SID)*, May 2010

Young Jin Jung, Dongwon Park, Sukmo Koo, Sunkyu Yu, Namkyoo Park, "Metal slit array Fresnel lens for wavelength-scale optical coupling to nanophotonic waveguides", *Optics express*, October 2009

Young Jin Jung, Dongwon Park, Sunkyu Yu, Sukmo Koo, Hyungsuk Yu, Sanghun Han, Namkyoo Park, Jae Hun Kim, Young Min Jhon, Seok Lee, "Metal-slit array fresnel-lens for optical coupling", 2009 International Conference on Numerical Simulation of Optoelectronic Devices(NUSOD), September 2009

### ABSTRACT OF THE DISSERTATION

#### Logical Reasoning Techniques for Physical Layout in Deep Nanometer Technologies

by

Dong Won Park

#### Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California San Diego, 2021

Professor Chung-Kuan Cheng, Chair Professor Bill Lin, Co-Chair

As VLSI technologies are continuously evolving sub-10*nm*, design of the routable and manufacturable layout for integrated circuits (ICs) has been more challenging. To maintain power-performance-area-cost (PPAC) gains from many scaling barriers, IC design demands orchestrated innovations across the entire stages of the design-to-silicon infrastructure. For this design-technology co-optimization (DTCO) in each physical design stage, the holistic exploration is essential across all the design considerations due to the limited resources, high density, and complex conditional design rules. However, many conventional ways focus on divide-and-conquer-style sub-problems and/or heuristic approaches because of the huge search

space of the problem, resulting in limited optimality. In this dissertation, we propose several constraint-based exact solving, i.e., constraint satisfaction problem (CSP), frameworks in various physical design questions related to standard cell placement and routing such as detailed routing, standard cell synthesis, and engineering change order (ECO). Our outcomes have the enhanced optimality compared to conventional approaches due to the concurrent manner between design considerations without any sequential/separate procedures. We utilize/select the appropriate logical reasoning technique, such as Integer Linear Programming (ILP), Boolean satisfiability (SAT), and Satisfiability Modulo Theories (SMT), depending on the problem characteristics.

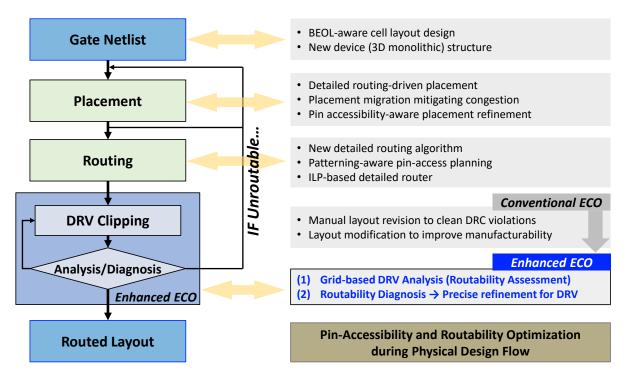

In detailed routing, routability (including pin-accessibility) between standard cells becomes a critical bottleneck due to the limited number of routing tracks, higher pin density, and complex design rules. To reduce turnaround time, we suggest a fast routability analysis framework to analyze routing feasibility by using SAT solving technology. Routability analysis framework produces design rule-correct routability assessment within only 0.02% of ILP runtime on average. Also, we propose a precise routability diagnosis framework to diagnose explicit reasons for design-rule violations (DRVs) in the form of human-interpretable explanations, while specifying conflicting design rules with a physical location.

To maximize PPAC gains in DTCO of standard cell synthesis, the automation of standard cell layout is essential for smooth technology transition. Since many conventional approaches lack the optimality of the cell layout due to the sequential/heuristic manner, we propose a SMT-based automated standard cell synthesis framework, which simultaneously solves place-and-route, through a novel dynamic pin allocation scheme without deploying any sequential/separate operations. After tackling the scalability by developing various search-space reduction techniques, our framework successfully generates a whole set of 7*nm* standard cell library. On top of complete cell libraries, we propose standard cell scaling framework which enables the parametric study of standard cell layout with respect to the scaled cell architectures. In particular, we strictly ensure the pin-accessibility of the cell layout, which is intrinsically restricted by limited track number,

through our novel Boolean constraints, while maintaining the scaling advantages.

# Chapter 1

# **Introduction and Preliminaries**

In the past decades, semiconductor technologies have significantly contributed to the human society, and led entire industries toward more advanced systems with evolution of integrated circuits (ICs). Innovations and advancements on physical design (PD) guide progresses of modern VLSI designs and the automation. By virtue of the PD community and their efforts, the power-performance-area-cost (PPAC) of ICs has been extremely enhanced, the overall industry has been profitable, and the global semiconductor market size has been grown dramatically for the past decades. Although innovations of VLSI technologies, semiconductor industry has failed to manage development (i.e., design and verification) cost due to the time-consuming turnaround time of iterative design procedures as shown in Figure 1.1. Design for the routable and manufacturable layout in advanced technologies is no more trivial due to complex design considerations such as limited resources, high density, and complex design rules.

As shown in Figure 1.2, allowable tracks of standard cell has been reduced from 9T at 20*nm* node in 2012 to 6T at 7*nm* node in 2019 and is predicted to be 5T or even below for 3*nm* node in the near future. To maintain PPAC gains from the scaling barriers, IC design demands orchestrated innovations across the entire manufacture stages of the design-to-silicon infrastructure. For this design-technology co-optimization (DTCO), the holistic exploration is

Figure 1.1: Design technology crisis [1]

Figure 1.2: Scaling road map [2].

essential across all the design considerations of combined physical design stages. However, as we know, physical design for manufactureable IC layout is divided into many stages as depicted in Figure 1.3. This sequential design process is inevitable, because each subproblem

Figure 1.3: Physical design stages and the targets of this dissertation.

already requires an enormous search space due to the combinatorial searching for the millions of transistors. What was worse, some subproblem (e.g., placement or routing) is divided into further hierarchical/sequential sub-procedures such as global placement (GP), detailed placement (DP), global routing (GR), and detailed routing (DR). Therefore, many conventional works focus on divide-and-conquer-style and/or heuristic approaches due to the intrinsic scalability limitation of the problem. As a result, outcomes of these approaches are hard to reach the optimal solution due to the intractable search space partitioning and heuristic manner.

In this dissertation, we propose several exact solving methodologies and its automation for place-and-route problems in both in-cell (i.e., standard cell synthesis) and inter-cell (i.e., DR stage) across advanced technology nodes (i.e., sub-10*nm*), which have better optimality compared to the conventional approaches, through multi-objective optimization based on constraint-based design considerations. In other words, our problems (in both standard cell synthesis and detailed routing stage) are particular forms of constraint satisfaction problem (CSP), the subject of intense research in artificial intelligence (AI). We convert practical DFM(Design for manufacturability)related considerations in both placement and routing stages into either constraint or objectives to find better PPAC solutions. Then, for the resolution of CSP, we utilize the state-of-the-art solver of Integer Linear Programming (ILP), Boolean satisfiability (SAT), and Satisfiability Modulo Theories (SMT). To ensure the practical scalability of the framework from intrinsic complexity explosion of exact solving, we enrich/refine our constraints by developing efficient search space pruning techniques (e.g., breaking symmetry, conditional assignment using logical constraint), by adopting efficient representations (e.g., Boolean cardinality constraint and its encodings). As a consequence, we achieve the practical scalability of our framework for each target criteria. With this in mind, in the remaining Chapter 1, we introduce ILP, SAT, and SMT for its concept and several features/techniques utilized in this dissertation. Also, we describe basic foundations of our frameworks for placement and routing optimization. Then, this dissertation present new methodologies and its automated framework in three topics of physical design; (i) routability analysis and diagnosis in detailed routing (Chapter 2,3), (ii) standard cell synthesis (Chapter 4), and (iii) parametric standard cell scaling study for DTCO (Chapter 5)

The rest of this chapter is organized as follows. Section 1.1 introduces ILP and its usages in detailed routing. Section 1.2 introduces SAT and its techniques to refine the complexity of CNF (conjunctive normal form) representation. Section 1.3 introduces SMT and its general technique to reduce the solving complexity. Section 1.4 describes basic foundations of our frameworks. Table 1.1 presents the notations.

# 1.1 Integer Linear Programming (ILP) for Routing

Linear programming (LP) is a sort of optimization technique for a linear objective function, which are subject to linear equality and linear inequality constraints. If all variables in

<sup>&</sup>lt;sup>1</sup>The symbol d is L (Left), R (Right), F (Front), B (Back), U (Up), D (Down), or a combination of these directions, e.g., FL means FrontLeft.

| Description                                                            |

|------------------------------------------------------------------------|

| The number of vertical tracks in the given routing (cell bounding) box |

| The number of horizontal tracks in the given routing box               |

| Set of FETs                                                            |

| t <sup>th</sup> FET                                                    |

| 0-1 indicator if FET t is flipped                                      |

| <i>x</i> -axis coordinate of lower-left corner of <i>t</i>             |

| Width (or height) of FET <i>t</i>                                      |

| Set of internal pins of FET t                                          |

| $i^{th}$ pin of FET $t$                                                |

| Net information of pin <i>p</i>                                        |

| Three-dimensional (3-D) routing graph                                  |

| Set of vertices in $(i^{th}$ metal layer of) the routing graph G       |

| A vertex with the coordinate $(x_v, y_v, z_v)$                         |

| A <i>d</i> -directional <sup>1</sup> adjacent vertex of $v$            |

| Set of adjacent vertices of v                                          |

| Cost for metal segment on $e_{v,u}$                                    |

| Set of edges in the routing graph G                                    |

| An edge between $v$ and $u$ , $u \in a(v)$                             |

| Weighted cost for metal segment on $e_{v,u}$                           |

| Set of multi-pin nets in the given routing box                         |

| <i>n<sup>th</sup></i> multi-pin net                                    |

| A source of <i>n</i>                                                   |

| Set of sinks of <i>n</i>                                               |

| $m^{th}$ sink of $n$                                                   |

| A two-pin subnet connecting $s^n$ and $d_m^n$ , i.e., a commodity      |

| 0-1 indicator if v is used for n                                       |

| 0-1 indicator if $e_{v,u}$ is used for <i>n</i>                        |

| 0-1 indicator if $e_{v,u}$ is used for commodity $f_m^n$               |

| 0-1 indicator if there is a metal segment on $e_{v,u}$                 |

| Capacity variable for $e_{v,u}$ of commodity $f_m^n$                   |

| 0-1 indicator if v forms d-side EOL of a metal segment                 |

|                                                                        |

Table 1.1: Notations for formulations in this dissertation.

linear programming are restricted to be integer, such problems are called ILP (integer linear programming) as expressed in (1.1).

Minimize

$$c^T x$$

Subject to  $Gx \le h$  (1.1)

$x \in \mathbb{Z}$

Since the search space of integer variable's domain is discrete, the problem of ILP is a non-convex problem. Therefore, exhaustive combinatorial searching is required to achieve the optimal solution. The popular method for solving ILP is "Branch and Bound". After quickly finding optimal solution (but, non-integer) of LP, "relaxation" of ILP without integer constraints, several efficient searching algorithms (including "Branch and Bound") are executed to find minimized integer solution with respect to object function in state-of-the-art ILP solvers [6, 7].

## 1.1.1 Binarized/Undirected Multi-Commodity Network Flow theory

By virtue of its ability to obtain optimal solutions, ILP-based optimization has been widely applied to physical design. Previous works successfully describe ILP-based detailed routing formulation for standard cell synthesis [8] and detailed routers [9, 10] based on popular multi-commodity network flow theory (MCNF) [11]. Recently, Kang *et al.* [5, 12] proposed a binarized MCNF formulation to define source-sink connectivity of each net at a per-commodity granularity (so-called *SAT-friendly ILP*). Inspired by [5, 12], we propose further refined MCNF without flow direction as shown in (1.2), resulting in fully binarized formulation (i.e., binary integer linear programming).

$$f_m^n(v,u) = f_m^n(u,v), \quad No \text{ Direction}$$

(1.2)

Since ILP formulation has been fully binarized, we are able to precisely convert/compare ILP formulation to SAT formulation. This is presented in Chapter 2.

# 1.2 Boolean Satisfiability (SAT) for Detailed Routing

The Boolean Satisfiability (SAT) technique is one of the most successful automated logical reasoning methods in computer science including artificial intelligence (AI). A wide range of practical and challenging questions have been encoded to SAT formulas. A proposition logic formula of SAT consists of variables, AND (i.e., conjunction), OR (i.e., disjunction), and NOT (i.e, negation). The SAT problem is, given a proposition logic formula, to find a variable assignment to make formula evaluates to 1 (i.e., Satisfiable), or prove that no such assignment exists (i.e., Unsatisfiable). The CNF (i.e., product of sum), a conjunction of clauses<sup>2</sup>, is basic input format for most of state-of-the-art SAT solvers.

By virtue of SAT's fast reasoning, SAT techniques are widely applied in physical design. However, adopting SAT has been limited to standard cell routing [13], escape routing [14], and special-purpose ICs (e.g., FPGA [15, 16] and cross-referencing biochip [17]) due to the high complexity of expressing "countable" design metrics and constraints in DR problems incorporating complex conditional design rules. Recently, Kang *et al.* [5, 12] proposed a SAT-based routability analysis framework with design rule-correct assessment, resulting in fast routability analysis for early "go/no-go" decision. Although the SAT-based routability analysis is feasible in physical design, further work is still open in terms of practical scalability. Furthermore, once we identify the routability, the diagnosis remains an open problem for physical designers.

In this dissertation, we propose a light-weight CNF representation of routability analysis framework to achieve better practicality (Chapter 2). Also, we propose a framework precisely diagnoses explicit reasons for DRVs in the form of human-interpretable explanations while specifying conflicting design rules with a physical location. It means that our routability diagnosis framework is a a special version of SAT solver for describing DRVs expertly. (Chapter 3). The rest of this section, we introduce several SAT techniques for the complexity refinement and the

<sup>&</sup>lt;sup>2</sup>A *literal* is either a variable (i.e., *positive literal*) or the negation of a variable (i.e., *negative literal*). A *clause* is a disjunction of literals (or a single literal).

diagnosis.

### **1.2.1 SAT Encodings for Boolean cardinality constraint**

Since we utilize MCNF as the foundation of our routing formulation, the majority of our formulation is exclusiveness constraint such as vertex and edge exclusiveness. Furthermore, we adopt geometric variable-based exclusiveness to ensure conditional design rules [5, 12]. In SAT problem, encoding for these exclusiveness (i.e., Boolean cardinality) constraints is non-trivial problem in terms of an efficient CNF representation. For instance, vertex indicator  $v^n$  in our formulation is restricted by vertex exclusiveness as shown in (1.3).

$$\sum_{n \in \mathbb{N}} v^n \le 1, \quad \forall v \in \mathbb{V}, \ v \ne s^n, d_m^n$$

(1.3)

This at-most-1 (i.e., "**AM1**") constraint can be encoded to CNF representation using *binomial* encoding<sup>3</sup> as expressed in (1.4).

$$\bigwedge_{i=1}^{n-1} \bigwedge_{j=i+1}^{n} \neg \left( v^{i} \wedge v^{j} \right) \equiv \bigwedge_{i=1}^{n-1} \bigwedge_{j=i+1}^{n} \left( \neg v^{i} \vee \neg v^{j} \right)$$

(1.4)

Although *binomial* encoding for **AM1** is straightforward, it is not efficient in terms of the CNF formula because  $\binom{n}{2}$  clauses are required to represent all possible combinations of two variables. Accordingly, intensive studies for the efficient CNF representation of **AM1** are reported [18, 19]. In our routing analysis, we apply *commander* encoding [20] which has the most refined complexity (in our problem) in terms of clause number. In a running example set  $X = \{x_1, x_2, x_3, x_4, x_5, x_6, x_7, x_8, x_9\}$ , the *binomial* encoding requires  $\binom{9}{2} = 36$  clauses (i.e., the

<sup>&</sup>lt;sup>3</sup>This encoding scheme has several different names such as *binomial*, *pairwise* and *naïve*.

clause complexity is  $O(n^2)$  in CNF as described in (1.4). Meanwhile, the *commander* encoding with three disjoint subsets  $G_1 = \{x_1, x_2, x_3\}$ ,  $G_2 = \{x_4, x_5, x_6\}$ , and  $G_3 = \{x_7, x_8, x_9\}$ , and three commander variables  $c_1$ ,  $c_2$ , and  $c_3$  requires three exactly-1<sup>4</sup> (i.e., "E1") for each group and one AM1 for commander variables (i.e., total 24 clauses and the clause complexity is O(n)) as described in (1.5) and (1.6).

$$\bigwedge_{i=1}^{3} \mathbf{E1}(\{\neg c_i\}, G_i) = \bigwedge_{i=1}^{3} \left( \mathbf{AM1}(\{\neg c_i\}, G_i) \land \mathbf{AL1}(\{\neg c_i\}, G_i) \right) : 21 \ clauses$$

(1.5)

binomial

$$AM1(c_1, c_2, c_3)$$

: 3 clauses (1.6)

This is presented in Chapter 2.

### **1.2.2** Boolean Constraint Propagation (BCP)

BCP (Boolean Constraint Propagation), also called unit propagation, is the basic procedure of most of SAT solver to meet the conflict and reduce clause complexity [21]. Using unit clauses (i.e., clauses that have only one literal.), BCP is executed, resulting in the simplified CNF representation. If a set of clauses contains the unit clause *a*, the other clauses are simplified by two following rules.

- Every clause containing *a* literal is removed (i.e., the clause is satisfied regardless of other literals.).

- In every clause,  $\neg a$  literal is deleted (i.e.,  $\neg a$  does not contribute the satisfiability of the clause containing  $\neg a$ .).

<sup>&</sup>lt;sup>4</sup>Exactly-1 (E1) is the conjunction of at-most-1 (AM1) and at-least-1 (AL1).

BCP procedure is recursively executed until the repeatedly simplified set of clauses has no more unit clauses. A running example illustrates this BCP procedure in Figure 1.4.

**Figure 1.4**: An example of (a) SAT formula  $\sum$ , and (b) the associated implication graph through BCP.

In the running example, the SAT formula  $\sum$  consists of 5 clauses including one unit clause (i.e.,  $c_5$ ) as shown in Figure 1.4(a). At the first iteration  $i_1$  of BCP, two unit clauses (i.e.,  $c_1$  and  $c_3$ ) are generated and one clause (i.e.,  $c_2$ ) is removed from the formula. In the next iteration  $i_2$ of BCP, one unit clause (i.e.,  $c_4$ ) is generated. As a result, the satisfiable variable assignment  $S_{\sum}$ (i.e.,  $(a, b, \neg c, d)$ ) is found. Furthermore, the implications between variables is identified through BCP as depicted in Figure 1.4(b).

In this dissertation, we utilize the BCP procedure as a built-in SAT pre-processor in our routability analysis framework to refine the complexity of CNF representation (Chapter 2). Furthermore, we utilize DAG (directed acyclic graph)-based implication graphs for identifying the root cause of the conflict, while our routability diagnosis framework is specifying conflicting design rules (Chapter 3).

### **1.2.3** Minimal Unsatisfiable Subset (MUS)

A MUS (Minimal Unsatisfiable Subset) is a clause subset of an infeasible constraint formula which is both unsatisfiable and not able to make smaller without becoming satisfiable [22, 23]. In other words, an unsatisfiable subset of infeasible formula is MUS if all its proper subsets are satisfiable. For example, a given infeasible formula  $\sum_U$  as shown in Figure 1.5(a), possible MUSes are  $\{c_2, c_4\}$  and  $\{c_1, c_2, c_3\}$  as extracted in Figure 1.5(b).

**Figure 1.5**: An example of (a) infeasible SAT formula  $\sum_U$ , and (b) the corresponding MUSes.

In our routability diagnosis framework, this MUS significantly contributes the diagnosis time reduction by replacing the diagnosis target with the very small number of original clauses. This is presented in Chapter 3.

# 1.3 Satisfiability modulo theories (SMT) for Standard Cell Layout

Based the fast reasoning ability of SAT, SMT (Satisfiability modulo theories) methodologies empowers us to represent more expressive language containing non-Boolean variables (e.g., integer, bit-vector, etc.) and predicate symbols [24]. With ILP and SAT, SMT is also a successful logical reasoning technique in various applications of computer science such as microfluidic platform [25], cyber-physical system [26, 27], vehicle routing [28], , analog placement [29]. and floorplanning of VLSI physical design [30]. Recently, several state-of-the-art SMT solvers with the optimization methodology (so-called "OMT") are released [31, 32].

In this dissertation, we utilize SMT to represent the standard cell layout design problem because SMT-based methodologies support a much richer modeling language than SAT or ILP formulas. For example, logical constraints (e.g., "if-then-else" for the "Either-Or" constraint) are able to be easily implemented by "ITE" keyword, meanwhile ILP formula requires additional auxiliary variables for logical constraints. Furthermore, an state-of-the-art SMT solver [31] include built-in Boolean cardinality functions such as at-most k (i.e., "**AMk**") and at-least k (i.e., "**ALk**") as introduced in Section 1.2.1. This is represented in Chapter 4.

For the generation of a whole set of a standard cell library, we propose various tactics to mitigate the intrinsic scalability limitation of the exact solving. The rest of this section introduces one of our approaches to prune search space based on solution symmetry. This scheme is utilized in Chapter 5.

# **1.3.1** Breaking symmetry predicates

To extend the scalability in a combinatorial solving similar to our problem (i.e, the CSPbased exact solving for the optimization), many previous works suggest breaking symmetry predicates as additional constraints to prune the symmetry search space [33, 34, 35]. If the formula preserves the theory (i.e., satisfiability and optimization results in our problem) in spite of permutation of variable assignment, its variable permutation denotes the symmetry in the search space. And then, we never want to visit more than one of them. For this symmetry, we can "break" the symmetry by adding a constraint with logical implication between variables (e.g.,  $a \implies b$ for interchangeable variables a and b). This logical implication construct a lexicographic order on the set of assignments (i.e.,  $a \le b$  for interchangeable variables a and b). Therefore, the search space, not following the constructed order (i.e., a > b), will be pruned during the solving. In our standard cell layout generation, the solutions of the transistor placement have a few symmetries. This is presented in Chapter 5.

# **1.4** Preliminaries of Framework Configurations

As manufacturing technology nodes continuously evolve into sub-10*nm*, routing between standard cell in DR stage has become more challenging due to scaling barriers such as higher pin density and resolution limitations of optical lithography [9, 36, 37]. Although multi-patterning techniques such as LELE (litho-etch-litho-etch), SADP and SAQP (self-aligned double and quadruple patterning) enable the manufacturing of sub-10*nm* technology nodes [38, 39, 40], these approaches induce more complex conditional design rules and restricts routing wires to grid-based (i.e., on-grid) unidirectional routing track due to the process resolution. Therefore, the grid based technology fits the ILP, SAT and SMT methodology (i.e., reasoning techniques for discrete models) proposed in this dissertation. With this in mind, the rest of this section introduce our framework configurations related to routing graph definition, supernode for source and sink connectivity, and boolean cardinality constraint for conditional design rules.

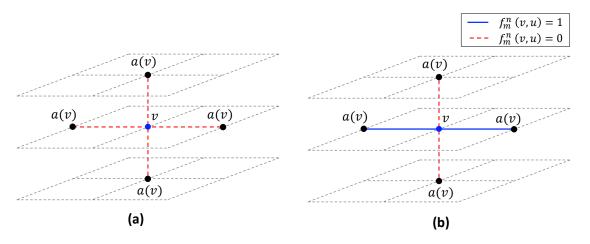

## **1.4.1** On-grid Unidirectional Routing Graph: G(V, E)

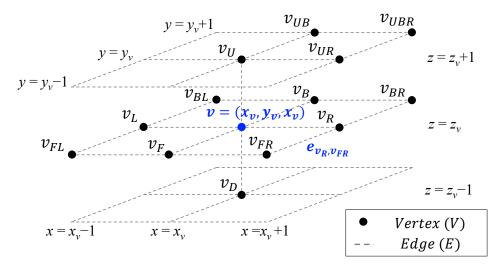

We use a multiple metal layered routing graph G = (V, E) to represent available routing resources (e.g., horizontal and vertical tracks on multiple metal layers, inter-layer vias) and routing between sources and sinks. Each vertex v is mapped to coordinates  $(x_v, y_v, z_v)$ , where x, y, and z are induced from horizontal routing tracks, vertical routing tracks, and metal layer, respectively as depicted in Figure 1.6. Each edge  $e_{v,u}$  between vertex v and vertex u represents flow with capacity one, including inter-layer vias.

## 1.4.2 Supernode

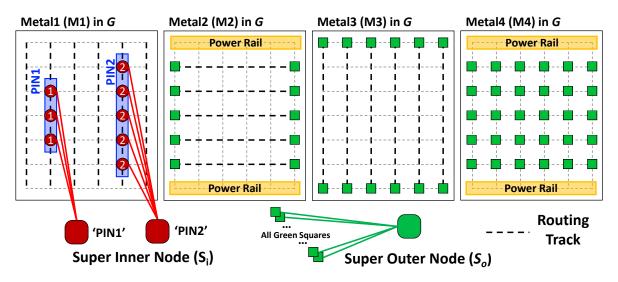

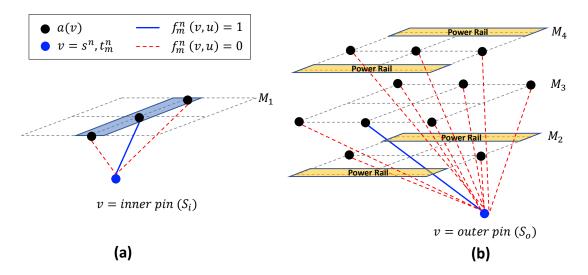

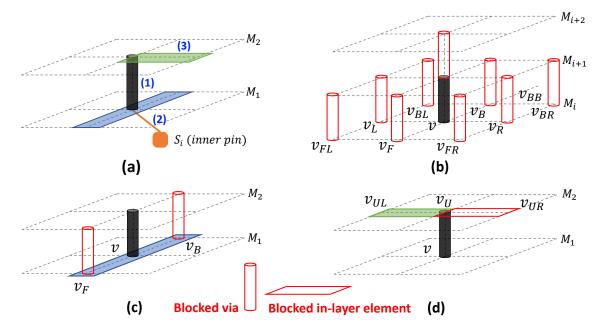

For the consistency of our MCNF formulation, we adopt supernode to group multiple feasible pin locations as [10, 5, 12]. Figure 1.7 illustrates supernodes in G. A supernode for a pin on M1 (i.e., inner pin) is connected to vertices covering the pin (red circles on *PIN*1 and *PIN*2).

**Figure 1.6**: An example of grid-based routing graph, G(V, E).

A supernode for a pin connected to vertices at the boundary of G (i.e., outer pin) is depicted in Figure 1.7 (green squares). Using supernode composition, each commodity consists of one source and one sink as supernode, respectively. In particular, our supernode for outer pins (i.e., Super Outer Node  $S_o$ ) abstracts all supernodes of outer pins so that our framework has only one set of variables for the supernode (i.e., shared supernode). Thus, the complexity of exclusiveness-related constraint is reduced compared to [5, 12]. Note that we denote the pin on M1 by Super Inner Node  $S_i$  to distinguish from  $S_o$ .

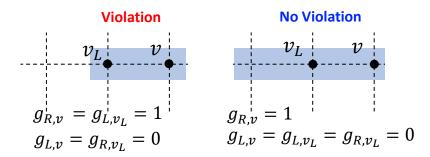

# 1.4.3 Geometric variable for conditional design rules

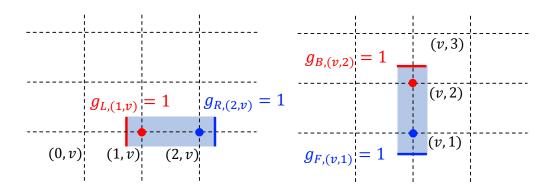

We adopt geometric variable (GV)  $g_{d,v}$  determined by the EOL of a metal segment as shown in the Constraint (1.7).

$$g_{L,v} = \neg m_{v_L,v} \wedge m_{v,v_R}, \qquad \forall v \in V_2$$

$$g_{R,v} = m_{v_L,v} \wedge \neg m_{v,v_R}, \qquad (1.7)$$

Figure 1.8 shows an example to determine  $g_{d,v}$ . Since the left-/back- and right-/front-directional

**Figure 1.7**: Supernodes. *PIN*1 and *PIN*2 respectively cover three and five vertices on *M*1 layer (i.e., inner pin). Outer pins are connected to boundary vertices of *G* through Super Outer Node  $(S_o)$ .

EOLs (depicted in red and blue bars) are respectively located at (1,v)/(v,2) and (2,v)/(v,1),  $g_{L,(1,v)}/g_{B,(v,2)} = 1$  and  $g_{R,(v,2)}/g_{F,(v,1)} = 1$ . We convert logical Constraint (1.7) into linear Constraint (1.8) since  $x \wedge y = z \Leftrightarrow z \leq x, z \leq y, z \geq x + y - 1$  and  $\neg x \Leftrightarrow 1 - x$ , as described in [9]. The front- and back-directional GV are derived by changing *L* and *R* to *F* and *B*, respectively.

$$g_{L,v} \leq 1 - m_{v_{L},v} ; g_{L,v} \leq m_{v,v_{R}} ; g_{L,v} \geq m_{v,v_{R}} - m_{v_{L},v}$$

$$g_{R,v} \leq m_{v_{L},v} ; g_{R,v} \leq 1 - m_{v,v_{R}} ; g_{R,v} \geq m_{v_{L},v} - m_{v,v_{R}}$$

(1.8)

With GVs, we are able to represent all conditional design rules as the **AM1** constraint, which is the simplified boolean cardinality constraints. With this simple representation for conditional design rules, we can easily add new kinds of design rules into our framework without significant burdens in terms of complexity.

**Figure 1.8**: An example to determine geometric variable  $g_{d,v}$ .

## Chapter 2

# Detailed Routing: Routability Analysis and Optimization Framework

## 2.1 Introduction