#### **UC Santa Cruz**

#### **UC Santa Cruz Electronic Theses and Dissertations**

#### **Title**

Design and Analysis of Robust Variability-Aware SRAM to Predict Optimum Access-Time to Achieve Yield Enhancement in Future Nano-Scaled CMOS.

#### **Permalink**

https://escholarship.org/uc/item/9pv711jz

#### **Author**

Samandari-Rad, Jeren

#### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SANTA CRUZ

## DESIGN AND ANALYSIS OF ROBUST VARIABILITY-AWARE SRAM TO PREDICT OPTIMAL ACCESS-TIME TO ACHIEVE YIELD ENHANCEMENT IN FUTURE NANO-SCALED CMOS

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

**ELECTRICAL ENGINEERING**

by

Jeren Samandari-Rad

December 2012

|              | is approved:                    |

|--------------|---------------------------------|

|              | Professor Richard Hughey, Chair |

|              | Professor Sung Mo (Steve) Kang  |

|              | Professor Jose Renau            |

| Tyrus Miller |                                 |

Vice Provost and Dean of Graduate Studies

The Dissertation of Jeren Samandari-Rad

Copyright © by

Jeren Samandari-Rad

2012

## **Table of Contents**

| Li | st of Figures                                                                                                                                                                                                               | vii                                              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Li | st of Tables                                                                                                                                                                                                                | xi                                               |

| Ał | ostract                                                                                                                                                                                                                     | xii                                              |

| De | dication                                                                                                                                                                                                                    | xiv                                              |

| Ac | knowledgments                                                                                                                                                                                                               | xv                                               |

| I  | Introduction                                                                                                                                                                                                                | 1                                                |

| 1  | Motivations                                                                                                                                                                                                                 | 2                                                |

| 2  | Literature Review  2.1 Classical Models  2.2 More Advanced Models  2.3 Current/Recent Models  2.3.1 Limitation on Parallel Slicing  2.3.2 Limitation on Slice Width  2.3.3 Limitation on the Operation Region  Contribution | 7<br>8<br>9<br>12<br>23<br>23<br>25<br><b>28</b> |

| II | SRAM Architecture, Operation, and Design Considerations                                                                                                                                                                     | 36                                               |

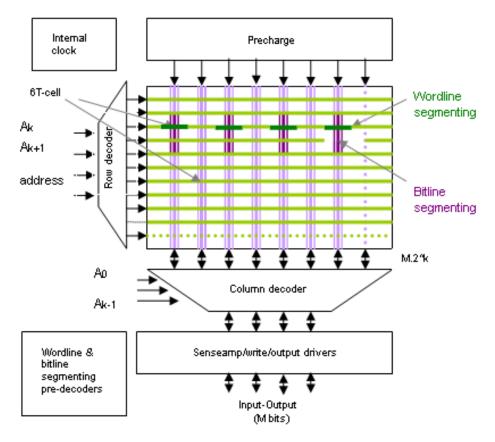

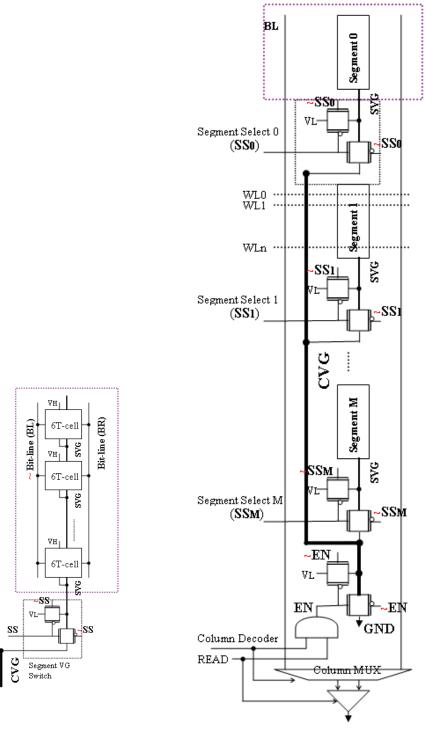

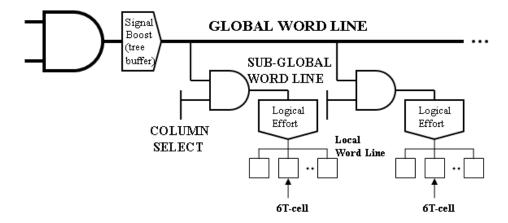

| 4  | Hierarchical Memory Architecture  4.1 6T-cell Structure and Operation                                                                                                                                                       | 37<br>38<br>39<br>41<br>43                       |

| 5  | SRA  | М Оре  | eration                                                          | 47  |

|----|------|--------|------------------------------------------------------------------|-----|

|    | 5.1  | Read.  |                                                                  | 50  |

|    | 5.2  | Write  |                                                                  | 51  |

|    | 5.3  | Access | s-time                                                           | 52  |

|    | 5.4  |        |                                                                  |     |

|    |      |        |                                                                  |     |

| II | I SI | RAM D  | Design Considerations and Analysis                               | 55  |

| 6  | Desi | gn Con | siderations and Analysis, Device                                 | 61  |

|    | 6.1  | D2D a  | nd WID variations                                                | 61  |

|    | 6.2  |        | Noise Margin (SNM)                                               |     |

|    |      | 6.2.1  | Hold Noise Margin                                                | 73  |

|    |      | 6.2.2  | Read Noise Margin                                                | 74  |

|    |      | 6.2.3  | Write Noise Margin                                               |     |

|    | 6.3  | Soft E | rror                                                             |     |

|    | 6.4  | Negati | ve Bias Temperature Instability (NBTI)                           | 77  |

|    |      | 6.4.1  | Supply Voltage and Temperature Dependence                        | 89  |

|    |      | 6.4.2  | Input Control in Static and Dynamic Operation                    |     |

|    |      | 6.4.3  | Impact of NBTI on Process/Design)                                | 95  |

|    | 6.5  | Hot-Ca | arrier Injection (HCI)                                           | 98  |

|    | 6.6  | Single | Electron Tunneling (SET)                                         | 100 |

| 7  | Desi | gn Con | siderations and Analysis, Power                                  | 102 |

|    | 7.1  | _      | t of Temperature on Delay, Power, and Performance                | 102 |

|    | 7.2  | •      | erature and Voltage Variation                                    |     |

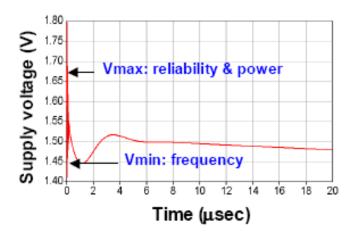

|    |      | 7.2.1  | Supply Voltage Variation                                         |     |

|    |      | 7.2.2  | Temperature Variation                                            |     |

|    |      | 7.2.3  | PVT Variations and their Reduction Techniques                    |     |

|    | 7.3  | IR-Dro | op, EM, and $Ldi/dt$                                             |     |

|    | 7.4  |        | onnect Challenges                                                |     |

|    |      | 7.4.1  | Overview of Interconnect                                         |     |

|    |      | 7.4.2  | Requirements of the interconnection materials                    |     |

|    |      | 7.4.3  | Progress Trend and Future of Interconnect                        |     |

|    |      | 7.4.4  | SPICE Model and Performance Metrics                              |     |

|    |      | 7.4.5  | Existing and Future Interconnects                                |     |

|    |      | 7.4.6  | Performance comparison between Cu/low-k, m-SWCNT Bundle, and     |     |

|    |      |        | Optical Interconnects                                            | 166 |

|    |      | 7.4.7  | Capacitively Driven Low-Swing Interconnect (CDLSI)               |     |

|    |      | 7.4.8  | Performance comparison between CDLSI, Cu/low-k, CNT, and Optical |     |

|    |      |        | Interconnects                                                    | 174 |

|    | 7.5  | Maior  | Techniques for Leakage Control in Caches/SRAMs                   |     |

|    | -    |        | Lowering the Oviescent Vdd (Gated-Vss)                           | 177 |

|             | 7.5                         | .2 Multiple Threshold CMOS (MTCMOS)                | 177                             |

|-------------|-----------------------------|----------------------------------------------------|---------------------------------|

|             | 7.5                         | •                                                  |                                 |

| 7           | '.6 Po                      | wer, Leakage, and Energy Delay                     | 178                             |

|             | 7.6                         |                                                    |                                 |

|             | 7.6                         | 1                                                  |                                 |

|             | 7.6                         | 1                                                  |                                 |

|             | 7.6                         | •                                                  |                                 |

|             | 7.6                         |                                                    |                                 |

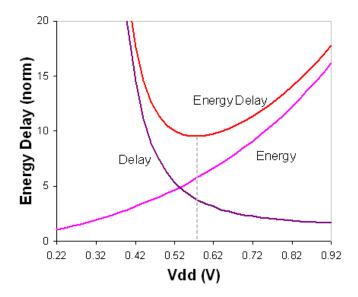

|             | 7.6                         | .6 Energy-Delay Product                            | 193                             |

| IV          | Failu                       | re in SRAM                                         | 197                             |

| 8 F         |                             | in SRAM                                            | 198                             |

| 8           | 3.1 SF                      | AM cell failure                                    | 200                             |

|             | 8.1                         | .1 Read Failure                                    | 20                              |

|             | 8.1                         |                                                    | 20                              |

|             | 8.1                         | .3 Access Failure                                  | 20                              |

|             | 8.1                         | .4 Hold Failure                                    | 20                              |

| 8           | 3.2 M                       | odeling Timing Errors                              | 20                              |

|             | 8.2                         | .1 Our General Approach and Assumptions            | 20                              |

|             | 8.2                         | .2 Timing Errors in SRAM Memory                    | 21                              |

| V           | Propo                       | sed Model: VAR-TX                                  | 21                              |

| 9 (         | )ur Pro                     | posed Model                                        | 21.                             |

| 9           | ).1 De                      | rivation of access-time and its variation          | 21                              |

|             | 9.1                         | .1 D2D variability analysis                        | 22                              |

|             | 9.1                         | .2 WID variability analysis                        | 22                              |

|             | 9.1                         | .3 Combined WID and D2D analysis                   | 23                              |

| 9           | .2 Inc                      | orporating leakage, power, and area                | 23                              |

| 9           | 0.3 M                       | odel assumptions and implementation                | 23                              |

| 9           |                             | odel optimization                                  | 23                              |

| 9           | 0.5 Ho                      | w to use the model                                 | 23                              |

|             |                             |                                                    |                                 |

| VI          | Expe                        | imental Results                                    | 23                              |

|             | •                           | rimental Results ion Results and Analysis          |                                 |

| 10 S        | -<br>Simulat                | ion Results and Analysis                           | 23                              |

| <b>10 S</b> | Simulat<br>0.1 Ve           | ion Results and Analysis rification by Monte-Carlo | <b>23</b> 23                    |

| 10 S        | Simulat<br>0.1 Ve<br>0.2 Va | ion Results and Analysis                           | 23:<br>23:<br>23:<br>24:<br>24: |

| 10.3.2                                    | Cumulative $V_{th}$ , $L$ , and $V_{dd}$ Variability                       | 248 |

|-------------------------------------------|----------------------------------------------------------------------------|-----|

| 10.3.3                                    | Individual $V_{th}$ , $L$ , & $V_{dd}$ Variations                          | 252 |

| 10.3.4                                    | Wordline vs. Bitline Variability                                           | 255 |

| 10.3.5                                    | Bank Variability                                                           | 257 |

| 10.3.6                                    | FMAX Mean Variability                                                      | 261 |

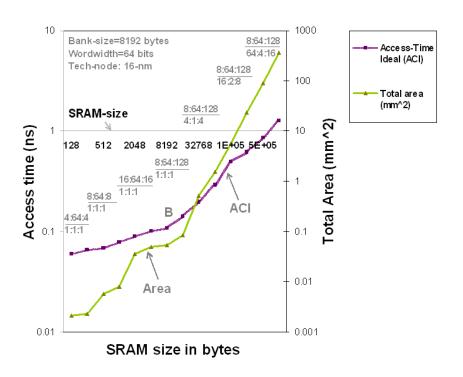

| 10.3.7                                    | Area vs. SRAM size                                                         | 263 |

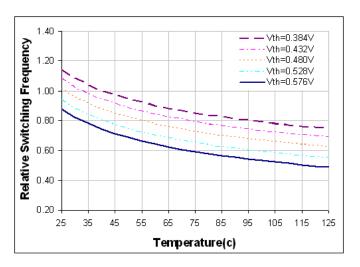

|                                           | Temperature Impact on Relative Switching Frequency                         |     |

| 10.4 Power                                | Simulation Results and Analysis                                            | 267 |

|                                           | Overview                                                                   |     |

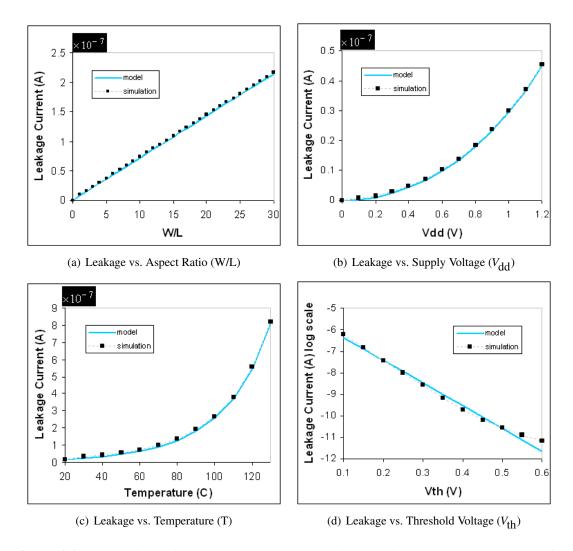

|                                           | Impact of Parameter Variations on Leakage Current                          |     |

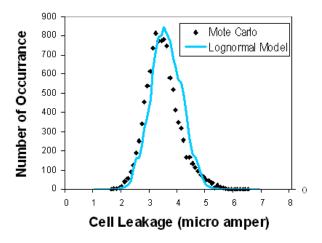

|                                           | Statistical Estimation and Distribution of Leakage Current in SRAM         | 272 |

| 10.4.4                                    | Impact of Transistor Threshold Voltage $(V_{th})$ and Temperature $(T)$ on |     |

|                                           | Leakage Power                                                              |     |

|                                           | Simulation Results for Power, Leakage, and Energy                          |     |

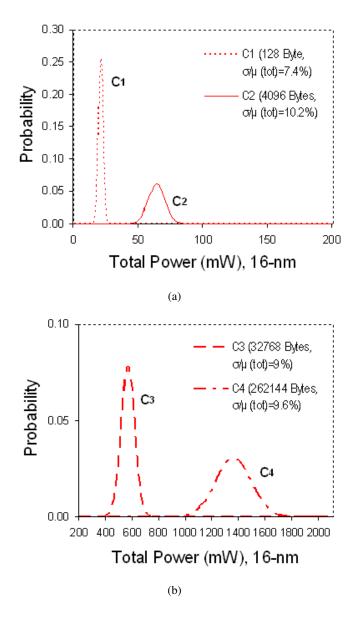

|                                           | Probability Distribution of Total Power                                    |     |

| 10.5 SRAM                                 | yield-estimation model                                                     | 281 |

| VII Conclus                               | ion                                                                        | 283 |

| 11 Summary                                |                                                                            | 284 |

| 12 Future Wor                             | k                                                                          | 291 |

| Bibliography                              |                                                                            | 296 |

| Our Published Paper (in ISQED-2012) [147] |                                                                            | 314 |

## **List of Figures**

|                            | 15<br>17<br>17<br>18<br>20<br>22<br>]. 26 |

|----------------------------|-------------------------------------------|

| h dif-<br>algo-<br>        | 17<br>18<br>20<br>22<br>]. 26             |

| algo-<br><br><br>rely [193 | 18<br>20<br>22<br>]. 26                   |

| algo-<br>                  | 18<br>20<br>22<br>]. 26                   |

| ely [193                   | 20<br>22<br>]. 26                         |

| ely [193                   | 20<br>22<br>]. 26                         |

| <br><br>rely [193          | 22<br>]. 26                               |

| ely [193                   | ]. 26                                     |

| ely [193                   |                                           |

|                            | 38                                        |

|                            | 50                                        |

|                            | 40                                        |

|                            | 42                                        |

|                            | 44                                        |

| ry for                     |                                           |

|                            | 46                                        |

|                            | 50                                        |

|                            | 51                                        |

|                            | 52                                        |

|                            | 53                                        |

|                            | 57                                        |

|                            | 59                                        |

| RAM                        |                                           |

|                            | 67                                        |

| ied to                     | 70                                        |

|                            | 70                                        |

|                            | 72                                        |

| r.<br>I                    | y for                                     |

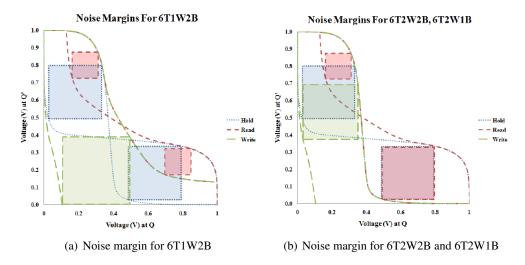

| 6.4  | Comparison of hold noise margin, read noise margin, and write noise margin                              |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

|      | of 6T-SRAM designs [180]                                                                                | 75  |

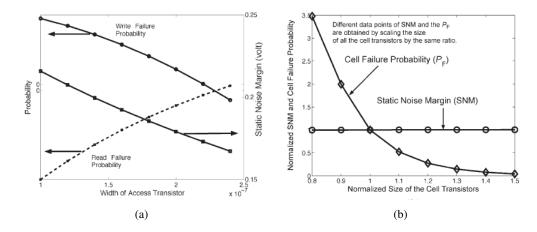

| 6.5  | Variation of SNM and failure probability with (a) width of the access transistors;                      |     |

|      | and (b) normalized cell area [115]                                                                      | 76  |

| 6.6  | An NBTI model [34] vs. measurement data by W. Wang et al. [182]                                         | 82  |

| 6.7  | Impact of $V_{\text{th}}$ variation on NBTI                                                             | 83  |

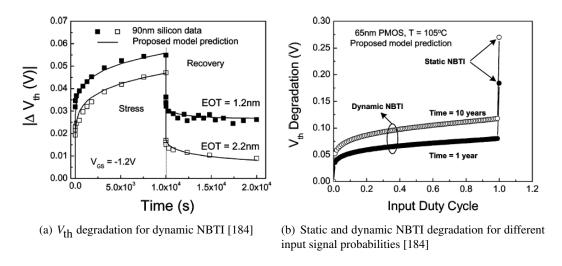

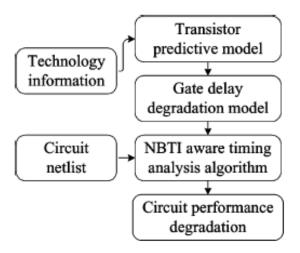

| 6.8  | NBTI timing analysis framework [184]                                                                    | 85  |

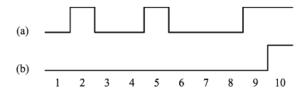

| 6.9  | Random input sequence. (a) Normal case. (b) Extreme case [184]                                          | 86  |

| 6.10 | Timing degradation analysis algorithm [184]                                                             | 88  |

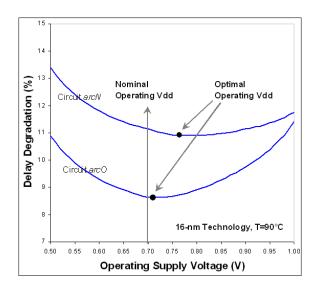

| 6.11 | Optimal $V_{dd}$ for minimum degradation of circuit performance for two different                       |     |

|      | 16-nm SRAM architectures: optimal $(\frac{64:64:16}{1:1:1})$ and non-optimal $(\frac{4:64:256}{1:1:1})$ | 91  |

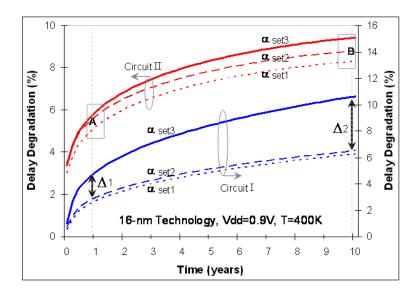

| 6.12 | Delay degradation over time for various duty cycle sets of two sample circuits                          | 94  |

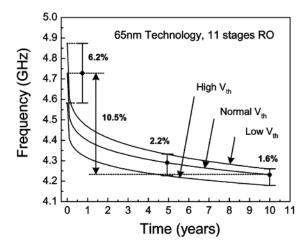

| 6.13 | Frequency degradation of an 11-stage ring oscillator (RO) under both process                            |     |

|      | variation and NBTI effect [184]                                                                         | 96  |

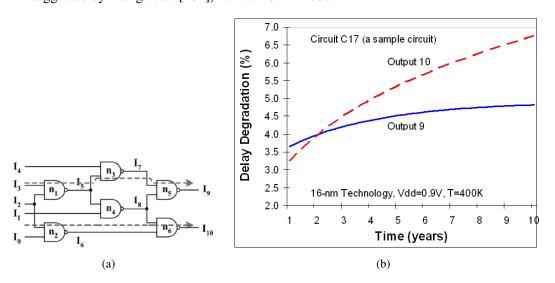

| 6.14 | Example circuit to demonstrate the critical path changing with time                                     | 97  |

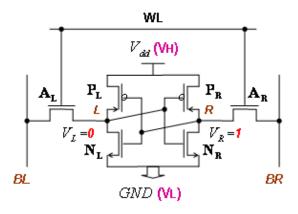

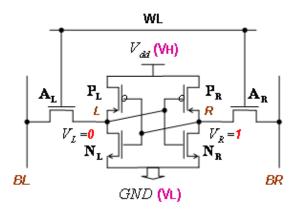

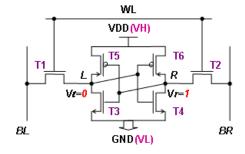

| 7.1  | 6 transistor (6T) storage cell (repeated for convenience)                                               | 104 |

| 7.2  | A piece of resistive material with electrical contacts on both ends [101]                               | 110 |

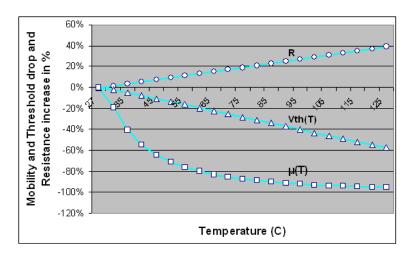

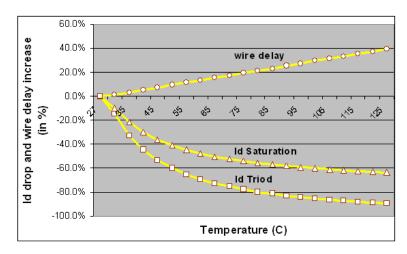

| 7.3  | NMOS Mobility & Threshold, and wire Resistance change vs. Temperature                                   | 111 |

| 7.4  | Drain Current and Wire Delay vs. Temperature                                                            | 112 |

| 7.5  | Supply voltage variation [27]                                                                           | 115 |

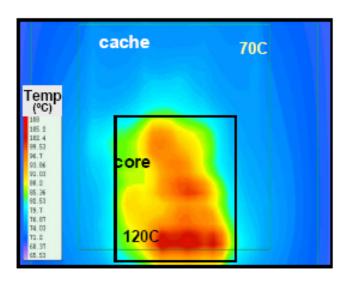

| 7.6  | Within die temperature variation [27]                                                                   | 116 |

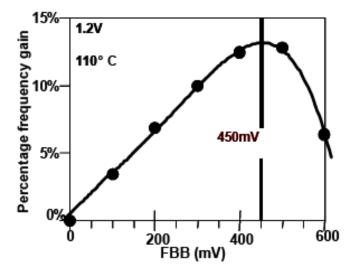

| 7.7  | Optimal FBB for sub-90-nm generations [27]                                                              | 121 |

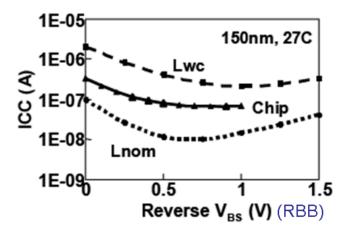

| 7.8  | Leakage reduction by reverse body bias [27]                                                             | 122 |

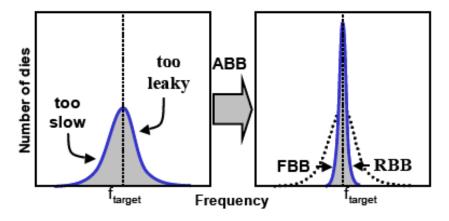

| 7.9  | Target frequency binning by adaptive body bias [27]                                                     | 123 |

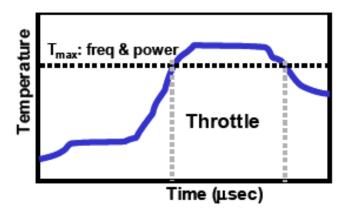

| 7.10 | Temperature based $V_{cc}$ /frequency throttling [27]                                                   | 125 |

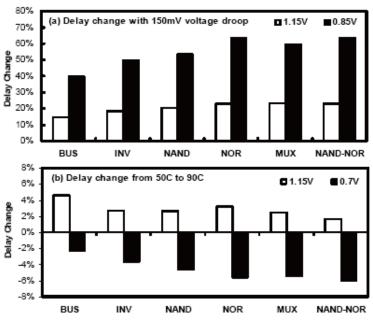

| 7.11 | Measured delay changes to $V_{cc}$ and Temperature [172]                                                | 127 |

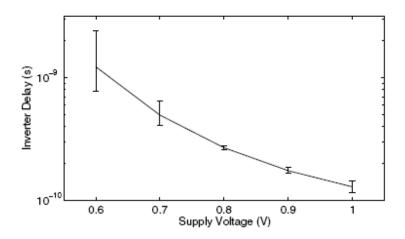

| 7.12 | Impact of temperature on a commercial 65-nm technology [191]                                            | 128 |

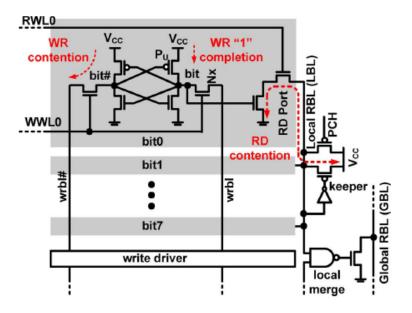

| 7.13 | The 8T-SRAM cell architecture showing the WR and RD ports [143]                                         | 131 |

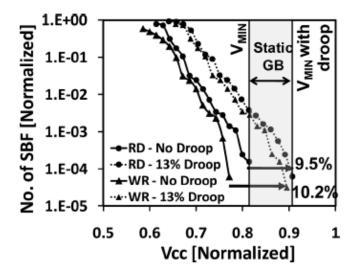

| 7.14 | Measured number of single bit failures in the 16 KB array with and without $V_{cc}$                     |     |

|      | droop [143]                                                                                             | 133 |

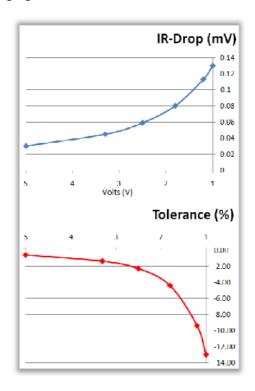

| 7.15 | IR-Drop & Tolerance vs. $V_{dd}$ [62]                                                                   | 139 |

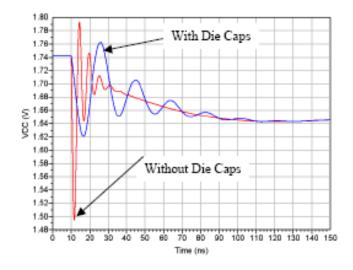

|      | Effectiveness of on-die decoupling capacitors [27]                                                      | 140 |

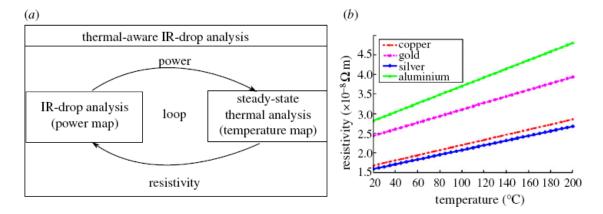

| 7.17 | Electrical-thermal coupling. (a) Flow chart and (b) temperature-dependent re-                           |     |

|      | sistivity of metals [155]                                                                               | 142 |

| 7.18 | Voltage Drop on Plane Shape [62]                                                                        | 143 |

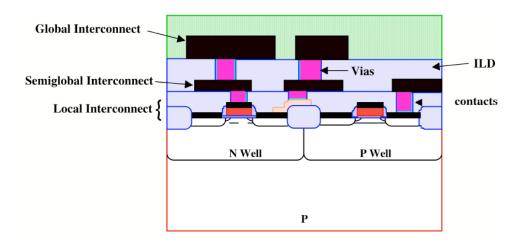

| 7.19 | Schematic cross-section of backend structure, showing interconnects, contacts,                          |     |

|      | and vias, separated by dielectric layers [148]                                                          | 145 |

| 7.20 | Input Buffer Distribution [130]                                                                         | 148 |

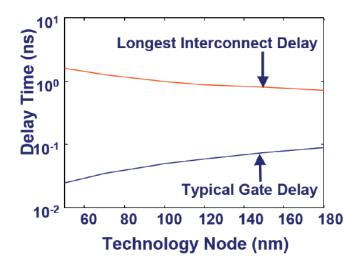

| 7.21 | Delay as a function of technology node both for <i>global</i> interconnect and typical                  |     |

|      | CMOS gate [87]                                                                                          | 150 |

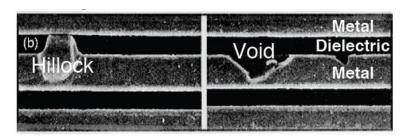

| 7.22 | Hillocks and voids induced by electromigration with high current density in a                           |     |

|      | Cu interconnect [87]                                                                                    | 150 |

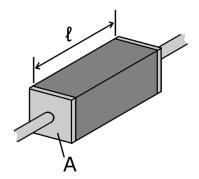

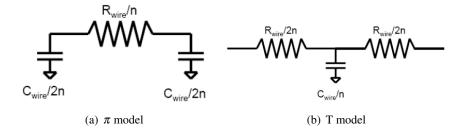

| 7.23         | One segment of a distributed wire model using SPICE [87]                             | 152                               |

|--------------|--------------------------------------------------------------------------------------|-----------------------------------|

| 7.24         | Equivalent circuit of a distributed RC interconnect with step input function [87].   | 153                               |

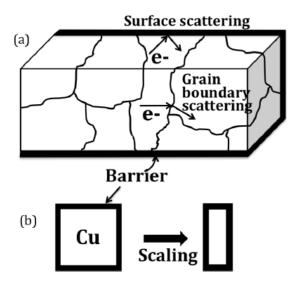

| 7.25         | Schematic illustration of the surface and grain boundary scatterings, and the        |                                   |

|              | barrier effect [87]                                                                  | 157                               |

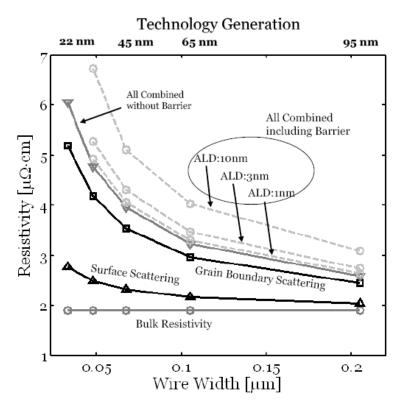

| 7.26         | Cu resistivity in terms of wire width taking into account the surface and grain      |                                   |

|              | boundary scattering and barrier effect [87]                                          | 158                               |

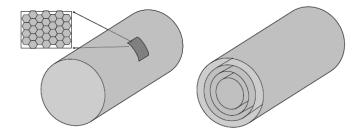

| 7.27         |                                                                                      | 159                               |

|              | Three dimensional illustration of (a) SWCNT, (b) MWCNT [87]                          | 160                               |

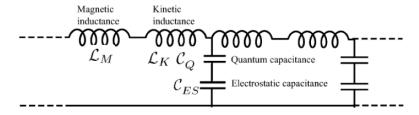

|              | Transmission line LC components of SWCNT [87]                                        | 160                               |

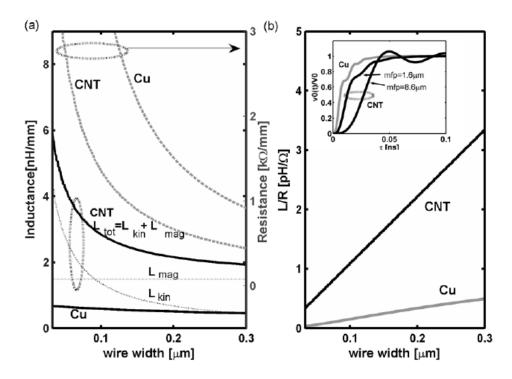

| 7.30         | (a) Inductance and resistance and (b) Inductance to resistance ratio as a function   |                                   |

|              | of the wire width [87]                                                               | 161                               |

|              | Graphical illustration of 2-D Graphene nano-ribbon (GNR) [56]                        | 162                               |

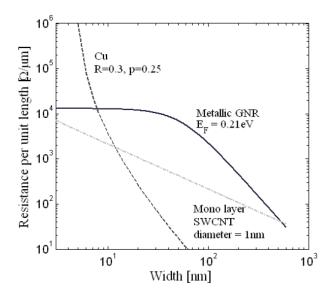

|              | Resistance comparison between GNR, mono-layer SWCNT, and Cu [2]                      | 163                               |

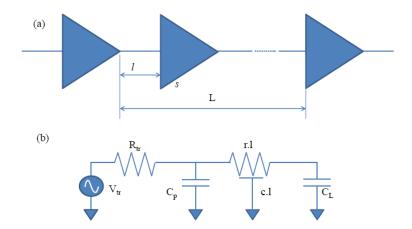

| 7.33         | (a) Schematic of an optimally buffered interconnect. (b) The equivalent circuit      |                                   |

|              | of one segment [87]                                                                  | 164                               |

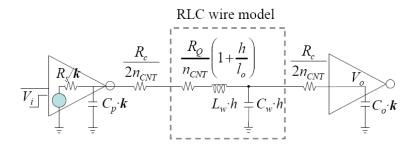

|              | Equivalent circuit model of a repeater segment for CNTs [87]                         | 165                               |

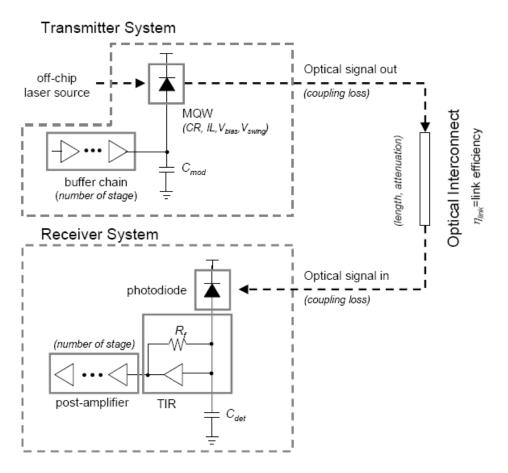

|              | The schematic of a quantum-well modulator-based optical interconnect [83]            | 166                               |

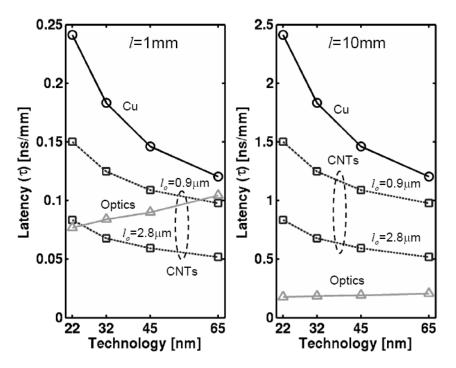

| 7.36         | Latency as a function of technology node for two different interconnect lengths [12] |                                   |

|              | 50]                                                                                  | 167                               |

| 7.37         | Energy per bit vs. technology node for two different interconnect lengths corre-     | 4.60                              |

| <b>5.0</b> 0 | sponding to <i>global</i> and <i>semiglobal</i> wire length scales [125, 50]         | 168                               |

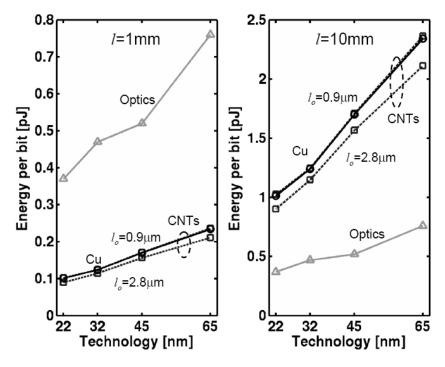

| 7.38         | Latency and energy per bit in terms of wire length for the 22-nm technology          | 1.60                              |

| 7.20         | node [87]                                                                            | 169                               |

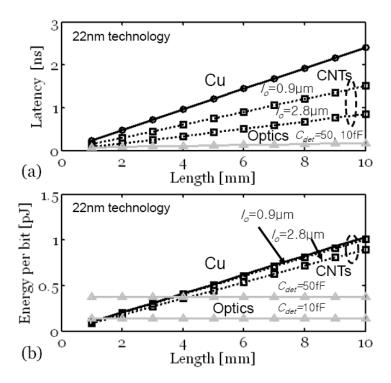

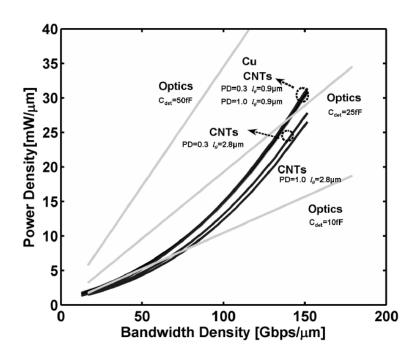

| 7.39         | The impact of CNT and optics technology improvements on power density vs.            | 171                               |

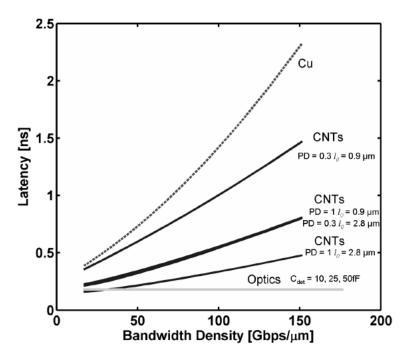

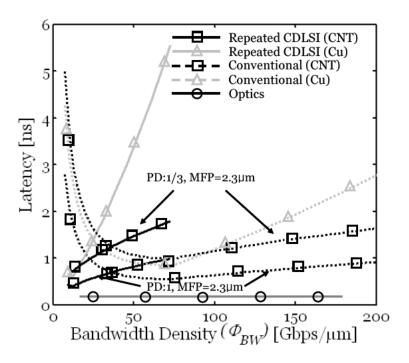

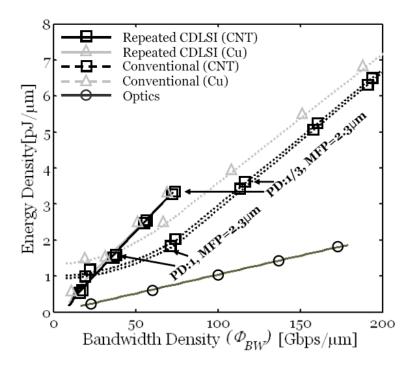

| 7.40         | bandwidth density [87]                                                               | 171                               |

| 7.40         | The impact of CNT and optics technology improvement on latency vs. band-             | 170                               |

| 7 41         | width density [87]                                                                   | <ul><li>172</li><li>173</li></ul> |

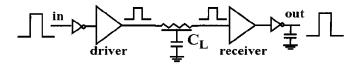

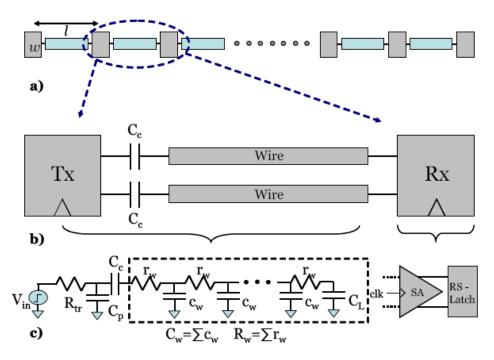

|              | Schematic of conventional low-swing interconnect scheme [141]                        | 173                               |

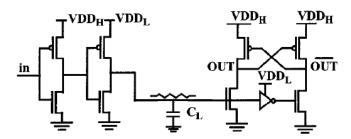

|              | (a) Simple illustration of repeated capacitively driven low-swing interconnect       | 1/3                               |

| 1.43         | (CDLSI). (b) Zoomed schematic of one segment of CDLSI. (c) Equivalent                |                                   |

|              | circuit model of one segment [87]                                                    | 174                               |

| 7 44         | Delay vs. bisectional bandwidth density $(\Phi_{BW})$ [87]                           |                                   |

|              | Energy Density vs. bisectional bandwidth density $(\Phi_{BW})$ [87]                  | 176                               |

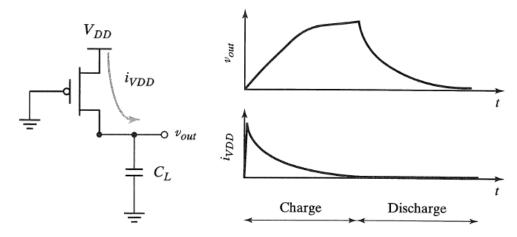

|              | Dynamic Dissipation due to Charging and Discharging Capacitances [141]               | 180                               |

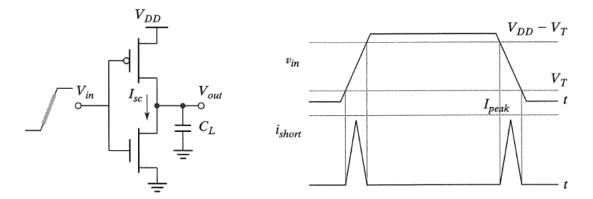

|              | Short-circuit currents during transients [141]                                       | 185                               |

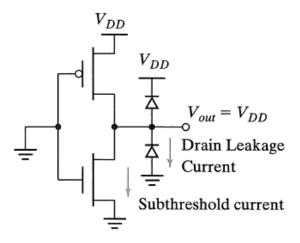

|              | Sources of leakage currents in CMOS inverter (for $V_{in}$ =0 V) [141]               | 188                               |

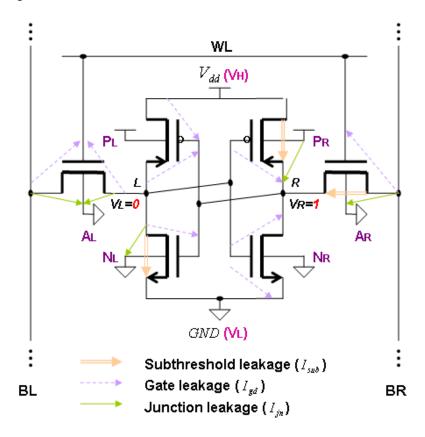

|              | Different components of SRAM cell leakage (based on Mukhopadhyay et al. [115]        |                                   |

|              | Normalized delay, energy, and energy-delay plots for CMOS inverter in 16-nm          | ,,                                |

|              | CMOS technology.                                                                     | 195                               |

|              |                                                                                      |                                   |

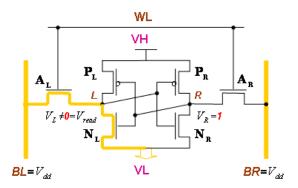

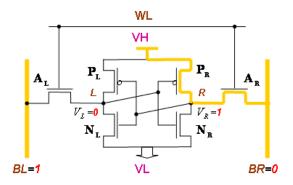

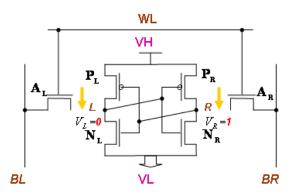

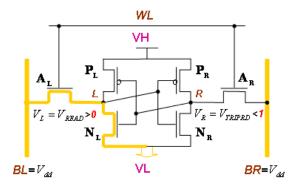

| 8.1          | Read Failure: Flipping data during "read."                                           | 201                               |

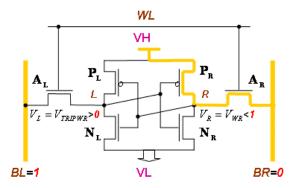

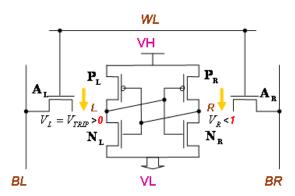

| 8.2          | Write Failure: Memory cell does not register an input change correctly               | 203                               |

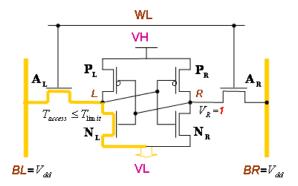

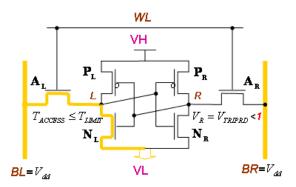

| 8.3<br>8.4<br>8.5 | Access failure: $T_{ACCESS} > T_{LIMIT}$                                            | 205        |

|-------------------|-------------------------------------------------------------------------------------|------------|

| 9.1<br>9.2        | Curve fitting for Hspice simulation for an SRAM                                     |            |

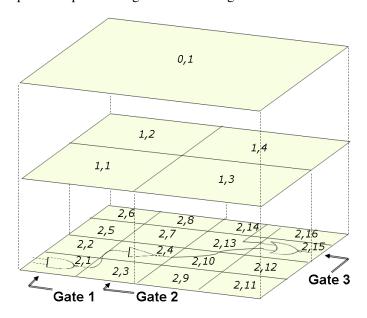

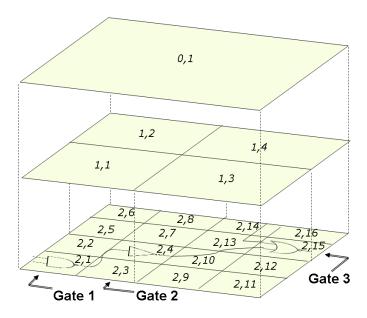

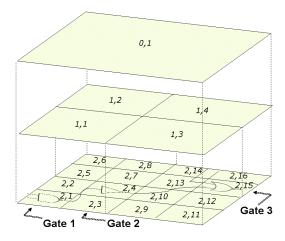

| 10.1              | Spatial correlation modeling for WID variations (Based on Fig.1 of Agarwal [4])     |            |

|                   | ( · <b>I</b> · · · · · · · · · · · · · · · · · · ·                                  | 239        |

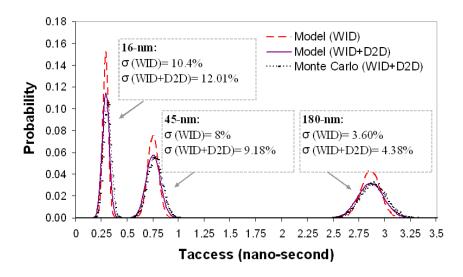

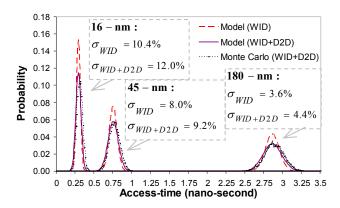

|                   | Verifying our proposed model with Monte Carlo                                       |            |

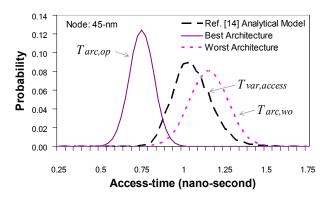

|                   | Validating optimization capability of our model                                     | 242        |

| 10.4              | Comparing the improved cumulative distribution function (CDF) of optimum-           |            |

|                   | L L                                                                                 | 243        |

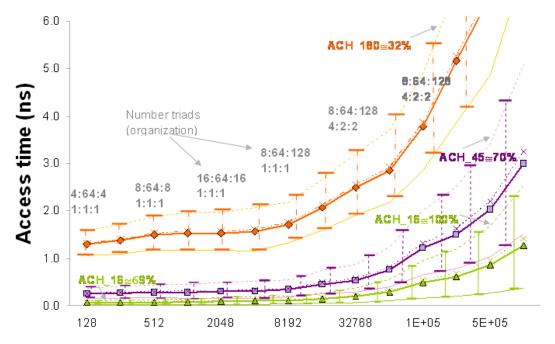

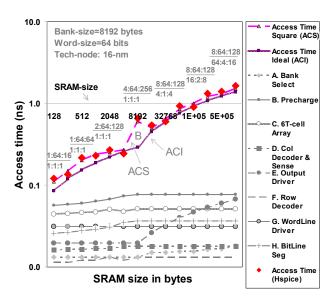

| 10.5              | Access-time for "square" SRAM (ACS), Access-time for "non-square" SRAM              |            |

|                   | (ACI), and ACI break-down traces                                                    | 246        |

| 10.6              | Comparing the ACI (ideal access-time) 3-sigma corner points of 16-nm with           |            |

|                   |                                                                                     | 249        |

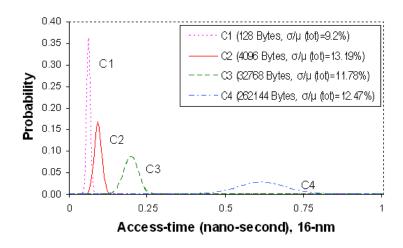

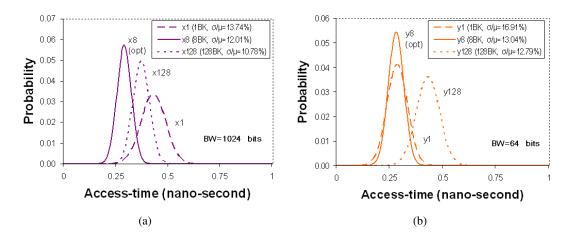

|                   | Cumulative distribution of access-time for 4 different SRAM sizes in 16-nm node.    | 251        |

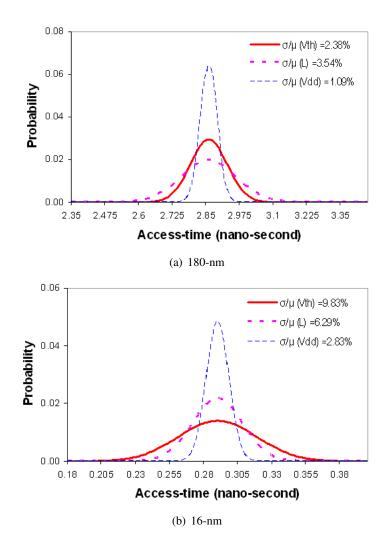

| 10.8              | Individual Distribution of Access-time for (a) 180-nm 64KB SRAM and (b)             |            |

|                   | 16-nm 64KB SRAM                                                                     | 254        |

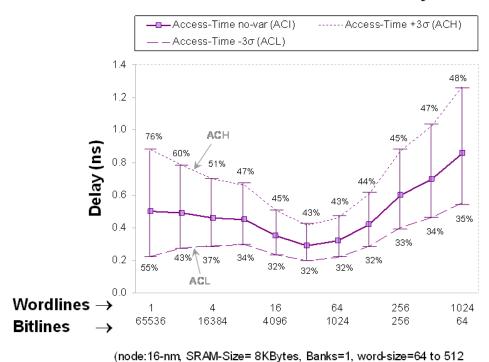

| 10.9              | Wordline vs. Bitline $3\sigma$ corner-points (ACH and ACL) Variability of 16-nm     |            |

|                   |                                                                                     | 255        |

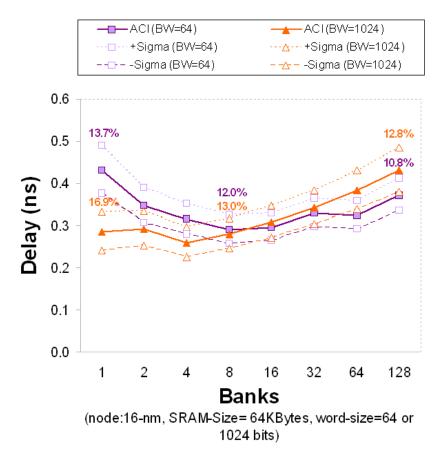

|                   | Bank Variability; Access-time variation vs. number of banks                         | 258        |

| 10.11             | Bank Variability; illustrating the distribution of ACI (ideal access-time) for two  | 250        |

| 10.10             | $\mathcal{E}$                                                                       | 259        |

| 10.12             | Area showing higher increase rate for each doubling of SRAM sizes, as com-          | 262        |

|                   | 1                                                                                   | 263        |

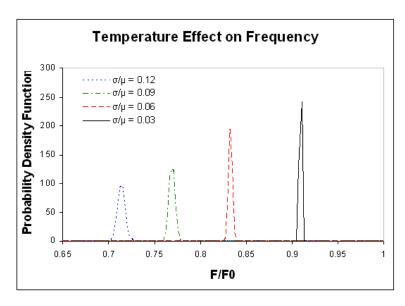

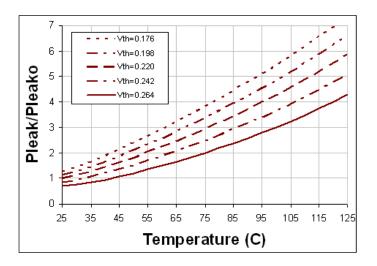

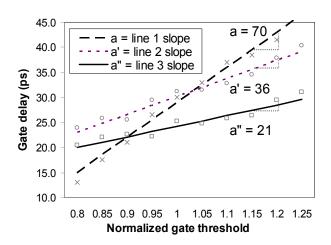

|                   | Relative switching frequency versus temperature for different threshold voltages.   |            |

|                   | i i i i i i i i i i i i i i i i i i i                                               | 266        |

| 10.15             | 6 Comparisons of the analytical model [195] against our circuit-level simulation    | 270        |

| 10.17             |                                                                                     | 270        |

|                   | Distribution leakage of a 16-nm SRAM cell ( $I_{leak}$ )                            |            |

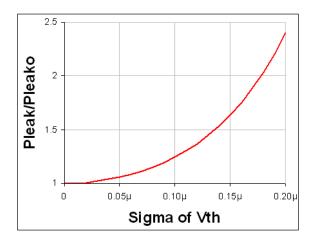

|                   | Relative leakage power in the 16-nm SRAM chip as a function of $V_{th}$ 's $\sigma$ | 215        |

| 10.18             | Relative leakage power versus temperature for different threshold voltages at       | 075        |

| 10.10             | 125°C                                                                               | 215        |

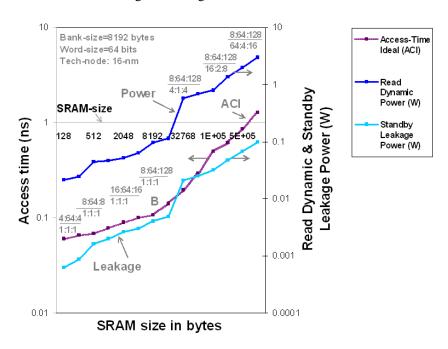

| 10.19             | Read Dynamic Power, Standby Leakage Power, and Ideal Access-time (ACI)              | 276        |

| 10.20             | for different SRAM sizes in our 16-nm design                                        | 270        |

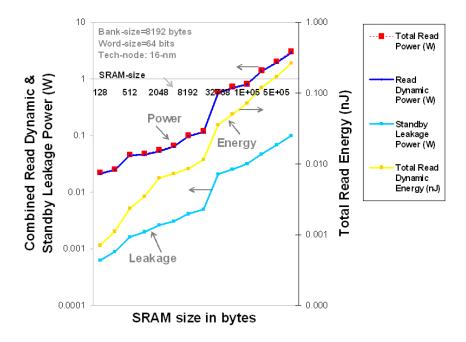

| 10.20             | Olllustrating the combined "Read Dynamic Power + Standby Leakage Power"             |            |

|                   | and the Total Read Dynamic Energy for different SRAM sizes in our 16-nm design      | 277        |

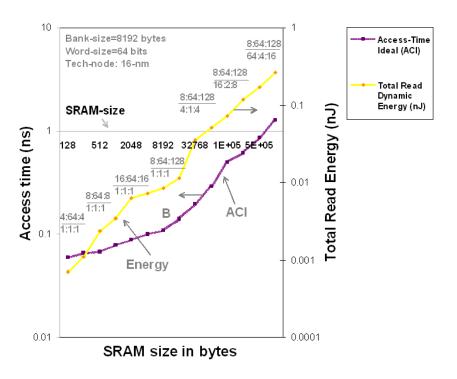

| 10 21             | Total Read Dynamic Energy and Ideal Access-time (ACI) for different SRAM            | <i>Δ11</i> |

| 10.41             |                                                                                     | 278        |

| 10.22             | The probability distribution of the total power for four different SRAM sizes.      |            |

| 10.22             | The probability distribution of the total power for four different SIXAIN SIZES     | 200        |

## **List of Tables**

|                                                                                                 | 86                                                                                                                  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                                                                                 |                                                                                                                     |

| and $arcO$ (optimum, $\frac{64:64:16}{1:1:1}$ )                                                 | 89                                                                                                                  |

| Temperature dependency of mobility, threshold voltage and resistance [191]                      | 105                                                                                                                 |

| Temperature-induced delay change in a 65-nm technology [191]                                    | 128                                                                                                                 |

| $\alpha$ and $\beta$ for lumped and distributed networks for different points of interest [87]. | 154                                                                                                                 |

| Comparison of different architectures with Ref. (VARIUS [169])                                  | 244                                                                                                                 |

| Comparing the <b>cumulative</b> ACI 1-sigma of 16-nm with those of 180-nm and                   |                                                                                                                     |

| 45-nm for different SRAM-sizes                                                                  | 250                                                                                                                 |

| Comparing the <b>individual</b> ACI 1-sigma of 16-nm with those of 180-nm and                   |                                                                                                                     |

| * *                                                                                             | 253                                                                                                                 |

| Analysis of Mean and standard deviation of Ideal Access-Time (ACI) for two                      |                                                                                                                     |

| different organizations, in 16-nm SRAMs of different bank numbers                               | 260                                                                                                                 |

| FMAX (maximum frequency) MEAN Variability for a 64KB SRAM in three                              |                                                                                                                     |

| different technology nodes                                                                      | 262                                                                                                                 |

| SRAM yield before and after optimization                                                        |                                                                                                                     |

|                                                                                                 | Comparing the <b>cumulative</b> <i>ACI</i> 1-sigma of 16-nm with those of 180-nm and 45-nm for different SRAM-sizes |

#### **Abstract**

# DESIGN AND ANALYSIS OF ROBUST VARIABILITY-AWARE SRAM TO PREDICT OPTIMAL ACCESS-TIME TO ACHIEVE YIELD ENHANCEMENT IN FUTURE NANO-SCALED CMOS

by

#### Jeren Samandari-Rad

Design variability due to inter-die (D2D) and intra-die (WID) process variations has the potential to significantly reduce the maximum operating frequency and the effective yield of high-performance chips in future process technology generations. This variability manifests itself by increasing the access-time variance and mean of fabricated chips.

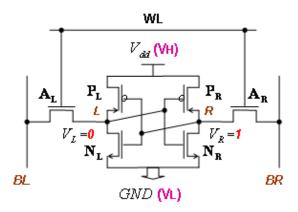

This thesis proposes a new hybrid analytical-empirical model, called VAR-TX, that exhaustively computes and compares all feasible architectures subject to D2D and WID process variations (PV). Based on its computation, VAR-TX predicts the optimal architecture that provides minimum access-time and minimum access-time variation for yield enhancement in future 16-nm on-chip conventional six-transistor static random access memories (6T-SRAMs) of given input specifications and given area and power constraints. The given specifications include SRAM size and shape, number of columns, and word-size.

In addition, this thesis reviews 6T-cell design challenges and the main causes for failure. Also provided are several newly designed or modified circuits that are crucial for SRAM

stability, reliability, robustness, speed, and reduced power consumption. This thesis also compares the impact of D2D and WID variations on access-time for 16-nm SRAM with the 45-nm and 180-nm nodes and demonstrates that the drastic increase in the 1- and 3-sigma of the smaller nodes is mainly due to the increase in the WID variations. A considerable number of simulation results regarding access-time, leakage current, and dynamic power are presented and analyzed throughout this thesis to help predict the impact of process, operation, and temperature variations on SRAM variability, as well. Finally, the VAR-TX model argues previously published works that suggest that square SRAM always produces minimum delays and it significantly extends and enhances the older models by adding both an extra dimension of architectural consideration and additional device parameter fluctuation to the analysis, while producing delay estimates within 8% of Hspice results.

To my daughter Sonia, who has taught me how to love,

and to my adviser, Vice Provost & Professor Richard Hughey, who has dazzled me and so many others with not only his brilliance, but his amazing love and devotion towards all those around him;

I am forever grateful for the incredible impact you have made on my life.

#### Acknowledgments

I would like to thank all those who contributed to the emergence, creation, and correction of this thesis. I would like to start with the Lord for looking over my health and providing me with whatever I needed to complete my graduate education at UC Santa Cruz.

I would like to thank my thesis advisor, Professor and Vice Provost Richard Hughey, who is always an invaluable source of support and inspiration, from turning my research work around to giving me intelligent hints on effective research strategies, pointing me in the right direction, and providing me with a great deal of technical and editorial remarks/suggestions and so many answers I needed to complete my research project. I am immensely grateful to Prof. Hughey, whose intellectual, spiritual, and financial support made the success of this project possible. I will remain indebted to him for his vital support, his brilliance, and his unsurpassed positive attitude and personality for the years to come.

I would like to thank Professor Jose Renau for encouraging me to expand the design space of this project and to delve into several challenging award-wining related research works. His crucial suggestions helped me produce results that can be used by current and future SRAM designers. It's no wonder that many in and out of UCSC think of Prof. Renau as an embodiment of good heart and brain.

I would like to thank Chancellor and Professor Steve Kang for being kind enough to serve on my Thesis Defense committee and take time from his busy schedule (both at UC Merced and at UCSC) to read my thesis and give me his valuable feedback.

I am grateful to Prof. Matthew Guthaus whose initial ideas and direction helped me

get started on this project. Prof. Gauthaus' effective proofreading, his knowledge and expertise with conferences, and his patience in tolerating my numerous technical questions during the start of this project are among the reasons which helped my paper on SRAM (with him and Prof. Hughey) get the approval/acceptance of ISQED-2012 committee members.

I am grateful to Dr. Xuchu Hu (Cadence) for her smart solutions of the technical glitches I occasionally came upon, to Derek Chen (Space Systems/Loral) for his sound Ultrasim simulation tool hints, to Kevin Woo (Intel) and Ehsan Ardestani (UCSC) for answering my tricky LaTex questions, and to Dr. Rebekah Brandt (recent UCSC EE graduate) for her diligent proofreading contribution, which was instrumental in turning a rough draft into a user-friendly Thesis.

I apologize for the inadvertent potential omission of some deserving friends and colleagues whose contributions played a role in the extraordinary experiences I have been fortunate to enjoy. I thank them all, here, collectively.

## Part I

## Introduction

## **Chapter 1**

#### **Motivations**

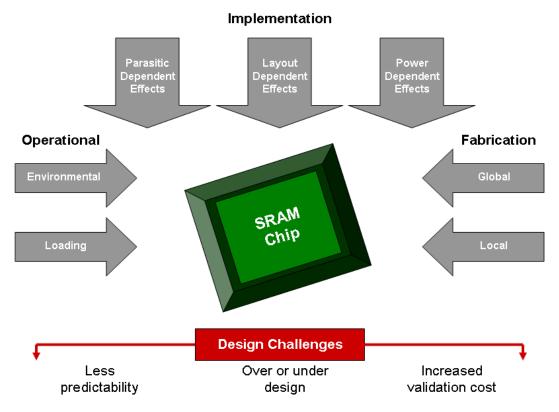

As device feature-size reduction is becoming dominant in the semiconductor industry, its impact on product reliability, yield, and therefore cost is dramatically increasing. Embedded microprocessors and other high-performance on-chip modules incorporate Static Random Access Memory (SRAM) or cache components that play significant roles in overall chip functionality and reliability. Unwanted variations in SRAM circuits may result in access-time variations and chip functional failures. This means the cost and performance of a vast number of chips today heavily depend on the reliability and speed of their on-chip SRAM, which is increasingly affected by scaled-down feature sizes.

The memory component of many chips span and even exceed 70% of the total area. Due to the crucial role of on-chip memories, much of the computer architecture research involves investigating trade-offs between various memory systems. This, however, can not be done adequately without a firm grasp of the costs of each alternative. For example, it is impossible to compare two different SRAM organizations without considering the difference in *access*

or *cycle-times*. Similarly, we must take the chip area and power requirements of each alternative into account. Only when all the costs are considered can we make an informed decision. But without a reliable, accurate, and inexpensive modeling tool in hand, this cost consideration itself would be either expensive, time consuming, inaccurate, or all three. This thesis provides an effective modeling methodology and corresponding toolkit that satisfies these requirements.

In order to continue the growth of modern memory technology, it is important to increase the access-time speed while curbing the energy usage. For faster access-time, new innovations in manufacturing processes and novel circuit designs are needed. Similarly, new efforts are required to control the power and energy consumption of storage, computing, and IT facilities and their cooling systems. Besides the environmental impact, excessive power consumption also reduces system reliability, increases cooling cost and cuts the battery cycle time. Effective power and thermal management will help to relieve the bottleneck of today's VLSI design and accelerate the growth of the information technology and many other similar industries. It will also enable today's computing and communication devices to work efficiently with emerging energy storage and energy harvesting technologies to achieve energy autonomy.

A robust, standard 6 transistor Static Random Access Memory (6T-SRAM) designed for an optimum architecture with power management considerations could significantly contribute to the system being able to work on different types of hardware with variable workload.

This thesis proposes a novel model (VAR-TX) that is suitable to the memory design of the next generation future technology node (i.e. 16-nm). It also covers recent progress on adaptive power management, including runtime monitoring, modeling, classification, learning, and controlling techniques for power and temperature optimization of a computing device. The

core of this thesis is presenting the process of building our proposed model (VAR-TX) that predicts the optimum architecture for a standard 6T-SRAM running at a maximum possible speed that satisfies a given power consumption and area for future technology nodes. However, to achieve this goal, it is necessary to cover several crucial stability-, reliability-, and energy-related topics that are considered (either explicitly or implicitly) during our SRAM design. This is because, like many other cutting-edge technologies, we believe that future technology nodes beyond 32-nm will face such challenges as temperature-related issues, the effect of Negative Bias Temperature Instability (NBTI), Hot Carrier Injection (HCI), the  $V_{\rm dd}$  variation as a static IR drop or dynamic L di/dt, and several others (the most important of which are covered in this thesis) more than ever before. In a nutshell, our motivation for this research is to make the following contributions to the VLSI field:

- ★ Presenting VAR-TX: our new model that helps predict the variation of access-time due to process and operational variation in memory design for current and next generation future technology nodes (i.e., 16-nm).

- ★ Providing a first-order solution to mitigate the effects of increasing process variations in future technology nodes.

- ★ Providing an effective method to maximize the yield.

- ★ Making our proposed model VAR-TX freely available to the public to help predict the optimum architecture of a 6T-SRAM to achieve maximum speed for given power and area constraints.

- ★ Providing new simulation tricks that help avoid prohibitively long mixed-signal circuit simulations.

- ★ Providing a broad overview of the important challenges in SRAM design that could be used as a valuable reference for SRAM/cache designers.

These contributions are explained in further detail in Chapter 3. The following abstractivly lists our modeling methodology for the derivation of delay distribution, discussed in detail in Chapter 9.

- 1. Compute the sensitivities and store them in tables.

- 2. Compute the D2D component of the path delay.

- 3. Express the WID component of the path delay variation as an analytical expression of the device parameter variation.

- 4. Combine the two components (namely, D2D and WID) of the path delay variations to obtain the joint path delay distribution.

- 5. Optimize the delay through the examination of all possible architectures to achieve maximum yield.

The thesis is organized as follows:

In Part I, Chapter 2 begins by presenting literature research on prior approaches to memory compilers/models made for one or more of the following purposes: general trade-off analysis, analysis of tolerance to process variations, power reduction, and analysis of tolerance of "soft errors" [transient errors induced by radiation] [17]. Part I, Chapter 3 states the contribution of this thesis to the SRAM community. Part II illustrates our hierarchical memory architecture (Chapter 4—in which several novel/modified circuits designed for increasing the speed, lowering the power, and minimizing the variability is presented and discussed). Part II also reviews SRAM memory operation (Chapter 5). Part III discusses design challenges. The design challenges and analysis is broken down into two separate chapters: Chapter 6 and 7. Chapter 6 covers such device-related topics as Die-to-Die (D2D) and within-in die (WID) variations, static noise margin (SNM), soft errors, negative bias temperature instability (NBTI), hot carrier injection (HCI), and single electron tunneling. Chapter 7 covers such power-related topics as temperature impacts, temperature and voltage variation,  $V_{dd}$  variation as a static IR drop or dynamic L di/dt, interconnect, techniques for leakage control, and the power (temperature, leakage, and energy-delay)—all of which contribute to the SRAM variability. The main causes for failure are discussed in Part IV (Chapter 8). Part V outlines the proposed new model VAR-TX (Chapter 9), after discussing two different classes of variability: inter-die (D2D) and intra-die (WID). Part VI, (Chapter 10) illustrates and analyzes our simulation results that demonstrate the impact of process (P), voltage (V), temperature (T), and technology nodes variability on speed, power, and yield of the designed SRAM. Part VII summarizes the impact of this research and future work. Finally, Appendix A presents this thesis's published paper in ISQED-2012 [147].

## Chapter 2

### **Literature Review**

The scaling of SRAM in the presence of variability is becoming increasingly difficult, due to the reduced stability and increased leakage current with the scaling of silicon technology. Various circuit techniques have been proposed to curb process variations and thus improve SRAM access-time and stability while lowering power use. Past research on memory modeling can be classified into three groups, chronologically:

- The Classical Models (oldest, circa 1990s) are primarily based on models and equations that take no variability considerations in mind.

- 2. The *more Advanced Models* (coming after the Classical Models) mostly focus on innovative ways to reduce delay, leakage/dynamic power, or a combination of these two.

- 3. Finally, the *Current/Recent models* (following the Advanced Models) are mostly based on the analysis of the effects of variability on the memory performance.

#### 2.1 Classical Models

T. Wada et al. [167] present an equation for the access-time of an on-chip cache as a function of various cache parameters (cache size, associativity\*, block size) as well as organizational and process parameters. Unfortunately, Wada's access-time model has a number of significant shortcomings. First, the cache tag (a memory storage for holding addresses [131]) and comparator in set-associative memories are not modeled, and in practice, these often constitute the critical path. Second, each stage in this model (e.g., bitline, wordline) assumes that the inputs to the stage are step waveforms; actual waveforms are far from steps and this can greatly impact the delay of a stage. Third, all memory sub-arrays are stacked linearly in a single file; this can result in aspect ratios of greater than 10:1 and overly pessimistic access-times. Furthermore, Wada's decoder model is a gate-level model which contains no wiring parasitics. In addition, transistor sizes in this model are fixed independent of the load. As an example, the wordline driver is always the same size, independent of the number of cells that it drives. Finally, Wada's model predicts only the cache access-time, whereas both the access- and cycle-time are important for design comparisons.

\* **Associativity** is a scheme used in memory architecture. Associativity allows each location in the main memory be cached by one of 2, 4, 8 or more cache locations. For example, in 2-way associativity, each location in the main memory could be in one of two cache locations. Associativity improves cache performance. For more see [131].

Among the proposals made in the recent past, CACTI [189] has been cited most. The CACTI authors improved Wada's access-time model [167] significantly by adding several new

features. These include a tag array model with comparator and multiplexer drivers. CACTI was an excellent analytical model for trade-off analysis in the late 1990s and early 2000s, but naturally exhibited shortcomings with scaled-down technology. Only the decoder component was modeled at the transistor level; remaining components were modeled at gate level or were equation-based. CACTI improved some of its shortcomings later on—in its newer versions (i.e. CACTI 6.5, 2009)—by modeling different types of wires, such as RC based wires with different power, delay, and area characteristics and differential low-swing buses. It also included, among others, a new feature of Non-Uniform Cache Access (NUCA) for chip multiprocessors that takes into account the effect of network contention during the design space exploration. Although much enhanced, as compared to its initial model, CACTI is still far from perfection. CACTI is based on DRAM technology and is mostly an equation-based model (and not hybrid empirical-analytical model like VAR-TX). It does not account for variations in  $V_{\rm th}$ , L (also called  $L_{\rm gate}$ ), and  $V_{\rm dd}$ , which greatly impact cache/SRAM stage delays and power; therefore, CACTI does not capture the effect of the random variations of electrical properties of the memory circuits on the access-time and power.

#### 2.2 More Advanced Models

X. Liang and K. Turgay [98] present a unified architecture-level modeling methodology for SRAM and content-addressable-memory (**CAM\***) array structures. Although their model considers most fundamental circuit parameters, it cannot depict  $V_{\rm th}$ ,  $L_{\rm gate}$ , and  $V_{\rm dd}$  fluctuations over the entire SRAM.

\*Content-addressable memory (CAM) is a type of computer memory used in certain high speed searching applications. It is also known as associative memory, associative storage, or associative array, although the last term is more often used for a programming data structure. Unlike standard computer memory (random access memory or RAM), in which the user supplies a memory address and the RAM returns the data word stored at that address, a CAM is designed such that the user supplies a data word and the CAM searches its entire memory to see if that data word is stored anywhere in it. If the data word is found, the CAM returns a list of one or more storage addresses where the word was found (and in some architectures, it also returns the data word, or other associated pieces of data). Thus, a CAM is the hardware embodiment of what in software terms would be called an associative array.

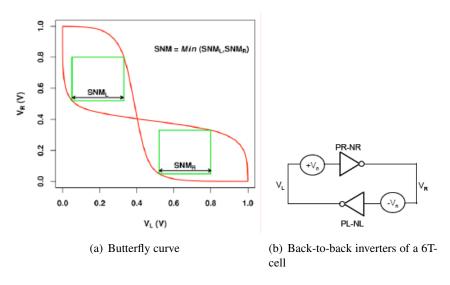

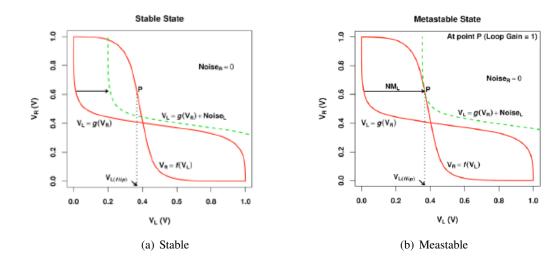

K. Agarwal and S. Nassif [6] offer an excellent model for characterizing the DC **noise margin\*** of a memory cell; this model can estimate cell-failure probabilities during *read* and *write* operations. However, these authors do not show how parameter fluctuations, which are crucial to access-time, determine the stability of entire SRAMs of different sizes and shapes. The proposed VAR-TX model, driven by mixed-signal simulations of a standard 6T-SRAM circuit, does include these fluctuations.

A. Agarwal et al. [4] present a useful model for path-based statistical timing analysis by modeling D2D and specially correlated WID device length variations. However, due to using the older 180-nm node, these authors neither included the impact of  $V_{\rm th}$  and  $V_{\rm dd}$  variations nor the architectural/organizational optimization in their modeling. This makes the application of their rather old model to the newer nodes (i.e. 32-nm and below) impractical and also makes their analysis and results much less accurate as compared to those of our proposed path-based model that takes all those missing factors into account.

<sup>\*</sup> In electrical engineering, noise margin is the amount by which a signal exceeds the minimum amount for proper operation.

R. Joshi et al. [70] propose a dynamic supply boosting technique for low voltage SRAMs at and beyond 65 nm using partially-depleted silicon-on-insulator (**PD-SOI\***) technologies. The technique exploits the capacitive coupling effect in a floating-body PD-SOI device to dynamically boost the virtual array supply voltage during *read* operation, thus improving the *read* performance, read/half-select stability, and  $V_{min}$ . Although their proposed technique enables significant reduction of the standby cell power and circuit active power in a single supply methodology, it requires a more complex circuitry and a special manufacturing process. It is also possible to improve  $V_{min}$  by using dual supply methodologies as discussed in [70, 71], but this comes at the expense of extra supply and wire routing complexity, both at the global and local levels.

\* Partially-depleted silicon-on-insulator (PD-SOI) refers to a Semiconductor CMOS (complementary metal-oxide-semiconductor) process with seven layers of copper (Cu) interconnect and low-k dielectric.

M. Yamaoka et al. [103] propose either expanding the *write* margin, using a power-line-floating *write* technique, or process-variation-adaptive *write* replica circuit to enable low-voltage *write* operation. Although effective in considerably lowering the leakage power, these techniques require careful and sensitive control of both column select and row select to prevent the degradation of stability of other cells in the same row or column.

B. Mohammad et al. [111] use a novel circuit to increase the Static Noise Margin (SNM) and the *write* margin of the SRAM cell. Despite their success in increasing the SNM and in reducing the voltage swing of the circuit mostly during the *write* (but not necessarily during the *read* operation as well), the paper reveals that the speed of their memory *access* is

reduced in part due to their "W1 voltage reduction."

G. Ming et al. [110] suggest reducing the power consumption by dynamically charging the bitlines, as well as charge sharing due to bitline charge/discharge; but this comes at the expense of reduced static noise margin.

#### 2.3 Current/Recent Models

Several good works regarding process variability have been published by P. Gupta in the recent past. In his earlier publication [60], Gupta proposes reducing the leakage power (and leakage power variability) by about 24%–38% by applying gate-length biasing only to those devices that do not appear in critical paths. This comes at the cost of up to a 10% delay penalty, thus assuring negligible degradation in the system level chip design performance. In his successor work [61], Gupta proposes algorithms for the creation of isolated and dense variants for each library cell to compensate for reduced delay and increased leakage incurred by lithography focus problems to achieve designs that are more robust to lithography focus variation.

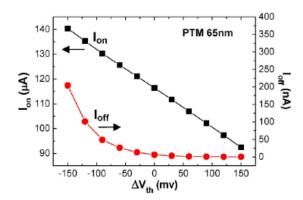

Gupta complements his previous works with a new proposal [97] that suggests a new method to exploit the unequal drive and leakage current distributions across the transistor channel in order to find an optimal non-rectangular shape for the channel to achieve further savings in leakage current. More specifically, Gupta et al. propose making a library of two different cells: one for improved delay (with a shorter dumbbell-shape transistor channel, during  $I_{on}$ ), and the other for improved leakage (with a longer dumbbell-shaped transistor channel, during  $I_{off}$ ). Following that, in response to any last minute developments of the chip manufacturing

process that could cause specification failures, Gupta et al. present a new framework to perform an Engineering Change Order (ECO) to correct the problems through incremental gate sizing for process changes late in the design cycle.

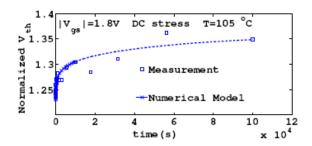

In one of his latest works, Gupta et al. [34] address the main NBTI-induced degradation issues. They argue that the recent related works [34] that have relied on device-level analytical models are limited in their flexibility to model the impact of architecture-level techniques on NBTI degradation. He and his co-authors propose a flexible numerical model for NBTI degradation that can be adapted to better estimate the impact of architecture-level techniques on NBTI degradation. In this work, Gupta et al. shows that **guardbanding\*** may still be an efficient way to deal with aging. Although insightful, especially for technology nodes prior to 45-nm, Gupta's work mostly hinges upon the systematic variation of gate-length (and gate-width) and not on the significance of random variation of  $V_{\rm th}$  as well. Since the random variation of  $V_{\rm th}$  is the dominant variability factor in newer technology nodes (i.e. 45-nm and beyond), the application of Gupta's analytical works (assuming  $V_{\rm th}$  as constant) to the newer nodes may fall short of high accuracy and effectiveness.

\* Traditionally, **guardbanding** has been used to protect against NBTI. For example, the operating frequency is reduced or supply voltage is increased to account for degradation over the lifetime of a design, such that there are no timing violations due to aging during the lifetime. The subject of NBTI is discussed in Chapter 6.

Mukhopadhyay et al. [115] offers an excellent model for failure probabilities of SRAM cells due to process-parameter variations. However, their computationally-intensive model only considers random fluctuations in  $V_{\rm th}$ , and only for a single SRAM cell. Furthermore, they sug-

gest that their model could be improved by including systematic fluctuations in  $V_{\rm th}$ , as well as considering both types of fluctuations (random and systematic) in  $L_{\rm gate}$ .

Teodorescu et al. [169] build upon Mukhopadhyay's work [115] by modeling a selected group of 6T-cells in an array of 6T-cells, but still only include variation in  $V_{\rm th}$ . Our VAR-TX model, in contrast, not only includes variations in  $V_{\rm th}$ ,  $L_{\rm gate}$  and  $V_{\rm dd}$ , but does so for an entire 6T-SRAM.

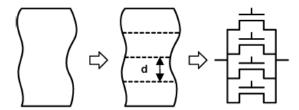

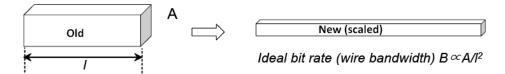

Among the contemporary reputable variability-related research works in academia are those developed by Yu Cao and his research group at Arizona State University. They create the Predictive Technology transistor Models (PTM) that this thesis has used for simulation. In one of their recent works [193], Y. Cao et al. develop an *efficient SPICE simulation method* and *statistical variation model* that accurately predicts threshold variation as a function of dopant fluctuations and gate length change caused by lithography and the etching process. By understanding the physical principles of atomistic simulations, they: 1) identify the appropriate method to divide a nonuniform gate into slices, as shown in Figure 2.1, in order to map those fluctuations into the device model; 2) extract the variation of  $V_{th}$  from the strong-inversion region instead of the leakage current, benefiting from the linearity of the saturation current with respect to  $V_{th}$ ; 3) propose a compact model of  $V_{th}$  variation that is scalable with gate size and the amount of dopant and gate length fluctuations; and 4) investigate the interaction with non-rectangular gate (NRG) and reverse narrow width effect (RNWE\*).

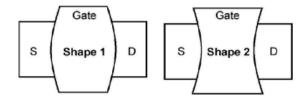

<sup>\*</sup> RNWE (reverse narrow width effect) nonuniformly reduces the threshold voltage in different locations: the closer a gate slice is to the gate end, the larger the drop is. Such nonuniformity along the width direction interacts with NRG and varies the output current [157, 159]. For instance, when the slice with the minimum length is close to the gate end extension (Shape 1 in Figure 2.2),

**Figure 2.1:** Flow to divide a nonuniform gate into slices. Each slice has a unique  $V_{\text{th }i}$  and  $L_i$  due o RDF and LER [193].

the threshold drop in that slice will be more significant due to both drain induced barrier lowering (DIBL) and stronger RNWE, leading to the largest leakage increase; on the other hand, if the slice with the minimum length is located far away from the gate end extension (e.g., in the middle of the gate, see Shape 2 in Figure 2.2), then RNWE is much weaker and the leakage is lower. Figure 2.2 shows these two representative conditions of the gate shape distortion, in which both shapes have the same nominal size and magnitude of NRG and line edge roughness (LER); but one is convex and the other is concave and thus, they are different in RNWE.

**Figure 2.2:** Threshold variation under NRG and RNWE. Two representative gate distortions under NRG [193].

To model a nonrectangular gate in the SPICE environment, the slicing method splits the nonuniform edge into many slices, such that each slice can be approximated into a regular transistor with a uniform gate length. One can then apply the nominal device model to each slice for predicting the I-V characteristics. The final performance of the transistor under LER is calculated from the summation of currents from all the slices [159, 59, 164]. This procedure is illustrated in Figure 2.1.

This proposed work [193] correctly models the variation of device output current in

all operating regions (given the post-lithography gate geometry) and projects the amount of  $V_{\rm th}$  variation at advanced technology nodes. Although this method is rudimentary, easy to operate in practice, and widely adopted in previous works [193, 159, 59], it comes with some limitations: limitation on parallel slicing, limitation on slice width, and limitation on the operation region. Due to their conceptual usefulness, these three topics are briefly discussed in further detail at the end of this chapter (Subsections 2.3.1 – 2.3.3). In these three sections we will see how the three limitations can make the proposed modeling and method somewhat costly and prone to inaccuracy, if sufficient care is not taken.

The most respected industrial works on variation are from the IBM Austin Research

Labs group, many of which authored or co-authored by Sani Nassif. The remainder of this

section lists several of these works.

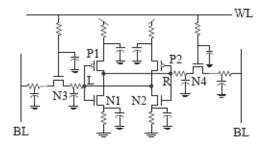

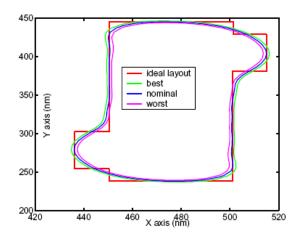

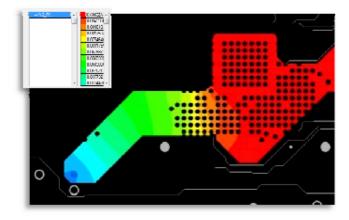

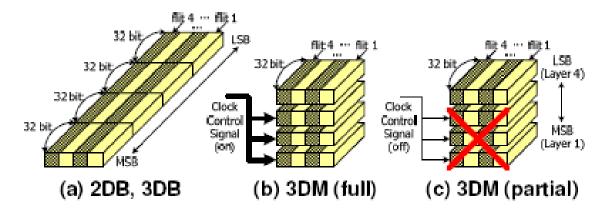

In one of the recent works from the IBM Labs group, Y. Zhou et al. [197] perform a critical study of the effects of Back-end-of-line (BEOL) lithographic variations on 45-nm SRAM performance and yield analysis. They present an SRAM simulation model with internal cell interconnect RC parasitics (see Figure 2.3) for their study of the BEOL lithographic impact. Using their method, they systematically evaluate the impact of BEOL variations on memory designs. First, they study the impact of ideal parasitics assuming no lithographic variations. Then they look into the worst-case, best-case, and nominal lithographic variations (see Figure 2.4) to show that on average, ideal parasitics impact the delay by more than 20-30% and also impact the stability yield leading to an increase of 100 mV to the SRAM minimum operating voltage,  $V_{min}$ . Based on these results, they claim that power estimation with their BEOL model is more accurate, and a traditional model without interconnect parasitics may be off by 33% in accuracy.

Figure 2.3: 6 Transistor SRAM Schametic with RC network [197].

**Figure 2.4:** Different lithographic profiles from the same layout profile of SRAM with different depth of focus (DOF) [197].

The close match between these findings and the simulation results of our model (VAR-TX) further validates the analysis presented in this thesis. Y. Zhou et al. also show that the additional accounting of the lithographic variations for the BEOL study induces about 4% variation on the SRAM *read* delay. Finally, they point out that when the resistance change (due to misalignment) is of the same order of magnitude as the nonlinear device resistance, the impact is more severe.

Another recent work from the IBM Labs group [145], developed by Sherief Reda and Sani R. Nassif, proposes a novel statistical framework to model the impact of process

variations on semiconductor circuits through the use of process sensitive test structures. Based on multivariate statistical assumptions, they propose the use of the expectation-maximization algorithm (commonly known as EM) to estimate any missing test measurements and to calculate accurately the statistical parameters of the underlying multivariate distribution.

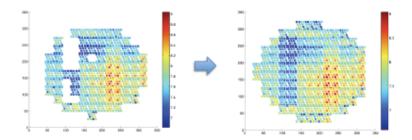

Figure 2.5: An example of filling missing measurements on wafer using the EM algorithm [145].

Figure 2.5 shows an example where the EM algorithm fills the missing measurements of one of the wafers. The color of a measurement gives its value (or speed in this case). Visual inspection shows that predicted values seem to "fit" within the range of the rest of the measurements. Using their proposed model, they analyze the impact of the systematic and random sources of process variations to reveal their spatial structures. They utilize the proposed model to develop a novel application that significantly reduces the volume, time, and costs of the parametric test measurements procedure without compromising its accuracy. They verify their models and results on measurements collected from more than 300 wafers and over 25,000 die fabricated at a state-of-the-art facility and prove the accuracy of their proposed statistical model and demonstrate its applicability towards reducing the volume and time of parametric test measurements by a factor of about 2.5 - 6.1 at no impact to test quality.

In another IBM work, they reason that the analysis performed at the "schematic" level

can be deceiving (as it ignores the interdependence between the implementation layout and the resulting electrical performance). In response, A. Bansal et al. [16] present a computational framework, referred to as "Virtual SRAM Fab," for analyzing and estimating pre-Si SRAM array manufacturing yield considering both lithographic and electrical variations. They demonstrate their proposed framework for SRAM design/optimization for the 45-nm node and use it for both the 32-nm and 22-nm technology nodes, as well. The authors illustrate the application and merit of the framework using two different SRAM cells in a 45-nm PD-SOI technology, which have been designed for similar stability and performance, but exhibit different parametric yields due to layout and lithographic variations. They also demonstrate the application of Virtual SRAM Fab for prediction of layout-induced imbalance in an 8T-cell, which is a popular alternative candidate for SRAM implementation in 32- and 22-nm technology nodes.

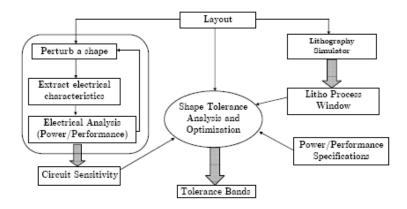

A few of the works from the IBM Labs group aim to attack the variability issues by proposing new lithography-related methodologies. As the move to low-k1 lithography has made it increasingly difficult to print feature sizes which are a small fraction of the wavelength of light, many of the manufacturing processes still treat a target layout as a fixed requirement for lithography. However, in reality layout features may vary within certain bounds without violating design constraints. The knowledge of such tolerances, coupled with models for process variability, can help improve the manufacturability of layout features while still meeting design requirements. Noticing such a notion, S. Banerjee et al. [15] propose a methodology to convert *electrical slack* in a design to *shape slack* or tolerances on individual layout shapes using a two-phase approach. In the first step, the *delay slack* is redistributed to generate *delay bounds* on individual cells using linear programming. In the second phase, which is solved

as a quadratic program, these *delay bounds* are converted to *shape tolerances* to maximize the process window of each shape. The authors show that the *shape tolerances* produced by their proposed methodology can be used within a process-window optical proximity correction (PWOPC) flow to reduce delay errors arising from variations in the lithographic process.

The authors validate the accuracy of their proposed methodology by presenting the results of their experiments on 45-nm SOI cells using accurate process models that show that the use of their *shape slack* generation in conjunction with PWOPC reduces delay errors by a factor of 2 on average (i.e. from 3.6% to 1.4%), compared to the simplistic way of tolerance band generation. Figure 2.6 illustrates the two key components in the depicted flow of the proposed methodology.

Figure 2.6: Flow for generation of tolerance bands [15].

One of the key components is *Electrical sensitivity* and the other one is the *litho-graphic process window*. *Electrical sensitivity* is a measure of how critical a particular shape is from the design point of view. Some examples of critical shapes are transistors and interconnects on timing-critical paths. Variations in manufacturing that perturb the electrical properties of these shapes may have an adverse effect on the timing of the design. In order to improve para-

metric yield, the tolerances on such shapes is required to be small. Conversely, the *lithographic* process window is a measure of the degree of difficulty in printing a certain shape [102]. The smaller the process window for a shape, the more difficult it is to print in the presence of process variability. Some examples of shapes with low *lithographic process window* are line-ends and layout hot-spots [86]. Such shape constructs require greater flexibility (higher tolerances) in order for lithography to find a robust solution.

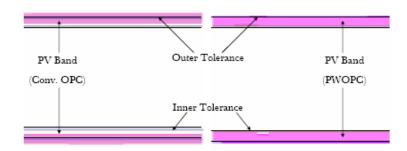

Figure 2.7 shows a transistor with a small outer tolerance and a large inner tolerance. This condition is typical of devices on critical paths. By this figure, the authors in IBM group [15] intend to show that they have performed both **OPC\*** (optical proximity correction) and **PWOPC\*** on this feature. They also show that they have subsequently generated lithographic contours at different process corners and compiled the process variability (PV) band which represents the outermost and innermost aerial image contours in the presence of variability. Finally, and most importantly, the authors want to show that whereas the use of OPC cannot ensure that contours across the process window will lie within acceptable *shape tolerances*, the use of PWOPC moves the PV bands to lie within the *shape slack*; thus validating their proposed methodology.

\* Optical proximity correction (OPC) is the technique of generating a mask to print a given layout [43]. A conventional OPC tool typically uses optical and resist models to predict the image of the mask on the wafer. The tool then computes the edge placement error (EPE) between the image and target and finally moves mask edges so as to minimize this geometric error. This technique optimizes the image at a single (nominal) point and hence does not provide a solution that is robust to variations in the lithographic process.

\* Process-window OPC (PWOPC) is a mask generation technique that increases lithographic yield by improving image quality at multiple process corners [15]. This method computes the aerial image contours at a number of different lithographic process points

and uses a weighted sum of EPE as the cost function for minimization. When tolerances are specified, the algorithm optimizes for weighted EPE until a contour at a certain corner exceeds the bounds, at which point the computational effort shifts to optimization at that corner alone [57].

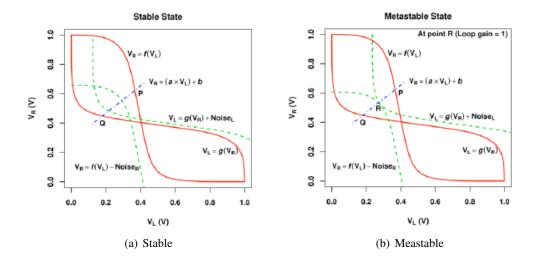

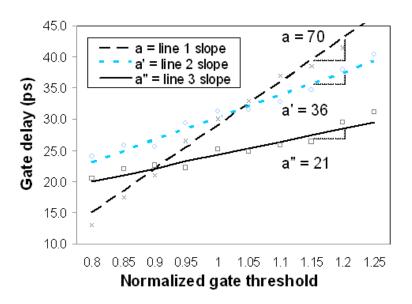

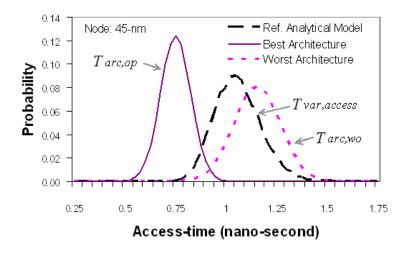

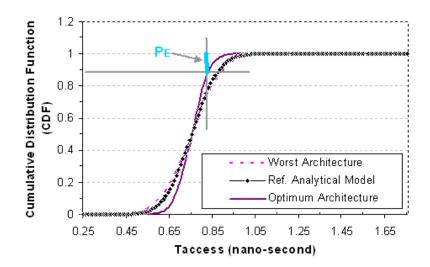

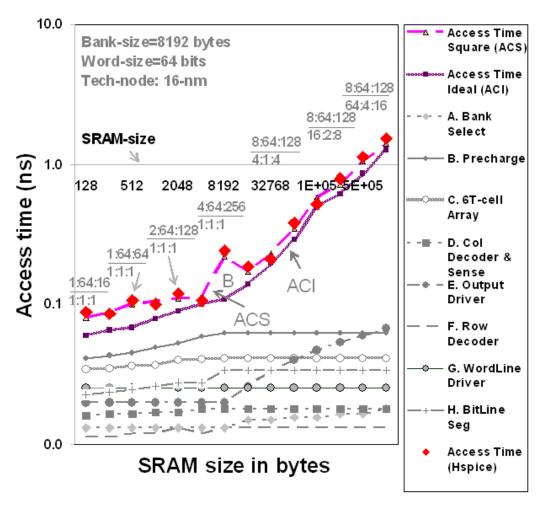

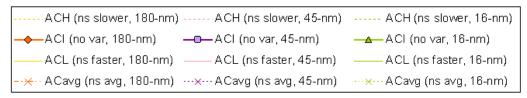

**Figure 2.7:** Benefits of using tolerances with PWOPC [15].