# **UC Santa Barbara**

# **UC Santa Barbara Electronic Theses and Dissertations**

# **Title**

Development of III-Nitride Tunnel Junctions and p-n Diodes by Ammonia-Assisted Molecular Beam Epitaxy

# **Permalink**

https://escholarship.org/uc/item/9px1s8b0

## **Author**

Wang, Jianfeng

# **Publication Date**

2020

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

# Santa Barbara

Development of III-Nitride Tunnel Junctions and p-n Diodes by Ammonia-Assisted

Molecular Beam Epitaxy

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Materials

by

Jianfeng Wang

Committee in charge:

Professor James Speck, Chair

Professor Claude Weisbuch

Professor Steven DenBaars

Professor Umesh Mishra

September 2020

| Claude Weisbuch |  |  |

|-----------------|--|--|

| Steven DenBaars |  |  |

| Umesh Mishra    |  |  |

James Speck, Committee Chair

The dissertation of Jianfeng Wang is approved.

September 2020

[This page is optional]

Development of III-Nitride Tunnel Junctions and p-n Diodes by Ammonia-Assisted

Molecular Beam Epitaxy

Copyright © 2020

by

Jianfeng Wang

#### ACKNOWLEDGEMENTS

There are many people I'd like to thank for helping me throughout this journey. I'd like to thank my parents for their dedication in my education which bring me to graduate school. In Penn State, my undergraduate advisor Professor Clive Randall offered me the first key to the door of research. My co-advisor Dr. Ramakrishna Rajagopalan showed me research can be fun and enjoyable. He also helped me with every detail about graduate school applications.

The life at UCSB has been a great journey. I would like to thank my advisor Professor James Speck for giving me the great opportunity, for sharing his passion for science, and for all the guidance along the way. I would like to thank my committee members, Professor Claude Weisbuch, Professor Steve Denbaars, and Professor Umesh Mishra for the great classes they teach, their kind suggestions and helping me with the academic checkpoints.

I was lucky to have many great mentors in graduate school. Dr. Erin Young showed me how to use MBE and gave us the opportunity to take care of the 930 she treasured so much after she left. Dr. Elaheh Ahamed gave us great research suggestions, cared for our experience, and helped me a lot with job search. Dr. Asad Mughal showed me how to use cleanroom and gave me a lot of career advises. Dr. Burhan SaifAddin helped me with research. We also had many inspiring conversations. I want to thank all my mentors for showing me how to do research and answering all my questions.

None of my research would be possible without the MBE lab managers, Kurt Olsson and John English. Kurt work tirelessly and takes good care of all the MBE system - a seemingly impossible job. Part of my joy for working in the MBE lab come from working with John, watching him came up with genius ideas for every problem, and reading his fun notes on toolboxes. I would also like to thank the Nanofab staff and the CNSI lab managers. Including

Dr. Youli Li, Aiden Hopkins, Brian Lingg. Special thanks to Dr. Tom Mates for the many SIMS hours. I also want to thank the SSLEEC and Materials department staff for their help and support.

I would like to thank my wonderful teammates that collaborated with me and helped me with my research. First, I would like to thank my fellow nitride MBE lab mates, Dr. Kelsey Jorgensen, Kai Shek Qwah, Dr. Christian Robertson, Dr. Richard Cramer, Dr. Erin Young, Dr. Micha Fireman, Christian Wurm, Zachary Biegler, and Dr. Morteza Monavarian. We went through the exhausting openings together, survived the difficult times by encouraging each other, and shares great time outside of work. Many of them are also dear friends to me. I want to thank the diode team for achieving such great result in a very short time frame thanks to everyone's kind collaboration. The team members include Dr. Esmat Farzana, Dr. Kelsey Jorgensen, Kai Shek Qwah, Zachary Biegler, Dr. Morteza Mornavarian, Dr. Yuewer Zhang, and Dr. Christian Robertson. I also want to thank the UV team. Thanks to Dr. Burhan SaifAddin for his mentorship, Chris Zollner for the AlN on SiC templates I used for Chapter 3's work, Dr. Abdullah Almogbel for the discussions on n-AlGaN, Michael Iza for leading the meetings, Yifan Yao for help with processing, Micheal Wang and Vincent Rienzi for the fruitful discussions. I am thankful for the Speck group members. Thanks to Wan Ying Ho for teaching me how to process LEDs, Yi Chao Chow for his suggestions and help with processing, Dr. Bastien Bonef for the APT measurements, Dr. Yuewei Zhang for his great suggestions, Akhil Mauze for the great chats, Cheyenne Lynsky for the suggestions about p-GaN studies, Dr. Daniel Myers and Dr. Andrew Espenlaub for helping me as senior group members. I would like to thank my office mate Cheyenne Lynsky and Dr. Matthew Wong for the great discussions about science and life. I am also thankful for all the SSLEEC and MBE lab

colleagues. It is my great privilege to work in an inspiring research environment built by their shared effort. I am also thankful for the women community in SSLEEC, Materials, ECE, and STEM in general.

Outside of the UCSB campus I would like to thank my friends, both those in Santa Barbara and those live elsewhere, for helping me to stay happy and showing me there's infinite possibility in life beyond success in work. I would like to thank my cat Sadie for allowing me to pet her and brush her so that I can stay sane. Fortunately, she has more hair than average PhD student. Last but not the least, I want to thank my families, especially my grandmother for caring for me and supporting me to get to where I am today.

I'm really fortunate to have all the people helping me to get here. I'm grateful for everyone and every moment, mentioned here or not, on this journey.

#### VITA OF JIANFENG WANG

# September 2020

Engineering Science Building Rm 3215C, University of California, Santa Barbara, CA, USA, 93106

Email: lisa.wjf@gmail.com

Tel: +1-(814)-206-6862

Linkedin: www.linkedin.com/in/jianfeng-wang-ucsb

#### SUMMARY OF SKILLS

- Conducted research for > 6 years, focusing on epitaxial growth, characterization, processing, and testing of III-Nitride semiconductor, (UV) LEDs, p-n diodes, tunnel junctions, optical/power devices and supercapacitors

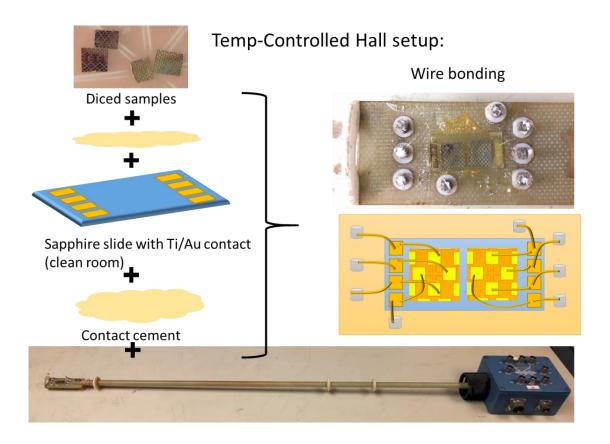

- Operated, maintained, and trained junior students on sophisticated instruments such as NH<sub>3</sub>-assisted Molecular Beam Epitaxy (MBE) system and temp-controlled Hall setup

- Wrote 2 first-author journal articles, a patent, presented at 2 international conferences and 3 reviews

- Experienced team player by collaborating in > 5 research groups and communicating across cultures

## **EDUCATION**

1. University of California Santa Barbara (UCSB)

Aug 2015 – Sep 2020 (Expected)

**Ph.D.** in Materials, Electronic/Photonic Materials course track, GPA 3.78

Thesis Advisor: James Speck (email: speck@ucsb.edu)

Committee: James Speck, Umesh Mishra, Steven Denbaars, Claude Weisbuch

2. Pennsylvania State University, University Park (Penn State)

Aug 2013 - May 2015

**B. S.** in Materials Science and Engineering, Minor in Economics, graduated with distinction **Thesis Advisor:** Clive Randall (email: car4@psu.edu) Ramakrishnan Rajagopalan (email: rur12@psu.edu)

3. Harbin Institute of Technology (HIT)

Aug 2011 – Jun 2013

**B. E.** in Welding, Honor School

#### RESEARCH SKILLS

- Instruments: NH<sub>3</sub>-MBE (UHV epitaxy system, including cryo panels, pumps, gauges, pressure control, mass flow controller, respirator), plasma-assisted MBE (PA-MBE), cleanroom, glovebox, MOCVD

- Materials Fabrication: e-beam evaporation, photolithography, reactive-ion etching, dicing saw, atomic layer deposition, plasma-enhanced CVD, inductive coupled plasma etching, chemical-mechanical polishing, flip-chip bonding, contact aligner, wire bonder, polisher

- Characterization: X-ray diffraction, reflection high-energy electron diffraction (RHEED), atomic force microscopy, secondary-ion mass spectrometry, (temp-controlled) Hall, capacitance-voltage measurements, scanning electron microscopy, photoluminescence, electroluminescence, 4-pt probe, LIV characterization, integrating sphere, oscilloscope, optical microscopy, electrochemical impedance analyzer, potentiostat, galvanostat

- Data Processing & Analysis: MATLAB, Origin, Microsoft Excel, Mathematica

- Modeling: SiLENSe, ddcc (1D, 2D), BandEng, Material Studio

- Other Software: L-edit, Klayout, LabVIEW, Crystal Maker, Autodesk 3D, C/C++

- Languages: English (Full Professional Proficiency), Mandarin (Native)

## RESEARCH PROJECTS

- 1. Low leakage and high reverse breakdown GaN p-n diodes for power electronic applications (ARPA-E PNDIODES program)

Aug 2019 Present

- Established growth condition for top-quality III-nitride material with low impurity level  $(3\times10^{15}/\text{cm}^3)$

- Characterized morphology and impurity level of the drift region material

- Measured diode IV behavior using high voltage setup (up to 2000 V)

• Developed low-leakage ( $I_{on}/I_{off} > 10^{10}$ ) high breakdown voltage (> 1000 V) GaN on GaN vertical p-n diodes with low ideality factor (n=1.3) and low ON resistance ( $R_{ON sp} = 0.28 \text{ m}\Omega \cdot \text{cm}^2$ )

## 2. Low voltage penalty hybrid tunnel junctions for visible applications

(Solid State Lighting & Energy Electronics Center at UCSB)

Aug 2016 – Present

- Grew GaN and InGaN-based hybrid and all MBE tunnel junctions on MOCVD grown LEDs

- Fabricated record-low voltage penalty (0.23 V) blue tunnel junction LEDs

- Analyzed high-volume industrial testing results using statistical methods

- Wrote patent for improved light extraction structure for tunnel junction LEDs

# 3. High conductivity Si-doped AlGaN for UV emitters

Oct 2017 – July 2019

(Solid State Lighting & Energy Electronics Center at UCSB)

- Grew high doping level (4×10<sup>19</sup>/cm<sup>3</sup>) low resistivity (3 mΩ·cm) n-Al<sub>0.6</sub>Ga<sub>0.4</sub>N on AlN/SiC templates

- Characterized the dislocation density, alloy composition, relaxation ratio, dopant level, and electrical properties of the AlGaN thin film

- Fabricated thin film flip chip UVC tunnel junction LEDs with doubled light extraction efficiency

- Measured the electrical and optical performance of the UV emitter

- Simulated the band structure to improve epi design

#### 4. Mg-doped GaN with controllable doping by valved Mg cell

Aug 2015 - Aug 2017

- Maintained valved Mg cell on MBE and temperature-controlled Hall setup

- Grew Mg doped GaN with low resistivity, high quality, and highly controllable doping up to 3×10<sup>20</sup>/cm<sup>3</sup>

- 5. **Lithium-ion supercapacitors with pre-lithiated graphite anode** Apr 2014- May 2015 (Project founded by NSF ERC Advanced Self-Powered Systems of Integrated Sensors and Technologies (ASSIST))

- Developed Li-ion capacitors with high energy density and cyclability, large voltage range, as well as ultra-low self-discharge

- Characterized coin cell performance such as cyclic voltammetry, constant charge discharge by electrochemical measurements

- Assembled capacitor and electrical double layer capacitor (EDLC) coin cells in glove box

- Fabricated pre-lithiated graphite anode with controlled degree of lithiation

- Synthesized electrode using powder materials

- Fabricated PVDF membranes by phase inversion process to be used as separators for Li-ion capacitors

#### **EXPERIENCE**

#### 1. Graduate Student Researcher, MBE growth of III-Nitride materials and devices

Aug 2015 – Present

Advised by Dr. James S. Speck, the Solid State Lighting & Energy Electronics Center (SSLEEC), UCSB

- Led a group of 3 to maintain, trouble-shoot, and modify cryogenic and ultra-high vacuum MBE systems

- Became a subject matter expert in growing top-quality III-nitride materials and devices using NH<sub>3</sub>-MBE

- Managed the training on multiple sophisticated instruments and coordinated system upgrade, part ordering, and maintenance with lab managers and vendors

- Coordinated collaborations with other groups and industry collaborators using multiple languages

## 2. Graduate Student Teaching Assistant

Apr 2017 - Jun 2017

Materials department, UCSB, with Prof. Van der Ven

- Managed a class of 30+ graduate students, coordinate time and locations for TA sessions

- Explained complex scientific concepts in basic terms and answer questions during the sessions

## 3. Undergraduate Student Researcher

Apr 2014 – May 2015

Advised by Dr. Clive A. Randall and Dr. Ramakrishnan Rajagopalan, Penn State

3. Summer Student Researcher Intern

Materials Research Institute, Penn State

Jun 2014 - Aug 2014

#### REFEREED PUBLICATIONS

#### **Journal Articles**

- 1. **Wang, J.,** Young, E. C., Ho, W., Bonef, B., Fireman, M., Margalith, T., & Speck, J. S. "III-Nitride Blue Light-emitting Diodes Utilizing Hybrid Tunnel Junction with Low Excess Voltage. Manuscript submitted (Aug 2020)

- 2. **Wang, J.,** SaifAddin, B. K., Zollner, C. J., Bonef, B., Alomogbel, A. S., Yao, Y., Iza, M., Zhang, Y., Fireman, M. N., Young, E. C., Nakamura, S., & Speck, J. S. "Optimization of n-type conductivity of Sidoped Al<sub>0.6</sub>Ga<sub>0.4</sub>N by ammonia-assisted molecular beam epitaxy for UV emitters," Manuscript in preparation (Sep 2020)

- 3. Farzana, E., **Wang, J.**, Monavarian, M., Itoh, T., Qwah, K. S., Biegler, Z. J., Jorgensen, K. F., & Speck, J. S. "Over 1 kV vertical GaN-on-GaN p-n diodes with low on resistance using molecular beam epitaxy," Manuscript in preparation (Sep 2020)

- 4. Qwah, K. S., Monavarian, M., Lheureux, G., Wang, J., Wu, Y.-R., & Speck, J. S. "Theoretical and experimental investigations of vertical hole transport through unipolar AlGaN structures: Impacts of random alloy disorder," *Appl. Phys. Lett.* 117, 022107 (2020)

#### **Conference Presentations**

- 1. Wang, J., Young, E. C., SaifAddin, B., Zollner, C., Almogbel, A., Fireman, M. N., Iza, M., Nakamura, S., Denbaars, S. P., & Speck, J. S. "Hybrid III-Nitride Tunnel Junctions for Low Excess Voltage Blue LEDs and UVC LEDs," 2019 Compound Semiconductor Week (CSW), Nara, Japan, 2019, pp. 1-1, doi: 10.1109/ICIPRM.2019.8819252.

- Wang, J., Young, E. C., SaifAddin, B., Zollner, C., Almogbel, A., Fireman, M. N., Iza, M., Nakamura, S., Denbaars, S. P., & Speck, J. S. "Hybrid MOCVD/MBE Tunnel Junctions for III-Nitride UVC LEDs and Low Voltage Penalty Blue LEDs," 13th International Conference on Nitride Semiconductors 2019 (ICNS-13), Bellevue, Washington, 2019.

- 3. **Wang, J.,** Ma, D., Rajagopalan, R., Randall, C., "Fabrication of Low Leakage Electrochemical Capacitors", ASSIST Webinar, Apr. 2015

- 4. **Wang, J.,** Ma, D., Rajagopalan, R., Randall, C., "Lithium-ion Capacitors using Pre-lithiated Graphite Anode", Z3.18, MRS 2014 Fall Meeting, Dec. 2014, Boston. (Poster).

- 5. Ma, D., Wang, J., Wang, Y., Rajagopalan, R., Randall, C., "Lithium-ion Capacitors using Prelithiated Graphite Anode", Materials Day 2014 Meeting, Oct. 2014, State College. (Poster).

- 6. Berbano, S., Ma, D., **Wang, J.**, Wang, Y., Lanagan, M., Rajagopalan, R., Randall, C., "Supercapacitor Materials & Devices for a Self-Powered and Adaptive Sensing Platform", NSF ASSIST Site Visit Raleigh, NC, May 19, 2015. (Poster).

#### LEADERSHIP/EXTRACURRICULAR

- 1. Volunteer of Nittany Greyhounds (organization for re-homing ex-racing dogs) Nov 2014 May 2015

- 2. Member of CSSA (Chinese Students and Scholars Association) Academic Department

Dec 2013 - May 2015

3. Head of Business Department of Enactus (Entrepreneurship Action US), HIT Chapter

May 2012 – Mar 2013

- Lead the department to cooperate with Walmart, providing female students with vocational training

- Participated in improving the operation mode of Sunshine Baby Autistic Children Training Center

- 4. Volunteer of Aiesec (international student organization for leadership development)

Jun 2012 - Aug 2012

• Cooperated with volunteers from Britain, Swiss, and Italy

Provided elementary school students from underdeveloped areas in China with classes about English and foreign culture

#### **ABSTRACT**

Development of III-Nitride Tunnel Junctions and p-n Diodes by Ammonia-Assisted

Molecular Beam Epitaxy

by

# Jianfeng Wang

Tunnel junctions (TJs) offer alternative designs and promise in some cases improved performances for nitride-based light-emitting diode (LEDs) and laser diodes (LDs). To achieve the high p-type doping in the TJ, Mg-doped GaN with controllable doping was desired. For visible wavelength range applications, two TJ techniques, hybrid TJ and all MBE TJ, were investigated. The study targeted a low voltage penalty compared to the conventional ITO contact. For ultraviolet (UV) applications, a hybrid UV TJ was enabled by the development of low resistivity n-AlGaN. In recent years, GaN-based power electronics have attracted great interests due to the attractive physical properties of the III-N material system. Vertical GaN p-n diodes with low leakage and high breakdown field was demonstrated.

With a valved Mg source and indium as surfactant, high quality p-GaN with controllable and reproducible doping levels are grown by NH<sub>3</sub> MBE. The high doping levels achievable enables TJ applications. Details of doing Hall measurements on p-GaN were also discussed.

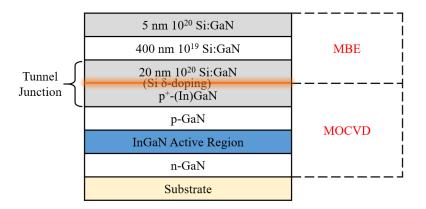

The voltage penalty of the TJ LEDs and LDs, in comparison with standard contact technologies, has been a major concern especially for commercial applications. In this study, methods to achieve low excess voltage were investigated. Using NH<sub>3</sub> MBE, hybrid GaN TJs were grown on commercial metalorganic chemical vapor deposition (MOCVD) grown blue LED wafers. Atom probe tomography (APT) and secondary ion mass spectrometry (SIMS) indicate 1 min buffered HF (BHF) clean of the regrowth interface reduced Mg and impurity

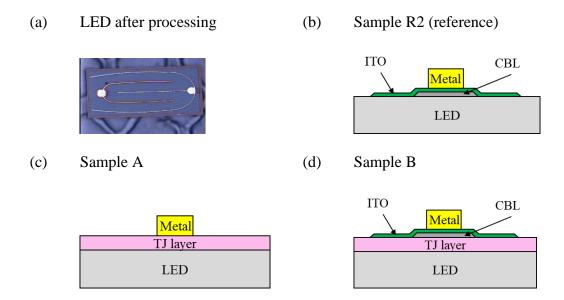

incorporation into the n++ regrown TJ layers. The wafers were processed and measured in parallel to reference wafers using both university and industry cleanroom and measurement setups. At 20 A·cm<sup>-2</sup>, TJ LEDs grown with Si  $\delta$ -doping at the junction interface processed in the university cleanroom had a forward voltage of 3.10 V in comparison to 2.87 V for LEDs processed with a standard ITO contact. Unencapsulated TJ LEDs processed by industrial process without indium tin oxide (ITO) or current blocking layer (CBL) had about 0.3 V excess voltage compared to reference LEDs. The TJ LEDs also had more uniform light emission profile. The low excess voltage and consistent results acquired in both settings suggest that tunnel junction can be scaled for industrial processes. Similar studies were done to for all MBE TJs. Systematic studies examined the effect of InGaN interlayers.

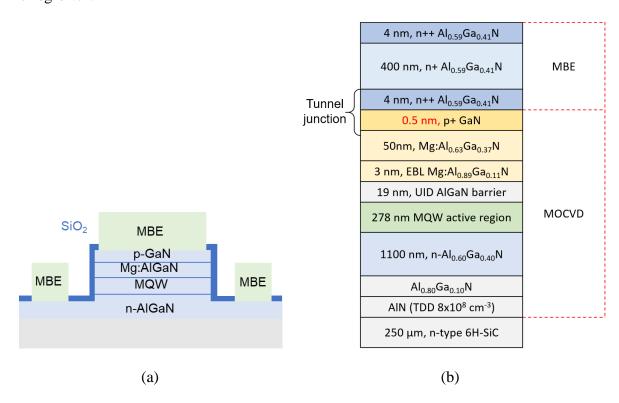

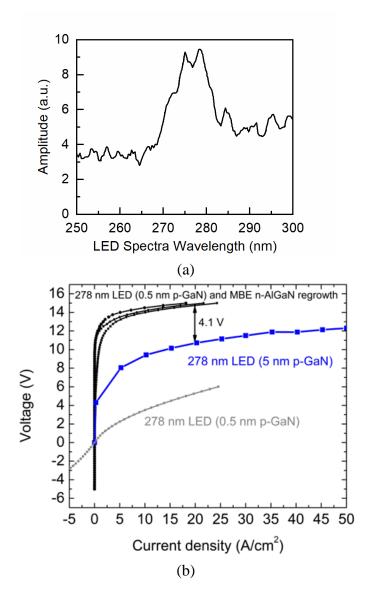

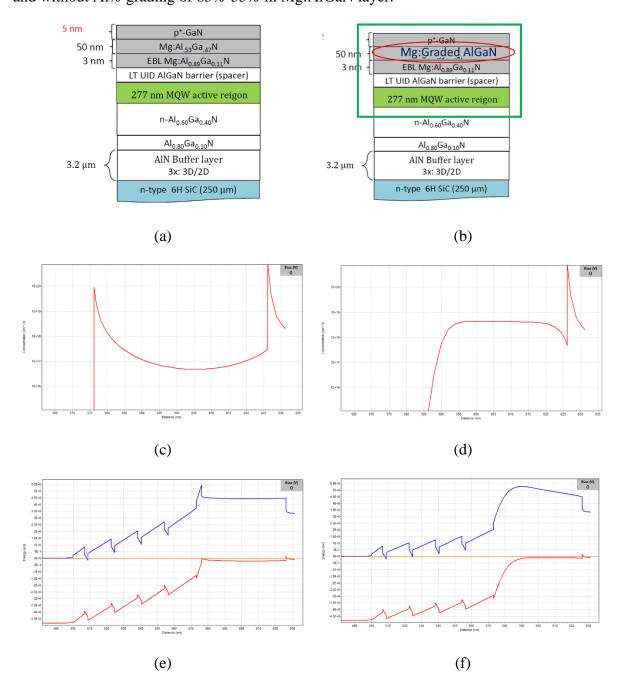

Highly doped n-Al<sub>0.6</sub>Ga<sub>0.4</sub>N can be used to form tunnel junctions (TJs) on deep ultraviolet (UVC) LEDs and potentially double the light extraction efficiency (LEE) compared to the use of p-GaN/p-AlGaN. High quality Al<sub>0.6</sub>Ga<sub>0.4</sub>N was grown by NH<sub>3</sub>-assisted molecular beam epitaxy (NH<sub>3</sub> MBE) on top of AlN on SiC substrate. The film is crack free under scanning electron microscope (SEM) for the thickness investigated (up to 1  $\mu$ m). X-ray diffraction reciprocal space map scan was used to determine the Al composition and the result is in close agreement with APT measurement result. By varying the growth parameters including growth rate, and Si cell temperature, n-Al<sub>0.6</sub>Ga<sub>0.4</sub>N with a doping level of  $4\times10^{19}$ /cm<sup>3</sup> and a resistivity of 3 m $\Omega$ ·cm was achieved. SIMS measurement shows that a high Si doping level up to  $2\times10^{20}$ /cm<sup>3</sup>. Using a vanadium-based annealed contact, ohmic contact with a specific resistance of  $10^{-6} \Omega$ ·cm<sup>2</sup> as determined by circular transmission line measurement (CTLM) was achieved. Finally, the n-AlGaN regrowth was done on MOCVD grown UVC LEDs to form UVC TJ

LED. The sample was processed into thin film flip chip (TFFC) configuration. The emission wavelength is around 278 nm and the excess voltage of processed UV LED is around 4.1 V.

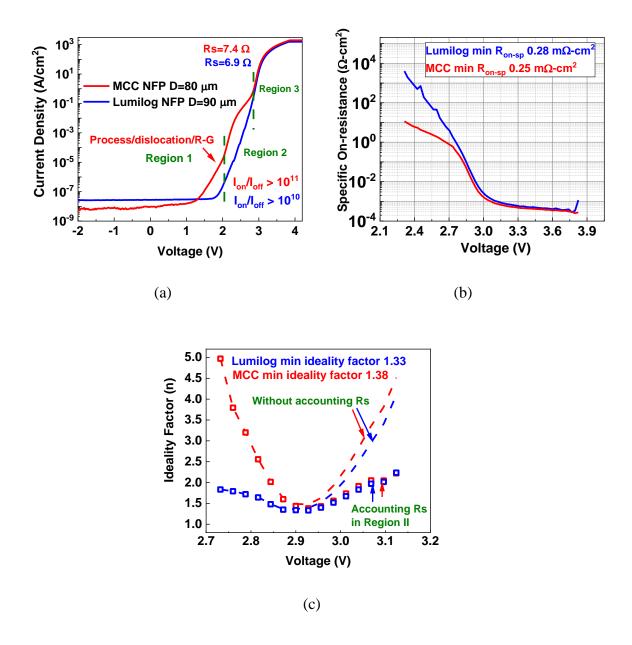

In the last part of the study, growth development of low leakage, high reverse breakdown field GaN p-n diodes was shown. Efforts were made to optimize morphology and achieve low impurity un-intentionally doped (UID) GaN in the drift region. Secondary ion mass spectrometry (SIMS) and capacitance-voltage (CV) measurements showed oxygen and carbon concentrations in the low  $10^{16}$  cm<sup>-3</sup> and N<sub>D</sub>-N<sub>A</sub> level of  $3\times10^{15}$  cm<sup>-3</sup>. This was combined with the use of high-quality p-GaN to make GaN p-n diodes with on/off ratio> $10^{10}$ , ideality factor of 1.33, and a minimum specific on resistance of 0.29 m $\Omega$ ·cm<sup>2</sup>.

# TABLE OF CONTENTS

| Chapter 1 p-type doping of GaN by valved Mg cell for tunnel junction application     | tions 1 |

|--------------------------------------------------------------------------------------|---------|

| 1.1 Introduction                                                                     | 1       |

| 1.1.1 III-Nitride MBE                                                                | 1       |

| 1.1.2 Valved Mg Cell                                                                 | 2       |

| 1.1.3 Mg-doping of III-Nitride Materials                                             | 6       |

| 1.1.4 Hall calibration sample epi structures                                         | 7       |

| 1.1.5 Temperature Controlled Hall Measurement                                        | 10      |

| 1.2 Impurity reduction in p-GaN                                                      | 11      |

| 1.3 Range of Mg doping level achieved                                                | 15      |

| 1.4 H <sub>2</sub> diffusion in MBE p-GaN grown with high NH <sub>3</sub> flux       | 16      |

| References                                                                           | 19      |

| Chapter 2 Hybrid Tunnel Junctions for Visible Applications                           | 22      |

| 2.1 III-nitride blue light-emitting diodes utilizing hybrid tunnel junction with low | excess  |

| voltage                                                                              | 22      |

| 2.1.1 Introduction                                                                   |         |

| 2.1.2 Experimental                                                                   |         |

| 2.1.3 Results                                                                        | 29      |

| 2.1.4 Discussion                                                                     |         |

| 2.4.5 Conclusion                                                                     |         |

| 2.2. Hybrid growth technique of tunnel junction on c-plane and m-plane               | 44      |

| 2.2.3 p-GaN activation                                                               | 44      |

| 2.2.4 Sample cleaning                                                                | 45      |

| 2.2.5 NH <sub>3</sub> annealing before growth                                        | 45      |

| 2.2.6 n-TJ regrowth by MBE                                                           | 45      |

| References                                                                           | 48      |

| Chapter 3 Highly doped n-AlGaN with low resistivity for UV TJ LEDs                   | 56      |

| 3.1 Introduction                                                                     | 56      |

| 3.2 Experimental                                                                     | 58      |

| 3.3 Results                                                                          | 61      |

| 3.3.1 Epitaxial growth of AlGaN                                                      | 61      |

| 3.3.2 Doping optimization for Si-doped AlGaN                                         | 67      |

| A 3 3 HVC THEDs                                                                      | 71      |

| 3.4 Conclusion                                                                                | 73  |

|-----------------------------------------------------------------------------------------------|-----|

| 3.5 Future work                                                                               | 74  |

| References                                                                                    | 77  |

| Chapter 4 Growth development for low leakage high reverse breakdown GaN p-n                   |     |

| diodes                                                                                        | 86  |

| 4.1 Introduction                                                                              | 86  |

| 4.2 Unintentionally doped GaN with low impurity concentration for n <sup>-</sup> drift region | 90  |

| 4.2.1 C/H/O levels vs growth rate by SIMS                                                     | 90  |

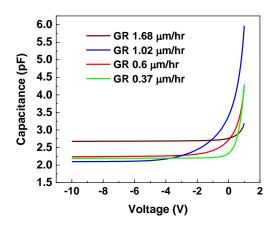

| 4.2.2 N <sub>net</sub> vs growth rate by CV measurements                                      | 91  |

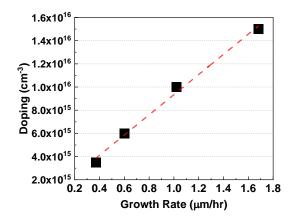

| 4.2.3 Morphology vs growth temperature by AFM                                                 | 93  |

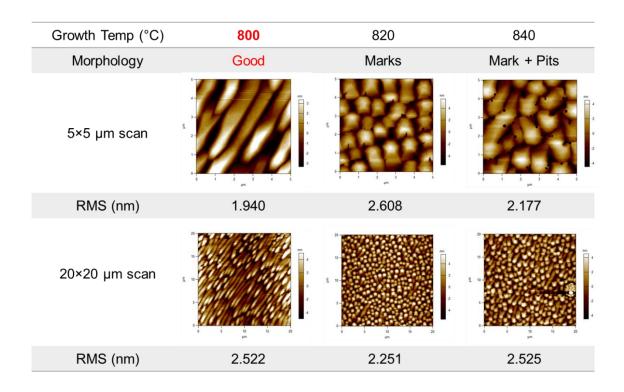

| 4.3 GaN p-n diode batch 1                                                                     | 94  |

| 4.4 GaN p-n diode batch 2                                                                     | 101 |

| 4.5 SIMS and CV analysis of batch 1 and 2 diodes                                              | 106 |

| 4.2 Conclusion                                                                                | 107 |

| References                                                                                    | 109 |

| Chapter 5 Summary and future work                                                             | 110 |

| 5.1 All MBE tunnel junctions for visible applications (on-going work)                         | 110 |

| 5.1.1 Introduction                                                                            | 110 |

| 5.1.2 Growth of InGaN by NH <sub>3</sub> MBE as interlayers                                   | 111 |

| 5.1.3 Experimental details for developing all MBE tunnel junction blue LEDs                   | 112 |

| 5.1.4 Initial Results                                                                         | 116 |

| 5.2 Summary and future work                                                                   | 117 |

| References                                                                                    | 119 |

| Appendices                                                                                    | 120 |

| Appendix A. Examples of ammonia MBE growth recipes                                            | 120 |

| A.1 SIMS stack for Si doping                                                                  | 120 |

| A.2 All MBE tunnel junctions with InGaN interlayer                                            | 120 |

| A.3 Continuous vertical diode                                                                 | 122 |

| Appendix B. Calibrations for NH <sub>3</sub> MBE growths                                      | 123 |

| B.1 Emissivity calibrations                                                                   | 123 |

| B.2 Growth rate and composition calibrations for AlGaN                                        | 124 |

| Appendix C. Hall measurements                                                                 | 127 |

| C.1 Room temperature Hall measurements                                                        |     |

| C.2 Temperature-controlled Hall measurements                                                  |     |

| Appendix D. SIMS measurements        | 129 |

|--------------------------------------|-----|

| Appendix E. Process travelers        | 130 |

| E.1 Pd/Au vs TJ LED                  | 130 |

| E.2 ITO vs TJ LED                    | 132 |

| E.3 Miscellaneous for LED processing | 134 |

| E.4 Diode_v1                         | 137 |

| E.5 Diode_v2                         | 139 |

| E.6 CV for UID on STN                | 142 |

| References                           | 144 |

# LIST OF FIGURES

| Figure 1.1 A typical design of an effusion cell. The charge is exposed to the growth environment.                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Valved Mg cell used for this work. (a) Picture of a valved corrosive source model vcor 110 manufactured by Riber. (b) The valve opening is controlled by the vertical movement of parts (blue area in image).                                                                                                                                                           |

| Figure 1.3 The doping level as a function of the week the Mg-doped samples are grown. The red and brown dots correspond to 10% and 15% valve opening respectively. The doping levels from 5 weeks' time fluctuates within 1× 10 <sup>18</sup> /cm <sup>3</sup> range, showing great reproducibility. Figure courtesy Prof. Nicholas Grandjean                                      |

| Figure 1.4 The Mg flux is controlled by both the cell temperature and valve opening. (a) The doping level increase exponentially as a function of cell temperature by CV measurements. The deviation on the start of trend is due to strong compensation effect. (b) Relative flux as a function of valve opening. The flux is highly controllable. Figure courtesy Prof. Nicholas |

| Grandjean                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 1.6 AFM images of GaN:C layer showing pits on the surface. The RMS roughness was 0.75 nm                                                                                                                                                                                                                                                                                    |

| Figure 1.7 SIMS measurements for GaN:C SIMS stack. The CBr <sub>4</sub> flow used was 30, 20, 10 sccm for the GaN:C layers from left to right                                                                                                                                                                                                                                      |

| Figure 1.11 SIMS of Mg, H, C, H, and O level in Mg SIMS stack sample                                                                                                                                                                                                                                                                                                               |

| Figure 1.13 The hydrogen diffusion in Mg-doped GaN follows Fick's law. (a) Initial concentration profile (b) concentration profile during the diffusion process as calculated by Mathematica                                                                                                                                                                                       |

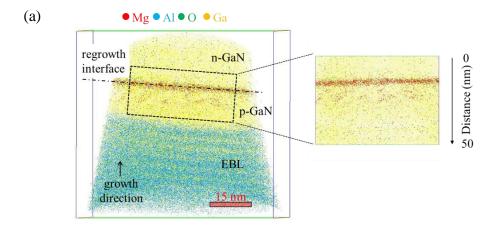

| side TJ    regrowth interface    MOCVD grown blue LED). Data courtesy of Dr. Bastien                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Bonef31                                                                                                                                    |

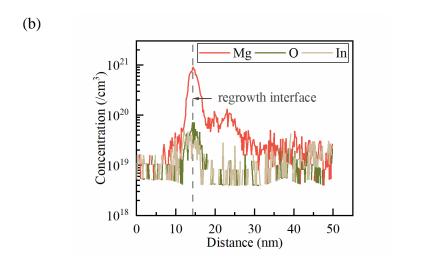

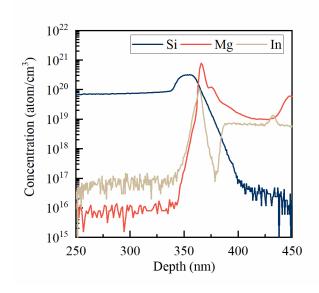

| Figure 2.4 SIMS concentration profiles for silicon, magnesium, and indium near the tunnel                                                  |

| junction region (no Si δ-doping). Data courtesy Dr. Tom Mates                                                                              |

| Figure 2.5 SIMS concentration profiles for silicon, magnesium, carbon, hydrogen, and                                                       |

| oxygen near the tunnel junction region for (a). samples treated by BFH dip (sample 3); and                                                 |

| (b). sample treated by solvent clean before regrowth (sample 4). The sample cleaned by BHF                                                 |

| has sharper Mg profile at the junction. The level of C, H, and O impurities were also lower.                                               |

| (Type II MOCVD wafer were used in this experiment). Data courtesy Dr. Tom Mates 33                                                         |

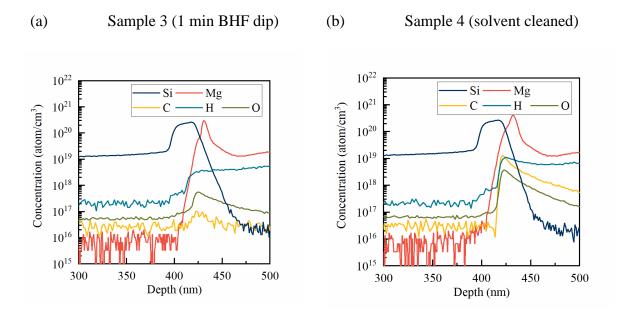

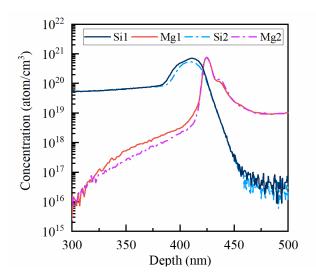

| Figure 2.6 SIMS concentration profiles for silicon and magnesium for TJ samples with and                                                   |

| without $\delta$ [Si] doping at the junction interface. The solid lines represent the sample with $\delta$                                 |

| [Si] (sample 1). The dotdash lines represent the sample without $\delta$ [Si] (sample 2). The peak                                         |

| Si level near the samples' junction are $7.1 \times 10^{20}$ cm <sup>-3</sup> and $5.4 \times 10^{20}$ cm <sup>-3</sup> respectively. Data |

| courtesy Dr. Tom Mates                                                                                                                     |

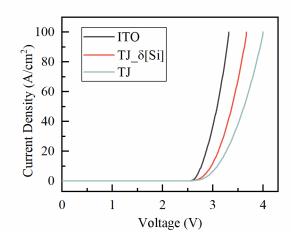

| Figure 2.7 I-V characteristics of standard (sample R1) and TJ LEDs with (sample 1) and                                                     |

| without (sample 2) Si $\delta$ -doping at the junction interface. At 20 A·cm <sup>-2</sup> , the voltage for sample                        |

| R1, sample 1, and sample 2 were 2.87, 3.10, and 3.27 V respectively. The voltage penalty of                                                |

| sample 1 is only 0.23 V as compared to sample R1.                                                                                          |

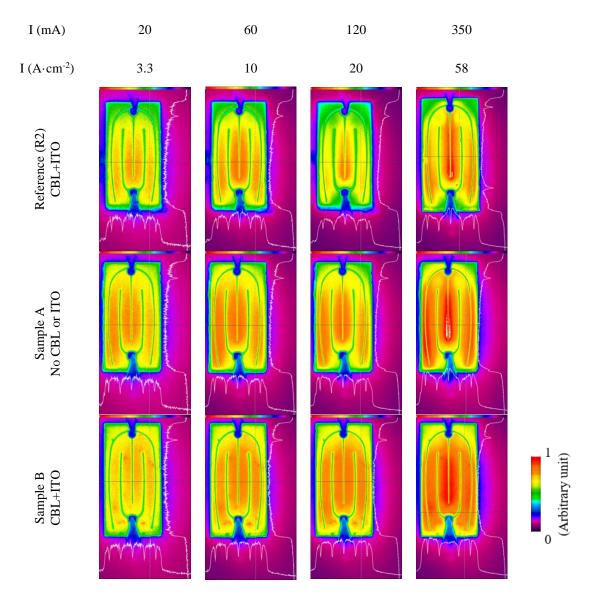

| Figure 2.8 Charge coupled device (CCD) images of a LED from the three wafers at various                                                    |

| current density. The white lines show the light intensity as a function of lateral or vertical                                             |

| position. The tunnel junction LEDs have more uniform light output than reference LEDs.                                                     |

| (The same scale was used for all images.)                                                                                                  |

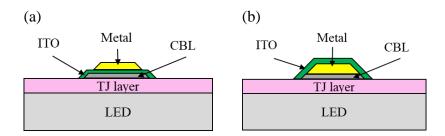

| Figure 2.9 Examples of proposed light extraction structure for TJ LEDs. (a). The conductive                                                |

| layer (ITO) is between metal contact and CBL. (b). The conductive layer (ITO) is above the                                                 |

| metal contact. 42                                                                                                                          |

| Figure 2.10 Examples of samples with and without titanium backside coating grown with                                                      |

| indium bonding. The indium and titanium on the sample backside partially evaporated during growth.                                         |

|                                                                                                                                            |

| Figure 2.11 LED samples showing emission under RHEED at the initial stage of growth. The                                                   |

| blue samples were LEDs. The yellow sample was GaN on sapphire template                                                                     |

| Figure 3.1 (a). MBE n-AlGaN regrowth was done on the on top of the p-GaN and n-AlGaN                                                       |

| region of the MOCVD grown UVC LED sample to form hybrid TJ UVC LED. Figure                                                                 |

| courtesy Dr. Burhan SaifAddin. (b). Schematic of the UVC tunnel junction (TJ) LED                                                          |

| epitaxial structure                                                                                                                        |

| Figure 3.2 (a) Front view and (b) side view of an Al cell crucible                                                                         |

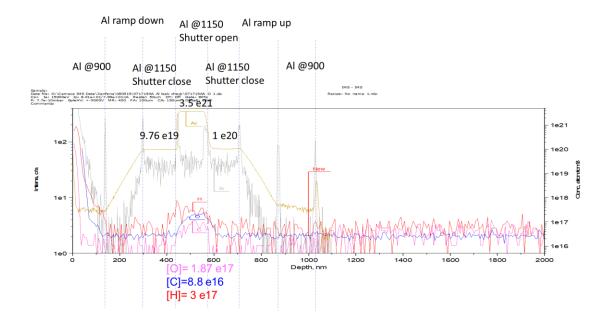

| Figure 3.3 SIMS measurements of Al cell shutter leak check.                                                                                |

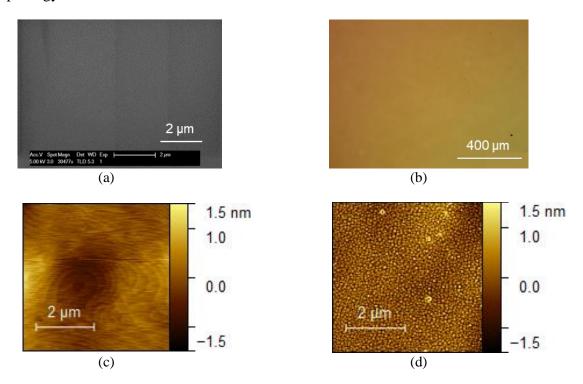

| Figure 3.4 (a) SEM image of a crack-free AlGaN layer (110 nm), Al=55.5%, and a growth                                                      |

| rate of 218 nm/hr. (b) Optical microscope image of a crack-free Al <sub>0.59</sub> Ga <sub>0.61</sub> N layer (1 $\mu$ m)                  |

| grown at 210 nm/hr showing no cracks. (c) AFM image of the AlN on SiC template, which                                                      |

| shows step flow growth. The rms roughness is 0.3 nm (d) AFM image of 100 nm AlGaN                                                          |

| layer grown by MBE on the template with Al%=65.5% and a growth rate of 216 nm/hr. The                                                      |

| surface was smooth and rms roughness is 0.48 nm. 63                                                                                        |

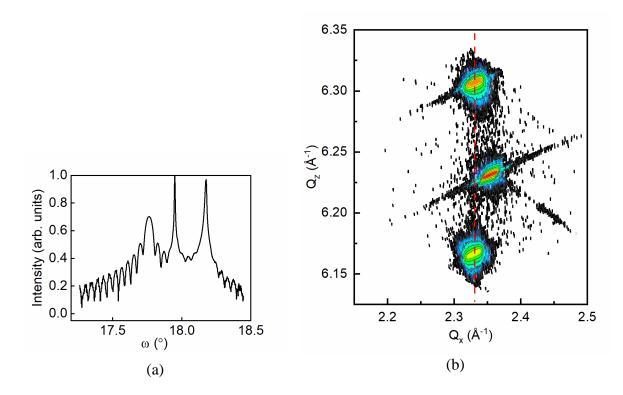

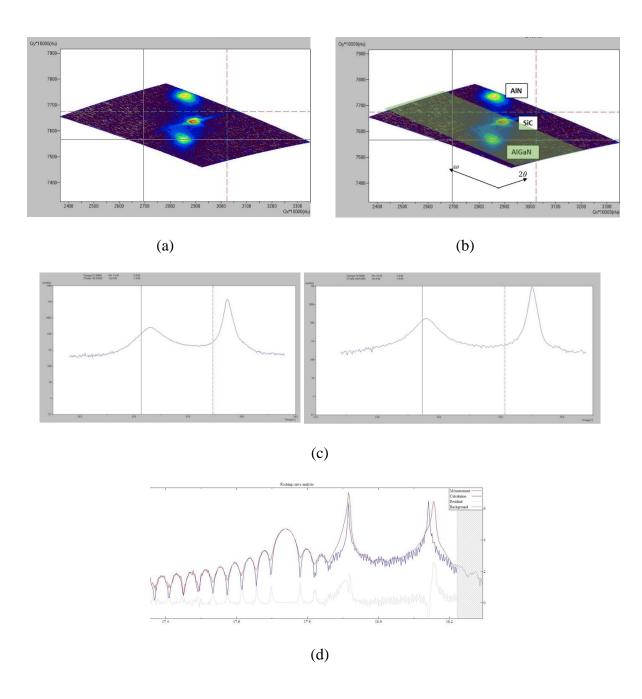

| Figure 3.5 (a) $\omega$ -2 $\theta$ scan of 100 nm Al <sub>0.60</sub> Ga <sub>0.40</sub> N film grown at 218 nm/hr with clear              |

| thickness fringes. The spacings between the fringes were used to calculate the film thickness                                              |

| and growth rate. From left to right, the peaks are: AlGaN, SiC, and AlN peaks. (b) RSM scan                                                |

| of 400 nm fully strained Al <sub>0.60</sub> Ga <sub>0.40</sub> N film grown at the same condition as in 3 (a). The |

|--------------------------------------------------------------------------------------------------------------------|

| separation between the SiC (in the middle) and the AlGaN peak (bottom) was used to                                 |

| calculate the Al% composition and relaxation ratio. The same $Q_x$ between the AlN (top) and                       |

| AlGaN peak shows that the AlGaN film is fully strained.                                                            |

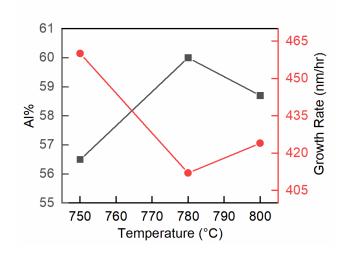

| Figure 3.6 Alloy composition and growth rate dependence with the growth temperature 65                             |

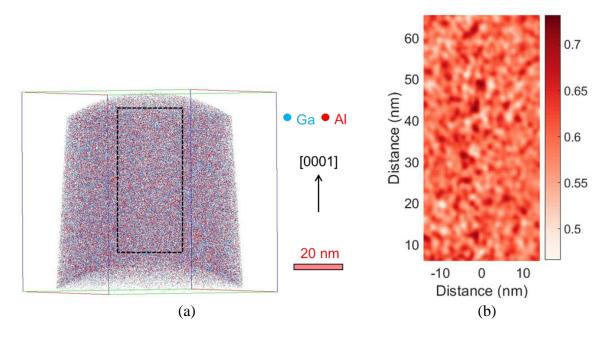

| Figure 3.7 3D APT reconstruction of 60 nm of Al <sub>0.59</sub> Ga <sub>0.41</sub> N showing Al and Ga atoms. (b)  |

| 2D distribution of the Aluminum fraction measured from the dashed rectangle shown in (a).                          |

| APT data courtesy Dr. Batien Bonef                                                                                 |

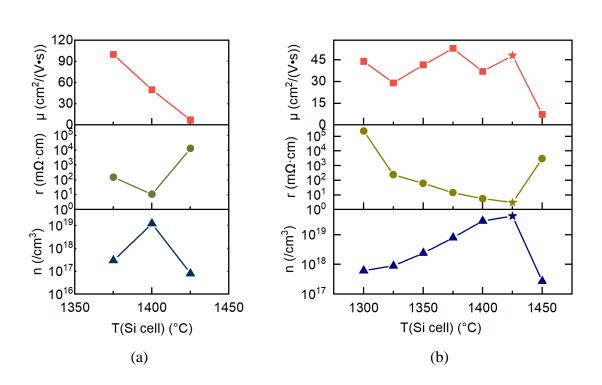

| Figure 3.8 Doping optimization for n-AlGaN by varying the Si cell temperature using a                              |

| growth rate of (a) 109 nm/hr at Al%=61.6% (series 1) and (b) 210 nm/hr at Al%=59.4%                                |

| (series 2). The n-AlGaN grown at 109 nm/hr with the Si cell at 1450 °C was resistive and                           |

| thus not shown in (a). The star shape denotes the optimum growth condition for the 210                             |

| nm/hr growth rate                                                                                                  |

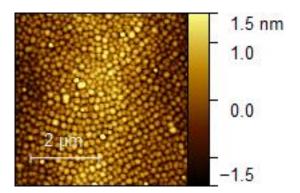

| Figure 3.9 AFM image of the optimum n-AlGaN growth condition (star sign in Figure 6).                              |

| The RMS roughness is 0.6 nm. There were no pits on the surface                                                     |

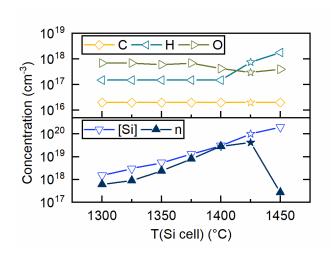

| Figure 3.10 Si, C, H, and O concentration in n-AlGaN series 2 samples measured by                                  |

| secondary ion mass microscopy (SIMS). The n-type carrier concentration is included for                             |

| comparison. The star shape denotes the optimum doping condition                                                    |

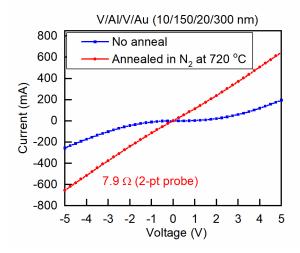

| Figure 3.11 IV curve for CTLM pattern with 10 nm gap on n-AlGaN with vanadium-based                                |

| contact before and after annealing in N <sub>2</sub> gas at 720 °C for 30 s                                        |

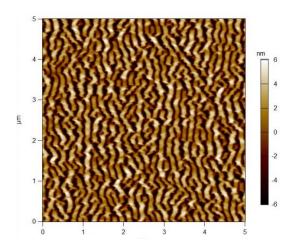

| Figure 3.12 AFM images of the n-AlGaN regrown area on the UVC TJ LED71                                             |

| Figure 3.13 (a) Electroluminescence spectra of the UVC LED with TJ. (b) I-V characteristics                        |

| for the processed TJ LED, an LED with the same MOCVD structure but without the TJ                                  |

| regrowth, and an identical LED without regrowth but with 5 nm of p-GaN on top of the                               |

| MOCVD structure. Figure courtesy Dr. Burhan SaifAddin                                                              |

| Figure 3.14 The hole concentration and band diagram for UV LEDs with and without Al%                               |

| grading. (a) Schematic of UV LED. (b) Schematic of UV LED with Al% grading of 85-55%                               |

| in Mg:AlGaN layer. (c) At a Mg concentration of $1 \times 10^{19}$ , hole concentration, h, is ~ $10^{16}$ . (d)   |

| with grading, h is $\sim 10^{18}$ . (e-f) Valence band is closer to Fermi level with grading                       |

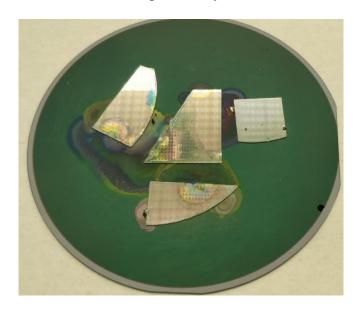

| Figure 3.15 Images of samples after the regrowth. Indium-crept on the sample surface for UV                        |

| LED wafers with SiO <sub>2</sub> hard mask. No such effect was observed for blank regrowth (for                    |

| example, the sample on the top right)                                                                              |

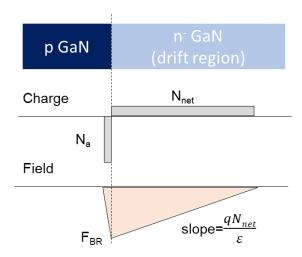

| Figure 4.1 Charge and field profile for GaN p-n diode with lightly-doped drift region. Figure                      |

| courtesy Dr. Yuewei Zhang.                                                                                         |

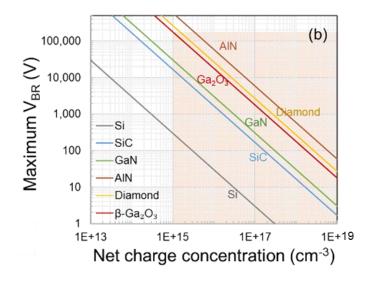

| Figure 4.2 Maximum breakdown voltage as a function of the net charge concentration in the                          |

| drift region for p-n diode grown using different materials. Figure courtesy Dr. Yuewei                             |

| Zhang                                                                                                              |

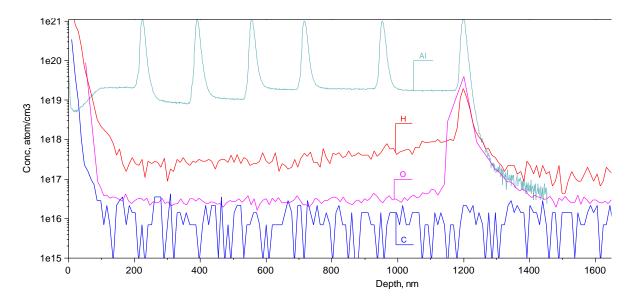

| Figure 4.3 SIMS measurements for O, C, and H level in UID GaN layers grown using growth                            |

| rate of 0.6, 1.0, 1.5, and 1.7 $\mu$ m/hr from right to left                                                       |

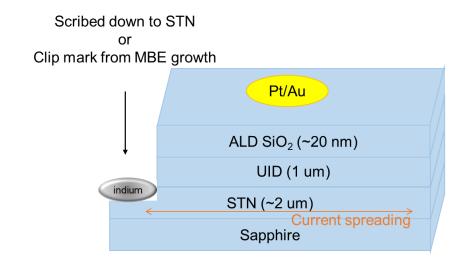

| Figure 4.4 Schematics of processed sample used for CV measurements. Metal-insulator-                               |

| semiconductor (MIS) structure was formed using ALD SiO <sub>2</sub> and Pt/Au                                      |

| Figure 4.5 CV measurements of UID GaN grown at different growth rates. (a) Capacitance as                          |

| a function of voltage. (b) Doping levels for different growth rate. Figure courtesy Dr. Esmat                      |

| Farzana                                                                                                            |

| Figure 4.6 AFM of 1 µm of UID GaN grown on the MCC substrate at 0.6 µm/hr and at growth temperature of 800, 820, and 840 °C, respectively. Figure courtesy Kai Shek Qwah.                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

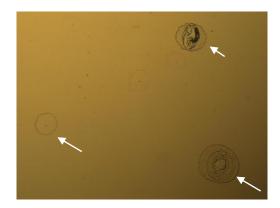

| Figure 4.7 Schematic of the diode epi structure. The drift region was 4 µm thick. (a)  Continuously grown diode. (b) Interrupted diode with ambient exposure at the p-n junction interface |

| Figure 4.8 AFM image for typical continuously grown diode. The surface was smooth with no pits observed. Figure courtesy Kai Shek Qwah                                                     |

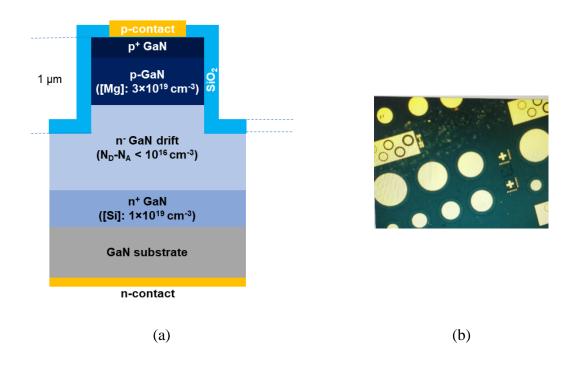

| Figure 4.9 Processed diode. (a) Schematics of the processed vertical GaN p-n diode. (b) Optical microscope image of the processed diode                                                    |

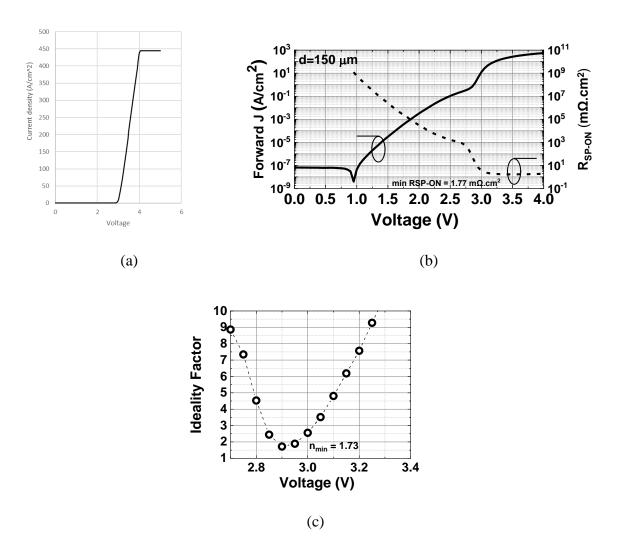

| Figure 4.10 Typical forward J-V characteristics of batch 1 diodes in (a) linear and (b) log scale. (c) Ideality factor of the diode. Figure courtesy Dr. Esmat Farzana, Dr. Morteza        |

| Monavarian                                                                                                                                                                                 |

| V. Figure courtesy Dr. Esmat Farzana, Dr. Morteza Monavarian                                                                                                                               |

| Figure 4.12 Histogram of reverse voltage $(V_{r_{-10}})$ of the diodes when a reverse current of 10                                                                                        |

| μA was reached                                                                                                                                                                             |

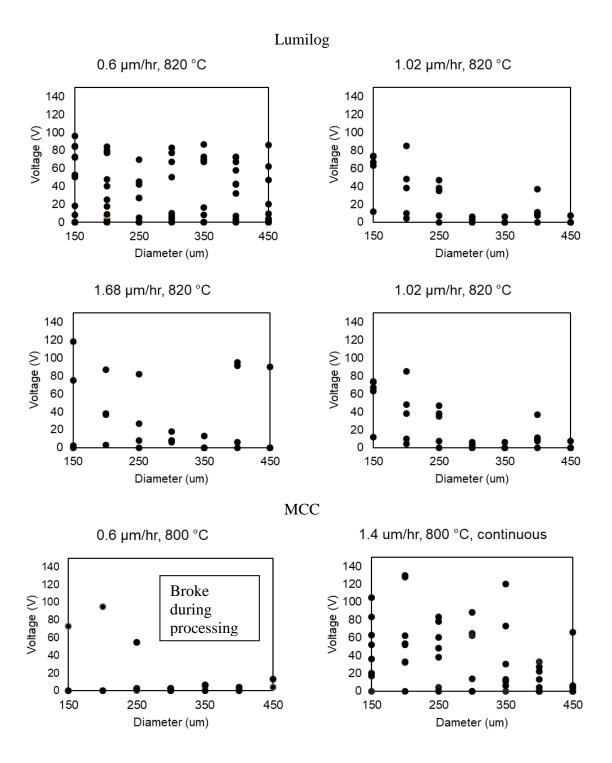

| Figure 4.13 Comparison of $V_{r_10}$ for (a) continuous and (b) interrupted diode                                                                                                          |

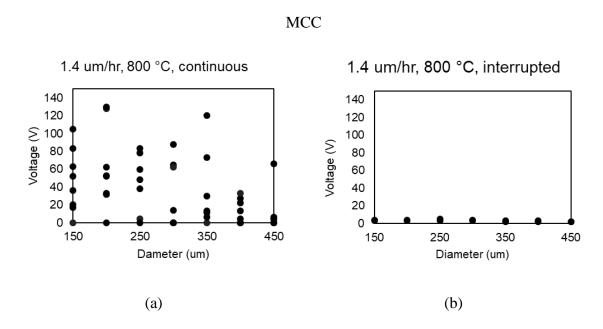

| Figure 4.14 Samples grown without the improved cleaning procedure showed dust and                                                                                                          |

| crater-like defect after growth. Figure courtesy Dr. Morteza Monavarian                                                                                                                    |

| Figure 4.15 Schematics of batch 2 diodes after processing                                                                                                                                  |

| Figure 4.16 Batch 2 diode performance in forward bias. (a) J-V characteristics in log scale. (b) Specific on-resistance. (c) Ideality factor. Figure courtesy Dr. Esmat Farzana, Dr.       |

| Morteza Monavarian. 104                                                                                                                                                                    |

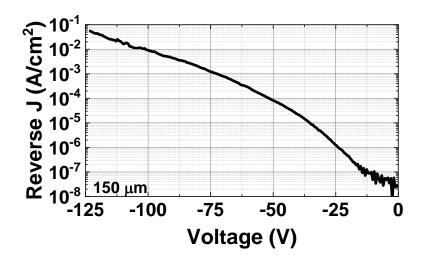

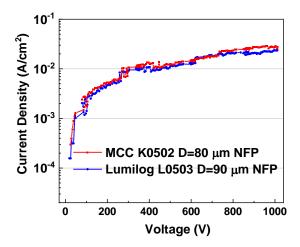

| Figure 4.17 Batch 2 diode performance in reverse bias. The leakage current was found to be dominated tool-related leakage. Both samples showed breakdown voltage over 1000 V               |

| (highest voltage of the instrument used for testing). Figure courtesy Dr. Esmat Farzana, Dr.                                                                                               |

| Morteza Monavarian. 105                                                                                                                                                                    |

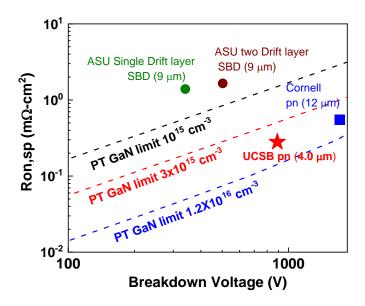

| Figure 4.18 Comparison of the diode performance achieved in this study and reported in                                                                                                     |

| literature. Note the diode in this study had thinner (4 µm) drift region and didn't reach                                                                                                  |

| breakdown. Figure courtesy Dr. Esmat Farzana. 106                                                                                                                                          |

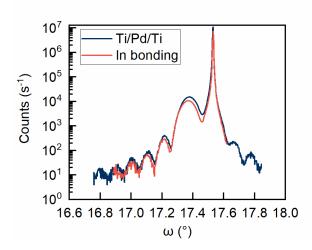

| Figure 5.1 $\omega$ -2 $\theta$ scan for InGaN sample coloaded by indium-bonding during growth. The                                                                                        |

| sample with backside coating had In%=6.0% while the one without backside coating had                                                                                                       |

| In%=6.4%. In growth rate for the two samples were 106 and 107 nm/hr, respectively 112                                                                                                      |

| Figure 5.2 Schematic of the regrowth LEDs' epitaxial structure                                                                                                                             |

# Chapter 1 p-type doping of GaN by valved

# Mg cell for tunnel junction applications

# 1.1 Introduction

## 1.1.1 III-Nitride MBE

Molecular Beam Epitaxy is a growth technique used to acquire high crystal quality semiconductors. An MBE system is usually under ultra-high vacuum (UHV) during operation [1]. The cryo panels helps maintain high vacuum in the growth chamber. During growth, sample is heated on the CAR (Continuous Azimuthal Rotation). The CAR is rotated so that the growth is uniform. When cells are heated, precursors have a longer mean-free-path than the distance from cell to substrate due to high vacuum. Gases and materials from cells react at the substrate. A pyrometer is used to monitor the substrate temperature as grown. The RHEED (Reflection High Energy Electron Diffraction) monitors the surface morphology.

III-Nitride materials can be grown by both N<sub>2</sub> plasma and NH<sub>3</sub> MBE. The former one's optimum growth regime is metal rich. Metal form ad-layers on substrate surface and is later dissolved to avoid metal island forming. [2] The defects in the material can form leakage path and affect the device performance. The growth temperature of plasma MBE is not limited. The

low temperature required for In incorporation can be met well still keeping good morphology.

Any 0-100% In incorporation (GaN-InN) can be achieved with plasma MBE. [1]

High V-III ratio is optimum for NH<sub>3</sub> MBE growth. [3] The growth temperature of NH<sub>3</sub> MBE is limited by the pyrolyzing temperature of NH<sub>3</sub>. At below 600°C, NH<sub>3</sub> pyrolyzing rate at the substrate surface reduces to zero. Thus, the low temperature necessary for In incorporation > 30% will lead to poor morphology. The NH<sub>3</sub> gas condenses on the cryo panel during growth. As more growth is done, green NH<sub>3</sub> ice accumulate on the panel. If cryo panel fails, the NH<sub>3</sub> ice will vaporize and over pressure the main chamber. Thus, a recovery is run after every two weeks of growth.

MBE is mainly used for research purpose and sometimes used in industry to fabricate electronics. LEDs and Lasers fabricated by MBE is generally inferior to equivalent devices produced by MOCVD. However, MBE provides a high vacuum environment (base pressure ~1×10<sup>-9</sup> torr) for crystal growth as opposed to MOCVD (15-750 Torr) [4]. Pyrometers and RHEED monitors the growth in real time. Thus, MBE's growth environment is easier to control, and the growth mechanism is better understood. It offers great research opportunities. Besides, the Mg-doped materials grown by MBE is active as grown [5] and allows device design with buried p-regions such as tunnel junctions. [6–10]

## 1.1.2 Valved Mg Cell

Traditionally, an effusion cell design as shown in Figure 1.1 is used for Mg doping. [11] In both plasma and NH<sub>3</sub> MBE, the Mg charge in such cell tends to be nitrided. The nitride layer forms a crust outside the Mg metal. It is then hard to get sufficient Mg flux out of the cell. The Mg-doping level is also unreproducible because the flux is not only depended on the cell

temperature but also affected by the nitride layer. One available solution is to run low temperature-high temperature cycles to crack the nitride layer and expose the inside charge. The steps are listed below:

<Raise up cell temperature to 450 °C – wait 60min>

<Cool down the cell to 100 °C – wait 30min>

<Repeat the cycle untill getting sufficient Mg flux>

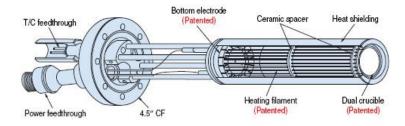

**Figure 1.1** A typical design of an effusion cell. The charge is exposed to the growth environment.

Another option, which is adopted by this work, is using a valved Mg cell. Figure 1.2 shows an valved Mg cell [12]. In this design, the Mg flux is controlled by both the valve opening and cell temperature. At idle state, the valve is close, separating Mg charge from the growth environment. While operating, the valve opens, and certain Mg flux is realized. After operation, the valve is kept open until the growth is done and system pumps down to low pressure. This way, negligible amount of active gas is trapped inside the cell. The exposure of Mg charge to the active gas is minimized.

**Figure 1.2** Valved Mg cell used for this work. (a) Picture of a valved corrosive source model vcor 110 manufactured by Riber. (b) The valve opening is controlled by the vertical movement of parts (blue area in image).

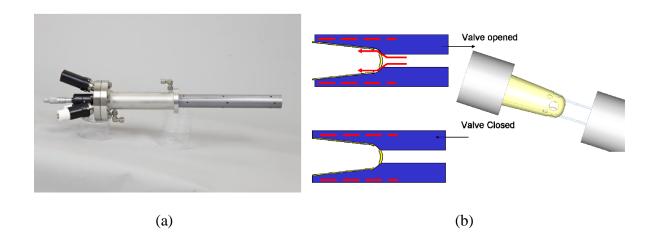

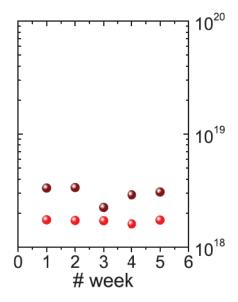

**Figure 1.3** The doping level as a function of the week the Mg-doped samples are grown. The red and brown dots correspond to 10% and 15% valve opening respectively. The doping levels from 5 weeks' time fluctuates within  $1 \times 10^{18}$ /cm<sup>3</sup> range, showing great reproducibility. Figure courtesy Prof. Nicholas Grandjean.

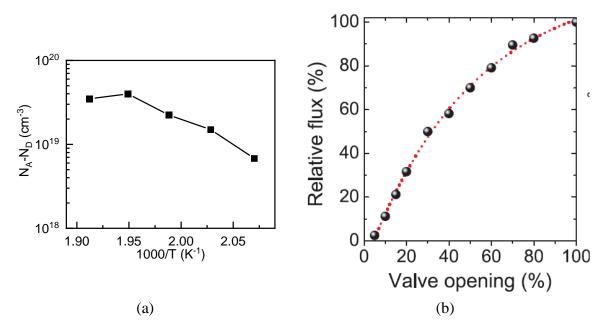

**Figure 1.4** The Mg flux is controlled by both the cell temperature and valve opening. (a) The doping level increase exponentially as a function of cell temperature by CV measurements. The deviation on the start of trend is due to strong compensation effect. (b) Relative flux as a function of valve opening. The flux is highly controllable. Figure courtesy Prof. Nicholas Grandjean.

Figure 1.3 (provided by Prof. Nicholas Grandjean (EPFL)) shows the doping levels of p-GaN grown with the valved Mg cell. The samples are grown in a 5 weeks' time span. Figure 1.4 (provided by N. Grandjean 2016) shows the doping level as a function of cell temperature and valve opening. The Mg doping acquired is highly reproducible and controllable.

This valved Mg magnesium cell offers great opportunity. M. Malinverni, et al. has shown that low temperature MBE p-doped Al(Ga)N can be grown with this cell design by CV measurements. [13] Previously, with the traditional effusion Mg cell, one of the biggest obstacles to developing tunnel junctions and LEDs with the Veeco Nitride 930 MBE used in this work is the inability to grow p-layer with high while stable doping level. It is expected that with this valved Mg cell, structures such as all MBE tunnel junctions will be possible.

# 1.1.3 Mg-doping of III-Nitride Materials

When III-nitrides were first studied, the development of GaN-based devices is hindered because the highly resistive p-layer. Later in 1989, Amano et al. discovered the method of activating MOCVD p-GaN by postgrowth exposure to a low energy electron beam irradiation. [14] In 1992, Nakamura et al. showed that a thermal annealing in N<sub>2</sub> would activate MOCVD p-GaN by the eliminating the Mg-H complexes. These works allow efficient MOCVD grown GaN-based LEDs.

In the hydrogen-rich MOCVD growth environment, magnesium is passivated by hydrogen, forming Mg-H complexes. [17,18] The p-layer layer can be activated by annealing in air or N<sub>2</sub>. For the hydrogen to escape, the layer must be exposed since n-type GaN has high energy barrier for hydrogen. [19] This limit the device design to be p-side up only. MOCVD p-GaN also suffers from memory effect. [20,21]

The ultra-high vacuum(UHV) growth environment of MBE allows p-GaN to be active as grown. The hydrogen partial pressure inside MBE chamber (<10<sup>-5</sup> torr) is several orders of magnitude less than in MOCVD growths (~400 torr), limiting the formation of Mg-H complexes. Due to the same reason, MBE p-GaN has minor memory effect than MOCVD p-GaN. However, Mg acceptors gets compensated more in MBE p-type materials. The compensating donor is believed to be nitrogen vacancies. [22–24] Using Indium as a surfactant has been shown to reduce the compensation ratio of NH<sub>3</sub> MBE p-GaN by one to two orders of magnitudes and improve the morphology. [5] Low temperature NH<sub>3</sub> MBE p-(Al)GaN has been studied by CV measurements with a valved Mg-cell. [13]

In MOCVD material, Mg is compensated nearly 100% by the hydrogen. The nitrogen vacancy level is magnitudes lower than that of Mg. Thus, after eliminating the Mg-H

complexes by annealing, the material becomes p-type. In MBE material, hydrogen level is much lower compared to Mg level. However, the nitrogen vacancy is only slightly lower than that of Mg at high temperature. This explains why the optimum temperature for growing MBE p-GaN is around 740 °C. [5,25]

Another challenge for acquiring good p-type materials is the high activation energy of Mg in III-Nitrides. Magnesium has the lowest activation energy (~200 meV) as an acceptor species in GaN. However, it is still a deep acceptor. The hole concentration in p-GaN is usually several percentages of the Mg concentration. The activation energy is found to increase with band gap energy. [26] Ohmic contact to p-GaN can potentially be achieved with p-type InGaN.

## 1.1.4 Hall calibration sample epi structures

For p-type doping, a Mg level of > high  $10^{18}$  is needed to achieve detectable hole concentration and ohmic contact. Hall measurements are also limited by detection limit of the setup for low mobility. Mobility below  $10~\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  cannot be accurately measured by the conventional Hall setup such as the one used for this study.

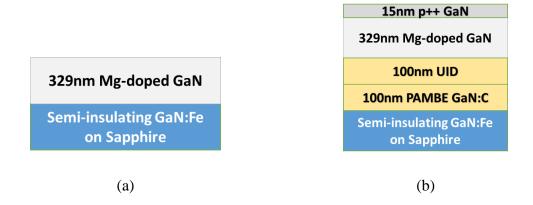

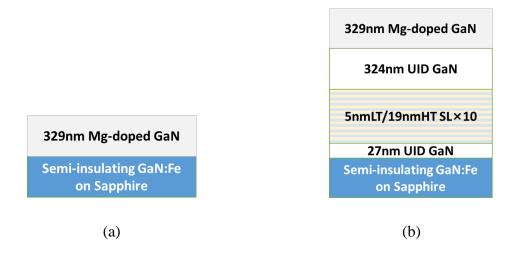

The structure of p-GaN Hall calibration samples is used as an example to explain the epi structure to use for Hall measurement. For quick calibrations, 300 nm p-GaN on semi-insulating GaN:Fe on sapphire sample is usually used. To acquire a better Ohmic contact, 15 nm of p++ contact layer is grown on top. The equations for analyzing bi-layer Hall structures can be found at citation [27] and [28]. It is necessary to confirm that if the contact layer will not affect the measurement results before each Hall measurements done using contact layers.

Parasitic conducting channels at the regrowth interface can also affect the measurement.

Carbon-doped GaN grown by PAMBE is insulating and used in high-electron-mobility

transistors (HEMT) [29]. By using 100 nm GaN:C at the regrowth interface, the impurities can be depleted. A 100 nm UID GaN layer can re-establish the growth morphology to be pit-free. Figure 1.5 shows the schematic epi structures for quick p-GaN Hall calibrations and more advanced structure for accurate Hall measurements.

**Figure 1.5** Schematic of epi structures for (a) quick p-GaN Hall calibrations and (b) accurate p-GaN Hall calibrations.

**Figure 1.6** AFM images of GaN:C layer showing pits on the surface. The RMS roughness was 0.75 nm.

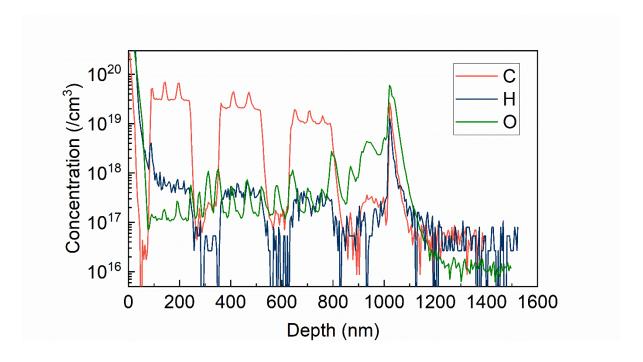

The growth of GaN:C was done using CBr<sub>4</sub> as the C source and N<sub>2</sub> plasma as the group V source. This requires a switch of growth mode if the later layers are grown using NH<sub>3</sub> MBE. The relationship between the CBr<sub>4</sub> flow and the C concentration was measured to be linear by SIMS measurements as shown in Figure 1.7. The GaN:C layers were grown using a N<sub>2</sub> flux of 1.1 sccm, a plasma power of 250 W, and a Ga flux of 1.8×10<sup>-7</sup> torr. The growth temperature was kept around 790-740 °C to achieve optimum III-V ratio and thus optimum growth regime [2]. The growth rate was 258 nm/hr and the CBr<sub>4</sub> flux were 10, 20, and 30 sccm from bottom to top GaN:C layers.

**Figure 1.7** SIMS measurements for GaN:C SIMS stack. The CBr<sub>4</sub> flow used was 30, 20, 10 sccm for the GaN:C layers from left to right.

The H concentration for C doped layers were higher than the un-intentionally doped layers. The oxygen profile had huge peak at the growth interface showed incorporation in later layers. The O concentration eventually stabilized around  $1\times10^{17}$ /cm<sup>3</sup>.

# 1.1.5 Temperature Controlled Hall Measurement

Room temperature Hall measurements can be used to determine the carrier concentration, mobility, and sheet resistance. Temperature controlled Hall measurements can be used to determine the acceptor concentration, compensating donor concentration, and activation energy.

In a non-degenerate p-type semiconductor, charge neutrality gives the following equation [30]:

$$\frac{p(p+N_D)}{(N_A-N_D-p)} = \frac{N_V}{g} \exp\left(\frac{-E_a}{k_B T}\right)$$

where p is the hole concentration,  $N_D$  is the donor concentration,  $N_A$  is the acceptor concentration,  $N_V$  is the effective density of states in the valence band  $(N_V = \frac{2(2\pi m_h^* k_B T)^{\frac{3}{2}}}{h^3})$ , h is Plank's constant,  $m_h^*$  is the effective hole mass in GaN,  $(m_h^* = 1.25m_0 \ [31])$ , g is the acceptor degeneracy (g = 4),  $E_a$  is the ionization energy of a hole,  $k_B$  is the Boltzmann constant.

The ionization energy is observed to decreases with increasing ionized acceptor concentration in Mg-doped GaN. [32,33] Thus, it is important to account for the reduction in ionization energy from the Columbic potential between ionized acceptors and holes. The following equation was adapted for p-type GaN [33]:

$$E_a(N_A^-) = E_{a0} - f \frac{q^2}{4\pi\epsilon} (N_A^-)^{1/3}$$

where  $N_A^-$  can be assumed to follow  $N_A^- = p + N_D^+$ ,  $N_D^+ = N_D$  (shallow donor).  $E_{a0}$  is the acceptor ionization energy. It can be assumed to be the same for p-GaN samples with Indium concentration less than  $1 \times 10^{20}$  cm<sup>-3</sup> [5]. f is the geometric factor  $(4\pi)^{\frac{1}{3}}\Gamma\left(\frac{2}{3}\right)$ . [33]

$\Gamma$  (x)is the gamma function. q is the charge of an electron or hole.  $\epsilon$  is the dielectric constant (assumed to be  $9.5\epsilon_0$ ).

By fitting the hole concentration and temperature relationship to the above equations, acceptor concentration, compensating donor concentration, and activation energy can be determined.

# 1.2 Impurity reduction in p-GaN

Mg-doped GaN are grown with a Veeco Gen 930 MBE system with conventional effusion cells for Ga, In, Al, Si, and valved Mg cell corrosive source model vcor 110 manufactured by Riber Inc. Purified NH<sub>3</sub> feed though an unheated showerhead injector. GaN:Mg Hall samples were grown on top of semi-insulating GaN:Fe on sapphire template manufactured by Lumilog Inc. Growths are done in a NH<sub>3</sub>-rich growth regime. The Mg source was kept at 250 °C and the opening was varied to achieve the desired amount of Mg incorporation.

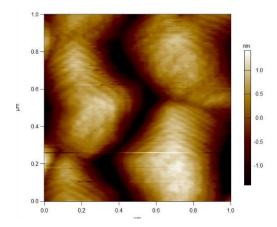

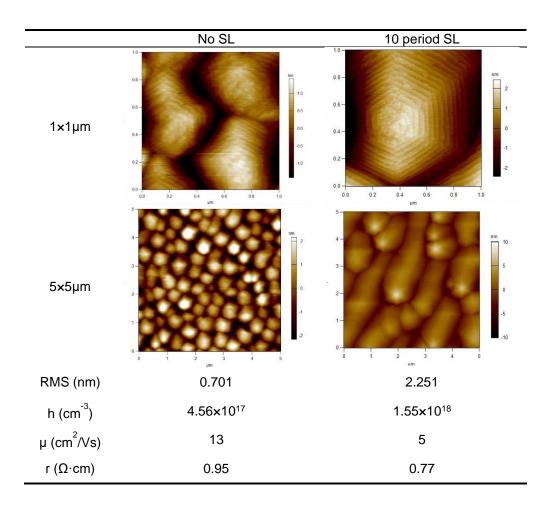

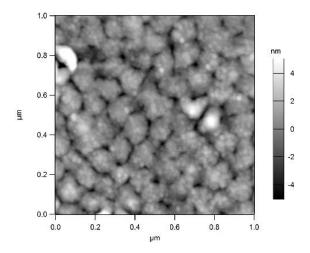

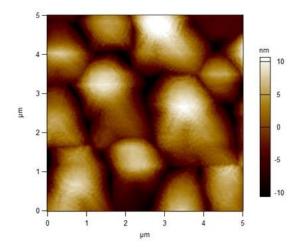

Figure 1.8 shows the atomic force microscopy (AFM) image of a p-GaN sample grown at typical growth condition. 329 nm of Mg-doped GaN was grown with a growth rate of 281 nm/hr at a growth temperature of 760 °C. Indium with a flux of  $1\times10^{-8}$  torr was used. The NH<sub>3</sub> flow rate was 200 sccm. The Mg valve was at 25% opening. The  $1\times1~\mu\text{m}^2$  AFM image shows no pits on the surface. The root mean square (rms) roughness is 0.701 nm.

**Figure 1.8** Typical AFM image of p-GaN grown with indium surfactant.

Hall measurements showed that the hole concentration is  $4.56 \times 10^{17}$  cm<sup>-3</sup>, with a resistivity of  $0.95~\Omega$ ·cm, and a mobility of  $13~\text{cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ .

A 10 period of 5 nm low temperature InGaN/19 nm high temperature GaN superlattice [34] was grown under the p-GaN to test its effect in terms of impurity reduction. The p-GaN growth condition was kept the same as the sample described above. Schematic of the p-GaN structure with and without the superlattice is shown in Figure 1.9.

**Figure 1.9** Schematic of the epi structure for p-GaN Hall sample with and without 10 periods of low temperature/high temperature impurity reduction super lattice.

Table 1.1 compares the AFM and Hall measurement result for the two samples. The superlattice reduced the resistivity of the p-GaN without degrading the morphology.

**Table 1.1** AFM images and Hall measurements for p-GaN grown at the same condition with and without impurity reduction super lattice.

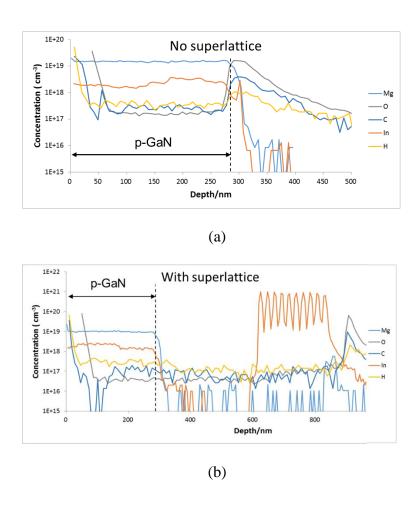

To investigate the impurity concentration change from the use of superlattice, Secondaryion mass spectrometry (SIMS) measurements were done for the two sample. Figure 1.10 shows the Mg, In, C, H, and O concentrations in the samples. The result is summarized in Table 1.2.

**Figure 1.10** Secondary-ion mass spectrometry (SIMS) measurements of p-GaN sample grown with and without superlattice.

**Table 1.2** Summary of SIMS measurement for p-GaN grown with and without the superlattice.

| atom-cm <sup>-3</sup> | No SL                 | SL                     |

|-----------------------|-----------------------|------------------------|

| [Mg]                  | 1.49×10 <sup>19</sup> | 9.89×10 <sup>18</sup>  |

| [ln]                  | 2.33×10 <sup>18</sup> | 1.91×10 <sup>18</sup>  |

| [0]                   | 1.93×10 <sup>17</sup> | 3.77×10 <sup>16</sup>  |

| [C]                   | 2.51×10 <sup>17</sup> | <1.26×10 <sup>17</sup> |

| [H]                   | 3.61×10 <sup>17</sup> | 2.95×10 <sup>17</sup>  |

The O and C concentration was greatly reduced while the H level was almost the same. We suspect that the hydrogen was from the NH<sub>3</sub> used during growth and thus its incorporation wasn't reduced by the use of superlattice.

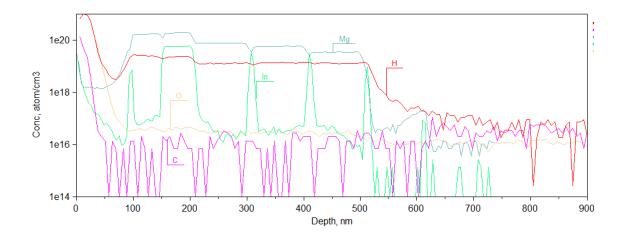

# 1.3 Range of Mg doping level achieved

The Mg doping level is controlled by either the Mg valve opening or the growth rate while fixing the Mg cell temperature at 250 °C. To map out the Mg level achievable, a SIMS stack with various growth condition (Table 1.3) was grown. The growth was done with a NH<sub>3</sub> flow of 200 sccm, an indium flux of  $5\times10^{-8}$  torr, at 750 °C. The result is shown in Table 1.3 and Figure 1.11. The maximum Mg level achieved was around  $3\times10^{20}$  cm<sup>-3</sup>, using a growth rate of 50 nm/hr and a Mg valve opening of 100%. This high doping level is beneficial for TJ applications where the Mg level in the p<sup>++</sup> layer is high. A typical Mg concentration for high quality p-GaN is around mid  $10^{19}$  cm<sup>-3</sup>, and is achieved using a growth rate of 300 nm·hr<sup>-1</sup>.

Table 1.3 Growth conditions for the Mg SIMS stack

| Mg%         | %     | UID                      | 80                       | 80, In                   | 80                       | 65                       | 50                       | UID                    | Template                 |

|-------------|-------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------------------------|--------------------------|

| Growth rate | nm/hr | 300                      | 100                      | 100                      | 300                      |                          |                          | N/A                    |                          |

| Mg          | /cm³  | 1.5<br>×10 <sup>18</sup> | 1.7<br>×10 <sup>20</sup> | 1.9<br>×10 <sup>20</sup> | 7<br>×10 <sup>19</sup>   | 5.7<br>×10 <sup>19</sup> | 3.5<br>×10 <sup>19</sup> | 5<br>×10 <sup>16</sup> | 1.2<br>×10 <sup>16</sup> |

| Н           | /cm³  |                          | 2.7<br>×10 <sup>19</sup> | 2.3×10 <sup>19</sup>     | 1.2<br>×10 <sup>19</sup> | 1.4<br>×10 <sup>19</sup> | 1.3<br>×10 <sup>19</sup> |                        |                          |

Figure 1.11 SIMS of Mg, H, C, H, and O level in Mg SIMS stack sample.

# 1.4 H<sub>2</sub> diffusion in MBE p-GaN grown with high NH<sub>3</sub> flux

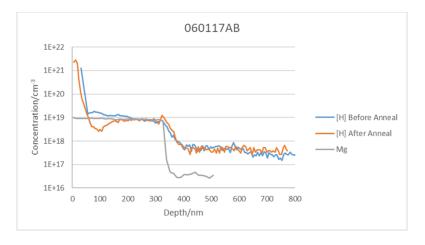

The H-Mg complex formed during p-GaN growth by MOCVD lower the formation energy of compensating defects [17]. Effort was made to see if passivation of MBE grown p-GaN can be realized by growing at high NH<sub>3</sub> flux of 1000 sccm. Figure 1.12 shows the SIMS profile for Mg and H level in as grown MBE p-GaN and the same sample after annealing in air at elevated temperature.

**Figure 1.12** SIMS measurement for Mg-doped GaN grown at 1000 sccm before and after annealing.

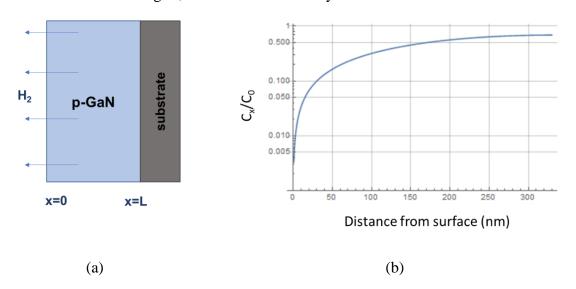

The hydrogen profile shows partial diffusion from the sample surface. The diffusion process can be simplified as single-side diffusion model with surface sink and an initial  $H_2$  concentration  $C_0$  across the sample thickness L as shown in Figure 1.13. The boundary conditions include: 1.  $H_2$  flux=0 at x=L (the growth interface between p-GaN and substrate). 2. The  $H_2$  concentration for the sample surface (x=0) is zero. The concentration changes with time based on the solution to Fick's law [35]:

$$c(x,t) = \sum_{n=0}^{\infty} \frac{4C_0}{(2n+1)\pi} \sin\left(\frac{(2n+1)\pi}{2L}x\right) \exp\left(-\left(\frac{(2n+1)\pi}{2L}\right)^2 Dt\right)$$

Where n is natural integral, and D is the diffusivity.

**Figure 1.13** The hydrogen diffusion in Mg-doped GaN follows Fick's law. (a) Initial concentration profile (b) concentration profile during the diffusion process as calculated by Mathematica.

Table 1.4 shows SIMS profile for a GaN:Mg sample grown at 800 °C with a NH<sub>3</sub> flux of 1000 sccm, a growth rate of 200 nm/hr and a Mg valve opening of 50%. Before annealing, the H:Mg ratio is 37%. The hole concentration was  $1\times10^{17}$  cm<sup>-3</sup>, the mobility was 8.5 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, the resistivity was 7.4  $\Omega$ ·cm. After annealing in air at 700 °C for 15 min, the Mg is fully

activated. With H:Mg = 5.7%, a hole concentration of  $1.7 \times 10^{17}$  cm<sup>-3</sup>, a mobility of 6 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, and a resistivity of 5.6  $\Omega$ ·cm. The resistivity of the sample decreased by the annealing process but is still high probably due to the high growth temperature. More studies need to be done to understand how to apply this to more standard p-GaN condition.

**Table 1.4** SIMS of p-GaN grown with high NH<sub>3</sub> flux before and after annealing.

|                  | Mg                   | Н                    | О                    |

|------------------|----------------------|----------------------|----------------------|

| Before annealing | 4.5×10 <sup>19</sup> | 1.7×10 <sup>19</sup> | 5.9×10 <sup>17</sup> |

| After annealing  | $4.4 \times 10^{19}$ | $2.5 \times 10^{18}$ | $1.0 \times 10^{18}$ |

# References

- 1. E. C. H. Kyle, PhD thesis, University of California, Santa Barbara, Materials, *Growth Development of III-Nitrides for Electronic Devices by Molecular Beam Epitaxy* (2016).

- 2. B. M. McSkimming, F. Wu, T. Huault, C. Chaix, and J. S. Speck, "Plasma assisted molecular beam epitaxy of GaN with growth rates >2.6μm/h," Journal of Crystal Growth **386**, 168–174 (2014).

- 3. T. Kuech, Handbook of Crystal Growth: Thin Films and Epitaxy (Elsevier, 2014).

- 4. R. Pelzel, "A Comparison of MOVPE and MBE Growth Technologies for III-V Epitaxial Structures," CS MANTECH Conference, May 13th 16th, 2013, New Orleans, Louisiana, USA (2013).

- 5. E. C. H. Kyle, S. W. Kaun, E. C. Young, and J. S. Speck, "Increased p-type conductivity through use of an indium surfactant in the growth of Mg-doped GaN," Appl. Phys. Lett. **106**, 222103 (2015).

- 6. J. T. Leonard, E. C. Young, B. P. Yonkee, D. A. Cohen, C. Shen, T. Margalith, T. K. Ng, S. P. DenBaars, B. S. Ooi, J. S. Speck, and S. Nakamura, "Comparison of nonpolar III-nitride vertical-cavity surface-emitting lasers with tunnel junction and ITO intracavity contacts," in (International Society for Optics and Photonics, 2016), Vol. 9748, p. 97481B.

- 7. J. Leonard, E. Young, B. P. Yonkee, D. A. Cohen, T. Margalith, S. Denbaars, J. Speck, and S. Nakamura, "Demonstration of a III-nitride vertical-cavity surface-emitting laser with a III-nitride tunnel junction intracavity contact," Applied Physics Letters **107**, 091105 (2015).

- 8. T.-Y. Seong, J. Han, H. Amano, and H. Morkoç, *III-Nitride Based Light Emitting Diodes and Applications* (Springer, 2017).

- 9. C. A. Forman, J. T. Leonard, E. C. Young, S. Lee, D. A. Cohen, B. P. Yonkee, R. M. Farrell, T. Margalith, S. P. DenBaars, J. S. Speck, and S. Nakamura, "Nonpolar GaN-based vertical-cavity surface-emitting lasers," in *2016 International Semiconductor Laser Conference (ISLC)* (2016), pp. 1–2.

- Y. Zhang, S. Krishnamoorthy, F. Akyol, S. Bajaj, A. A. Allerman, M. W. Moseley, A. M. Armstrong, and S. Rajan, "Tunnel-injected sub-260 nm ultraviolet light emitting diodes," Applied Physics Letters 110, 201102 (2017).

- 11. "Effusion Cell & Controller(id:408742) Product details View Effusion Cell & Controller from AlphaPlus Co., Ltd. EC21," https://alphaplus.en.ec21.com/Effusion\_Cell\_Controller--408646\_408742.html.

- 12. "CORROSIVE MATERIALS (eg. Sb) VALVED SOURCE Riber," https://www.riber.com/en/products/mbe-components-sources/21-effusion-sources/213-valved-sources/2133-vcor-series-all-pbn-valved-source.html.

- 13. M. Malinverni, J.-M. Lamy, D. Martin, E. Feltin, J. Dorsaz, A. Castiglia, M. Rossetti, M. Duelk, C. Vélez, and N. Grandjean, "Low temperature p-type doping of (Al)GaN layers using ammonia molecular beam epitaxy for InGaN laser diodes," Appl. Phys. Lett. **105**, 241103 (2014).

- 14. H. Amano, M. Kito, K. Hiramatsu, and I. Akasaki, "P-Type Conduction in Mg-Doped GaN Treated with Low-Energy Electron Beam Irradiation (LEEBI)," Jpn. J. Appl. Phys. **28**, L2112 (1989).

- 15. S. Nakamura, N. Iwasa, M. Senoh, and T. Mukai, "Hole Compensation Mechanism of P-Type GaN Films," Jpn. J. Appl. Phys. **31**, 1258 (1992).

- 16. S. Nakamura, T. Mukai, M. Senoh, and N. Iwasa, "Thermal Annealing Effects on P-Type Mg-Doped GaN Films," Jpn. J. Appl. Phys. **31**, L139 (1992).

- 17. C. G. Van de Walle and J. Neugebauer, "First-principles calculations for defects and impurities: Applications to III-nitrides," Journal of Applied Physics **95**, 3851–3879 (2004).

- 18. J. Neugebauer and C. G. Van de Walle, "Hydrogen in GaN: Novel Aspects of a Common Impurity," Phys. Rev. Lett. **75**, 4452–4455 (1995).

- 19. J. Neugebauer and C. G. Van de Walle, "Role of hydrogen in doping of GaN," Appl. Phys. Lett. **68**, 1829–1831 (1996).

- 20. Y. Ohba and A. Hatano, "A study on strong memory effects for Mg doping in GaN metalorganic chemical vapor deposition," Journal of Crystal Growth **145**, 214–218 (1994).

- 21. H. Xing, D. S. Green, H. Yu, T. Mates, P. Kozodoy, S. Keller, S. P. DenBaars, and U. K. Mishra, "Memory Effect and Redistribution of Mg into Sequentially Regrown GaN Layer by Metalorganic Chemical Vapor Deposition," Jpn. J. Appl. Phys. **42**, 50 (2003).

- 22. J. Neugebauer and C. G. V. de Walle, "Native defects and impurities in GaN," in *Advances in Solid State Physics 35*, Advances in Solid State Physics (Springer, Berlin, Heidelberg, 1996), pp. 25–44.

- 23. U. Kaufmann, M. Kunzer, M. Maier, H. Obloh, A. Ramakrishnan, B. Santic, and P. Schlotter, "Nature of the 2.8 eV photoluminescence band in Mg doped GaN," Appl. Phys. Lett. **72**, 1326–1328 (1998).

- 24. P. Kozodoy, S. Keller, S. P. DenBaars, and U. K. Mishra, "MOVPE growth and characterization of Mg-doped GaN," Journal of Crystal Growth **195**, 265–269 (1998).

- 25. M. Malinverni, J.-M. Lamy, D. Martin, E. Feltin, J. Dorsaz, A. Castiglia, M. Rossetti, M. Duelk, C. Velez, and N. Grandjean, "Low temperature p-type doping of (Al)GaN layers using ammonia molecular beam epitaxy for InGaN laser diodes," Applied Physics Letters **105**, (2014).

- 26. K. Kumakura, T. Makimoto, and N. Kobayashi, "Activation Energy and Electrical Activity of Mg in Mg-Doped InxGa1-xN (x<0.2)," Jpn. J. Appl. Phys. **39**, L337 (2000).

- 27. S. H. Jain, P. B. Griffin, and J. D. Plummer, "Hall measurements of bilayer structures," Journal of Applied Physics **93**, 1060–1063 (2002).

- 28. "Mobility," in *Semiconductor Material and Device Characterization* (John Wiley & Sons, Ltd, 2005), pp. 465–522.

- 29. G. Koblmüller, R. M. Chu, A. Raman, U. K. Mishra, and J. S. Speck, "High-temperature molecular beam epitaxial growth of AlGaN/GaN on GaN templates with reduced interface impurity levels," Journal of Applied Physics **107**, 043527 (2010).

- 30. Semiconductor Physics An Introduction | Karlheinz Seeger | Springer (n.d.).

- 31. B. Santic, "On the hole effective mass and the free hole statistics in wurtzite GaN," Semicond. Sci. Technol. **18**, 219 (2003).

- 32. P. Kozodoy, H. Xing, S. P. DenBaars, U. K. Mishra, A. Saxler, R. Perrin, S. Elhamri, and W. C. Mitchel, "Heavy doping effects in Mg-doped GaN," Journal of Applied Physics **87**, 1832–1835 (2000).

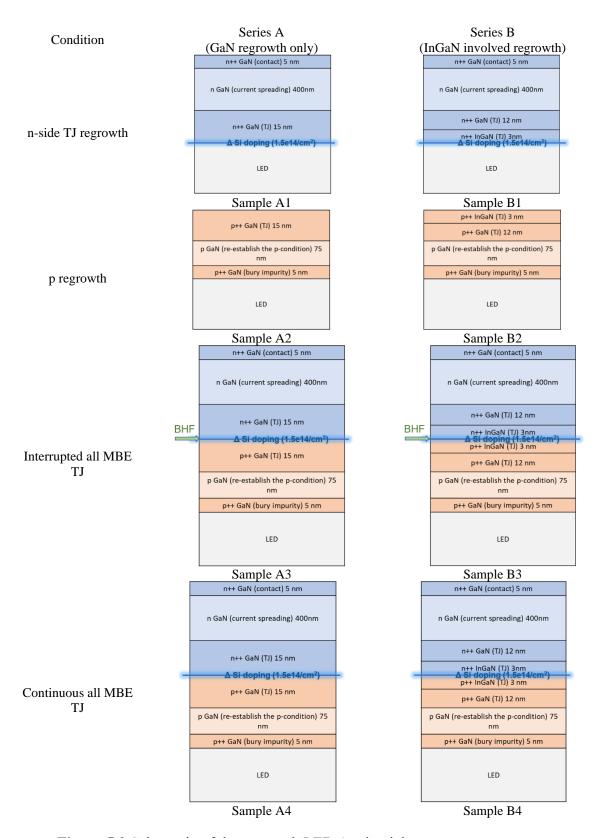

- 33. W. Götz, R. S. Kern, C. H. Chen, H. Liu, D. A. Steigerwald, and R. M. Fletcher, "Hall-effect characterization of III–V nitride semiconductors for high efficiency light emitting diodes," Materials Science and Engineering: B **59**, 211–217 (1999).