## UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

Device Physics and Material Properties of Two-Dimensional Semiconductors

Permalink https://escholarship.org/uc/item/9qz48186

Author Desai, Sujay Bharat

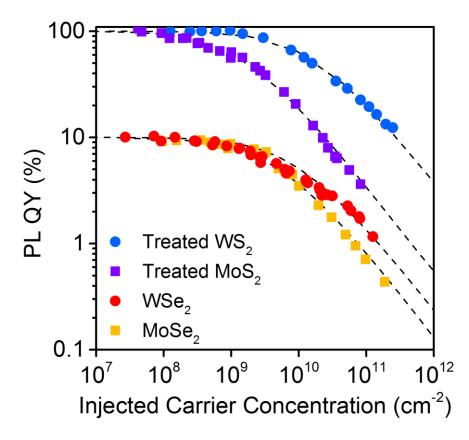

Publication Date 2018

Peer reviewed|Thesis/dissertation

Device Physics and Material Properties of Two-Dimensional Semiconductors

By

Sujay Bharat Desai

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali Javey, Chair Professor Junqiao Wu Professor Tsu-Jae King Liu Professor Jeffrey Bokor

Spring 2018

#### Copyright © 2018, by Sujay Bharat Desai

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Abstract

#### Device Physics and Material Properties of Two-Dimensional Semiconductors

by

Sujay Bharat Desai

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali Javey, Chair

Device architecture and materials innovations have enabled transistor scaling for the last several decades, boosting the performance of electronics, increasing the speed of communication and computational systems, lowering power consumption and reducing costs per operation. Twodimensional (2D) materials have gained tremendous attention in the last decade, after the discovery of graphene which has exceptional properties like high carrier mobility, ultra-thin van der Waals connected layers (~ 0.3 nm thick), high tensile strength, etc.

Transition metal dichalcogenides (TMDs) are a family of 2D materials similar to graphene, with an important difference, many of them have an electronic bandgap. Some examples like  $MoS_2$  and  $WS_2$  are also direct-band gap materials at the monolayer limit (~ 0.7 nm thick). The impressive electronic and optical properties along with their ultra-thin nature, have made them potential candidates for use in future electronics and optoelectronic applications, along with other nanomaterials like carbon nanotubes.

Device physics and the electronic and optical properties of two-dimensional semiconductors are investigated in this thesis, with emphasis on TMDs. The first chapter presents an outline of the thesis and introduces 2D materials. Chapter 2 investigates the electronic properties of TMDs with focus on applications in sub-5 nm gate length transistors for low-power applications. MoS<sub>2</sub> channel transistors with 1-nm long carbon nanotube (CNT) gate electrodes are experimentally demonstrated, showing good On/Off current ratio of ~ 10<sup>6</sup> and good subthreshold swing of ~ 65 mV/decade. The electrostatics of the transistors are investigated using simulations which demonstrate an effective channel length of ~ 1 nm in the On state and ~ 4 nm in the Off state.

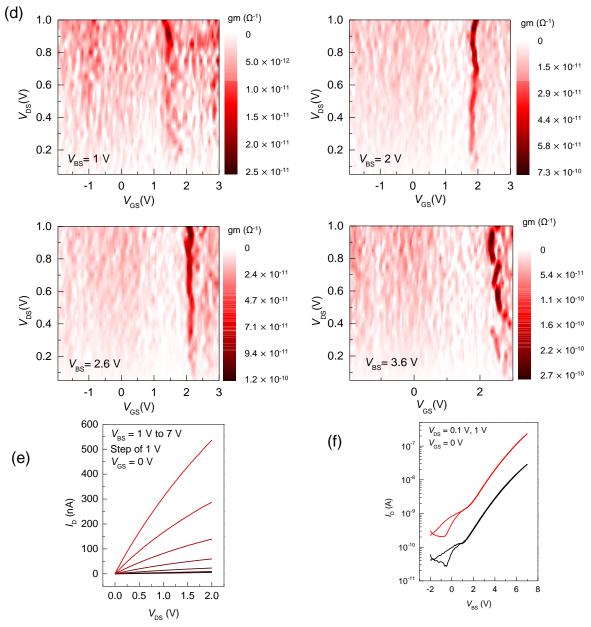

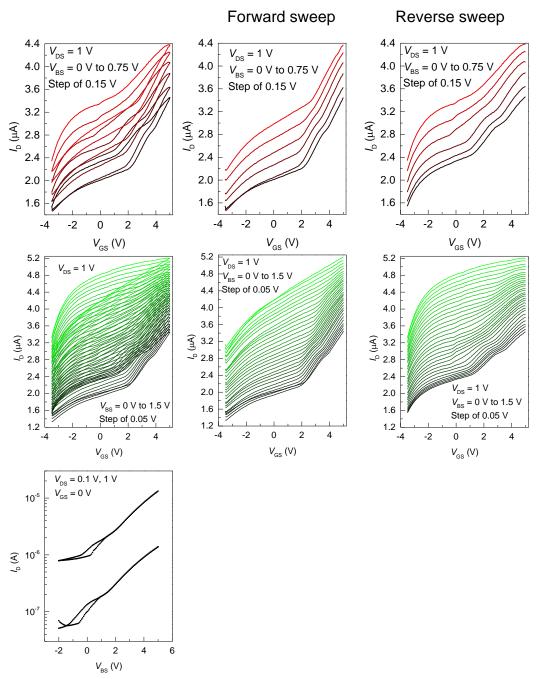

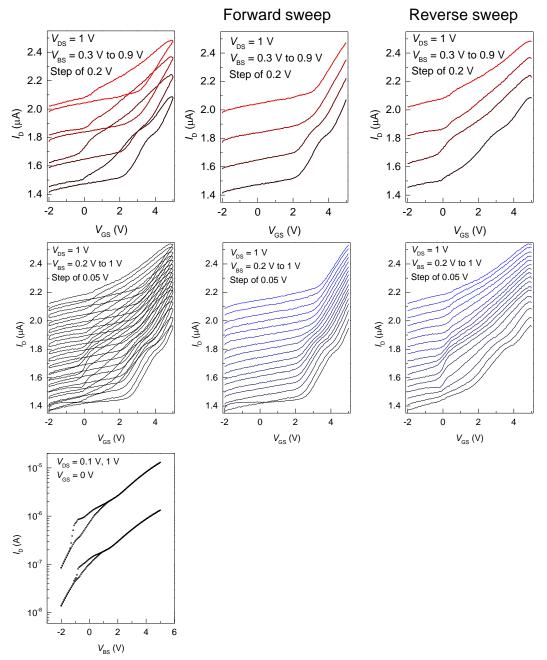

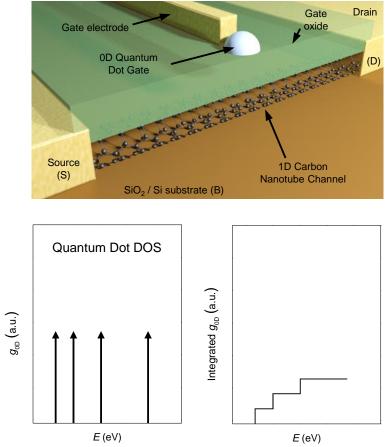

Chapter 3 considers the impact of an atomic-scale gate on the performance of nanoscale transistors, for example 2D materials like graphene and metallic TMDs like WTe<sub>2</sub>, and 1D gates like graphene nanoribbons (GNRs) and CNTs. As the size of gates approaches atomic-limits, the low electronic density of states (DOS) in the gate limits the channel charge and thus the drain current. In addition, the gate DOS can be engineered to achieve a desired shape for the transfer characteristics of a transistor. The effect of gate quantum capacitance on nanoscale transistors is experimentally demonstrated, with the observation of room-temperature quantization features in CNT gated ultra-thin silicon-on-insulator (SOI) transistors (~ 3 nm thick SOI layer), which can be correlated to the Van Hove singularities in the 1D DOS of the CNT gate.

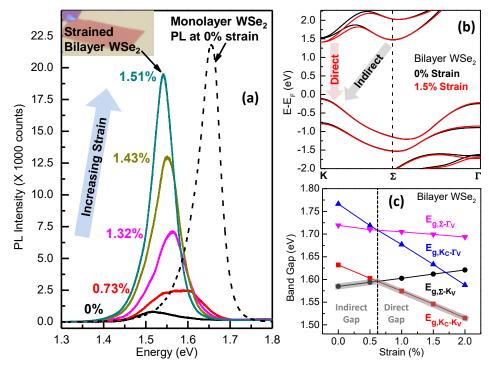

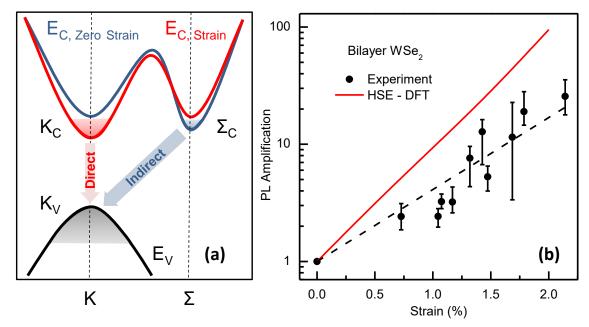

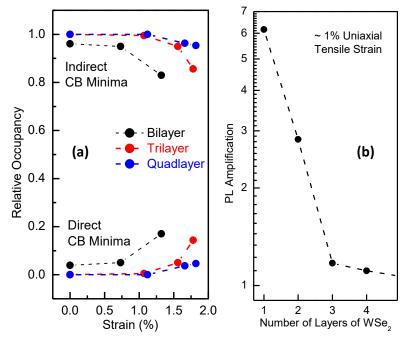

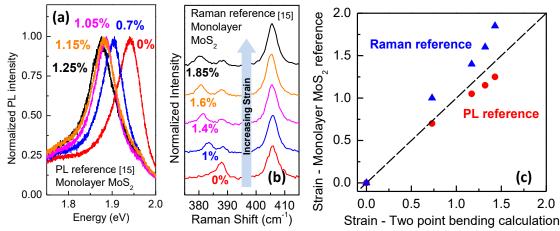

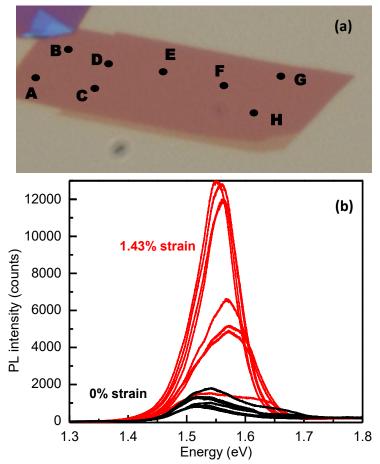

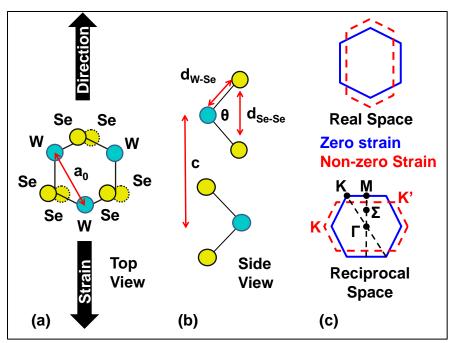

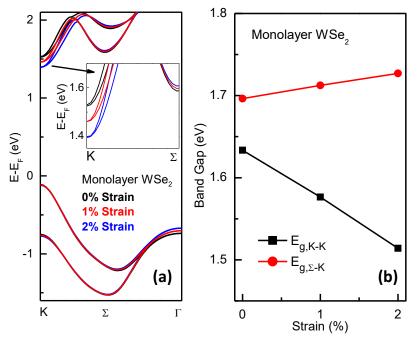

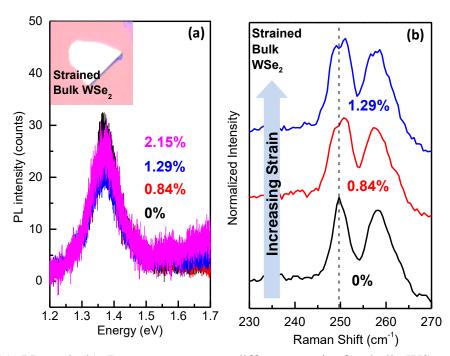

Strain engineering is an important tool used to boost mobility of carriers and enhance the performance of transistors. In chapter 4, the evolution of the electronic band structure of multilayer WSe<sub>2</sub> as a function of uniaxial tensile strain is investigated using photoluminescence and Raman spectroscopy. A strain induced indirect to direct bandgap transition is observed in multilayer WSe<sub>2</sub> with a ~ 35 x increase in photoluminescence in bilayer WSe<sub>2</sub>.

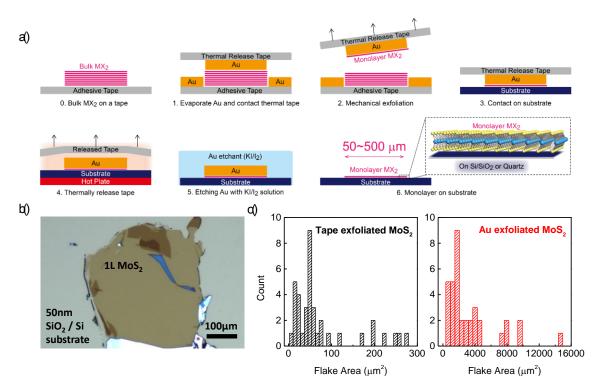

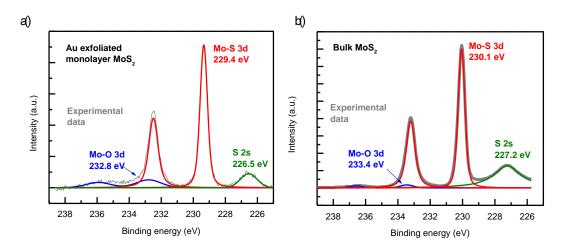

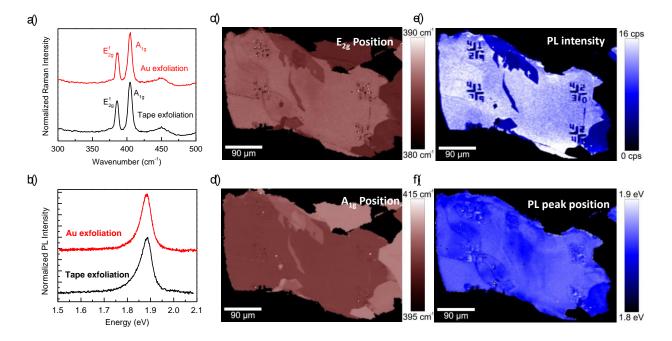

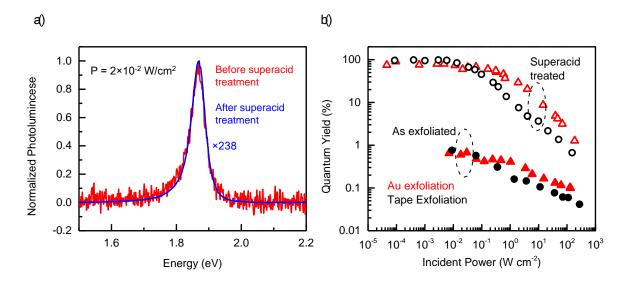

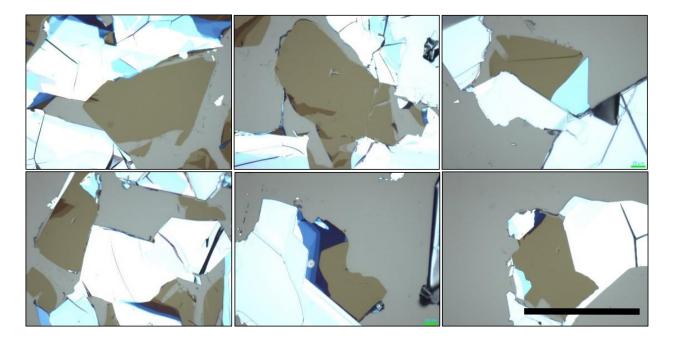

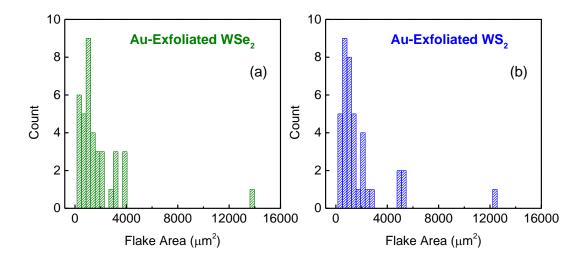

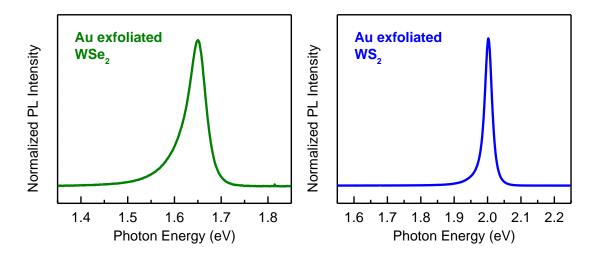

Chapter 5 focuses on a materials processing technique to selectively obtain large area monolayer 2D materials preferentially, with high yield. A gold mediated exfoliation technique is developed to selectively transfer monolayer 2D materials onto arbitrary substrates. A gold layer deposited on top of a 2D material crystal induces strain in the top-most monolayer, resulting in a reduction of the van der Waals coupling strength of the top-most monolayer with the bulk crystal. This enables the selective peeling of the top most monolayer with high predictability and large size. The monolayers obtained, for the specific examples of TMDs were characterized using electrical device, AFM and XPS measurements, and photoluminescence and Raman spectroscopy.

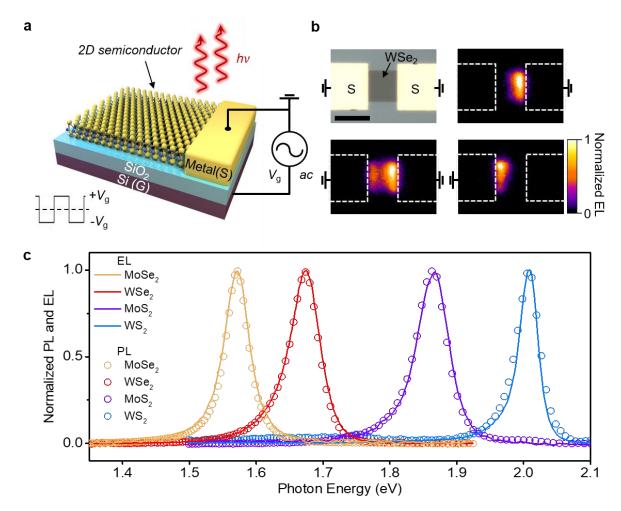

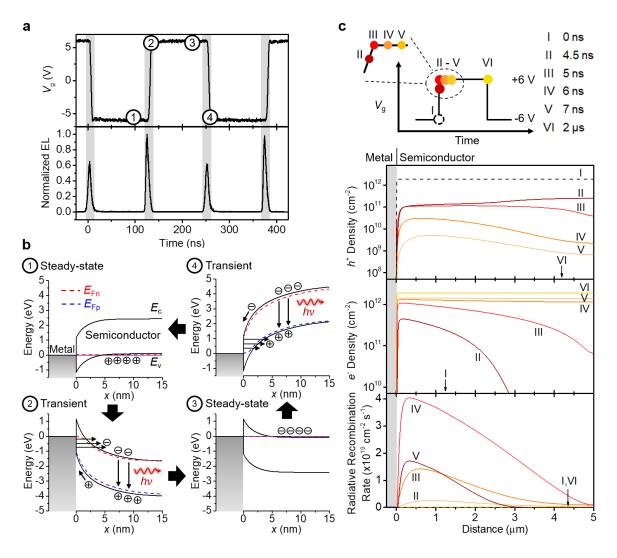

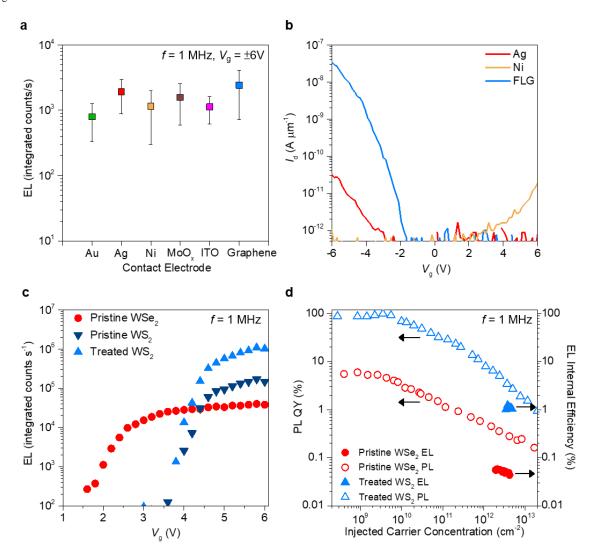

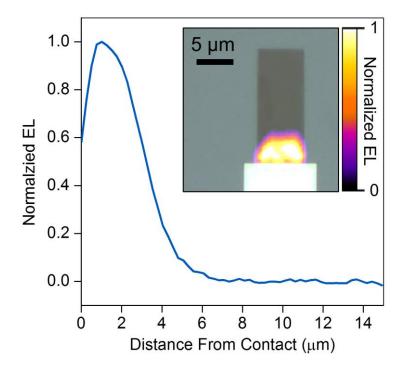

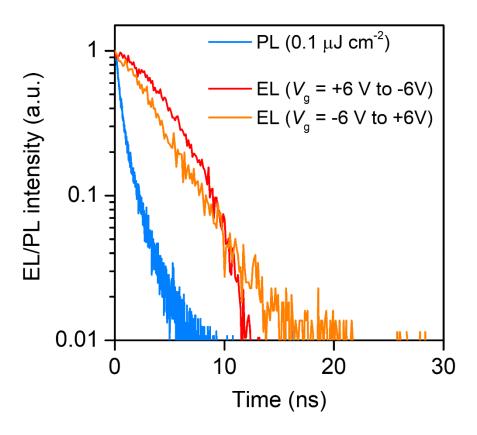

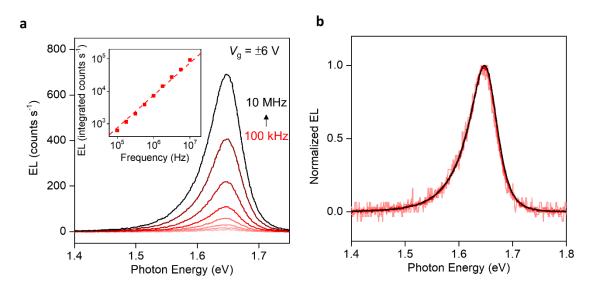

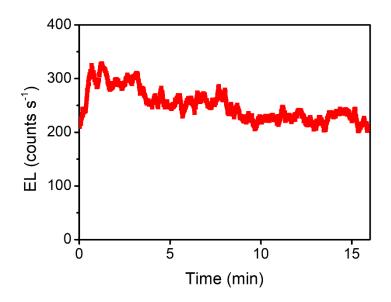

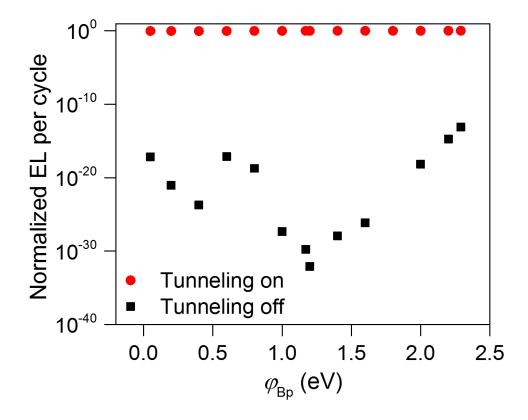

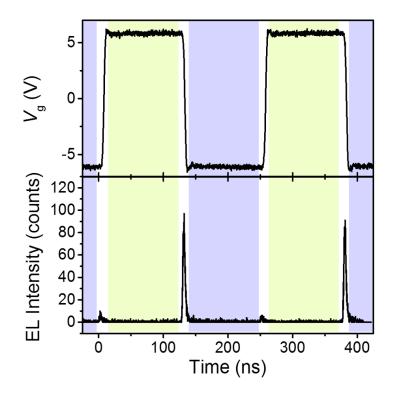

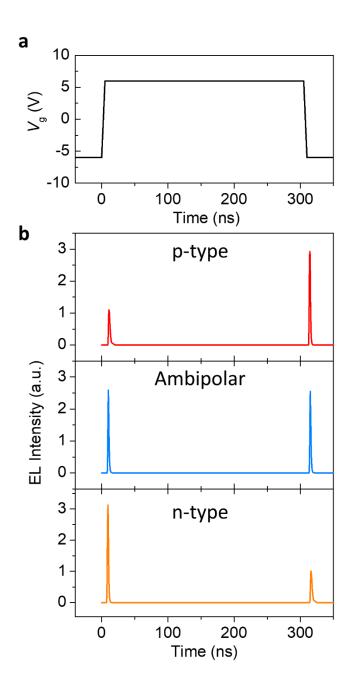

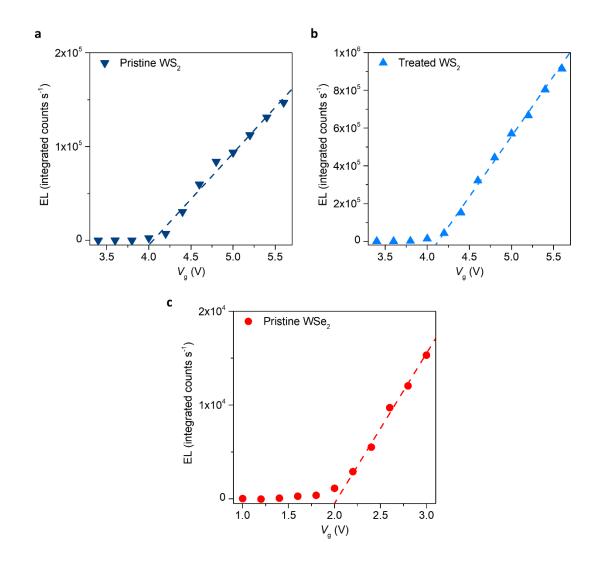

The next two chapters discuss the device physics and analysis of 2D materials based devices in the context of large-area and bright light emitting monolayer devices, and lateral 2D heterostructures, using simulations and analytical modeling. A new scheme for operating light emitting devices is discussed in chapter 6. Monolayer TMD devices on insulating substrates are operated with pulsed gate voltages resulting in transient electroluminescence. The emission mechanism, generation of bipolar carrier concentration and calculation of device efficiency are discussed in detail. The light output is independent of contact barrier height and the pulsed gating technique may be useful especially for materials which are difficult to dope p, and n type, for example wide bandgap semiconductors. Finally, the monolayers absorb only ~ 10% of visible light and can be used for large area transparent displays.

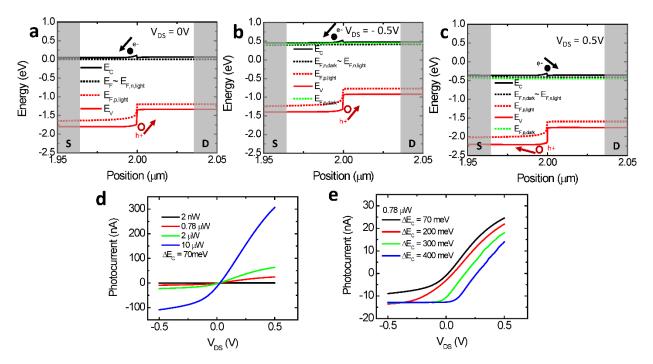

Chapter 7 discusses the device physics of lateral 2D heterostructures considering the specific case of monolayer-few layer MoS<sub>2</sub>. Using device simulations, with Kelvin Force Probe microscopy and photocurrent measurements, it is shown that a type-I heterostructure exists at the interface. Lateral 2D heterostructures by thickness modulation offer a unique way to obtain atomically sharp heterostructures with potential applications in optoelectronic devices like photodetectors. Chapter 8 presents the main conclusions of the thesis, and presents an outlook into the future of two-dimensional semiconductors.

To my parents, my sister, my friends and my mentors

# Table of Contents

| Chapter 1: Introduction                                         | 1 |

|-----------------------------------------------------------------|---|

| 1.1 Transistor scaling and materials innovation                 | 1 |

| 1.2 2D materials at the scaling limit of physical gate length   | 3 |

| 1.3 Effect of gate quantum capacitance in nanoscale transistors | 5 |

| 1.4 Strain Engineering of 2D materials                          | 5 |

| 1.5 Large-area monolayer exfoliation of 2D materials            | 7 |

| 1.6 Simulation and modeling of 2D materials based devices       | 7 |

| Chapter 2: MoS <sub>2</sub> Transistors with 1-Nanometer Gate Lengths | 9 |

|-----------------------------------------------------------------------|---|

| 2.1 Direct source-to-drain tunneling and short channel effects        | 9 |

| 2.2 Device structure and electrical characterization                  |   |

| 2.3 Simulation results and electrostatics                             |   |

| 2.4 Channel thickness dependence                                      |   |

| 2.5 Supporting Information                                            |   |

| Chapter 3: Gate Quantum Capacitance Effects in Nanoscale Transistors  |    |

|-----------------------------------------------------------------------|----|

| 3.1 Introduction                                                      |    |

| 3.2 Analytical electrostatics model                                   |    |

| 3.3 Carbon nanotube gated ultra-thin silicon-on-insulator transistors | 35 |

| 3.4 Conclusion                                                        | 38 |

| 3.5 Methods                                                           | 38 |

| 3.6 Supporting Information                                            | 41 |

| Chapter 4: Strain Induced Indirect to Direct Bandgap Transition in Few-Layer WSe2 | . 52 |

|-----------------------------------------------------------------------------------|------|

| 4.1 Introduction                                                                  | . 52 |

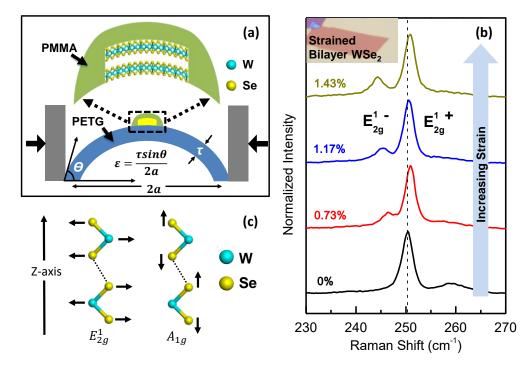

| 4.2 Uniaxial tensile strain in bilayer WSe <sub>2</sub>                           | . 53 |

| 4.3 Raman spectroscopy and photoluminescence enhancement                          | . 54 |

| 4.4 Density functional theory calculations                                        | . 55 |

| 4.5 Photoluminescence amplification factor model                                  | . 56 |

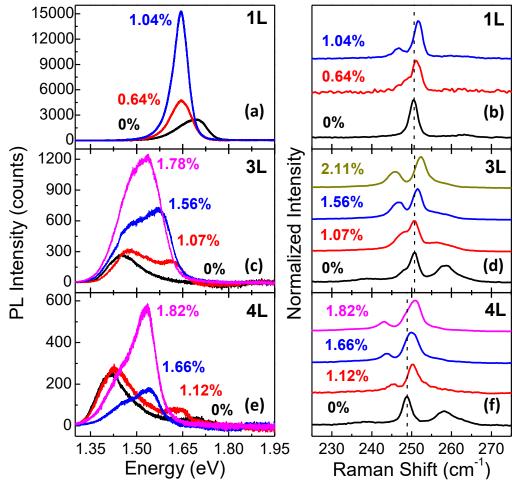

| 4.6 Mono, tri and quad layer WSe2 strain                                          | . 58 |

| 4.7 Supporting information                                                        | . 60 |

| Chapter 5: Gold Mediated Exfoliation of Ultra Large Optoelectronically Perfect |    |

|--------------------------------------------------------------------------------|----|

| Monolayers                                                                     | 69 |

| 5.1 Introduction                                                               | 69 |

| 5.2 Gold-mediated exfoliation technique                                        | 69 |

| 5.3 XPS characterization of gold-exfoliated MoS <sub>2</sub>                   | 71 |

| 5.4 Optical characterization of gold-exfoliated MoS2                           | 72 |

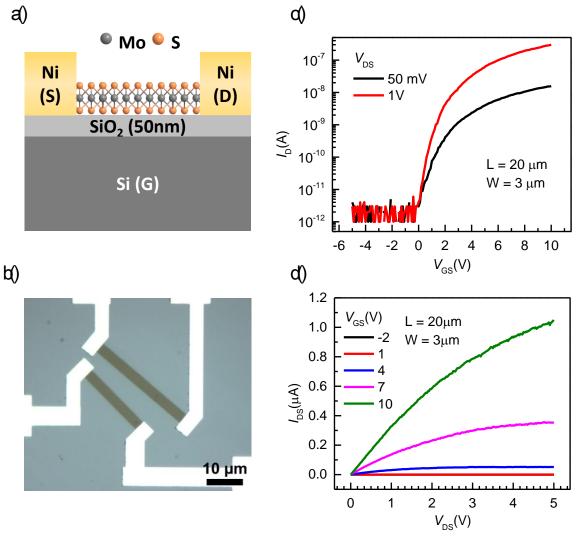

| 5.5 Electrical characterization of gold-exfoliated MoS2                        | 73 |

| 5.6 Experimental Section                                                       | 75 |

| 5.7 Supporting Information                                                     | 77 |

## Chapter 6: Large-area and bright pulsed electroluminescence in monolayer

| semiconductors                                          |     |

|---------------------------------------------------------|-----|

| 6.1 Introduction                                        |     |

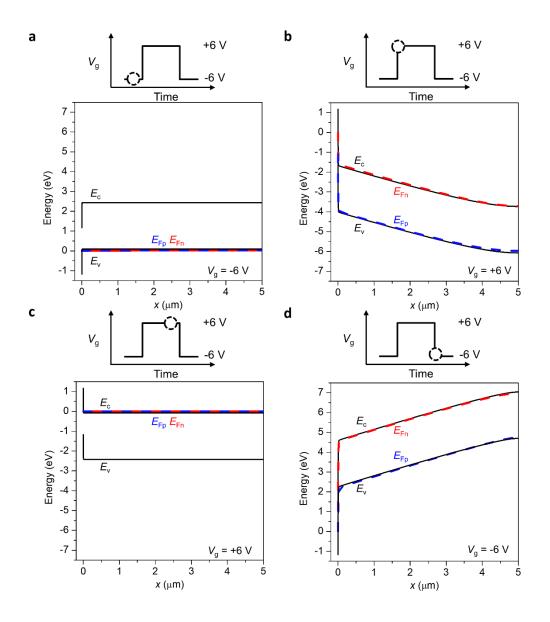

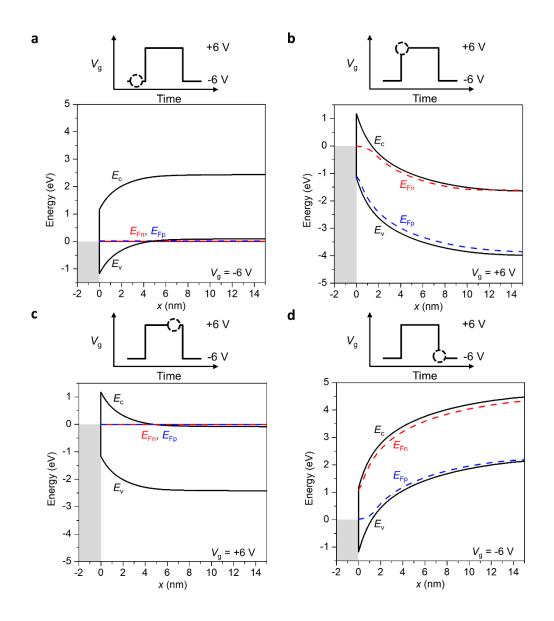

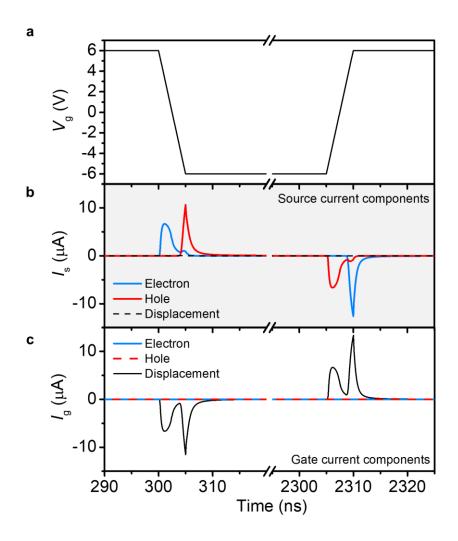

| 6.2 Operation and device structure of the t-EL device   | 83  |

| 6.3 Carrier injection and light emission mechanism.     |     |

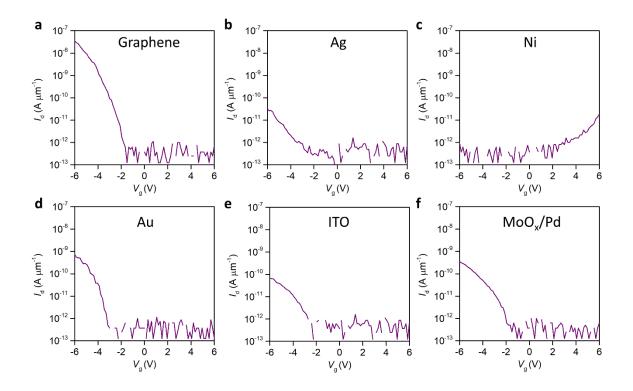

| 6.4 Schottky barrier height and gate-voltage dependence | 85  |

| 6.5 Device Simulations                                  | 88  |

| 6.6 Supplementary Figures                               | 89  |

| 6.7 Supplementary Notes                                 | 106 |

| Chapter 7: MoS <sub>2</sub> Heterojunctions by Thickness Modulation<br>7.1 Introduction |     |

|-----------------------------------------------------------------------------------------|-----|

| 7.1 Introduction                                                                        | 111 |

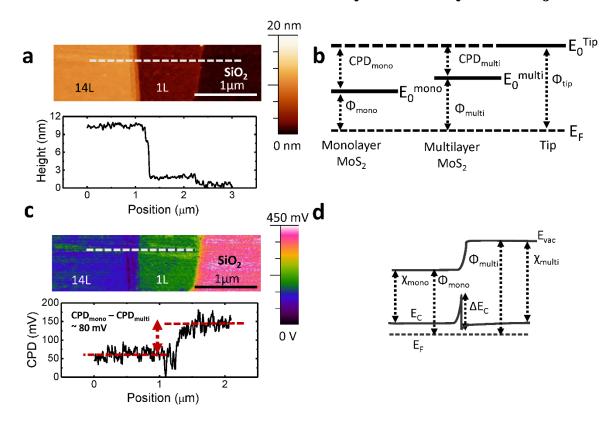

| 7.2 Band offset extraction at the monolayer-multilayer MoS <sub>2</sub> junction        |     |

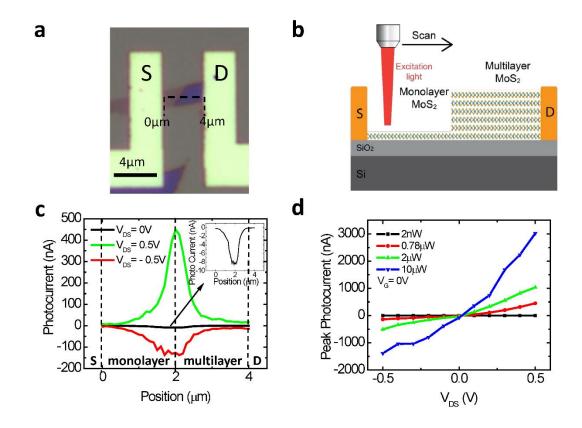

| 7.3 Photoresponse at the monolayer-multilayer MoS <sub>2</sub> junction                 | 113 |

| 7.4 Device Modeling                                                                     | 115 |

| 7.5 Conclusion                                                                          | 117 |

|                                                                                         |     |

| Chapter 8: Conclusion and outlook12 | !1 |

|-------------------------------------|----|

|-------------------------------------|----|

# **Acknowledgements**

I wish to thank Prof. Javey, for his advice, support, guidance and vision, and for giving me a position in his lab. He was instrumental in shaping my approach to tackling tough problems. I thank him for many of the skills I developed during my PhD, like project management, finding new research directions and critical thinking. His questions pushed me to think deep and come up with the best, robust, yet simplistic explanations for everything. I will always be grateful to him, for giving me this chance to do my PhD at UC Berkeley.

I wish to thank Prof. Tsu-Jae King Liu, Prof. Junqiao Wu and Prof. Jeffrey Bokor for being on my dissertation and qualifying exam committees. Thank you to Prof. King for your encouragement and inspiration throughout my PhD. I want to thank Prof. Joel Ager, Prof. Philip Wong of Stanford, Prof. Jing Guo of University of Florida, Prof. Chenming Hu, Prof. Ming Wu, Prof. Daryl Chrzan and Prof. Moon Kim of UT Dallas for their collaboration and their guidance.

I want to thank my mentors Prof. Hui Fang, and Prof. Rehan Kapadia who taught me everything about semiconductor fabrication in my first year. Hui's attitude of paying attention to details, performing and planning experiments methodically, seeped into me, defining the way I did research during the rest of my PhD. Rehan's unlimited enthusiasm and energy for research and his hard-working attitude were infectious. I thank him for teaching me a lot of things during my first year. I consider myself extremely lucky to have them as my mentors.

I would not have achieved anything without my esteemed peers and lab members. I cannot count the number of interactions I have had with Dr. Angada Sachid, Surabhi Madhvapathy, Dr. Mahmut Tosun, Dr. Hossain Fahad, Dr. Kevin Chen, Mark Hettick, Prof. Daisuke Kiriya and Dr. Steven Chuang. Thank you for training me and your collaboration, and for the extremely productive brainstorming sessions and for all your help with experiments. Thank you to Surabhi, Angada and Mahmut, you were great project partners and a joy to work with. Surabhi, you defied the meaning of an undergraduate student and were like a seasoned researcher. Thank you for all your help and time during my PhD, with the innumerable experiments throughout your time here.

Also thanks to Juan-Pablo Llinas (JP) for all your help especially during crunch time and Gregory Pitner for helping me with carbon nanotube growth. Thank you to the graduate students in Javey lab, Chunsong Zhao, George Zhang and Hyungjin Kim, it was fun to work with you. Thanks to my mentees, Theodor Lundberg and Tsegereda Esatu, I know you both will do awesome. I would also like to thank the Berkeley Nanolab and the staff. I wish to thank all my friends for their continuous support and encouragement, allowing me to traverse through the ups and downs of PhD. I could not have made it without you all.

Lastly, I wish to thank my parents and my sister, for all their sacrifices, encouragement, love, unwavering support and trust in my abilities and my choices. Thank you for letting me pursue my dreams and making them your own. There are no words which can justify your contribution to my PhD. This thesis is dedicated to you.

# 1

# Introduction

## 1.1 Transistor scaling and materials innovation

Moore's law and transistor scaling have been the backbone of the semiconductor industry for the last several decades. Transistor sizes have been continuously scaled down, enabling us to pack more of them per unit area of a silicon die. It has led to a boost in performance of electronics, increased communication speeds, and enabled devices which are more energy efficient and also cheaper per unit operation. It has enabled many technological advancements we see today, like supercomputers, data-centers, cloud-storage and smartphones (figure 1). Throughout this time period, the transistor architecture has steadily changed and the number of materials and elements used to create an integrated circuit have steadily increased. Strain engineering of silicon to enhance electron and hole mobility in transistors and the replacement of SiO<sub>2</sub> gate oxide with high-k dielectrics along with the transition to 3D FinFET transistors were the monumental changes in the last two decades.

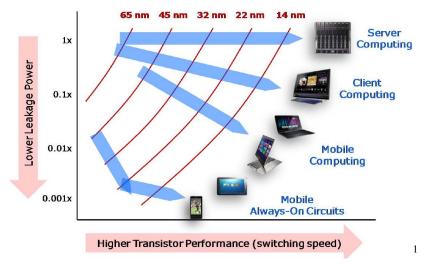

Figure 1: Electronics applications as a function of power consumption versus performance

As transistor scaling continues, it is becoming increasingly difficult to scale the transistors without impacting performance. Short channel effects, and direct source-to-drain tunneling in the sub-5 nm gate length regime, along processing related challenges remain the main roadblocks for Moore's law to continue. As part of the search for possible solutions to continue improving the performance of electronics and optoelectronics devices, two-dimensional (2D) materials have gained tremendous attention in the last decade, primarily after the discovery of graphene which

<sup>&</sup>lt;sup>1</sup> M. Bohr, Intel Development Forum 2014

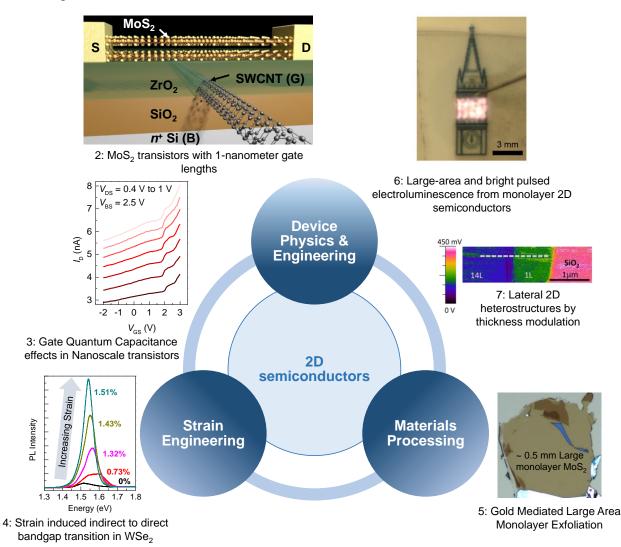

has exceptional properties like high carrier mobility, ultra-thin van der Waals connected layers (~0.3 nm thick), high tensile strength, etc. Transition metal dichalcogenides (TMDs) are a family of 2D materials similar to graphene. They are layered and many of them have a large bandgap. Some examples like MoS<sub>2</sub> and WS<sub>2</sub> are also direct-band gap materials at the monolayer limit (~0.7 nm thick). The impressive electronic and optical properties along with their ultra-thin nature, have made them potential candidates for use in future electronics and optoelectronic applications, similar to other nanomaterials like carbon nanotubes. This thesis investigates the device physics and the electronic and optical properties of two-dimensional semiconductors, with emphasis on TMDs (figure 2).

Figure 2: Thesis outline, highlighting the main projects and results, with emphasis on device physics and materials properties of 2D semiconductors. Numbering refers to the chapter numbers.

## 1.2 2D materials at the scaling limit of physical gate length

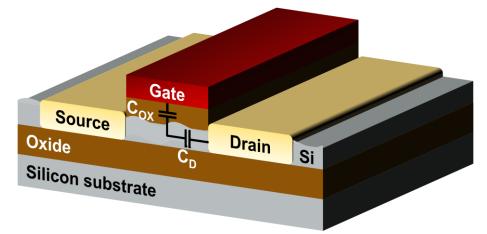

As transistors are scaled down, device architectures deviating from the bulk-planar MOSFET, for example FinFETs and ultra-thin body transistors perform better because of the better electrostatic control of the gate over the channel charge. However, when all the components of a transistor including the channel thickness are scaled down, surface roughness becomes an increasingly important factor, especially for 3D materials like Si. It is not possible to achieve atomically smooth silicon at thicknesses on the atomic scale, which is required for the ultimate scaled transistors. The surface roughness in channel would translate to variations in material properties along the channel, for example bandgap and mobility, and the presence of dangling bonds would degrade the performance of the device (figure 3).

Figure 3: Schematic of an ultra-thin channel transistor, emphasizing important factors to consider with device scaling, for example, coupling of channel with drain and surface roughness of channel

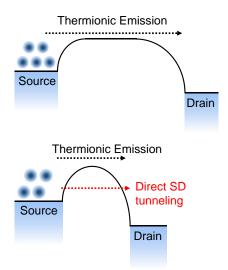

The dielectric constant of the channel is also an important factor in determining the level of short channel effects in a transistor. A low in-plane dielectric constant would help reduce the capacitive coupling to the drain and thus yield a lower characteristic length which would help scale the physical gate length. At the same time, a higher dielectric constant out-of-plane would help increase the capacitive coupling to the gate and aid in reducing the short channel effects further. In the sub-5 nm gate length regime, direct source to drain tunneling is predicted especially for low effective mass materials like Si (figure 4). A large band gap, low in-plane dielectric constant and larger carrier effective mass are all important in mitigating direct source to drain tunneling.

**Figure 4**: Schematic representation of current components at different gate lengths. At short gate lengths, direct source to drain tunneling which is undesirable becomes significant

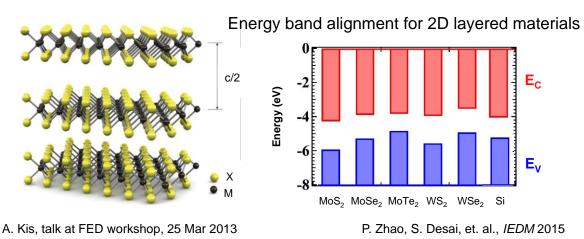

Figure 5: Schematic of TMD crystal structure and energy band alignment for some 2D layered materials relative to silicon

Relative to silicon, TMDs have uniform atomic scale thickness (example  $MoS_2$  monolayer is ~ 0.7 nm thick), higher effective mass of carriers (0.55 m<sub>0</sub> for  $MoS_2$  compared to 0.19 m<sub>0</sub> for silicon), larger bandgaps ( $MoS_2$  monolayer ~ 1.85 eV,  $MoS_2$  bilayer ~ 1.5 eV) and lower in-plane dielectric constants (~ 4 for  $MoS_2$ ) (figure 5). These electronic and material properties make these materials very interesting for applications in transistors at the scaling limits of gate length.

Chapter 2 investigates the electronic properties of TMDs with focus on applications in sub-5 nm gate length transistors for low-power applications. MoS<sub>2</sub> channel transistors with 1-nm long carbon nanotube (CNT) gate electrodes are experimentally demonstrated, showing good On/Off current ratio of ~  $10^6$  and good subthreshold swing of ~ 65 mV/decade. The electrostatics of the transistors are investigated using simulations which demonstrate an effective channel length of ~ 1 nm in the On state and ~ 4 nm in the Off state.

## 1.3 Effect of gate quantum capacitance in nanoscale transistors

Chapter 3 considers the impact of an atomic-scale gate on the performance of nanoscale transistors, for example 2D materials like graphene and metallic TMDs like WTe<sub>2</sub>, and 1D gates like graphene nanoribbons (GNRs) and CNTs. As the size of gates approaches atomic-limits, the low electronic density of states (DOS) in the gate limits the channel charge and thus the drain current. In addition, the gate DOS can be engineered to achieve a desired shape for the transfer characteristics of a transistor. The effect of gate quantum capacitance on nanoscale transistors is experimentally demonstrated for the first time, with the observation of room-temperature quantization features in CNT gated ultra-thin silicon-on-insulator (SOI) transistors (~ 3 nm thick SOI layer), which can be correlated to the Van Hove singularities in the 1D DOS of the CNT gate.

### **1.4 Strain Engineering of 2D materials**

Nayak, D. K.; Appl. Phys. Lett. 1994, 64 (19)

Cheng, T.-H.; Appl. Phys. Lett. 2010, 96 (211108)

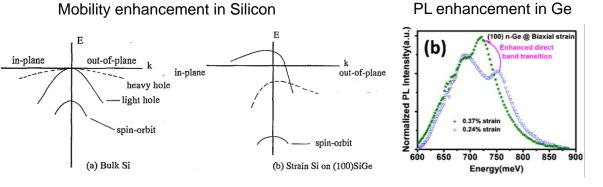

Figure 6: Applications of strain engineering in materials: Enhancement of carrier mobility in silicon and photoluminescence enhancement in germanium

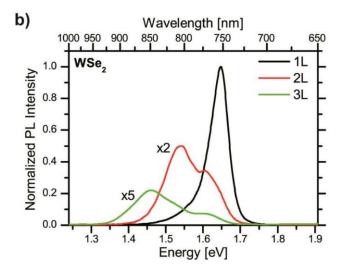

Strain engineering is an important tool used to boost mobility of carriers and enhance the performance of transistors (figure 6). TMDs like MoS<sub>2</sub>, WSe<sub>2</sub> and WS<sub>2</sub> are direct bandgap materials at the monolayer limit. However, thicker layers of these materials, from bilayer to bulk are indirect bandgap in nature (figure 7). For applications like solar cells and photodetectors, thicker direct bandgap materials are preferred, so that maximum amount of light can be absorbed in the material.

**Figure 7**: Photoluminescence of WSe<sub>2</sub> as a function of layer thickness (Tonndorf, P; R. Opt. Expr. 2013, 21 (4), 4908–4916)

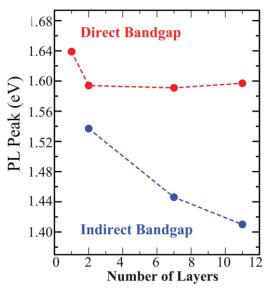

In chapter 4, the evolution of the electronic band structure of multilayer WSe<sub>2</sub> as a function of uniaxial tensile strain is investigated using photoluminescence and Raman spectroscopy. A strain induced indirect to direct bandgap transition is observed in multilayer WSe<sub>2</sub> with a ~ 35 x increase in photoluminescence in bilayer WSe<sub>2</sub>. The motivation to study the impact of strain on multilayer WSe<sub>2</sub> was the relatively small difference between the indirect and direct band gap energies in multilayer WSe<sub>2</sub>, relative to other TMDs like MoS<sub>2</sub>. For example, the difference between the indirect and direct bandgap is ~ 300 meV for bilayer MoS<sub>2</sub>, as compared to only 40 meV for bilayer WSe<sub>2</sub> (figure 8).

**Figure 8:** Evolution of the direct and indirect bandgap energies in WSe<sub>2</sub> as a function of layer thickness (Sahin, H.; Phys. Rev. B: Condens. Matter Mater. Phys. 2013, 87 (16), 165409)

## 1.5 Large-area monolayer exfoliation of 2D materials

Top down: Tape exfoliation method

DOI: <u>10.1039/C5TA00252D</u> (Review Article) <u>J.</u> <u>Mater. Chem. A</u>, 2015, **3**, 11700-11715

#### Bottom Up: Chemical Vapor Deposition

Nature 520, 656-660, (30 April 2015)

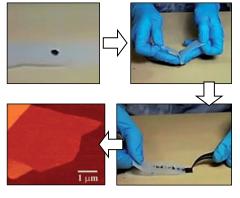

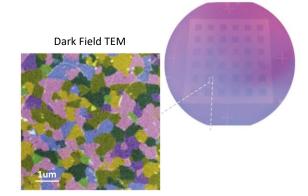

Figure 9: Common ways to obtain monolayer TMDs, mechanical exfoliation and chemical vapor deposition

Scotch tape exfoliation from bulk crystals, a technique used first to obtain monolayer graphene is one of the easiest techniques to obtain monolayer TMDs. However, the samples obtained using the mechanical tape exfoliation method, are of random thickness, monolayers and few layers are obtained with very low yield and the size of the obtained flakes is typically very small ~ 5  $\mu$ m. Another way to obtain monolayer TMDs is by bottom up synthesis using techniques like chemical vapor deposition. However the quality of grown materials is dependent on growth conditions, which determines grain sizes, defect density, strain, stoichiometry, etc.

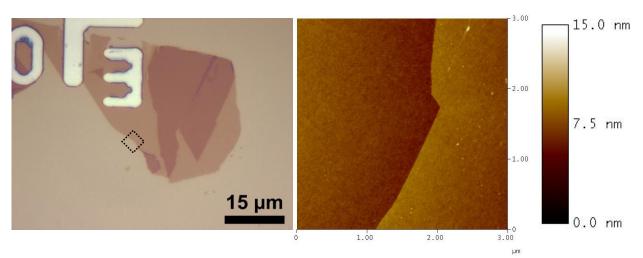

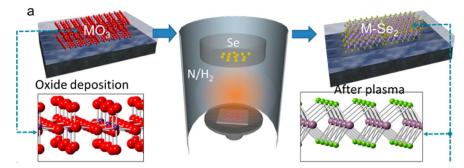

Chapter 5 focuses on a materials processing technique to selectively obtain large area monolayer 2D materials preferentially, with high yield. A gold mediated exfoliation technique is developed to selectively transfer monolayer 2D materials onto arbitrary substrates. A gold layer deposited on top of a 2D material crystal induces strain in the top-most layer, resulting in a reduction of the van der Waals coupling strength of the top-most layer with the bulk crystal. This enables the selective peeling of the top most layer with high predictability and large size. The monolayers obtained, for the specific examples of TMDs were characterized using electrical device, photoluminescence, Raman, AFM and XPS measurements.

## 1.6 Simulation and modeling of 2D materials based devices

Chapters 6 and 7 discuss the device physics and simulation based analysis of 2D materials based devices in the context of large-area and bright light emitting monolayer devices, and lateral 2D heterostructures.

Light emitting diodes consist of pn junctions formed by doping a semiconductor p and n type. This is difficult for 2D materials because of their ultra-thin nature. Substitutional doping would damage the 2D layer and other forms of doping like charge-transfer doping negatively

impact the optical properties and light emission efficiency of 2D materials. To circumvent this problem, a new scheme for operating monolayer semiconductor based light emitting devices is discussed in chapter 6. Monolayer TMD devices on insulating substrates are operated with pulsed gate voltages resulting in transient electroluminescence. The emission mechanism, generation of bipolar carrier concentration and calculation of device efficiency are discussed in detail. The light output is independent of contact barrier height and the pulsed gating technique may be useful especially for materials which are difficult to dope p, and n type, for example wide bandgap semiconductors. Finally, the monolayers absorb only ~ 10% of visible light and can be used for large area transparent displays.

Semiconductor heterostructures are widely used in LEDs, lasers and other optoelectronic devices. III-V materials are amongst the most widely used materials for this application because of the relative ease of forming heterostructures of different type and barrier height. However lattice mismatch in 3D heterostructures made from III-V materials can lead to defects and dislocations which degrade performance of the device. At the same time, it is difficult to define atomically sharp heterostructures using III-V materials since the boundary is generally graded due to inter-diffusion of atoms during growth. Chapter 7 discusses the device physics of lateral 2D heterostructures by means of thickness modulation, considering the specific case of monolayer-few layer MoS<sub>2</sub>. Using device simulations, with Kelvin Force Probe microscopy and photocurrent measurements, it is shown that a type-I heterostructure exists at the interface.

# <sup>2</sup>MoS<sub>2</sub> Transistors with 1-Nanometer Gate Lengths

## 2.1 Direct source-to-drain tunneling and short channel effects

As Si transistors rapidly approach their projected scaling limit of ~ 5 nm gate lengths, exploration of new channel materials and device architectures is of utmost interest (1-3). This scaling limit arises from short channel effects (4). Direct source-to-drain tunneling and the loss of gate electrostatic control on the channel severely degrade the OFF-state leakage currents, thus limiting the scaling of Si transistors (5, 6). Certain semiconductor properties dictate the magnitude of these effects for a given gate length. Heavier carrier effective mass, larger band gap and lower in-plane dielectric constant yield lower direct source-to-drain tunneling current (7). Uniform and atomically thin semiconductors with low in-plane dielectric constants are desirable for enhanced electrostatic control of the gate. Thus, investigation and introduction of semiconductors that have more ideal properties than Si could lead to further scaling of transistor dimensions with lower OFF-state dissipation power.

Transition metal dichalcogenides (TMDs) are layered 2-dimensional (2D) semiconductors that have been widely explored as a potential channel material replacement for Si (8-11), and each material exhibits different band structure and properties (12-16). The layered nature of TMDs allows uniform thickness control with atomic level precision down to the monolayer limit. This thickness scaling feature of TMDs is highly desirable for well-controlled electrostatics in ultrashort transistors (3). For example, monolayer and few-layer MoS<sub>2</sub> have been shown theoretically to be superior to Si at the sub-5 nm scaling limit (17, 18).

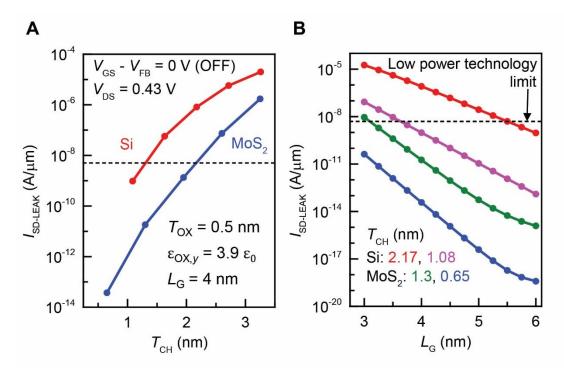

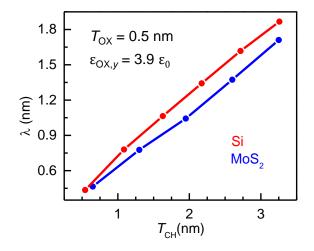

The scaling characteristics of MoS<sub>2</sub> and Si transistors as a function of channel thickness and gate length are summarized in Fig. 1. We calculated direct source-to-drain tunneling currents (*I*<sub>SD-LEAK</sub>) in the OFF-state for different channel lengths and thicknesses using a dual-gate device structure (Fig. S1) as a means to compare the two materials. MoS<sub>2</sub> shows more than two orders of magnitude reduction in *I*<sub>SD-LEAK</sub> relative to Si mainly because of its larger electron effective mass along the transport direction ( $m_n^* \sim 0.55m_0$  for MoS<sub>2</sub> versus  $m_n^* \sim 0.19m_0$  for Si [100]) (*19*), with a trade-off resulting in lower ballistic ON-current. Notably, *I*<sub>SD-LEAK</sub> does not limit the scaling of monolayer MoS<sub>2</sub> even down to the ~ 1 nm gate length, presenting a major advantage over Si [more details about calculations in supplementary materials (*20*)]. Finally, few-layer MoS<sub>2</sub> exhibits a lower in-plane dielectric constant (~ 4) compared to bulk Si (~ 11.7), Ge (~ 16.2) and GaAs (~ 12.9), resulting in a shorter electrostatic characteristic length ( $\lambda$ ) as depicted in Fig. S2 (*21*).

The above qualities collectively make MoS<sub>2</sub> a strong candidate for the channel material of future transistors at the sub-5 nm scaling limit. However, to date, TMD transistors at such small

<sup>&</sup>lt;sup>2</sup> Reprinted with permission from Sujay B. Desai, et. al., *Science*, 354, 99-102, 2016, Copyright 2016 American Association for the Advancement of Science

gate lengths have not been experimentally explored. Here, we demonstrate 1D gated 2D semiconductor field-effect transistors (1D2D-FET) with a single-walled carbon nanotube (SWCNT) gate, a MoS<sub>2</sub> channel and physical gate lengths of ~ 1 nm. The 1D2D-FETs exhibit near ideal switching characteristics, including a subthreshold swing (SS) of ~ 65 mV/decade at room temperature and high ON/OFF current ratios. The SWCNT diameter  $d \sim 1$  nm for the gate electrode (22) minimized parasitic gate to source-drain capacitance, which is characteristic of lithographically patterned tall gate structures. The ~ 1 nm gate length of the SWCNT also allowed for the experimental exploration of the device physics and properties of MoS<sub>2</sub> transistors as a function of semiconductor thickness (i.e., number of layers) at the ultimate gate length scaling limit.

**Figure 1: Direct source-to-drain leakage current**. (A) Normalized direct source-to-drain leakage current ( $I_{SD-LEAK}$ ), calculated using the WKB approximation as a function of channel thickness  $T_{CH}$  for Si and MoS<sub>2</sub> in the OFF-state.  $V_{DS} = V_{DD} = 0.43$  V from international technology roadmap for semiconductors (ITRS) 2026 technology node. (B)  $I_{SD-LEAK}$  as a function of gate length  $L_G$  for different thicknesses of Si and MoS<sub>2</sub> for the same OFF-state conditions as figure 1A. The dotted line in figures 1A and 1B represents the Low Operating Power (LOP) limit for the 2026 technology node as specified by the ITRS.

## 2.2 Device structure and electrical characterization

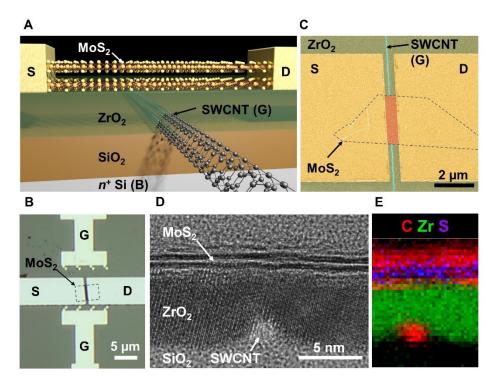

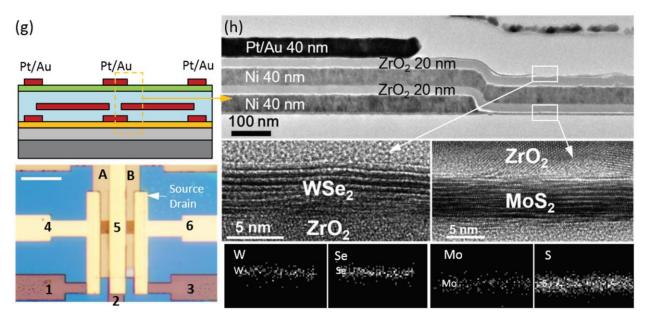

**Figure 2: 1D2D-FET device structure and characterization**. (**A**) Schematic of 1D2D-FET with a MoS<sub>2</sub> channel and SWCNT gate. (**B**) Optical image of a representative device shows the MoS<sub>2</sub> flake, gate (G), source (S) and drain (D) electrodes. (**C**) False-colored scanning electron microscope (SEM) image of the device showing the SWCNT (blue), ZrO<sub>2</sub> gate dielectric (green), MoS<sub>2</sub> channel (orange) and the Ni source and drain electrodes (yellow). (**D**) Cross-sectional TEM image of a representative sample showing the SWCNT gate, ZrO<sub>2</sub> gate dielectric and bilayer MoS<sub>2</sub> channel. (**E**) EELS map showing spatial distribution of carbon, zirconium and sulfur in the device region, conforming the location of the SWCNT, MoS<sub>2</sub> flake and the ZrO<sub>2</sub> dielectric.

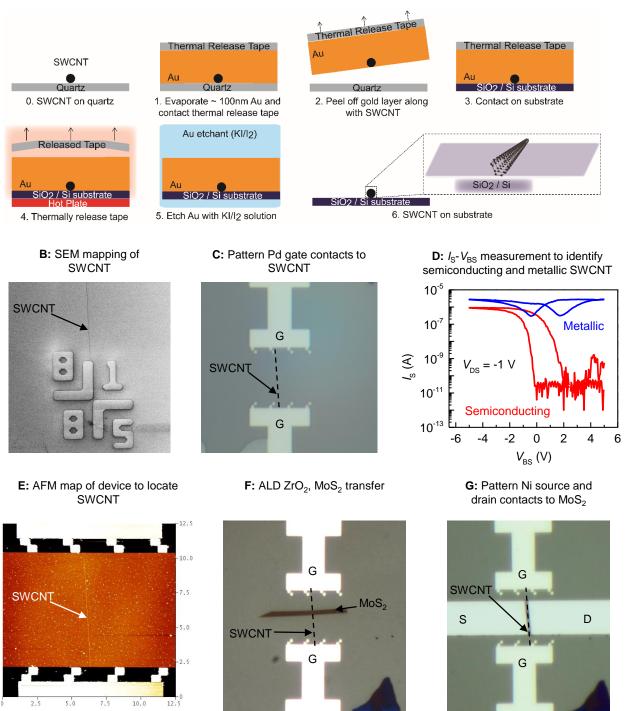

The experimental device structure of the 1D2D-FET (Fig. 2A) consists of a MoS<sub>2</sub> channel (number of layers vary), a ZrO<sub>2</sub> gate dielectric, and a SWCNT gate, on a 50 nm SiO<sub>2</sub>/Si substrate, with a physical gate length ( $L_G$ , ~ d) of ~ 1 nm. Long, aligned SWCNTs grown by chemical vapor deposition were transferred onto a  $n^+$  Si/SiO<sub>2</sub> substrate (50 nm thick SiO<sub>2</sub>) (23), located with scanning electron microscopy (SEM), and contacted with Pd via lithography and metallization. These steps were followed by atomic layer deposition (ALD) of ZrO<sub>2</sub>, and pick-and-place dry transfer of MoS<sub>2</sub> to complete the device. The detailed process flow and discussion about device fabrication is provided in Fig. S3.

Figure 2B shows the optical image of a representative 1D2D-FET capturing the MoS<sub>2</sub> flake, the source drain contacts to MoS<sub>2</sub> and the gate contacts to the SWCNT. The SWCNT and the MoS<sub>2</sub> flake can be identified in the false-colored scanning electron microscope (SEM) image of a representative sample (Fig. 2C). The 1D2D-FET consists of four electrical terminals; source (S), drain (D), SWCNT gate (G) and the  $n^+$  Si substrate back gate (B). The SWCNT gate underlaps

the S/D contacts. These underlapped regions were electrostatically doped by the Si back gate during the electrical measurements, thereby serving as  $n^+$  extension contact regions. The device effectively operated like a junctionless transistor (24), where the SWCNT gate locally depleted the  $n^+$  MoS<sub>2</sub> channel after applying a negative voltage and thus turning OFF the device.

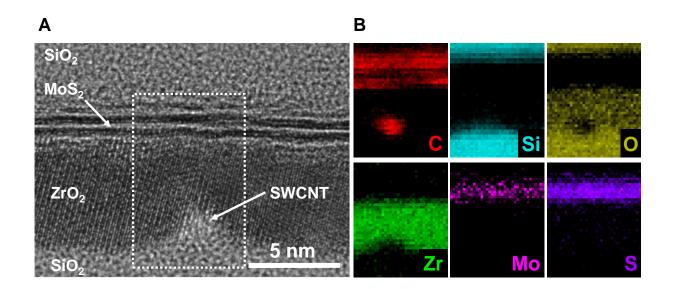

A cross-sectional transmission electron microscope (TEM) image of a representative 1D2D-FET (Fig. 2D) shows the SWCNT gate,  $ZrO_2$  gate dielectric (thickness ~ 5.8 nm), and the bilayer MoS<sub>2</sub> channel. The topography of  $ZrO_2$  surrounding the SWCNT and the MoS<sub>2</sub> flake on top of the gate oxide was flat as seen in the TEM image. This geometry is consistent with ALD nucleation initiating on the SiO<sub>2</sub> substrate surrounding the SWCNT, and eventually covering it completely as the thickness of deposited  $ZrO_2$  exceeds the SWCNT diameter, d (25). The spatial distribution of carbon, zirconium, and sulfur was observed in the electron energy loss spectroscopy (EELS) map of the device region (Fig. 2E), thus confirming the location of the SWCNT,  $ZrO_2$  and MoS<sub>2</sub> in the device (Fig. S4) (20).

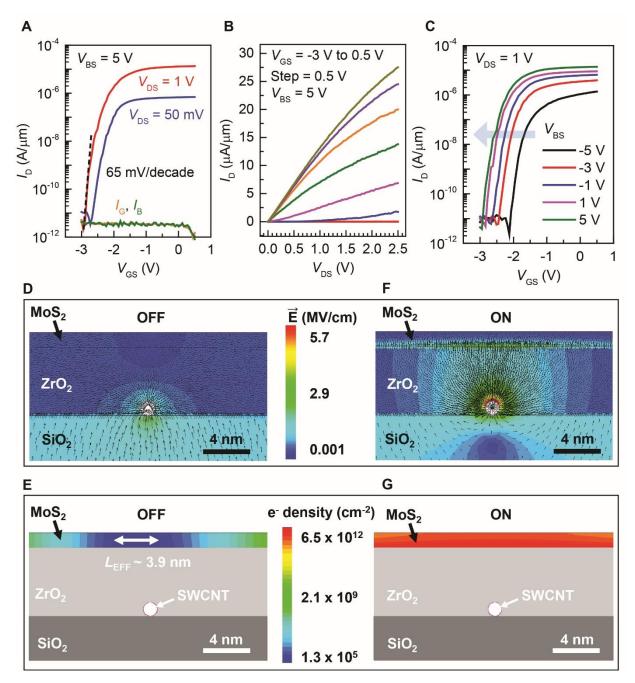

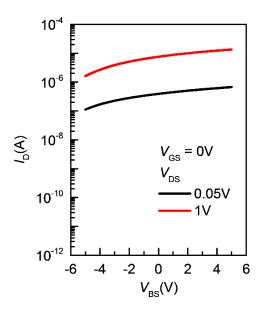

The electrical characteristics for a 1D2D-FET with a bilayer MoS<sub>2</sub> channel (Fig. 3) show that the MoS<sub>2</sub> extension regions (the underlapped regions between the SWCNT gate and S/D contacts) could be heavily inverted (i.e.,  $n^+$  state) by applying a positive back gate voltage of  $V_{BS}$ = 5 V to the Si substrate. The  $I_D$ -V<sub>BS</sub> characteristics (Fig. S5) indicate that the MoS<sub>2</sub> flake was strongly inverted by the back gate at  $V_{BS} = 5$  V. The  $I_D$ -V<sub>GS</sub> characteristics for the device at  $V_{BS} =$ 5 V and  $V_{DS} = 50$  mV and 1 V (Fig. 3A), demonstrate the ability of the ~ 1 nm SWCNT gate to deplete the MoS<sub>2</sub> channel and turn OFF the device. The 1D2D-FET exhibited excellent subthreshold characteristics with a near ideal SS of ~ 65 mV/decade at room temperature and ON/OFF current ratio of ~ 10<sup>6</sup>. The drain-induced barrier lowering (DIBL) was ~ 290 mV/V. Leakage currents through the SWCNT gate ( $I_G$ ) and the  $n^+$  Si back gate ( $I_B$ ) are below the measurement noise level (Fig. 3A). The interface trap density ( $D_{TT}$ ) of the ZrO<sub>2</sub>-MoS<sub>2</sub> interface estimated from SS was ~ 1.7 × 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup>, which is typical for transferred MoS<sub>2</sub> flakes (26) because of the absence of surface dangling bonds (20).

Figure 3B shows the  $I_D$ - $V_{DS}$  characteristics at different  $V_{GS}$  values and fixed  $V_{BS} = 5$  V. The  $I_D$ - $V_{GS}$  characteristics depended strongly on the value of  $V_{BS}$ , which affects the extension region resistance. The inversion of the extension regions increased with increasing  $V_{BS}$ , thus reducing the series resistance and contact resistance and led to an increase in the ON-current and an improvement in the SS. At more positive values of  $V_{BS}$ ,  $V_{GS}$  had to be more negative in order to deplete the MoS<sub>2</sub> channel, which in turn made the threshold voltage more negative. Above  $V_{BS} = 1$  V, the SS and  $I_{ON}$  did not improve any further and the extension regions were strongly inverted (Fig. 3C). Thus, the 1D2D-FET operated as a short channel device.

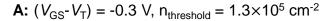

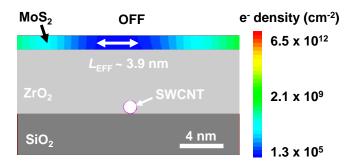

**Figure 3: Electrical characterization and TCAD simulations of 1D2D-FET** (A)  $I_D$ - $V_{GS}$  characteristics of a bilayer MoS<sub>2</sub> channel SWCNT gated FET at  $V_{BS} = 5$  V and  $V_{DS} = 50$  mV and 1 V. The positive  $V_{BS}$  voltage electrostatically dopes the extension regions  $n^+$ . (B)  $I_D$ - $V_{DS}$  characteristic for the device at  $V_{BS} = 5$  V and varying  $V_{GS}$ . (C)  $I_D$ - $V_{GS}$  characteristics at  $V_{DS} = 1$  V and varying  $V_{BS}$  illustrating the impact of back gate bias on the extension region resistance, SS, ON-current and device characteristics. Electric field contour plots for a simulated bilayer MoS<sub>2</sub> device using TCAD in the (D) OFF and (F) ON-state. Electron density plots for the simulated device using TCAD in the (E) OFF and (G) ON-state. The electron density in the depletion region is used to define the effective channel length ( $L_{EFF}$ ).  $L_{EFF} \sim d \sim L_G$  in the ON-state and  $L_{EFF} > L_G$  in the OFF-state because of the fringing electric fields from the SWCNT gate.

#### 2.3 Simulation results and electrostatics

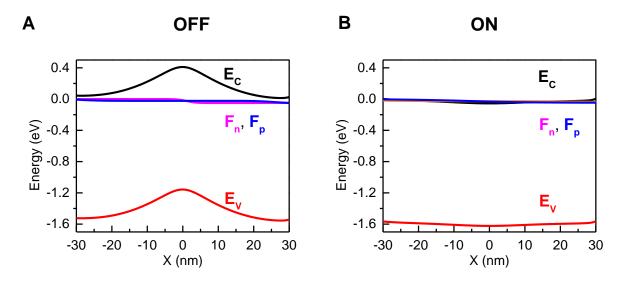

We performed detailed simulations using Sentaurus TCAD to understand the electrostatics of the 1D2D-FET. The OFF- and ON-state conditions correspond to ( $V_{GS} - V_T$ ) of -0.3 V and 1.5 V, respectively (which give an ON/OFF current ratio ~ 10<sup>6</sup>). The electric field contour plot (Fig. 3D) in the OFF-state has a region of low electric field in the MoS<sub>2</sub> channel near the SWCNT, indicating that it is depleted. The reduced electron density in the MoS<sub>2</sub> channel (Fig. 3E), and the presence of an energy barrier to electrons in the conduction band (Fig. S6A) are also consistent with the OFF-state of the device. The extension regions are still under inversion because of the positive back gate voltage. The electron density of the MoS<sub>2</sub> channel in the depletion region can be used to define the effective channel length ( $L_{EFF}$ ) of the 1D2D-FET, which is the region of channel controlled by the SWCNT gate (27-29). The channel is considered to be depleted if the electron density falls below a defined threshold ( $n_{threshold}$ ). The OFF-state  $L_{EFF}$ , defined as the region of MoS<sub>2</sub> with electron density  $n < n_{threshold}$  ( $n_{threshold} = 1.3 \times 10^5$  cm<sup>-2</sup>), for this simulated 1D2D-FET is  $L_{EFF} \sim 3.9$  nm (Fig. 3E). Note that  $L_{EFF}$  is dependent on  $V_{GS}$  and the value of  $n_{threshold}$ (Fig. S7).

As the device is turned OFF, the fringing electric fields from the SWCNT (Fig. 3D) deplete farther regions of the MoS<sub>2</sub> channel, and thus increase  $L_{EFF}$ . The short height of the naturally defined SWCNT gate prevents large fringing fields from controlling the channel, and hence achieves a smaller  $L_{EFF}$  compared to lithographically patterned gates (Fig. S8). The electric field and electron density contours for the device in the ON-state confirm the strong inversion of the channel region near the SWCNT (Fig. 3, F and G) with  $L_{EFF} \sim L_G = 1$  nm. The energy bands in this case are flat in the entire channel region (Fig. S6B), with the ON-state current being limited by the resistance of the extension regions and mainly the contacts. Doped S-D contacts along with shorter extension regions will result in increased ON-current.

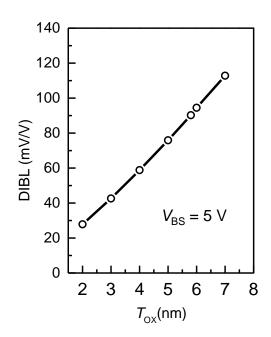

The impact of  $T_{OX}$  scaling on short channel effects like DIBL was also studied using simulations (Fig. S9). The electrostatics of the device improves, and the influence of the drain on the channel reduces as  $T_{OX}$  is scaled down to values commensurate with  $L_G$ . This effect is seen by the strong dependence of DIBL on  $T_{OX}$ , thus demonstrating the need for  $T_{OX}$  scaling and high-k 2D dielectrics to further enhance the device performance.

#### 2.4 Channel thickness dependence

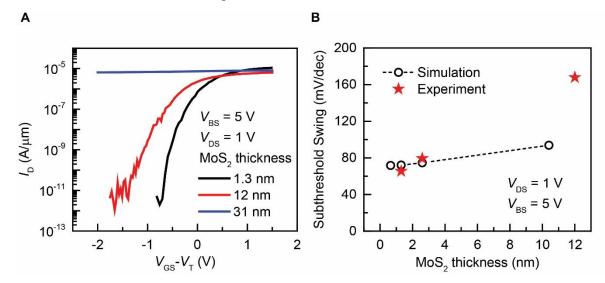

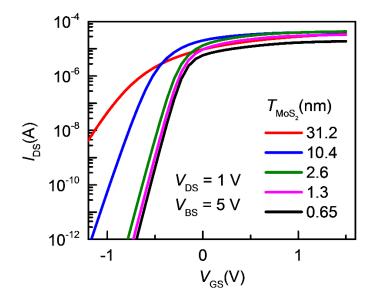

The effect of MoS<sub>2</sub> thickness on the device characteristics was systematically explored. At the scaling limit of the gate length, the semiconductor channel thickness must also be scaled down aggressively as described earlier. The electrostatic control of the SWCNT gate on the MoS<sub>2</sub> channel decreased with increasing distance from the ZrO<sub>2</sub>-MoS<sub>2</sub> interface. Thus, as the MoS<sub>2</sub> flake thickness was increased, the channel could not be completely depleted by applying a negative  $V_{GS}$ . Because of this effect, the SS for a 12 nm thick MoS<sub>2</sub> device (~ 170 mV/decade) was much larger than that of bilayer MoS<sub>2</sub> (~ 65 mV/decade), and as the thickness of MoS<sub>2</sub> was increased to ~ 31

nm the device could no longer be turned OFF (Fig. 4A). The experimental SS as a function of MoS<sub>2</sub> thickness was qualitatively consistent with the TCAD simulations (Fig. 4B and S10), showing an increasing trend with increasing channel thickness. The unwanted variations in device performance caused by channel thickness fluctuations (Fig. 4B and S10), and the need for low OFF-state current at short channel lengths (Fig. 1 and 3), thus justify the need for layered semiconductors like TMDs at the scaling limit.

Figure 4: MoS<sub>2</sub> thickness dependence. (A) Dependence of MoS<sub>2</sub> channel thickness on the performance of 1D2D-FET. SS increases with increasing MoS<sub>2</sub> channel thickness. (B) Extracted SS from experimental curves and TCAD simulations show increasing SS as channel thickness  $T_{CH}$  increases.

TMDs offer the ultimate scaling of thickness with atomic level control, and the 1D2D-FET structure enables the study of their physics and electrostatics at short channel lengths by using the natural dimensions of a SWCNT, removing the need for any lithography or patterning processes which are challenging at these scale lengths. However, large-scale processing and manufacturing of TMD devices down to such small gate lengths are existing challenges requiring future innovations. For instance, research on developing process-stable low-resistance ohmic contacts to TMDs, and scaling of the gate dielectric by using high- $\kappa$  2D insulators is essential to further enhance device performance. Wafer-scale growth of high quality films (*30*) is another challenge toward achieving very-large-scale integration of TMDs in integrated circuits. Finally, fabrication of electrodes at such small scale lengths over large areas requires significant advances in lithographic techniques. Nevertheless, the work here provides new insight into the ultimate scaling of gate lengths for a FET by surpassing the 5 nm limit (*3-7*) often associated with Si technology.

## **2.5 Supporting Information**

#### Materials and methods:

SWCNT growth on quartz: Aligned SWCNTs were grown according to a process similar to (23) modified to deliver a low aligned SWCNT density. 4" ST-cut quartz wafers were purchased from Hoffman Materials, Inc. then annealed at 900°C for 8.5 hours to repair the surface crystal. A  $\approx$ 3.66 Å film of iron (99.95% pure) was evaporated using electron-beam evaporation onto 4µm wide stripes defined using photo-lithography at a rate of 0.33 Å/s. This was followed by metal liftoff and resist removal. The sample was grown in a 5" diameter FirstNano EasyTube 3000 CNT CVD furnace. The temperature was ramped to 610 °C in O<sub>2</sub> for calcination, then to 865 °C in 120 sccm H<sub>2</sub> at 315 Torr for reduction of the iron catalyst. After stabilizing temperature for 10 minutes, 1 SLM of CH<sub>4</sub> was introduced to the chamber to begin growth. After one hour, the sample was cooled in H<sub>2</sub> ambient. The SWCNT density as measured by SEM was 1 SWCNT per 15 µm across the wafer.

SEM (scanning electron microscopy) imaging was performed using a Zeiss Gemini Ultra-55 field emission scanning electron microscope (FESEM). A ~ 1 kV accelerating voltage was used for imaging the devices and to register the locations of the SWCNTs with respect to pre-patterned lithography markers.

AFM (atomic force microscopy) was performed using a Digital Instruments Nanoscope Dimension 3100 AFM. The AFM was done in the tapping mode using ~ 300 kHz resonance frequency, Budget sensors Tap300-G tapping mode tips.

TEM (transmission electron microscopy) / STEM (scanning transmission electron microscopy): High resolution TEM/STEM imaging was performed using a probe-corrected JEM-ARM200F (JEOL USA, Inc.) operated at 200 kV. HAADF-STEM imaging was carried out with a 24 mrad convergence semi-angle electron beam and the collection angle for the ADF detector was set to 90-370 mrad.

*Elemental Mapping:* Electron energy loss spectroscopy (EELS) and energy dispersive spectroscopy (EDS) mapping was performed with a Gatan Enfina spectrometer and X-MaxN 100TLE detector (Oxford Instruments), respectively. The collection angle for the EELS spectrum was set to be 31 mrad. The spatial resolution of the mapping is 0.27 nm/pixel and the collection time is 0.4 s/pixel.

*Electrical characterization:* Electrical measurements were performed under vacuum (~ 10<sup>-5</sup> mbar) in Lakeshore vacuum probe station using Agilent Technologies B1500A Semiconductor Device Analyzer.

#### Analytical 2D electrostatics model for Dual Gate Metal-Oxide-Semiconductor Field-Effect Transistor (DGMOS-FET) (21, 31)

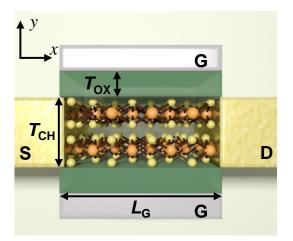

A symmetric DGMOS-FET structure is assumed as shown in Fig. S1. An analytical solution to the 2D Poisson equation is derived assuming a channel material with anisotropic dielectric constant using the approach taken in reference (21).

$$\vec{\nabla} \cdot \vec{D} = \rho \dots (1)$$

$$\begin{bmatrix} Dx \\ Dy \\ Dz \end{bmatrix} = \begin{bmatrix} \varepsilon x & 0 & 0 \\ 0 & \varepsilon y & 0 \\ 0 & 0 & \varepsilon z \end{bmatrix} \begin{bmatrix} Ex \\ Ey \\ Ez \end{bmatrix} \dots (2)$$

$$\varepsilon_x \frac{\partial^2 \varphi}{\partial x^2} + \varepsilon_y \frac{\partial^2 \varphi}{\partial y^2} = q N_A \dots (3)$$

Equation 3 is Poisson's equation in 2D considering an anisotropic dielectric constant. Here the axes of transport X and Y (Fig. S1) are assumed to coincide with the crystal axes of the material. Thus the electric permittivity tensor is diagonal. To solve the differential equation 3 and get an analytical expression for the electric potential, we assume the first term on the left hand side to be much smaller than the second term (quasi-2D approximation). The 2D electric potential in the channel region is then computed similar to the procedure in reference (21).

$$\varphi(x,y) = \frac{y^2 \varepsilon_{OX,y}(V_{GS} - V_{FB} - \varphi_s(x))}{\varepsilon_{CH,y} T_{CH} T_{OX}} - \frac{y \varepsilon_{OX,y}(V_{GS} - V_{FB} - \varphi_s(x))}{\varepsilon_{CH,y} T_{OX}} + \varphi_s(x) \dots (4)$$

Here  $\varphi_s(x)$  is the surface potential.

Equation 4 is evaluated at the center of the channel to give  $\varphi_C(x) = \varphi(x, \frac{T_{CH}}{2})$  and is then expressed in terms of  $\varphi_C(x)$  by replacing  $\varphi_S(x)$ .  $\varphi(x, y)$  which is expressed in terms of  $\varphi_C(x)$  must satisfy equation 3. After substitution into equation 3 and simplification we get,

$$\frac{\partial^2 \varphi_C(x)}{\partial x^2} + \frac{1}{\lambda^2} \left( V_{GS} - V_{FB} - \varphi_C(x) - \frac{q N_A \lambda^2}{\varepsilon_{CH,x}} \right) = 0 \dots (5)$$

where  $\lambda$  is the characteristic length of the device.

$$\lambda = \sqrt{\frac{\varepsilon_{CH,x}T_{CH}T_{OX}}{2\varepsilon_{OX,y}}} \left(1 + \frac{\varepsilon_{OX,y}T_{CH}}{4\varepsilon_{CH,y}T_{OX}}\right) \dots (6)$$

From the above equation we see that the characteristic length depends on the dielectric constant along both x and y. The larger the dielectric constant along y, the more the influence of gate voltage and smaller the characteristic length and short channel effects. On the other hand, a large dielectric constant along x means the influence of drain voltage on the channel increases and short channel effects such as DIBL become more prominent. The boundary conditions for solving equation 5 are  $\varphi_C(0) = V_{bi}$  and  $\varphi_C(L_G) = V_{bi} + V_{DS}$ . Considering the case of very light to no

doping in the channel i.e.  $N_A \sim 0$  (hence  $V_{bi} = \frac{E_g}{2q}$ ), and solving equation 5 with the above boundary conditions we get,

$$\varphi_{C}(x) = (V_{GS} - V_{FB}) \left(1 - e^{-\frac{x}{\lambda}}\right) + V_{bi} e^{-\frac{x}{\lambda}} - \frac{\sinh\left(\frac{x}{\lambda}\right)}{\sinh\left(\frac{L}{\lambda}\right)} (V_{GS} - V_{FB} - V_{bi}) \left(1 - e^{-\frac{L}{\lambda}}\right) + V_{DS} \frac{\sinh\left(\frac{x}{\lambda}\right)}{\sinh\left(\frac{L}{\lambda}\right)} \dots (7)$$

Using  $\varphi_c(x)$  as found above, the potential at the surfaces  $\varphi_s(x)$  and the 2D potential in the entire channel  $\varphi(x, y)$  can also be computed using equation 4. The barrier between the source and drain in the OFF-state is dependent on  $V_{\text{bi}}$  and hence the bandgap ( $E_g$ ) of the semiconductor. The larger the bandgap, the larger is the OFF-state barrier between source and drain.  $\lambda$  determines the shape of the barrier between source and drain.

The quasi-2D model provides a good qualitative analysis of the electrostatics in a DGMOS-FET for comparing different channel materials. For more accurate analysis, first principle calculations and self-consistent solutions of the Schrodinger-Poisson equations are essential.

#### **Direct source-to-drain tunneling leakage**

A qualitative estimate of the amount of direct source-to-drain tunneling in a material in the OFF-state can be obtained using the electrostatic model derived above. The WKB approximation (equation 8) is used to compute the probability of tunneling across the energy barrier, and the Landauer relation (equation 9) is used to calculate the leakage current due to tunneling (*32, 33*).

$$T(E) = e^{-\frac{2}{\hbar} \int_{x_i}^{x_o} \sqrt{2m^*(E_C(x) - E)} dx} \dots (8)$$

$$I_{SD-LEAK} = \frac{2q}{h} \int_{E_S}^{E_{C,max}} M(E) T(E) \left[ f(E, E_{F,S}) - f(E, E_{F,D}) \right] dE \dots (9)$$

$$M(E) = \frac{W\sqrt{2m^*(E-E_S)}}{\pi h} \dots (10)$$

The parameter values used for the calculations in Fig. 1 are given in table S1.

In equation 8, T(E) is the tunneling probability through the energy barrier at energy level *E*.  $x_o$  and  $x_i$  indicate the extent of the barrier.  $E_C(x)$  is the conduction band profile between the source and drain from  $x_i$  to  $x_o$ .  $m^*$  is the effective mass of the carriers tunneling through the barrier.

In equation 9,  $I_{SD-LEAK}$  is the direct source to drain leakage current. M(E) is the number of ballistic modes of transport at energy E (equation 10) (32),  $E_S$  is the energy level of the source (reference) and  $E_{C,max}$  is the top of the conduction band profile between the source and drain. f(E) is the Fermi-Dirac distribution and  $E_{F,S}$  and  $E_{F,D}$  are the Fermi levels in source and drain respectively.

TMDCs have a higher effective mass along the direction of transport (e.g.  $m_n^* \sim 0.55m_0$  for MoS<sub>2</sub> versus  $m_n^* \sim 0.19m_0$  for Si [100]) (19, 34) which reduces the tunneling probability and therefore  $I_{\text{SD-LEAK}}$ . Figure 1 discusses the impact of effective mass on transistor scaling using the example of a symmetric double-gate MOSFET (DGMOS-FET) structure (Fig. S1). Figure 1A shows normalized  $I_{\text{SD-LEAK}}$  as a function of channel thickness for Si and MoS<sub>2</sub>. The channel conduction band profile required to calculate  $I_{\text{SD-LEAK}}$  is derived using the analytical 2D DGMOS-FET electrostatic model proposed in ref (21). The parameter values used in the calculations (table S1) account for quantum mechanical effects on the bandgap, dielectric constant and effective mass at ultra-thin channel thicknesses (19, 35-39). MoS<sub>2</sub> shows more than two orders reduction in  $I_{\text{SD-LEAK}}$  compared to Si due to the larger electron effective mass. Figure 1B plots the dependence of  $I_{\text{SD-LEAK}}$  on  $L_G$ . The dotted lines in Fig. 1A and 1B represent the Low Operating Power (LOP) limit for the 2026 technology node as specified by the international technology roadmap for semiconductors (ITRS) (40). Figure 1B reveals that for similar channel thickness, MoS<sub>2</sub> transistors can be scaled to shorter gate lengths as compared to Si.

#### Calculation of D<sub>IT</sub>

$$SS = \frac{kTln(10)}{q} \left(1 + \frac{C_D + C_{IT}}{C_{OX}}\right) \dots (11)$$

Equation 11 relates SS to the interface trap density for the device (41). Here k is the Boltzmann constant, T is temperature in Kelvin and q is the charge of an electron. For the 1D2D-FET structure,  $C_D$  (depletion capacitance) ~ 0,  $C_{TT}$  (interface trap capacitance) =  $qD_{TT}$  and  $C_{OX}$  (oxide capacitance) =  $\varepsilon_{OX}/T_{OX}$ .  $\varepsilon_{OX}$  is the permittivity of the gate oxide (ZrO<sub>2</sub> dielectric constant ~ 25 (42)) and Tox is the oxide thickness (~ 5.8 nm) measured from TEM in Fig. 2D.

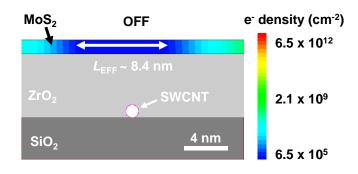

#### Analytical derivation of parasitic capacitance from fringing electric fields

Figure S8 shows the fringing electric field lines in an underlap transistor. The fringing electric field lines lead to parasitic capacitance ( $C_{\text{parasitic}}$ ) and a larger effective channel length ( $L_{\text{EFF}}$ ).

$$C_{OX} = \frac{L_G W \varepsilon_{OX}}{T_{OX}} \dots (12)$$

$$C_{parasitic} \approx \int_{T_{OX}}^{T_{ZrO2}} \left(\frac{2W \varepsilon_{OX}}{\pi y}\right) dy = \left(\frac{2W \varepsilon_{OX}}{\pi}\right) \ln \left(\frac{T_{ZrO2}}{T_{OX}}\right) = \left(\frac{2W \varepsilon_{OX}}{\pi}\right) \ln \left(1 + \frac{T_G}{T_{OX}}\right) \dots (13)$$

Equation 12 gives the capacitance  $C_{OX}$  for the parallel electric field lines from the gate electrode to the channel.  $\varepsilon_{OX}$  is the electric permittivity of the gate dielectric, W is the width and  $L_G$  is the physical gate length.  $T_{OX} = (T_{ZrO2} - T_G)$  is kept constant for devices of different gate heights ( $T_G$ ). Equation 13 calculates the parasitic capacitance due to the fringing electric field lines from the gate electrode and is dependent on  $T_G$ . Larger the height of the electrode, higher is the parasitic capacitance. The natural short height of a SWCNT helps achieve small  $L_{EFF}$  and small  $C_{\text{parasitic}}$  compared to lithographically patterned tall gate structures. The above simplistic analytical derivation for  $C_{\text{parasitic}}$  assumes the fringing electric field lines to be circular (Fig. S8) and

underestimates the capacitance. For accurate analysis, simulation of the 2D electrostatics in the device is essential.

**Figure S1: Schematic of dual-gated metal-oxide-semiconductor-field-effect-transistor.** Schematic of a symmetric dual-gated metal-oxide-semiconductor-field-effect-transistor (DGMOS-FET) used to study impact of channel material properties on the scaling limit of transistors in Fig. 1.

Figure S2: Dependence of characteristic length on channel thickness. Device electrostatic characteristic length ( $\lambda$ ) as a function of channel thickness ( $T_{CH}$ ) for Si and MoS<sub>2</sub>.

#### A: SWCNT transfer process

Figure S3: Detailed process flow for SWCNT gated MoS<sub>2</sub> FET

Figure S3 shows the detailed process flow for the device fabrication. The first step of the process involves the transfer of grown SWCNT from the growth substrate (quartz) to the target 50 nm SiO<sub>2</sub> / Si substrate using gold as the transfer layer (23) (Fig. S3A). The target substrate is pre-patterned with 0.5/30 nm Cr/Pt alignment markers. These alignment markers are used to relatively locate the transferred SWCNT in a scanning electron microscope (SEM) image (Fig. S3B). Care is taken to

ensure the SWCNTs are not damaged during the SEM by minimizing the exposure time under the electron-beam. Gate electrodes are then patterned using electron-beam lithography followed by 30 nm Pd evaporation and liftoff process (Fig. S3C). *Is-VBs* measurements of the SWCNT devices help to identify the metallic or semiconducting nature of the SWCNT (Fig. S3D). After the measurement, the SWCNT devices are mapped with an atomic force microscope (AFM) to find the relative location of the SWCNT with respect to the gate electrodes (Fig. S3E). Post the AFM map, ZrO<sub>2</sub> gate dielectric is deposited using atomic layer deposition (ALD) and the MoS<sub>2</sub> flake is transferred on top using a dry pick and transfer method (*14*) using poly(methyl methacrylate) (PMMA) as the transfer medium (Fig. S3F). The AFM map taken prior to the ALD is then used as a mask for a second electron-beam lithography step, to pattern the source and drain electrodes (Ni 40 nm) as shown in Fig. S3G, thus completing the device fabrication.

**Figure S4: EELS map.** EELS mapping of the 1D2D-FET showing the spatial location of the different elements (EDS map is shown for Mo). Carbon mapping clearly indicates the position of the SWCNT under the ZrO<sub>2</sub> gate dielectric and the MoS<sub>2</sub> flake on top of it. Carbon seen on top of the ZrO<sub>2</sub> can be attributed to organic residue like PMMA and contaminants from processing steps and dry transfer of MoS<sub>2</sub>.

Figure S5:  $I_D$ - $V_{BS}$  characteristics obtained by varying the  $n^+$  Si back gate.  $I_D$ - $V_{BS}$  characteristics for the device in Fig. 3A-C. The MoS<sub>2</sub> extensions regions are completely inverted using the Si back gate at  $V_{BS} = 5$  V.

**Figure S6: Energy band diagrams in ON and OFF-states.** Energy band diagrams corresponding to the TCAD simulations in Fig. 3D-G.  $V_{BS} = 5$  V,  $V_{DS} = 50$  mV,  $(V_{GS} - V_T) = 1.5$  V (ON) and  $(V_{GS} - V_T) = -0.3$  V (OFF), for the 2L MoS<sub>2</sub> device. In the OFF-state the bias applied to the SWCNT creates a barrier which opposes the flow of carriers from source to drain. In the ON-state no barrier exists to the flow of electrons from the source to drain and the ON-current is limited by the series resistance of the extension regions.

**B:**  $(V_{\text{GS}} - V_{\text{T}}) = -0.3 \text{ V}, \text{ n}_{\text{threshold}} = 6.5 \times 10^5 \text{ cm}^{-2}$

**Figure S7: Electron density contour plots.** Dependence of  $L_{EFF}$  on the definition of OFF-state and *n*<sub>thershold</sub> (electron density below which the channel is considered depleted) for  $V_{BS} = 5$  V,  $V_{DS} = 50$  mV (27-29). The OFF-state corresponds to ( $V_{GS} - V_T$ ) = -0.3 V and ON-state corresponds to ( $V_{GS} - V_T$ ) = 1.5 V (or an ON/OFF current ratio of ~ 10<sup>6</sup>).  $L_{EFF}$  is of the order of 5 nm as seen from the simulations. The 2D electron density is obtained by multiplying the 3D density obtained from simulations with  $T_{CH}$ , by assuming uniform distribution along the thickness of MoS<sub>2</sub>.

**Figure S8: Parasitic capacitance and dependence on gate height.** Effective channel length  $(L_{EFF})$  > physical gate length  $(L_G)$  due to fringing electric field.  $L_{EFF}$  and  $C_{parasitic}$  increase as the height of the gate  $(T_G)$  increases, for the same value of  $T_{OX}$  ( $T_{ZrO2} - T_G$ ).  $L_{EFF}$  and  $C_{parasitic}$  are small for a SWCNT gate as compared to lithographically defined gates because of the naturally short height of a SWCNT, and hence less fringing electric field lines coupling to the channel (43).

**Figure S9: Dependence of DIBL on gate oxide thickness.** Drain-induced barrier-lowering (DIBL) as a function of the ZrO<sub>2</sub> thickness calculated using simulations. Effective oxide thickness (EOT) scaling helps improve the electrostatics in the device and reduce DIBL.

**Figure S10: Thickness dependence of MoS<sub>2</sub>.**  $I_{DS}$ - $V_{GS}$  curves for several different channel thicknesses from TCAD simulations used to calculate SS in Fig. 4B. The TCAD results qualitatively match the experimental trends. Doping of MoS<sub>2</sub> ( $N_D$ ) is assumed to be  $10^{17}$  cm<sup>-3</sup>, and the dielectric constant of ZrO<sub>2</sub> = 25 (42). Electron affinity of MoS<sub>2</sub> is assumed to be 4 eV (44). All other values are as specified in table S1. For more quantitative comparison, the analysis must involve simulation of the 2D density of states for MoS<sub>2</sub>, correction for contact resistance, oxide and interface traps, along with using more accurate values for  $m^*$ ,  $E_G$ ,  $N_D$ , etc.

| MoS2                 |                   |                        |                              | Si                   |                   |                    |                              |

|----------------------|-------------------|------------------------|------------------------------|----------------------|-------------------|--------------------|------------------------------|

| T <sub>CH</sub> (nm) | ε (relative) (35) | $E_{\rm G}^{\rm (38)}$ | <b>m</b> <sub>e</sub> * (19) | T <sub>CH</sub> (nm) | ε (relative) (36) | $E_{\rm G}^{(37)}$ | <b>m</b> <sub>e</sub> * (39) |

| 0.65                 | 3.93              | 1.88                   | $\sim 0.55$                  | 0.5431               | 4.39              |                    | ~ 0.22                       |

| 1.3                  | 4.71              | 1.59                   | $\sim 0.55$                  | 1.0862               | 6.62              | 1.90               | ~ 0.22                       |

| 1.95                 | 4.90              | 1.47                   | $\sim 0.55$                  | 1.6293               | 7.66              | 1.46               | ~ 0.22                       |

| 2.6                  | 6.24              | 1.44                   | $\sim 0.55$                  | 2.1724               | 8.70              | 1.31               | ~ 0.22                       |

| 3.25                 | 7.71              | 1.42                   | $\sim 0.55$                  | 2.7155               | 9.73              | 1.23               | ~ 0.22                       |

| 10.4                 | ~ 10              | ~ 1.3                  | ~ 0.55                       | 3.2586               | 10.32             | 1.19               | ~ 0.22                       |

| 31.2                 | ~ 10.5            | ~ 1.3                  | ~ 0.55                       |                      |                   |                    |                              |

Table S1: Parameter values used for calculations in Fig. 1 and Fig. S2. Values have been extracted

from references (19, 35-39). The effects of quantum confinement at atomic-scale channel thicknesses on parameter values like bandgap, dielectric constant and effective mass are considered for more accurate analysis. The bandgap values for  $MoS_2$  correspond to the optical bandgap from photoluminescence spectra. The bandgap of Si is obtained from optical absorption spectra.

## **References:**

- 1. T. N. Theis, P. M. Solomon, It's Time to Reinvent the Transistor! *Science* 327, 1600-1601 (2010).

- 2. R. Chau, B. Doyle, S. Datta, J. Kavalieros, K. Zhang, Integrated nanoelectronics for the future. *Nat Mater* 6, 810-812 (2007).

- 3. A. D. Franklin, Nanomaterials in transistors: From high-performance to thin-film applications. *Science* 349, (2015).

- 4. M. Lundstrom, Moore's Law Forever? *Science* 299, 210-211 (2003).

- 5. M. Luisier, M. Lundstrom, D. A. Antoniadis, J. Bokor, in *Electron Devices Meeting* (*IEDM*), 2011 *IEEE International*. (2011), pp. 11.12.11-11.12.14.

- 6. H. Kawaura, T. Sakamoto, T. Baba, Observation of source-to-drain direct tunneling current in 8 nm gate electrically variable shallow junction metal–oxide–semiconductor field-effect transistors. *Applied Physics Letters* 76, 3810-3812 (2000).

- 7. W. S. Cho, K. Roy, The Effects of Direct Source-to-Drain Tunneling and Variation in the Body Thickness on (100) and (110) Sub-10-nm Si Double-Gate Transistors. *IEEE Electron Device Letters* 36, 427-429 (2015).

- 8. B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, Single-layer MoS<sub>2</sub> transistors. *Nat Nano* 6, 147-150 (2011).

- 9. D. Sarkar, X. Xie, W. Liu, W. Cao, J. Kang, Y. Gong, S. Kraemer, P. M. Ajayan, K. Banerjee, A subthermionic tunnel field-effect transistor with an atomically thin channel. *Nature* 526, 91-95 (2015).

- H. Liu, A. T. Neal, P. D. Ye, Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 6, 8563-8569 (2012).

- H. Wang, L. Yu, Y.-H. Lee, Y. Shi, A. Hsu, M. L. Chin, L.-J. Li, M. Dubey, J. Kong, T. Palacios, Integrated circuits based on bilayer MoS<sub>2</sub> transistors. *Nano letters* 12, 4674-4680 (2012).

- 12. K. F. Mak, K. L. McGill, J. Park, P. L. McEuen, The valley Hall effect in MoS<sub>2</sub> transistors. *Science* 344, 1489-1492 (2014).

- 13. D. Jariwala, V. K. Sangwan, L. J. Lauhon, T. J. Marks, M. C. Hersam, Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. *ACS Nano* 8, 1102-1120 (2014).

- 14. H. Fang, C. Battaglia, C. Carraro, S. Nemsak, B. Ozdol, J. S. Kang, H. A. Bechtel, S. B. Desai, F. Kronast, A. A. Unal, G. Conti, C. Conlon, G. K. Palsson, M. C. Martin, A. M. Minor, C. S. Fadley, E. Yablonovitch, R. Maboudian, A. Javey, Strong interlayer coupling in van der Waals heterostructures built from single-layer chalcogenides. *Proceedings of the National Academy of Sciences* 111, 6198-6202 (2014).

- K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, A. K. Geim, Two-dimensional atomic crystals. *Proceedings of the National Academy of Sciences of the United States of America* 102, 10451-10453 (2005).

- C.-H. Lee, G.-H. Lee, A. M. van der Zande, W. Chen, Y. Li, M. Han, X. Cui, G. Arefe, C. Nuckolls, T. F. Heinz, J. Guo, J. Hone, P. Kim, Atomically thin p–n junctions with van der Waals heterointerfaces. *Nat Nano* 9, 676-681 (2014).

- 17. Y. Yoon, K. Ganapathi, S. Salahuddin, How Good Can Monolayer MoS<sub>2</sub> Transistors Be? *Nano Letters* 11, 3768-3773 (2011).

- 18. L. Liu, Y. Lu, J. Guo, On Monolayer MoS<sub>2</sub> Field-Effect Transistors at the Scaling Limit. *IEEE Transactions on Electron Devices* 60, 4133-4139 (2013).

- 19. D. Wickramaratne, F. Zahid, R. K. Lake, Electronic and thermoelectric properties of fewlayer transition metal dichalcogenides. *The Journal of Chemical Physics* 140, 124710 (2014).

- 20. Supplementary materials are available on Science Online.

- 21. K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie, Y. Arimoto, Scaling theory for double-gate SOI MOSFET's. *IEEE Transactions on Electron Devices* 40, 2326-2329 (1993).

- 22. J. Svensson, T. Yu, D. S. Lee, J. M. Kinaret, Y. W. Park, E. E. B. Campbell, A carbon nanotube gated carbon nanotube transistor with 5 ps gate delay. *Nanotechnology* 19, 325201 (2008).

- 23. N. Patil, A. Lin, E. R. Myers, K. Ryu, A. Badmaev, C. Zhou, H. S. P. Wong, S. Mitra, Wafer-Scale Growth and Transfer of Aligned Single-Walled Carbon Nanotubes. *IEEE Transactions on Nanotechnology* 8, 498-504 (2009).

- 24. J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, R. Murphy, Nanowire transistors without junctions. *Nat Nano* 5, 225-229 (2010).

- 25. A. Javey, J. Guo, D. B. Farmer, Q. Wang, E. Yenilmez, R. G. Gordon, M. Lundstrom, H. Dai, Self-Aligned Ballistic Molecular Transistors and Electrically Parallel Nanotube Arrays. *Nano Letters* 4, 1319-1322 (2004).

- X. Zou, J. Wang, C.-H. Chiu, Y. Wu, X. Xiao, C. Jiang, W.-W. Wu, L. Mai, T. Chen, J. Li, J. C. Ho, L. Liao, Interface Engineering for High-Performance Top-Gated MoS<sub>2</sub> Field-Effect Transistors. *Advanced Materials* 26, 6255-6261 (2014).

- 27. T. Yuan, MOSFET channel length: extraction and interpretation. *IEEE Transactions on Electron Devices* 47, 160-170 (2000).

- 28. L. Barbut, F. Jazaeri, D. Bouvet, J.-M. Sallese, Downscaling and Short Channel Effects in Twin Gate Junctionless Vertical Slit FETs. *International Journal of Microelectronics and Computer Science* 4, 103-109 (2013).

- 29. H. Soonwon, L. Kwyro, Extraction of metallurgical effective channel length in LDD MOSFET's. *IEEE Transactions on Electron Devices* 42, 1461-1466 (1995).

- 30. K. Kang, S. Xie, L. Huang, Y. Han, P. Y. Huang, K. F. Mak, C.-J. Kim, D. Muller, J. Park, High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* 520, 656-660 (2015).

- 31. D. J. Frank, Y. Taur, H. S. P. Wong, Generalized scale length for two-dimensional effects in MOSFETs. *IEEE Electron Device Letters* 19, 385-387 (1998).

- 32. Mark Lundstrom (2005), "Notes on the Ballistic MOSFET," https://nanohub.org/resources/489.

- 33. C. S. Lee, E. Pop, A. D. Franklin, W. Haensch, H. S. P. Wong, A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime-Part II: Extrinsic Elements, Performance Assessment, and Design Optimization. *IEEE Transactions on Electron Devices* 62, 3070-3078 (2015).

- 34. H. D. Barber, Effective mass and intrinsic concentration in silicon. *Solid-State Electronics* 10, 1039-1051 (1967).

- X. Chen, Z. Wu, S. Xu, L. Wang, R. Huang, Y. Han, W. Ye, W. Xiong, T. Han, G. Long, Y. Wang, Y. He, Y. Cai, P. Sheng, N. Wang, Probing the electron states and metal-insulator transition mechanisms in molybdenum disulphide vertical heterostructures. *Nat Commun* 6, (2015).

- G. Zhang, M. B. Yu, C. H. Tung, G. Q. Lo, Quantum Size Effects on Dielectric Constants and Optical Absorption of Ultrathin Silicon Films. *IEEE Electron Device Letters* 29, 1302-1305 (2008).

- H. Jang, W. Lee, S. M. Won, S. Y. Ryu, D. Lee, J. B. Koo, S.-D. Ahn, C.-W. Yang, M.-H. Jo, J. H. Cho, J. A. Rogers, J.-H. Ahn, Quantum Confinement Effects in Transferrable Silicon Nanomembranes and Their Applications on Unusual Substrates. *Nano Letters* 13, 5600-5607 (2013).

- 38. K. F. Mak, C. Lee, J. Hone, J. Shan, T. F. Heinz, Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. *Physical Review Letters* 105, 136805 (2010).

- 39. Y. Liu, N. Neophytou, T. Low, G. Klimeck, M. S. Lundstrom, A Tight-Binding Study of the Ballistic Injection Velocity for Ultrathin-Body SOI MOSFETs. *IEEE Transactions on Electron Devices* 55, 866-871 (2008).

- 40. International Technology Roadmap for Semiconductors (ITRS) 2013, http://www.itrs2.net/2013-itrs.html.

- 41. S. M. Sze, K. K. Ng, *Physics of Semiconductor Devices*, (3rd Edition, John Wiley & Sons, Nov 3, 2006).

- 42. P. Harrop, J. Wanklyn, The dielectric constant of zirconia. *British Journal of Applied Physics* 18, 739 (1967).

- 43. H. Zhao, Y. C. Yeo, S. C. Rustagi, G. S. Samudra, Analysis of the Effects of Fringing Electric Field on FinFET Device Performance and Structural Optimization Using 3-D Simulation. *IEEE Transactions on Electron Devices* 55, 1177-1184 (2008).

44. S. Das, H.-Y. Chen, A. V. Penumatcha, J. Appenzeller, High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano letters* 13, 100-105 (2012).

# <sup>3</sup>Gate Quantum Capacitance Effects in Nanoscale Transistors

# **3.1 Introduction**

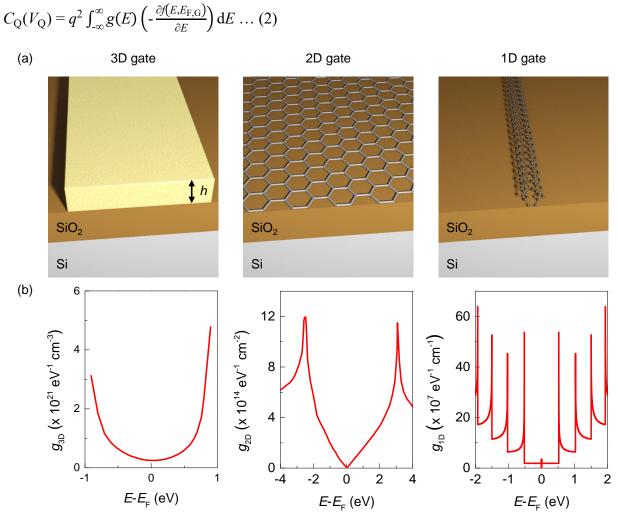

Nanomaterials like graphene, transition metal dichalcogenides (TMDs), carbon nanotubes (CNTs) and graphene nanoribbons (GNRs) have been proposed as potential materials for use in future scaled transistors <sup>1-7</sup>. These materials have low electronic density of states (DOS) resulting from their low-dimensional nature. The impact of quantum capacitance ( $C_Q$ ) of a low-dimensional channel material has become increasingly important, with increasing oxide capacitance ( $C_{OX}$ ) resulting from aggressively scaled effective oxide thicknesses (EOT) <sup>8,9</sup>. As the overall transistor and physical gate dimensions continue to shrink, nanomaterials like graphene and carbon nanotubes have been proposed as potential gate electrode materials because of their large conductivity at these atomic-scale sizes <sup>1,6,10</sup>. However, with the finite number of atoms in atomic-scale gates comes the problem of low gate DOS, which also impacts transistor characteristics and performance.

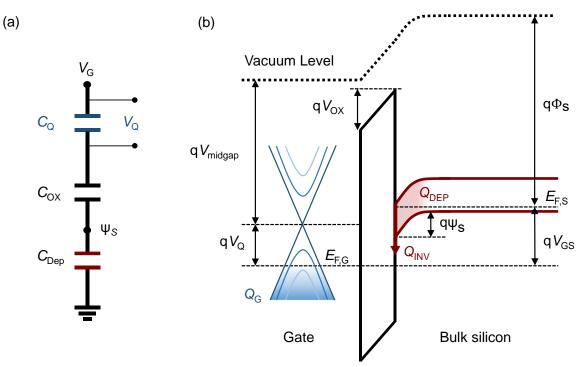

The gate charge  $(Q_G)$  in an ideal MOSFET is always equal and opposite of the total channel charge  $(Q_{CH})$  in the semiconductor <sup>11</sup>. An applied drain-source bias  $(V_{DS})$  across the channel results in a flow of the inversion charge  $(Q_{INV})$  and hence the drain current  $(I_D)$ . For MOSFETs with largevolume metal gate electrodes, the gate has a large DOS and an almost infinite capacity to balance  $Q_{CH}$ . However, for a low-dimensional atomic-scale gate the limited gate DOS limits  $Q_G$ , thereby limiting  $Q_{CH}$ , especially in inversion when  $Q_{INV}$  is large. The starvation of DOS in the gate will dictate the  $I_D$  characteristics in this case.

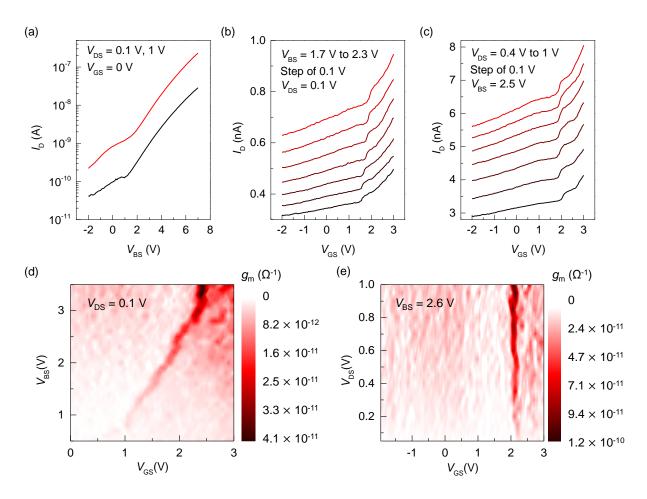

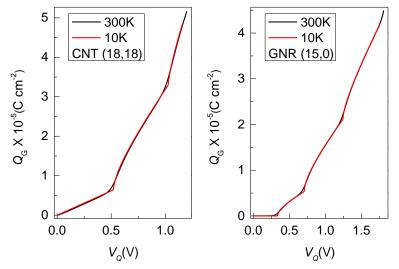

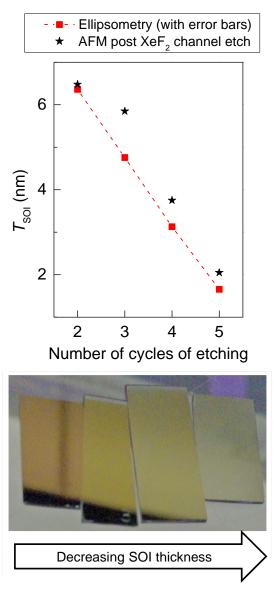

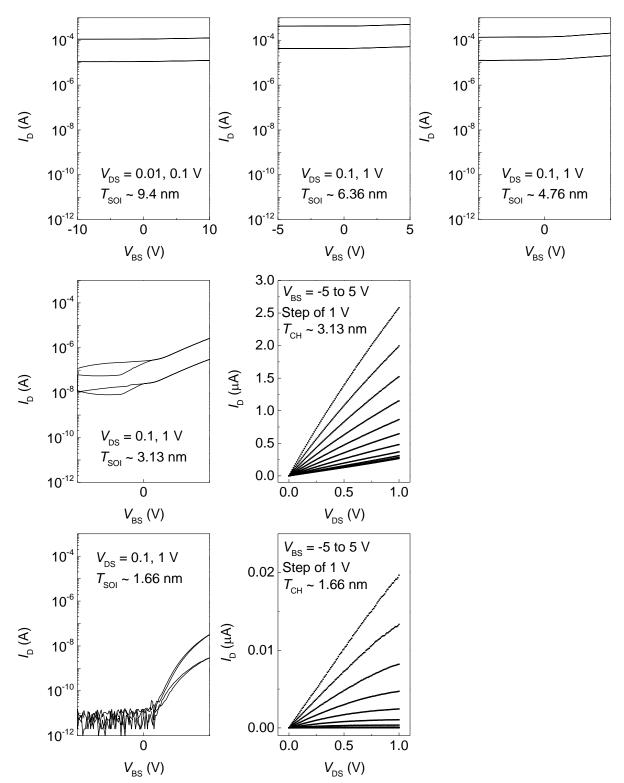

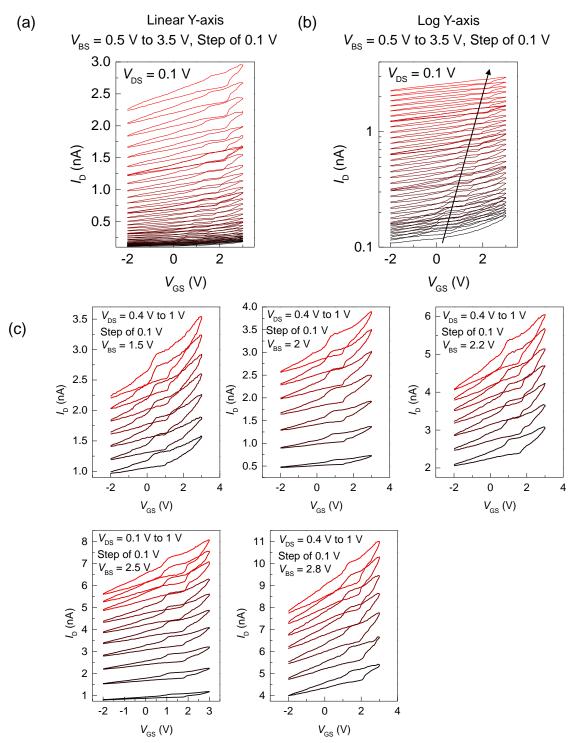

In this work, we consider the impact of gate  $C_Q$  on the transistor characteristics by developing an analytical electrostatics model for a bulk silicon channel MOSFET <sup>10</sup>. This is studied by computing the functional dependence of the gate electrostatic potential ( $V_Q$ ) and the value of  $Q_G$  on the gate DOS and the applied gate bias ( $V_{GS}$ ), for several different gate materials with different dimensionalities <sup>10, 12</sup>. We experimentally demonstrate for the first time, roomtemperature gate  $C_Q$  effects on the  $I_D$  characteristics for an ultra-thin silicon-on-insulator (SOI) channel transistor with a 1-dimensional (1D) single walled carbon nanotube (SWCNT) gate electrode. Quantization features resulting from the Van Hove singularities in the DOS of the CNT gate are observed in the transfer characteristics of the device. Finally, we discuss the potential of engineering the gate DOS to tailor the shape of the  $I_DV_{GS}$  characteristics of a device and the impact of gate  $C_Q$  on the performance of nanoscale transistors.

<sup>&</sup>lt;sup>3</sup> A manuscript similar to this chapter has been submitted to a peer-reviewed journal for publication

## 3.2 Analytical electrostatics model

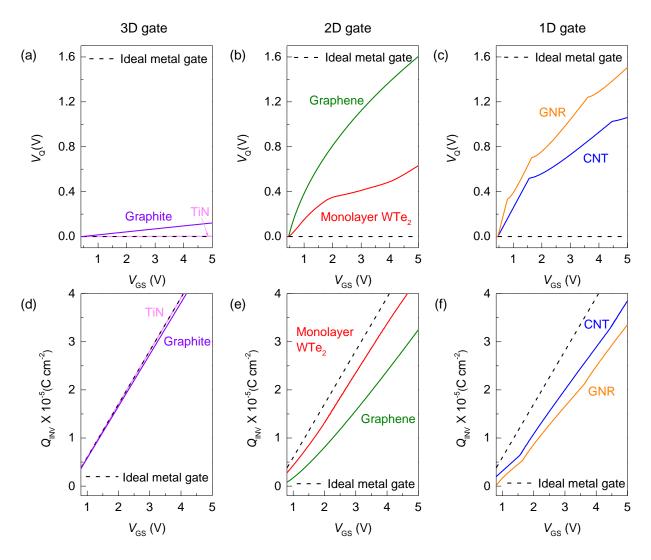

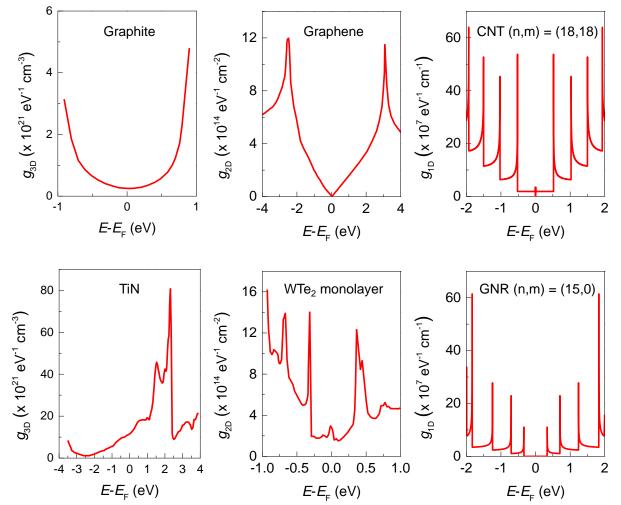

The concept of gate  $C_Q$  limited transistors is illustrated in figure 1a using the example of a bulk silicon channel MOSFET with gate electrodes of varying dimensionality. Figure 1b shows the DOS for the specific case of carbon based gates; graphite for 3D, graphene for 2D and carbon nanotube for 1D gate <sup>13-15</sup>. In a MOSFET with a bulk 3D gate, the gate DOS is very large and thus it can accommodate any  $Q_G$  needed to support an equal and opposite charge in the channel ( $Q_{CH} = Q_{INV} + Q_{DEP}$ ), where  $Q_{INV}$  and  $Q_{DEP}$  are the inversion and depletion charge densities respectively. As the dimensionality of the gate and the physical size reduces, the gate DOS is limited and in this case  $V_Q$  is related to  $Q_G$  by equation 1<sup>8,10</sup>.

$$Q_{\rm G} = \int_0^{V_{\rm Q}} C_{\rm Q} (V') \mathrm{d} V' \dots (1)$$

Here  $C_Q$  represents the quantum capacitance of the gate and can be calculated using equation 2.

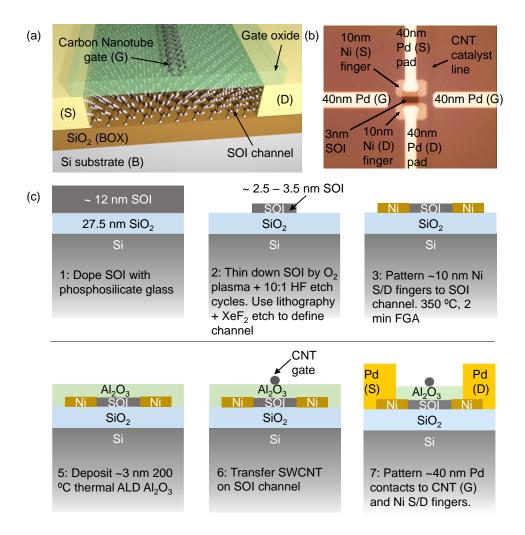

**Figure 1: Gate quantum capacitance effects in nanoscale transistors:** (a) Schematic of a bulk Si MOSFET and (b) the density of states for 3D (graphite, h = 100 nm), 2D (graphene) and 1D (CNT (n,m) = (18,18)) gate

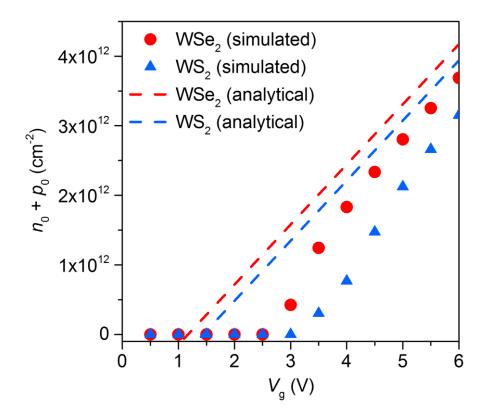

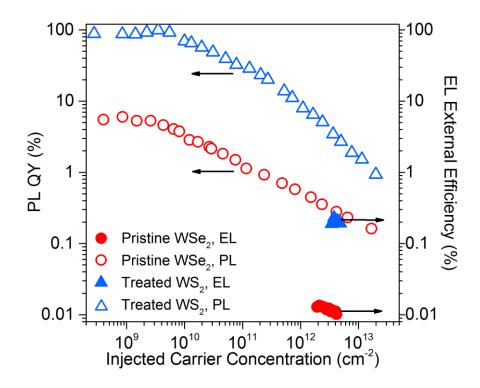

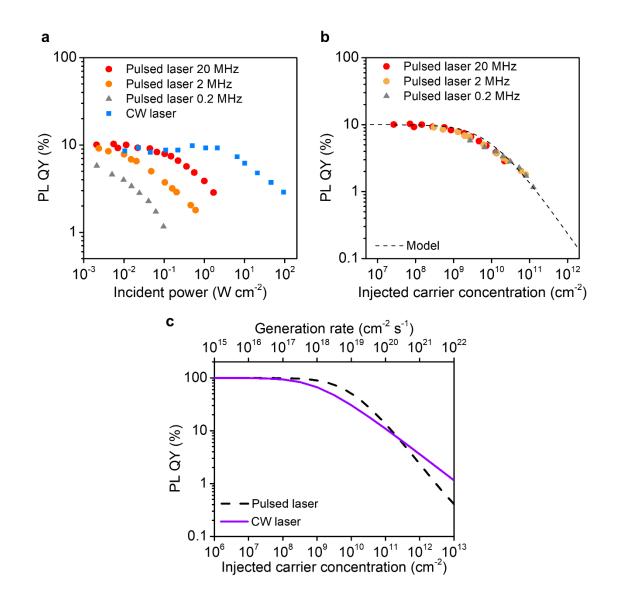

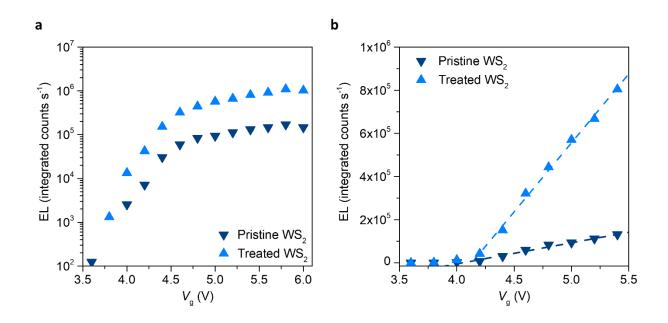

**Figure 2: Equivalent model and energy band diagram:** (a) Capacitance model for bulk Si MOSFET considering quantum capacitance of the gate electrode. (b) Energy band diagram showing the different model parameters