## UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

Design Techniques for High-Frequency CMOS Integrated Circuits: From 10 GHz To 100 GHz

**Permalink** https://escholarship.org/uc/item/5rc8t3j5

**Author** Deng, Zhiming

Publication Date 2010

Peer reviewed|Thesis/dissertation

# Design Techniques for High-Frequency CMOS Integrated Circuits: From 10 GHz To 100 GHz

by

Zhiming Deng

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Robert G. Meyer Professor Ming Gu

Fall 2010

# Design Techniques for High-Frequency CMOS Integrated Circuits: From 10 GHz To 100 GHz

Copyright 2010 by Zhiming Deng

#### Abstract

## Design Techniques for High-Frequency CMOS Integrated Circuits: From 10 GHz To $100 {\rm ~GHz}$

by

Zhiming Deng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

Technology developments have made CMOS a strong candidate in high-frequency applications because of its low power, low cost and higher-level integration. However, as an essential element in an RF building block, a CMOS device is not as good as a BJT device in terms of speed and a HEMT device in terms of noise performance. Therefore, conventional low-frequency design techniques for CMOS circuits may not satisfy the requirements for high-frequency applications wherein the operating frequencies get close to the cut-off frequency of a CMOS device. This research work explores design techniques for various high-frequency circuits at 10 GHz, 60 GHz and up to 110 GHz. Individual building blocks including low-noise amplifiers, voltage-controlled oscillators, high-frequency true-single-phase-clock frequency dividers, and mm-wave amplifiers are studied thoroughly using both theoretical analysis and practical circuit designs. Related fundamental techniques, such as MOS device modeling and de-embedding techniques, are also explored. Furthermore, as a prototype of systemlevel integration, a Ku-band LNB front-end is implemented for the application of a satellite receiver. To my parents

## Contents

| Lis      | st of | Figures                                                                                                                        | $\mathbf{V}$ |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------|--------------|

| Lis      | st of | Tables                                                                                                                         | x            |

| Ι        | In    | troduction                                                                                                                     | 1            |

| II       | Н     | ligh-Frequency RFIC Designs                                                                                                    | 3            |

| 1        |       | the Noise Optimization of CMOS Common-Source Low-Noise                                                                         |              |

|          |       | plifiers                                                                                                                       | 4            |

|          | 1.1   | Introduction                                                                                                                   | 4            |

|          | 1.2   | General Design Considerations for CS LNAs                                                                                      | 6            |

|          |       | 1.2.1 Descriptions of Modeling                                                                                                 | 6            |

|          |       | 1.2.2 The Selection of Design Variables                                                                                        | 11           |

|          |       | 1.2.3 Components for Power Matching                                                                                            | 11           |

|          | 1.0   | 1.2.4 Design Constraints                                                                                                       | 12           |

|          | 1.3   | The Noise Optimization Techniques                                                                                              | 14           |

|          |       | 1.3.1 Noise Factors of CS LNAs                                                                                                 | 14           |

|          |       | 1.3.2 Internal Noise Sources                                                                                                   | 16           |

|          | 1 4   | 1.3.3 Optimizations of Noise Factors                                                                                           | 17           |

|          | 1.4   | $Conclusion \dots \dots$ | 35           |

|          | 1.5   | Definitions of Variables                                                                                                       | 36           |

|          | 1.6   | Physical Constants                                                                                                             | 36           |

|          | 1.7   | Theorems about NF Optimizations                                                                                                | 38<br>39     |

|          | 1.8   | Expressions in Noise Factor Formulation                                                                                        | 39           |

| <b>2</b> | A C   | CMOS Ku-Band Single-Conversion Low-Noise Block Front-End                                                                       |              |

|          | for   | Satellite Receivers                                                                                                            | <b>42</b>    |

|          | 2.1   | Introduction                                                                                                                   | 42           |

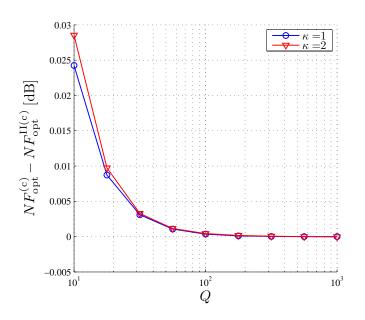

|          | 2.2   | Front-End Architecture                                                                                                         | 43           |

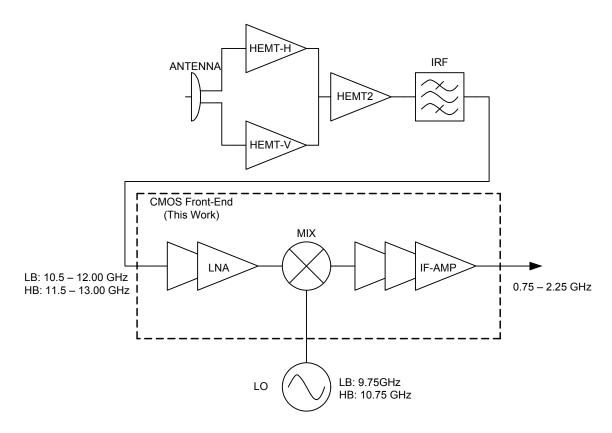

|   | 2.3 | Low-Noise Amplifier                                       | 45 |

|---|-----|-----------------------------------------------------------|----|

|   | 2.4 | Mixer and IF-Amplifier                                    | 47 |

|   | 2.5 | Experimental Results                                      | 49 |

|   | 2.6 | Conclusion                                                | 52 |

| 3 | ΔΔ  | -Port-Inductor-Based VCO Coupling Method for Phase Noise  |    |

| 0 |     | luction                                                   | 53 |

|   | 3.1 | Introduction                                              | 53 |

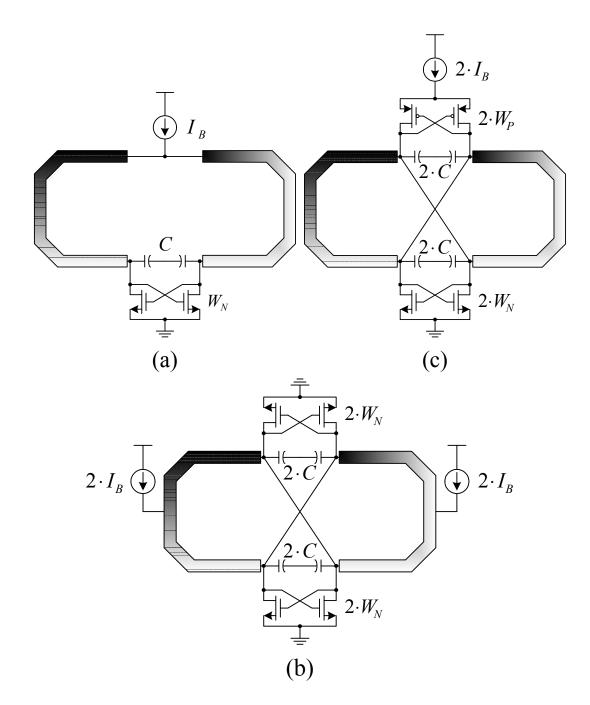

|   | 3.2 | VCO Circuit Designs                                       | 54 |

|   | -   | 3.2.1 4-Port Inductor                                     | 54 |

|   |     | 3.2.2 Interlocked-Ring Structure                          | 55 |

|   |     | 3.2.3 $LC$ Tank                                           | 55 |

|   |     | 3.2.4 VCO Topologies                                      | 57 |

|   | 3.3 | Experimental Results                                      | 58 |

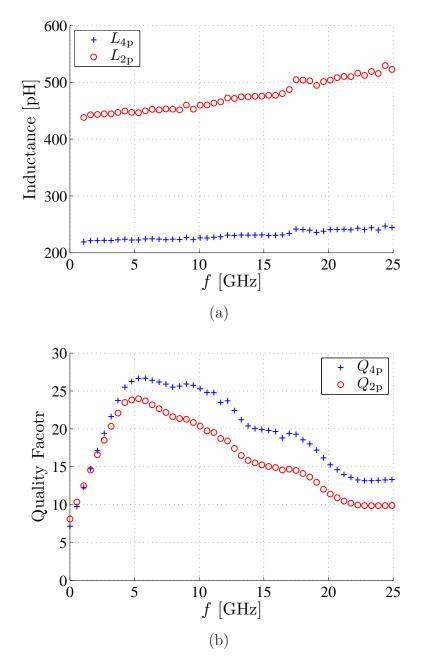

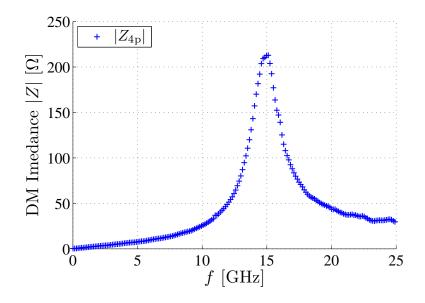

|   |     | 3.3.1 Passive Structures                                  | 58 |

|   |     | 3.3.2 Prototype VCOs                                      | 58 |

|   | 3.4 | Conclusion                                                | 65 |

| 4 | Des | ign of CMOS True-Single-Phase-Clock Dividers Based on the |    |

|   |     | ed-Power Trade-Off                                        | 66 |

|   | 4.1 | Introduction                                              | 66 |

|   | 4.2 | Basic TSPC Logic Family                                   | 67 |

|   | 4.3 | TSPC Dividers and Prescalers                              | 69 |

|   |     | 4.3.1 Ratioless Divide-by-2 Divider                       | 69 |

|   |     | 4.3.2 Ratioed Divide-by-2 Divider                         | 73 |

|   |     | 4.3.3 Divide-by-2/3 Prescaler                             | 76 |

|   | 4.4 | Experimental Results                                      | 76 |

|   | 4.5 | Conclusion                                                | 82 |

|   | 4.6 | TSPC Logic Truth Table                                    | 82 |

|   |     |                                                           |    |

## III CMOS mm-Wave Techniques

| <b>5</b> | A L  | ayout-Based Optimal Neutralization Technique for mm-Wave | <b>)</b> |

|----------|------|----------------------------------------------------------|----------|

|          | Diff | erential Amplifiers                                      | 88       |

|          | 5.1  | Introduction                                             | 88       |

|          | 5.2  | Neutralization Technique                                 | 89       |

|          | 5.3  | Design Approach                                          | 91       |

|          | 5.4  | Experimental Results                                     | 94       |

|          | 5.5  | Conclusion                                               | 96       |

87

| 6 | The | e "Load-Thru" (LT) De-embedding Technique for the Measure- |     |

|---|-----|------------------------------------------------------------|-----|

|   | mer | nts of mm-Wave Balanced 4-Port Devices                     | 99  |

|   | 6.1 | Introduction                                               | 99  |

|   | 6.2 | De-embedding Theory                                        | 00  |

|   |     | 6.2.1 DM and CM Separation                                 | .00 |

|   |     | 6.2.2 De-embedding Formula                                 | 02  |

|   |     | 6.2.3 Characterization of the Balun                        | .03 |

|   |     | 6.2.4 Characterization of $Z_T$                            | 04  |

|   | 6.3 | Design Consideration                                       | 05  |

|   | 6.4 | Measurement Verification                                   | 07  |

|   | 6.5 | Conclusion                                                 | .07 |

|   |     |                                                            |     |

|   |     |                                                            |     |

## IV Conclusion

| Bibliography |

|--------------|

|--------------|

iv

110

112

# List of Figures

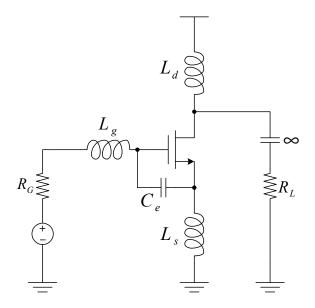

| 1.1 | The schematics of an inductively degenerated common-source LNA                                                                                |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | with an external gate-source capacitor. Both the source impedance                                                                             |    |

|     | and the load impedance are real                                                                                                               | 5  |

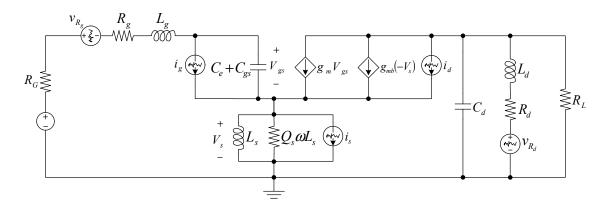

| 1.2 | The small signal model of a CS LNA including noise sources                                                                                    | 6  |

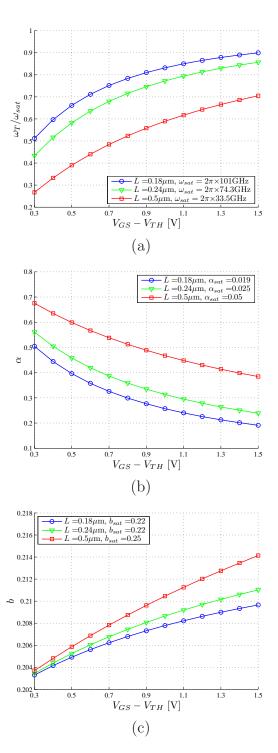

| 1.3 | The dependence of the MOSFET model parameters (a) normalized $\omega_T$ ,                                                                     |    |

|     | (b) $\alpha$ and (c) b on the bias voltage. The transistor channel lengths are                                                                |    |

|     | $L = 0.18 \ \mu \text{m}, \ L = 0.24 \ \mu \text{m} \text{ and } L = 0.5 \ \mu \text{m}.$                                                     | 10 |

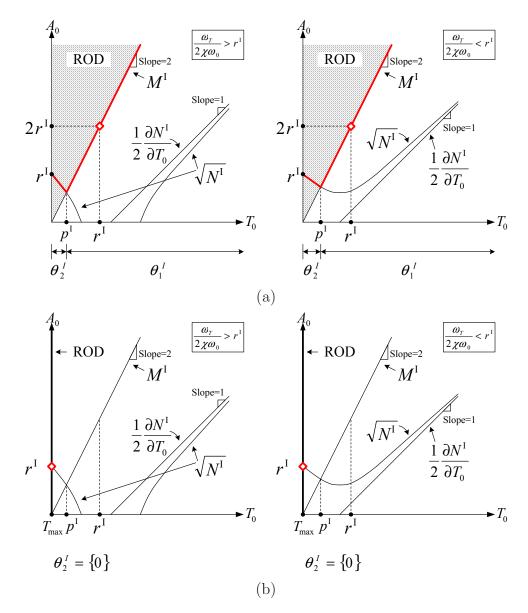

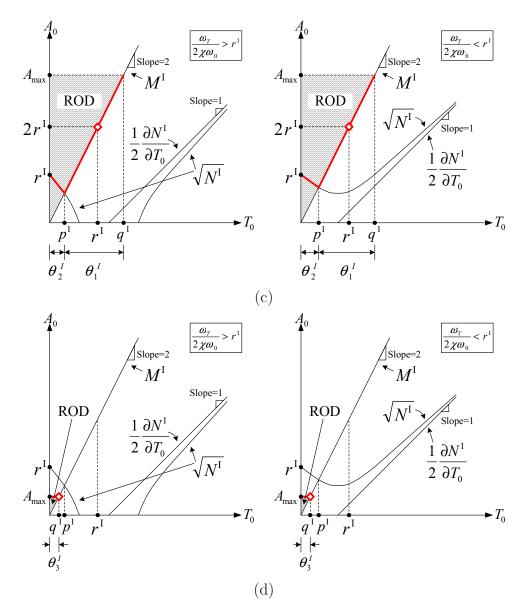

| 1.4 | The RODs and optimization results of the simple cases $(Q_{L_q} = Q_s =$                                                                      |    |

|     | $Q_{L_d} = \infty, \ b = 0$ with the assumptions (a) $A_{\text{max}} = \infty, T_{\text{max}} = \infty$ ,                                     |    |

|     | (b) $A_{\max} = \infty, T_{\max} = 0$ , (c) $A_{\max} > 2r^{I}, T_{\max} = \infty$ , (d) $A_{\max} < 0$                                       |    |

|     | $2r^{\rm I}, T_{\rm max} = \infty$ . In each case, two sub-plots are generated corresponding                                                  |    |

|     | to the condition $\frac{\omega_T}{2\chi\omega_0} > r^{\rm I}$ and $\frac{\omega_T}{2\chi\omega_0} < r^{\rm I}$ respectively. A solid line "—" |    |

|     | with high weight is the trace of the conditional optimum $\widehat{A}_0^{\mathrm{I}}$ for each                                                |    |

|     | $T_0$ . A " $\diamond$ " denotes the optimal design $\{A_{opt}^{I}, T_{opt}^{I}\}$ in an ROD                                                  | 20 |

| 1.4 | (Continued). $\ldots$                                        | 21 |

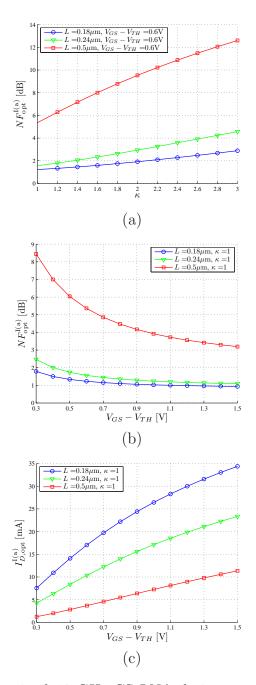

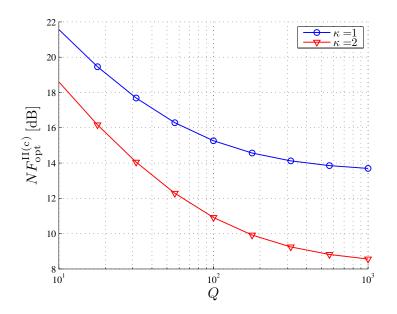

| 1.5 | An unconstrained 10 GHz CS LNA design uses ideal inductors ( $Q_{L_q} =$                                                                      |    |

|     | $Q_s = Q_{L_d} = \infty$ ) and ignores $g_{mb}$ $(b = 0)$ . (a) The optimal noise figure                                                      |    |

|     | varies with the capacitance ratio $\kappa$ ( $V_{GS} - V_{TH} = 0.6$ V). (b) The                                                              |    |

|     | optimal noise figure varies with the bias voltage $V_{GS}$ ( $\kappa = 1$ ). (c) The                                                          |    |

|     | drain current at the optimal design varies with the bias voltage $V_{GS}$                                                                     |    |

|     | $(\kappa = 1)$ . The channel lengths are $L = 0.18 \ \mu m$ , $L = 0.24 \ \mu m$ and                                                          |    |

|     | $L = 0.5 \ \mu \mathrm{m}$ respectively.                                                                                                      | 23 |

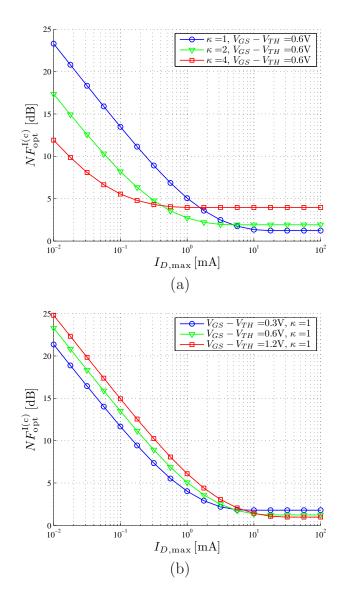

| 1.6 | An $I_D$ -Constrained 10 GHz CS LNA design uses ideal inductors ( $Q_{L_q} =$                                                                 |    |

|     | $Q_s = Q_{L_d} = \infty$ ) and ignores $g_{mb}$ $(b = 0)$ . The optimal noise figure                                                          |    |

|     | varies with $I_{D,\max}$ for (a) different $\kappa$ and (b) different $V_{GS}$ . The device                                                   |    |

|     | channel length is $L = 0.18 \ \mu \text{m}.$                                                                                                  | 26 |

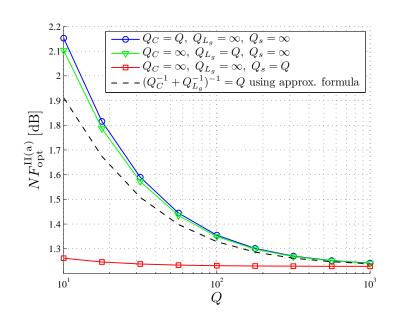

| 1.7  | The optimal noise figure varies with different combinations of $Q_C$ , $Q_{L_g}$<br>and $Q_s$ in an unconstrained 10 GHz LNA design. The results are<br>also compared to the approximate value calculated from (1.105). The<br>capacitance ratio is fixed at $\kappa = 1$ . We assume ideal inductor $L_d$ and<br>improve $\kappa$ . The bigs culture is set $V_{const} = 0.6$ N. The deviae |          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.8  | ignore $g_{mb}$ . The bias voltage is set $V_{GS} - V_{TH} = 0.6$ V. The device<br>channel length is $L = 0.18 \ \mu\text{m}$                                                                                                                                                                                                                                                                | 30       |

| 1.9  | channel length is $L = 0.18 \ \mu \text{m}$                                                                                                                                                                                                                                                                                                                                                  | 32       |

| 1.10 | 1.7. The perturbation is computed using $(1.122)$                                                                                                                                                                                                                                                                                                                                            | 35<br>36 |

| 2.1  | The architecture of a Ku-band LNB down-converter.                                                                                                                                                                                                                                                                                                                                            | 43       |

| 2.2  | The two-stage LNA.                                                                                                                                                                                                                                                                                                                                                                           | 44       |

| 2.3  | The noise model of a cs amplifier with inductive degeneration                                                                                                                                                                                                                                                                                                                                | 46       |

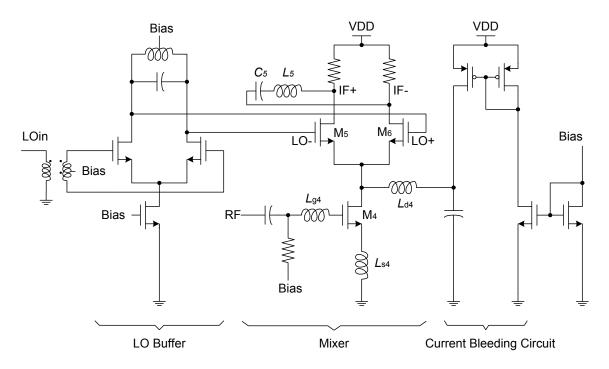

| 2.4  | The single-balanced mixer with the LO buffer                                                                                                                                                                                                                                                                                                                                                 | 47       |

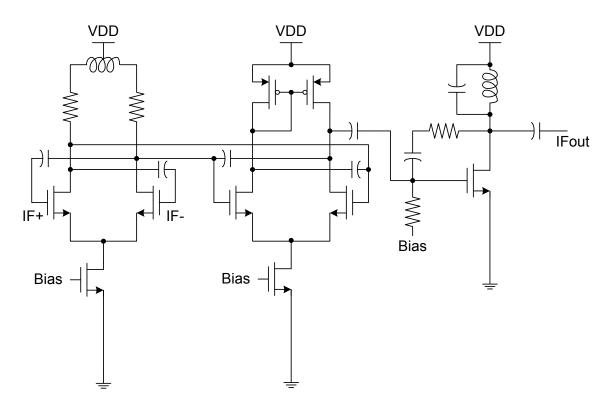

| 2.5  | The three-stage IF amplifier                                                                                                                                                                                                                                                                                                                                                                 | 48       |

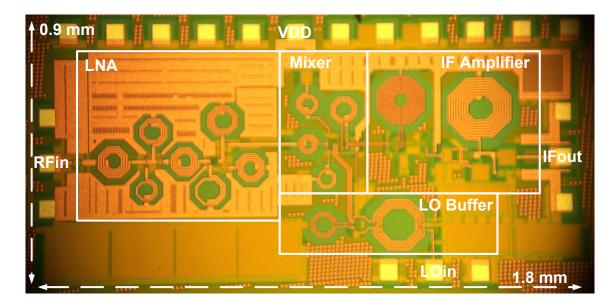

| 2.6  | The chip microphotograph of the front-end.                                                                                                                                                                                                                                                                                                                                                   | 49       |

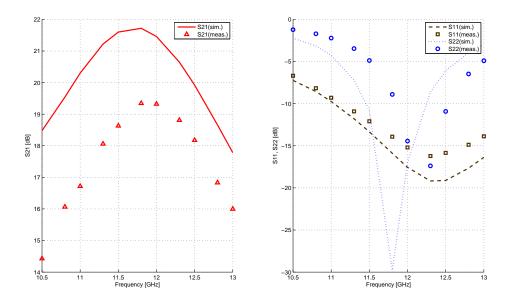

| 2.7  | Measured S-parameters of the stand-alone LNA                                                                                                                                                                                                                                                                                                                                                 | 50       |

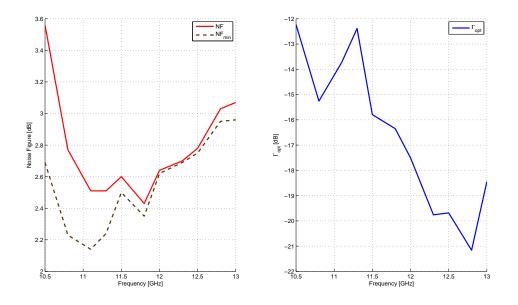

| 2.8  | Measured noise parameters of the stand-alone LNA                                                                                                                                                                                                                                                                                                                                             | 51       |

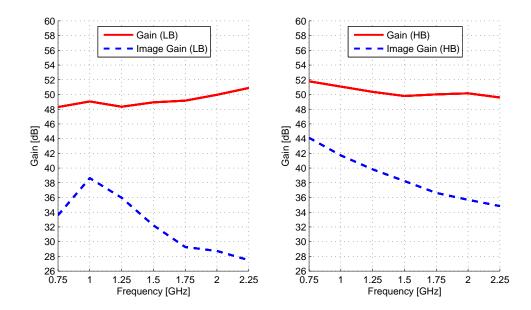

| 2.9  | Front-end conversion gain for the RF band and the image band (LB                                                                                                                                                                                                                                                                                                                             |          |

|      | and HB respectively) versus IF frequencies                                                                                                                                                                                                                                                                                                                                                   | 51       |

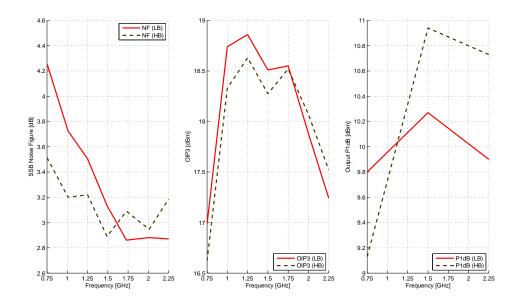

| 2.10 | Front-end SSB NF, OIP3 and output P1dB (LB and HB respectively)                                                                                                                                                                                                                                                                                                                              |          |

|      | versus IF frequencies                                                                                                                                                                                                                                                                                                                                                                        | 52       |

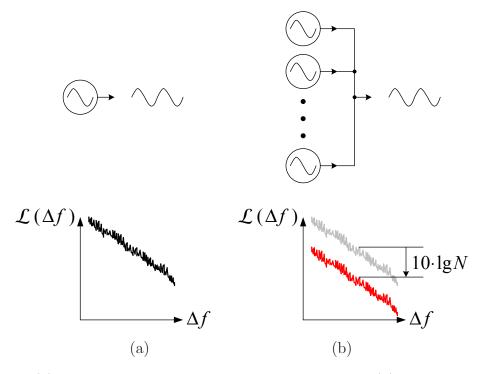

| 3.1  | (a) A stand-alone VCO and its phase noise plot. (b) $N$ equal VCOs are coupled by connecting their outputs together. The output voltage waveform is the same as that of a single VCO but the phase noise is                                                                                                                                                                                  |          |

| 3.2  | reduced by $10 \cdot \lg N$ (dB)                                                                                                                                                                                                                                                                                                                                                             | 54       |

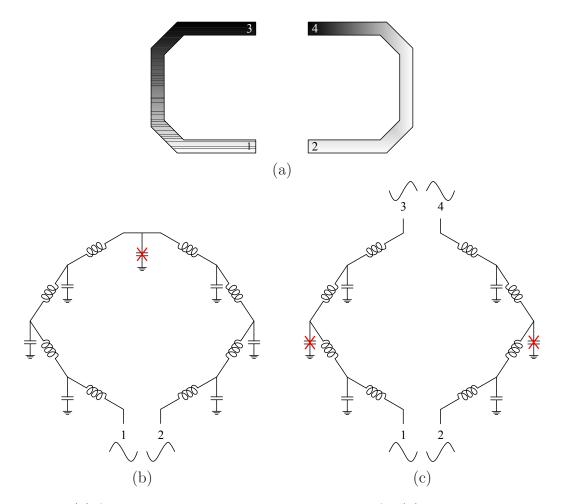

| 9.6  | port 2 and 3 in phase.                                                                                                                                                                                                                                                                                                                                                                       | 56       |

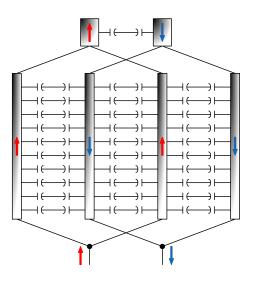

| 3.3  | A 5-bit (31-unit) coarse tuning capacitor array is connected in the                                                                                                                                                                                                                                                                                                                          |          |

|      | interlocked-ring structure. The current directions are shown by the                                                                                                                                                                                                                                                                                                                          |          |

| 0.4  | $arrows. \dots \dots$                                                                                                                                                                                                                                                                  | 57       |

| 3.4  | (a) A 2-port $LC$ tank. (b) A cross-coupled 4-port $LC$ tank                                                                                                                                                                                                                                                                                                                                 | 58       |

| 3.5          | The schematics of three VCO topologies: (a) NVCO, (b) NCVCO and (c) CCVCO. In these plots, the interlocked-ring structures of capacitor                                                                          |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.0          | arrays have been simplified.                                                                                                                                                                                     |

| 3.6          | The measured DM 2-port and 4-port characteristics of a 4-port induc-<br>tor: (a) the inductances and (b) the quality factors                                                                                     |

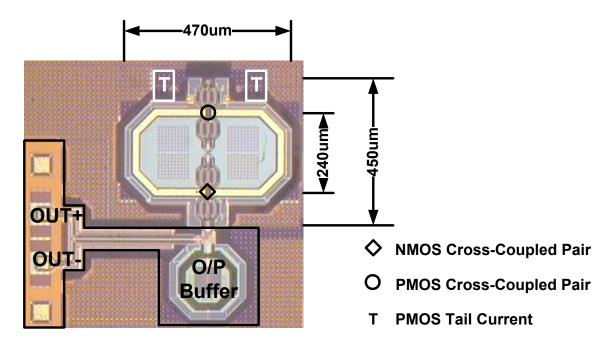

| $3.7 \\ 3.8$ | The measured DM impedance of a cross-coupled 4-port $LC$ tank The chip micrograph of the CCVCO design with the output buffer included                                                                            |

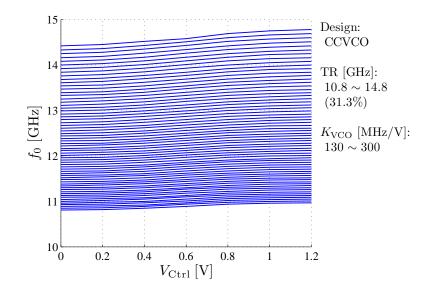

| 3.9          | The measured frequency tuning range of the CCVCO design with 6-bit coarse tuning control.                                                                                                                        |

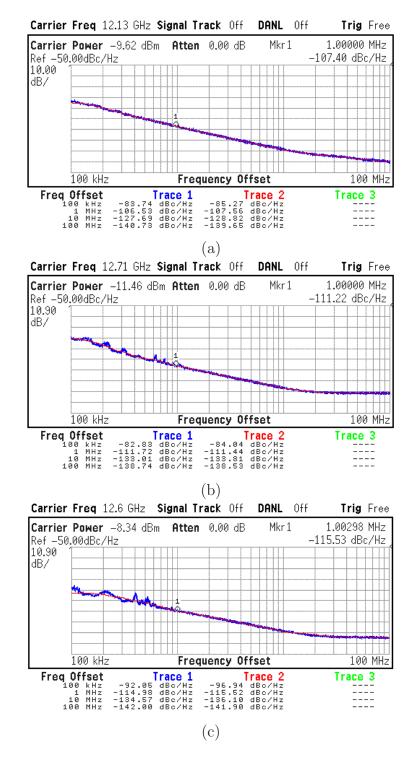

| 3.10         | The measured phase noise of the three VCO designs: (a) NVCO, (b) NCVCO and (c) CCVCO. Their coarse tuning control codes are all set to 0x1F.                                                                     |

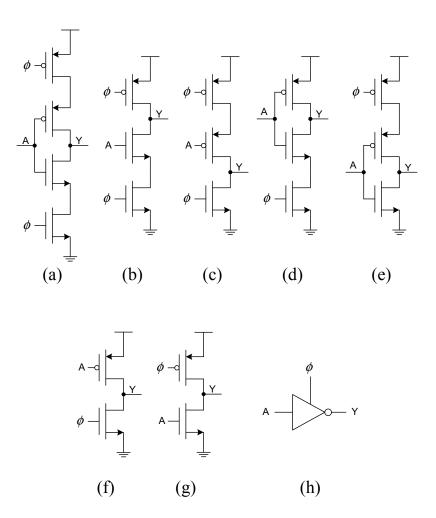

| 4.1          | The family of CMOS TSPC logic gates. Ratioless types: (a) CC, (b) CN, (c) CP, (d) NC and (e) PC. Ratioed types: (f) NP and (g) PN. A                                                                             |

| 4.9          | general symbol (h).                                                                                                                                                                                              |

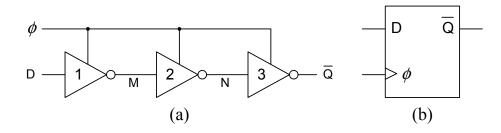

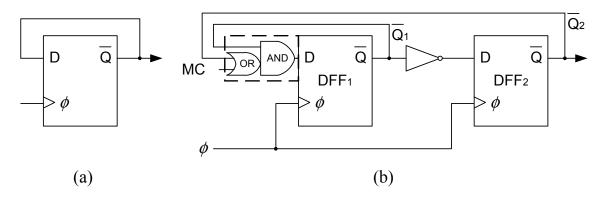

| 4.2          | <ul><li>(a) A three-stage edge-triggered TSPC DFF and (b) its symbol.</li><li>(a) A TSPC divide-by-2 divider. (b) A TSPC divide-by-2/3 prescaler.</li></ul>                                                      |

| 4.3          | The divider is 2 when $MC = 1$ and is 3 when $MC = 0$ .                                                                                                                                                          |

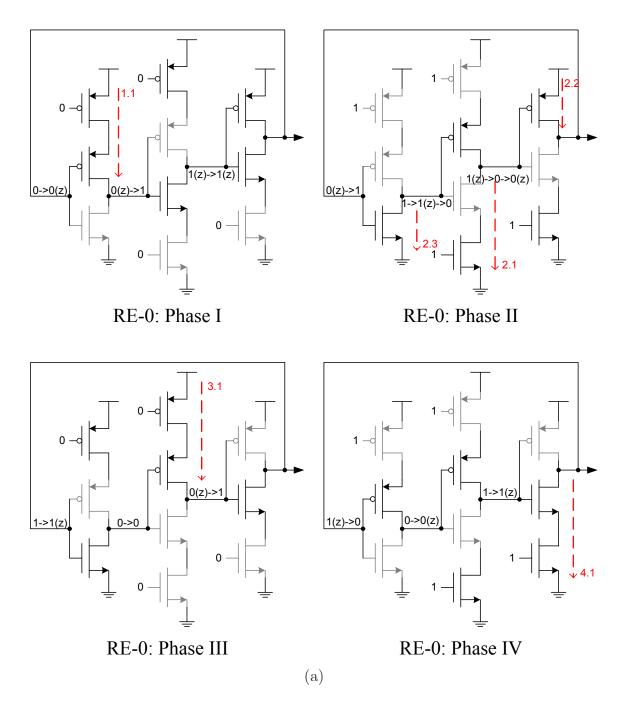

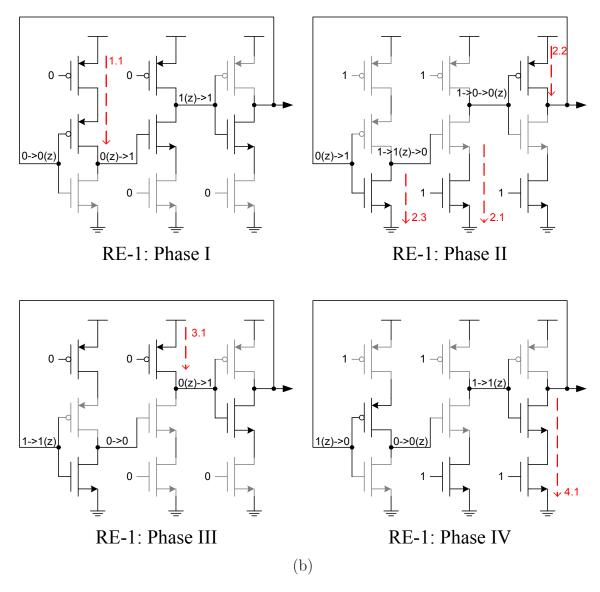

| 4.4          | The 4-phase divide-by-2 operation of two types of ratioless TSPC dividers: (a) RE-0 (PC-CC-NC) and (b) RE-1 (PC-CN-NC). The turned-                                                                              |

| 4.4          | off transistors are depicted in gray.                                                                                                                                                                            |

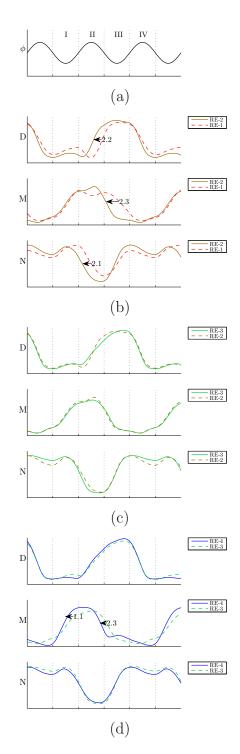

| 4.5          | Comparisons of simulated nodal waveforms of different types of di-<br>viders. (a) Input clock signal (four phases). (b) RE-2 versus RE-1. (c)<br>RE-3 versus RE-2. (d) RE-4 versus RE-3.                         |

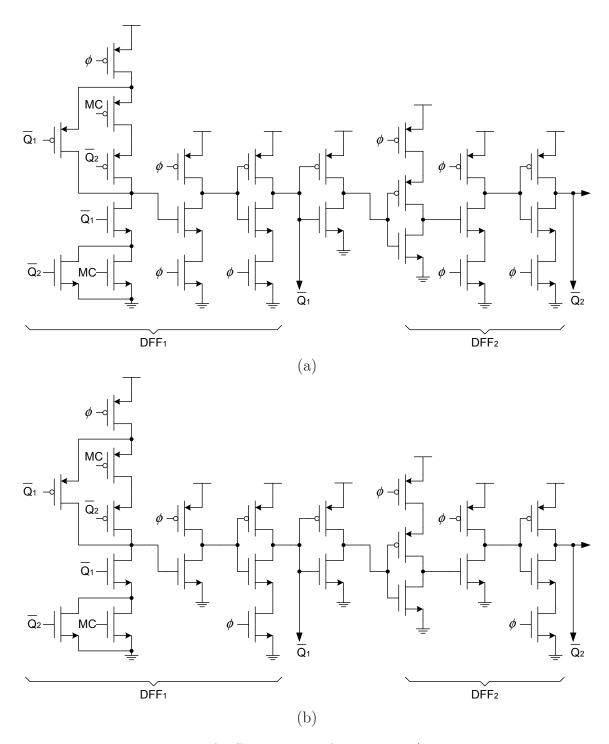

| 4.6          | The schematics of different types of divide-by-2/3 prescalers. The ra-                                                                                                                                           |

| 1.0          | tioless type: (a) RE-1 and the ratioed types: (b) RE-2, (c) RE-3 and                                                                                                                                             |

| 16           | (d) RE-4                                                                                                                                                                                                         |

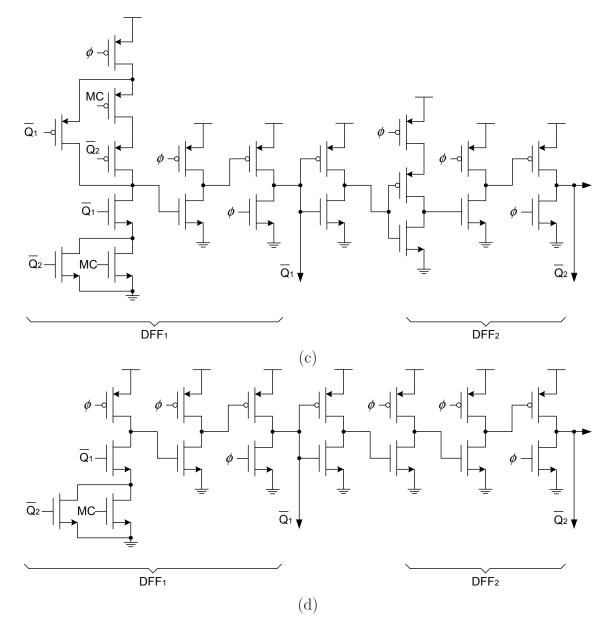

| $4.6 \\ 4.7$ |                                                                                                                                                                                                                  |

| 4.1          | (b) The micrograph of a test chip. Pads for the supply and the mode control "MC" are not shown                                                                                                                   |

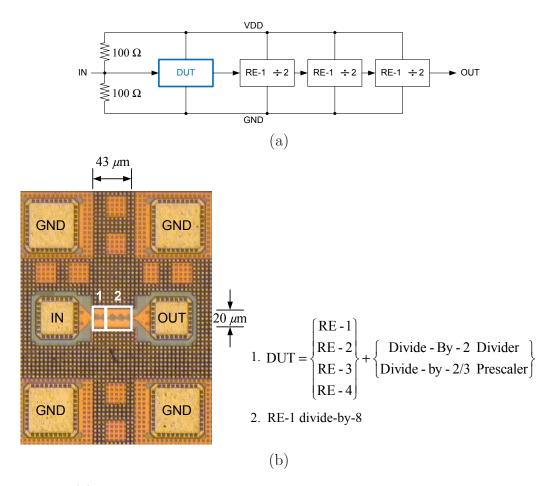

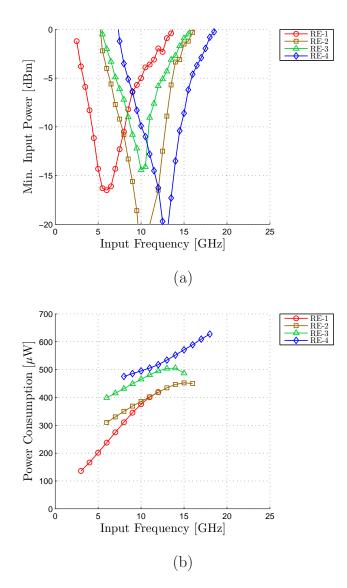

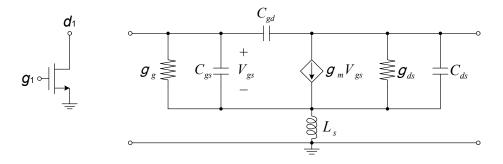

| 4.8          | The measurement results of various types of divide-by-2 dividers. (a)                                                                                                                                            |

|              | Input sensitivity curves. (b) Power consumption with input power of 0 dBm                                                                                                                                        |

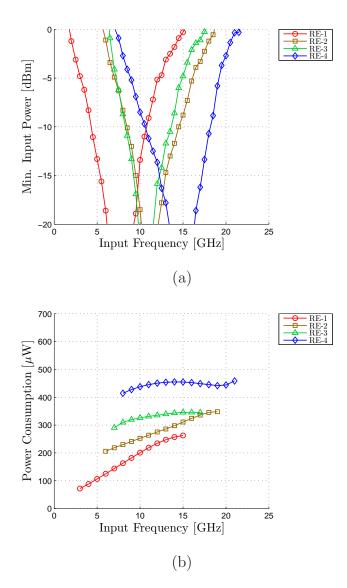

| 4.9          | The measurement results of various types of divide-by-2/3 prescalers.                                                                                                                                            |

| 1.0          | (a) Input sensitivity curves and (b) power consumption for the divide-<br>by-2 operation (MC=1). (c) Input sensitivity curves and (d) power<br>consumption for the divide-by-3 operation (MC=0). The input power |

|              | is set to 0 dBm for power consumption measurements                                                                                                                                                               |

vii

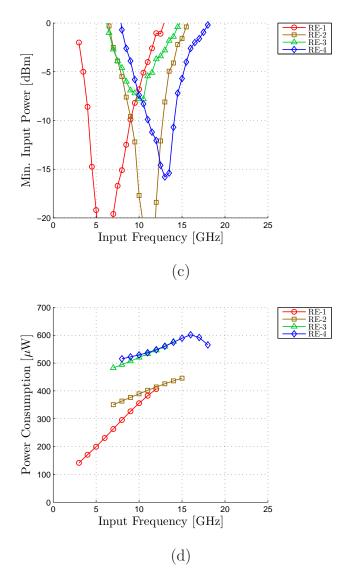

| 4.9<br>4.10         | (Continued)<br>The measured output waveforms of the RE-4 divide-by-2/3 prescaler, further divided by 8, with an input frequency of 18 GHz in (a) the divide-by-2 mode (MC=1, $f_{out}=18/16=1.125$ GHz) and (b) the divide-by-3 mode (MC=0, $f_{out}=18/24=0.75$ GHz). | 84<br>85                                  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

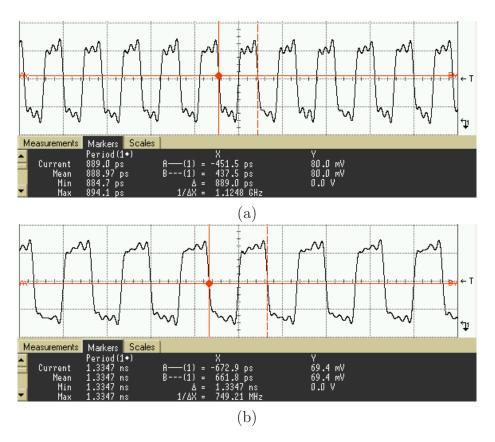

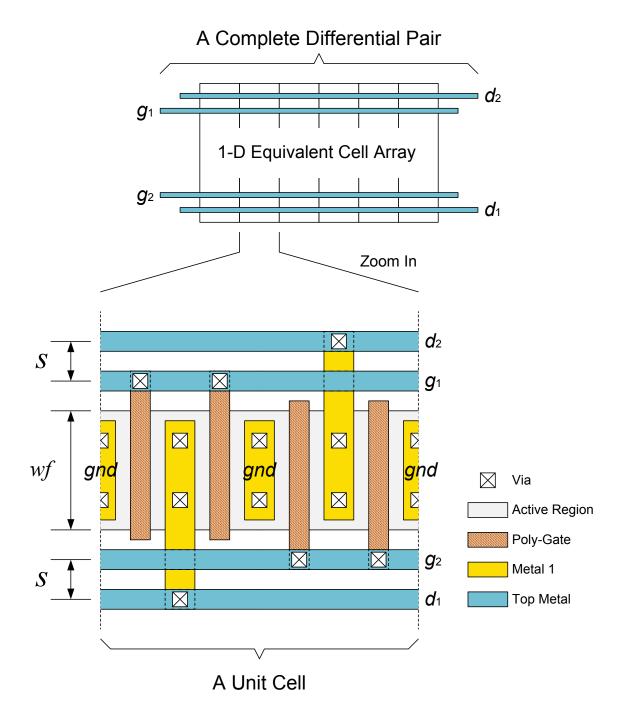

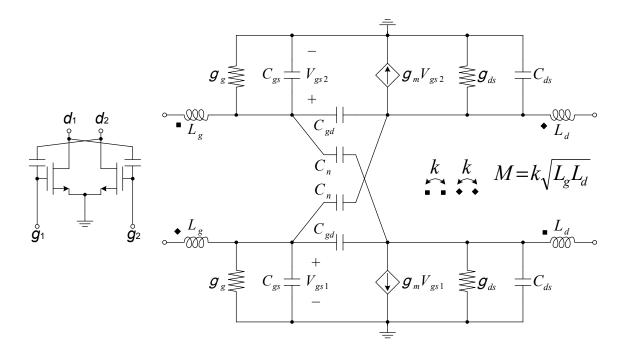

| $5.1 \\ 5.2 \\ 5.3$ | The single-ended configuration and its small-signal model A simplified diagram of the interdigital layout of a differential pair The differential-mode small-signal model of the proposed layout struc-                                                                | 89<br>92                                  |

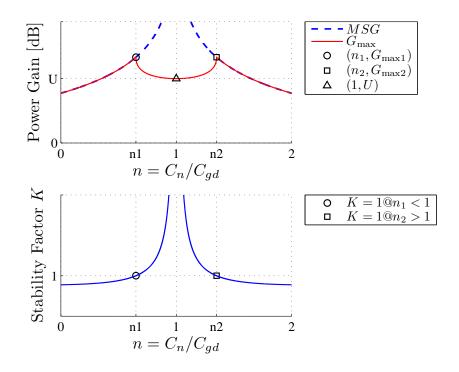

| 5.4                 | ture in Fig. 5.2                                                                                                                                                                                                                                                       | 93                                        |

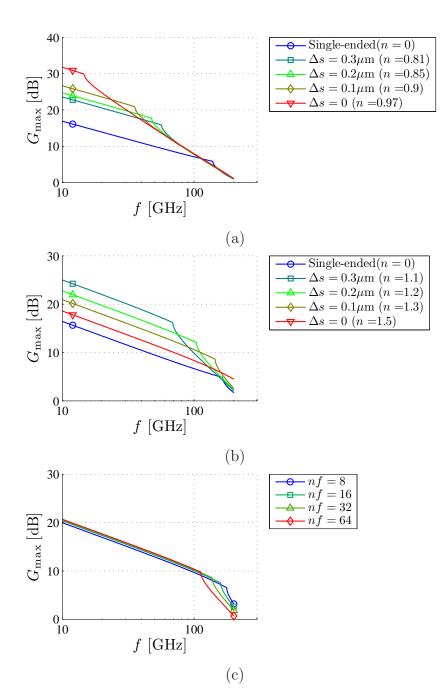

| 5.5                 | itor $C_n$ (Mutual inductance $M$ ignored)                                                                                                                                                                                                                             | 93                                        |

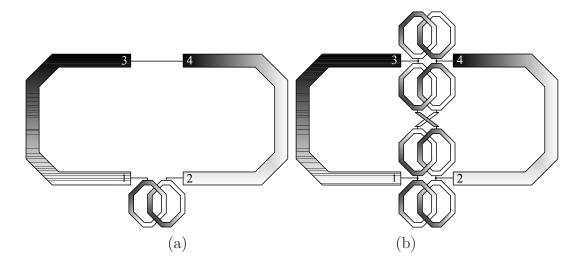

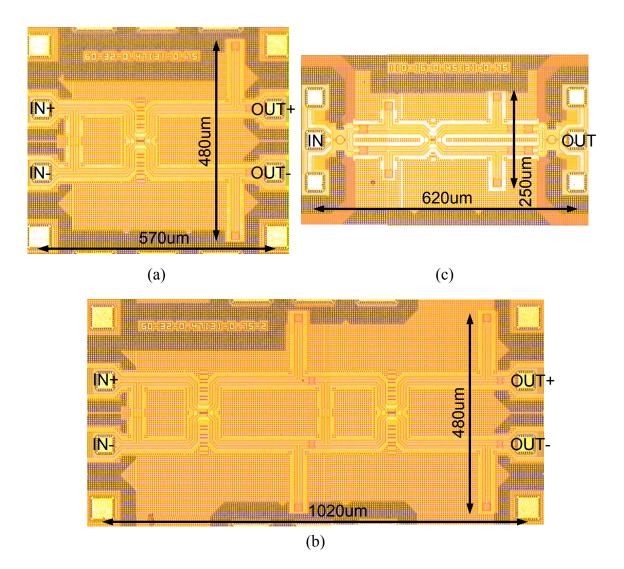

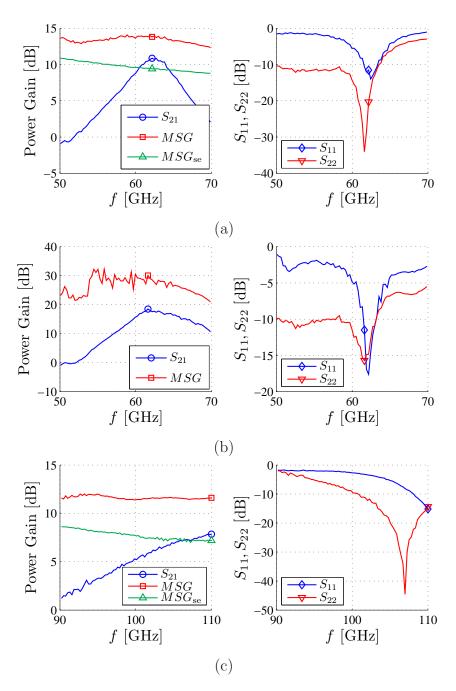

| 5.6                 | process                                                                                                                                                                                                                                                                | 95                                        |

| 5.7                 | GHz two-stage amplifier and (c) a 110 GHz single-stage amplifier with<br>on-chip baluns for de-embedding                                                                                                                                                               | 97<br>98                                  |

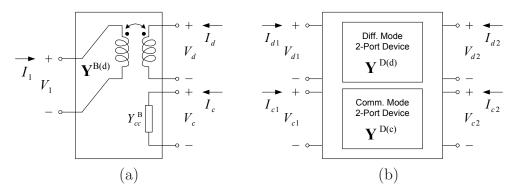

| 6.1                 | The mixed-mode models of (a) an ideal balun and (b) a balanced 4-port device.                                                                                                                                                                                          | 101                                       |

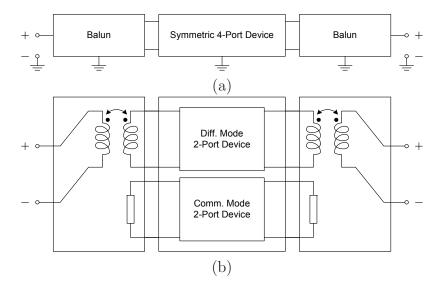

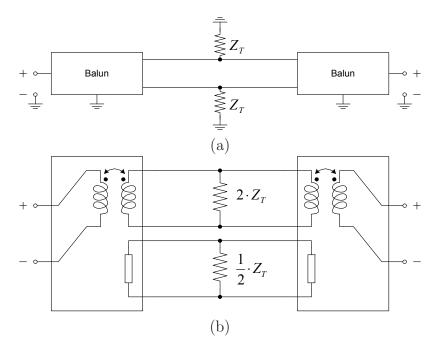

| 6.2                 | (a) The measurement setup of a symmetric 4-port device using ideal baluns. (b) The equivalent mixed-mode model of the setup                                                                                                                                            | 103                                       |

| 6.3                 | (a) The measurement setup of two back-to-back baluns with termina-<br>tion loads $Z_T$ in the middle. (b) The equivalent mixed-mode model of                                                                                                                           |                                           |

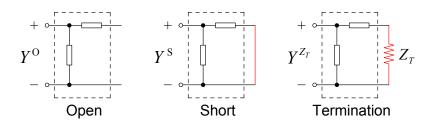

| 6.4                 | the setup                                                                                                                                                                                                                                                              | 104                                       |

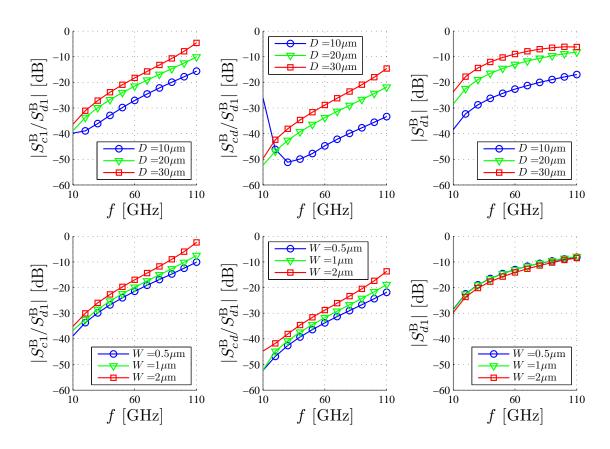

| 6.5                 | sitics are depicted inside the dashed-line box                                                                                                                                                                                                                         | $\begin{array}{c} 105 \\ 106 \end{array}$ |

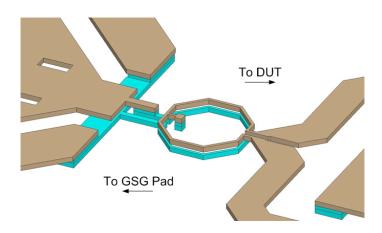

| 6.6                 | The 3-D balun structure                                                                                                                                                                                                                                                | 106                                       |

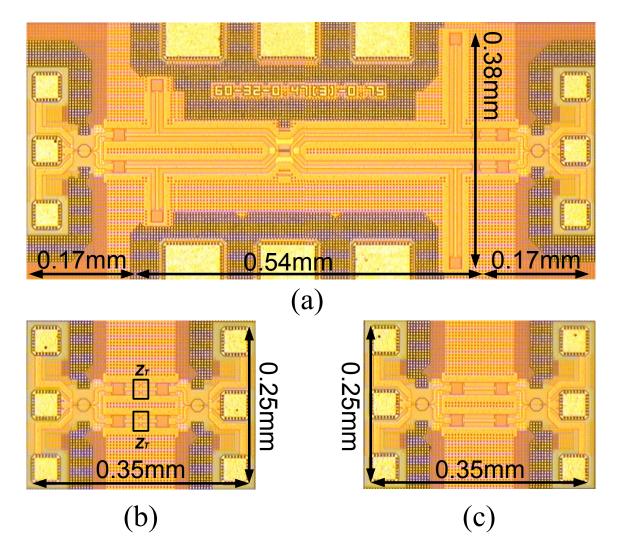

| The micrograph of (a) the 60 GHz differential amplifier with input                                        |                                                                                                    |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| and output baluns, (b) the "load" de-embedding structure and (c) the                                      |                                                                                                    |

| "thru" de-embedding structure                                                                             | 108                                                                                                |

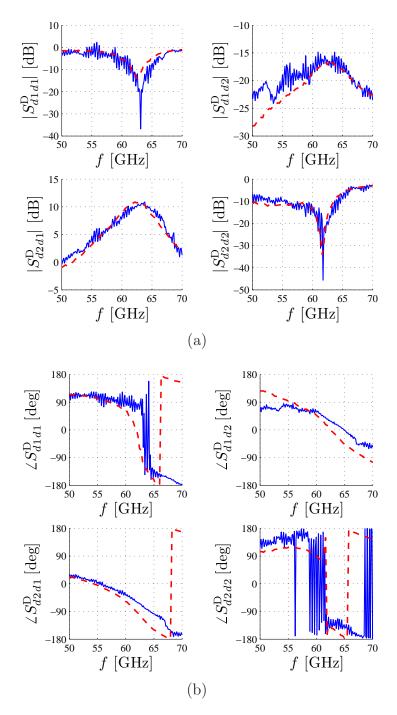

| The de-embedded differential-mode S-parameters of a differential am-                                      |                                                                                                    |

| plifier using the LT method (solid line) are compared with the directly                                   |                                                                                                    |

| measured data by using a balun probe (dashed line). (a) Magnitudes                                        |                                                                                                    |

| and (b) phases. $\ldots$ | 109                                                                                                |

|                                                                                                           | and output baluns, (b) the "load" de-embedding structure and (c) the "thru" de-embedding structure |

## List of Tables

| The $H$ -NTFs of the Equivalent Circuit of a CS LNA                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Formula to Compute $\frac{dF_{\text{opt}}}{db}\Big _{b=0}$                      | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Major Variables                                                                 | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Physical Constants                                                              | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Virtual CMOS Process Constants                                                  | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Intrinsic Noise Parameters                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Expressions about $\overline{ U ^2}$ , $\overline{ E ^2}$ and $\overline{UE^*}$ | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Expressions for the Calculation of $(1.122)$ , $(1.123)$ and $(1.126)$ .        | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Comparison of integrated LNB front-end performance                                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCO Performance Summary and Comparison                                              | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Four Types of 3-Stage Ratioless DFFs                                                | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Signal Transition in the 4-Phase Divide-by-2 Operation of a Rising-             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Edge-Triggered Divider                                                              | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                     | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The Truth Table of the TSPC Logics                                                  | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                     | The Formula to Compute $\frac{dF_{opt}}{db}\Big _{b=0}$<br>The Major Variables<br>The Physical Constants<br>The Physical Constants<br>The Virtual CMOS Process Constants<br>The Intrinsic Noise Parameters<br>The Intrinsic Noise Parameters<br>The Expressions about $\overline{ U ^2}$ , $\overline{ E ^2}$ and $\overline{UE^*}$<br>The Expressions for the Calculation of (1.122), (1.123) and (1.126)<br>Comparison of integrated LNB front-end performance<br>VCO Performance Summary and Comparison<br>Four Types of 3-Stage Ratioless DFFs<br>The Signal Transition in the 4-Phase Divide-by-2 Operation of a Rising-<br>Edge-Triggered Divider<br>Three Types of 3-Stage Ratioed DFFs |

#### Acknowledgments

I would like to express my deep and sincere gratitude to my research advisor, Professor Ali M. Niknejad, Professor of the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley. His wide knowledge and his logical way of thinking have been of great value for me. His understanding, encouraging and personal guidance have provided a good basis for the present dissertation.

I would also like to acknowledge Professor Robert G. Meyer, Professor Elad Alon, Professor Seth Sanders, Professors of the Department of Electrical Engineering and Computer Sciences, and Professor Ming Gu, Professor of the Department of Math, all from University of California at Berkeley, for their beneficial feedback on the research and dissertation writing.

# Part I Introduction

Technology developments have made CMOS a strong candidate in high-frequency applications because of its low power, low cost and higher-level integration. However, as an essential element in an RF building block, a CMOS device is not as good as a BJT device in terms of speed and a HEMT device in terms of noise performance. Therefore, conventional low-frequency design techniques for CMOS circuits may not be satisfactory in high-frequency applications wherein the operating frequencies get close to the cut-off frequency of a CMOS device. The goal of this research work is to explore design techniques for various high-frequency circuits.

This dissertation is organized in two parts. In Part II, the proposed circuit design techniques focus on the 10-GHz applications. In Chapter 1, a thorough discussion has been focused on the optimization of CMOS common-source low-noise amplifiers. The optimization method is according to different design constraints. The analysis is based on an accurate device model and can be applied to any frequency in general. In Chapter 2, a Ku-band integrated CMOS low-noise block receiver front-end is demonstrated for the application of satellite receivers. Very low noise figure has been achieved by applying the noise optimization technique. In Chapter 3, our discussion moves to the design of nonlinear circuits. A VCO coupling technique of using a 4port inductor is proposed for VCO phase noise reduction. Various VCO topologies are demonstrated and compared in terms of phase noise performance. This technique opens the opportunity for low phase noise performance with the supply voltage scaling down with the device sizes. In Chapter 4, design strategies for true-singlephase-clock (TSPC) dividers are discussed. They are important building blocks for high-frequency local-oscillator generation circuitries. A TSPC synthesis approach is proposed and different TSPC divider structures are compared in terms of speed and power consumption.

In Part III of the dissertation, amplifier designs at mm-wave frequencies are discussed. In Chapter 5, a layout-based neutralization method is proposed for power gain enhancement of differential amplifiers. Different from conventional neutralization methods, the new technique utilizes the coupling capacitor between signal wires and requires no additional external capacitors. Neutralization theory is also provided as a theoretical basis for the proposed method. In Chapter 6, an LT de-embedding technique is proposed to measure the differential mode characteristic of a balanced 4-port device using only 2-port measurements. This technique generally extends the measurable frequency range of 4-port devices where either differential probes or 4-port vector network analyzers are not available. This de-embedding technique supports the work presented in Chapter 5.

# Part II High-Frequency RFIC Designs

## Chapter 1

## On the Noise Optimization of CMOS Common-Source Low-Noise Amplifiers

In this work, we propose a general noise optimization technique for the CMOS common-source (CS) low-noise amplifiers (LNA). By directly employing the shortchannel MOSFET I - V characteristic and van der Ziel's noise model, we derive design equations for the selection of the circuit design parameters, such as transistor sizes, passive component values and bias voltages, subject to various gain and current consumption constraints. We also include several side effects including finite quality factor and the back-gate transconductance into the optimization process and analyze their impact on the optimization results. Design examples based on virtual but realistic process parameters are given to verify our analysis and to give design intuition.

#### **1.1** Introduction

CMOS technology is one of the most competitive options for radio-frequency integrated circuit designs with the advantages of low cost and the possibility of system integration. The common-source (CS) amplifier architecture, including its derivatives, gives high-gain and low-noise performance. Therefore, research on the CMOS CS low-noise amplifiers (LNA) has been an active topic. CMOS LNA design and operation at 10 GHz and 60 GHz has been demonstrated [1] [2]. As the operating frequency gets higher, there are two major concerns. One is that the power gain of each stage becomes very limited. The other is that the losses of passive devices can severely affect the performance.

Much research on CMOS CS LNA noise optimization has been done. According to the traditional noise analysis of a linear two-port network [3], a noise optimization

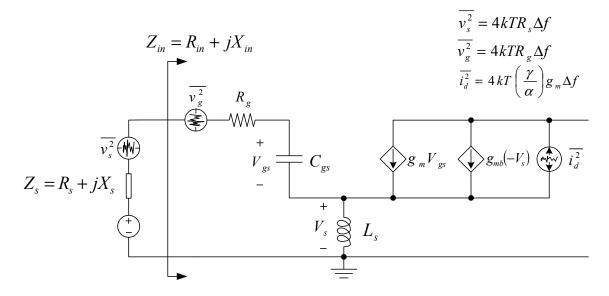

Figure 1.1: The schematics of an inductively degenerated common-source LNA with an external gate-source capacitor. Both the source impedance and the load impedance are real.

technique for inductively degenerated CS LNAs with constant-bias or constant-power constraints is developed in [4]. Further, [5] includes the series resistances of the inductors into the noise factor formula. In [6], an approach of adding an external capacitor between the gate and the source is proposed for current-limited designs. The selection of the degeneration inductor and the sizing of transistors in cascode LNAs are discussed in [7] based on exhaustive sweeps. [8] analyzes and compares various design strategies by deriving the full sets of noise parameters.

Nevertheless, there are still some interesting unsolved problems. First, the gainconstraint has not been considered. Second, no analysis has been given for the selection of the degeneration inductance under different design constraints. Third, design formulas including the finite quality factors of the inductors have not been derived and the effects of the finite quality factors on the noise figure degradation have not been analyzed either. To resolve these issues, the authors propose a general noise optimization technique for a CS LNA, Fig. 1.1. The chapter is organized as follows. Section 1.2 formulates the optimization problem for CS LNA designs. It describes the models for both active and passive devices, defines the design variables and introduces several optimization constraints. Section 1.3 gives a thorough discussion to the proposed optimization technique. Analytical solutions of the optimization problem are derived for the simple case with lossless inductors, the more complicated case with finite-Q inductors. Finally the complete case including the body effect is analyzed.

Figure 1.2: The small signal model of a CS LNA including noise sources.

#### 1.2 General Design Considerations for CS LNAs

Fig. 1.2 depicts the schematic of an inductively degenerated CS LNA. Before the noise optimization methods are shown, we need to discuss some general issues about the CS LNA design. These include modeling descriptions for both active and passive components, definitions of design variables and various practical design constraints. Many of the assumptions and notations we make in this section will be used throughout this chapter.

#### **1.2.1** Descriptions of Modeling

The drain current of an N-type MOSFET that operates in the saturation region can be described by the formula

$$I_{DSAT} = WC_{ox}\nu_{sat}\frac{(V_{GS} - V_{TH})^2}{V_{GS} - V_{TH} + mE_{sat}L}.$$

(1.1)

W is the channel width.  $C_{ox}$  is the gate oxide capacitance per unit area and it is related to the oxide thickness  $T_{ox}$  by  $C_{ox} = \frac{\varepsilon_{ox}}{T_{ox}}$ .  $\nu_{sat}$  is the saturation velocity and can be considered a constant.  $m = 1 + \frac{3T_{ox}}{W_{dep,max}}$ ,  $W_{dep,max}$  is the maximal depth of the depletion region at the channel surface.  $E_{sat}$  is the saturation electric field strength which is connected to the bias condition  $V_{GS}$  by the effective mobility  $\mu_{eff}$ ,

$$E_{sat} = \frac{2\nu_{sat}}{\mu_{eff}} = \frac{2\nu_{sat} \left[1 + \left(\frac{V_{GS} + V_{TH} + 0.2V}{6T_{ox}E_o}\right)^{\eta}\right]}{\mu_o}.$$

(1.2)

We have used a curve-fitting equation for  $\mu_{eff}$  where  $\mu_0$ ,  $\eta$  and  $E_o$  are empirical constants [10].

Eq. (1.2) can be linearized at  $V_{GS} + V_{TH} + 0.2 \approx 6T_{ox}\widetilde{E}_o$ ,

$$E_{sat} \approx \frac{2\nu_{sat}}{\mu_o} \left[ 1 + \left(\frac{\widetilde{E}_o}{E_o}\right)^{\eta} \times \left(1 - \eta \frac{\widetilde{E}_o}{E_o} + \eta \frac{V_{GS} + V_{TH} + 0.2V}{6T_{ox}E_o}\right) \right].$$

(1.3)

$\widetilde{E}_o$  is selected according to

$$\widetilde{E}_o = \frac{\widetilde{V}_{GS} + V_{TH} + 0.2\mathrm{V}}{6T_{ox}} \tag{1.4}$$

wherein  $\widetilde{V}_{GS}$  can take any normal value that biases the MOSFET in the strong inversion region.

Substitute  $E_{sat}$  in (1.1) by the linearized formula (1.3), we have

$$I_{DSAT} \approx \frac{WC_{ox}\nu_{sat}(V_{GS} - V_{TH})^2}{\left(1 + m\frac{L}{L_o}\right)(V_{GS} - V_{TH}) + m\widetilde{E}_{sat}L}$$

$$= WC_{ox}\nu_{sat}m\widetilde{E}_{sat}L\frac{\rho^2}{(1 + m\frac{L}{L_o})\rho + 1}$$

(1.5)

where

$$L_o \triangleq \frac{3\mu_o E_o}{\eta \nu_{sat}} \left(\frac{E_o}{\widetilde{E}_o}\right)^{\eta} T_{ox}, \qquad (1.6)$$

$$\widetilde{E}_{sat} \triangleq \frac{2\nu_{sat}}{\mu_o} \left[ 1 + \left(\frac{E_o}{E_o}\right)^{\eta} \times \left( 1 - \eta \frac{\widetilde{E}_o}{E_o} + \eta \frac{2V_{TH} + 0.2V}{6T_{ox}E_o} \right) \right], \qquad (1.7)$$

$$\rho \triangleq \frac{V_{GS} - V_{TH}}{m\widetilde{E}_{sat}L}.$$

(1.8)

Now  $L_o$  and  $\widetilde{E}_{sat}$  do not depend on bias.

Now we can derive the model parameters according to (1.5). The transconductance  $g_m \triangleq \frac{dI_{DSAT}}{dV_{GS}}$  is given by

$$g_m = \frac{WC_{ox}\nu_{sat}}{1 + m\frac{L}{L_o}} \left\{ 1 - \frac{1}{\left[ (1 + m\frac{L}{L_o})\rho + 1 \right]^2} \right\},$$

(1.9)

Eq. (1.9) defines a saturation level,  $\frac{WC_{ox}\nu_{sat}}{1+m\frac{L}{L_o}}$ , for  $g_m$  as the bias voltage  $V_{GS}$  increases.

The gate and drain capacitances are considered bias-independent. They have the forms

$$C_{gs} = x \cdot WLC_{ox}, \tag{1.10}$$

$$C_d = yC_{gs} = (xy) \cdot WLC_{ox} \tag{1.11}$$

with x and y being constants.

Then we can derive the expression of the device cut-off frequency  $\omega_T \triangleq \frac{g_m}{C_{as}}$ ,

$$\omega_T = \omega_{sat} \left\{ 1 - \frac{1}{\left[ (1 + m\frac{L}{L_o})\rho + 1 \right]^2} \right\}$$

(1.12)

where

$$\omega_{sat} = \frac{\nu_{sat}}{xL\left(1 + m\frac{L}{L_o}\right)}.$$

(1.13)

$\omega_T \approx \omega_{sat}$  if  $\rho \gg 1$ . It is called the high-bias condition which is satisfied for either very high bias voltages or very short short channel lengths. Fig. 1.3(a) shows how  $\omega_T$  approaches  $\omega_{sat}$  as the bias voltage increases for MOSFETs with different channel lengths.

$\alpha$  is defined as the ratio between  $g_m$  and  $g_{ds}|_{V_{DS}=0}$ . The drain current of a MOS-FET working in the linear region is given by

$$I_{DLIN} = 2WC_{ox}\nu_{sat} \frac{\left(V_{GS} - V_{TH} - \frac{m}{2}V_{DS}\right)V_{DS}}{V_{DS} + E_{sat}L}.$$

(1.14)

Then we can derive  $g_{ds}|_{V_{DS}=0}$ ,

$$g_{ds}|_{V_{DS}=0} = 2WC_{ox}\nu_{sat}\frac{\rho}{\frac{L}{L_o}\rho + \frac{1}{m}}.$$

(1.15)

Therefore,

$$\alpha = \frac{\left[ (1 + m\frac{L}{L_o})\rho + 2 \right] \left( \frac{L}{L_o}\rho + \frac{1}{m} \right)}{2 \left[ (1 + m\frac{L}{L_o})\rho + 1 \right]^2}.$$

(1.16)

For low bias voltages,  $\rho \ll 1$ , and  $\alpha$  equals to the long channel limit  $\frac{1}{m}$ . On the other hand, if the high-bias condition is satisfied,  $\alpha$  converges to  $\alpha_{sat}$ ,

$$\alpha_{sat} = \frac{L}{2\left(L_o + mL\right)}.\tag{1.17}$$

The convergence is shown in Fig. 1.3(b).

The body effect is also considered in the model due to the inductive degeneration. For a modern retrograde body doping profile, the threshold voltage  $V_{TH}$  is linearly dependent on the bulk-source voltage  $V_{BS}$ ,

$$V_{TH} = V_{THO} - (m-1)V_{BS}.$$

(1.18)

Then the back-gate transconductance  $g_{mb} \triangleq \frac{dI_d}{dV_{BS}}$  can be derived,

$$g_{mb} = \frac{WC_{ox}\nu_{sat}}{\frac{1-m\frac{L}{L_o}}{m-1}} \left\{ 1 - \left[ \frac{2m\frac{L}{L_o}\rho + 1}{(1+m\frac{L}{L_o})\rho + 1} \right]^2 \right\}.$$

(1.19)

We denote b as the ratio between  $g_{mb}$  and  $g_m$ . So

$$b = (m-1)\frac{\left(1+3m\frac{L}{L_o}\right)\rho + 2}{\left(1+m\frac{L}{L_o}\right)\rho + 2}.$$

(1.20)

Similar to  $\alpha$ , for  $\rho \ll 1$ , b equals to m-1. For  $\rho \gg 1$ , it converges  $b_{sat}$  (see Fig. 1.3(c)).

$$b_{sat} = (m-1)\frac{(L_o + 3mL)}{(L_o + mL)}.$$

(1.21)

From the above analysis and the corresponding plots, we conclude an important property of short-channel MOSFETs for which  $\rho \gg 1$  is easily satisfied. Their model parameters  $\omega_T$ ,  $\alpha$  and b are not very sensitive to the gate bias condition given that the device is biased in the strong inversion region and the drain voltage is high enough.

Finally we describe the passive components in the model.  $C_e$  is an external capacitor to help save power consumption [6]. A resistor in series with  $C_{gs}$  and  $C_e$  is used to model the distributed resistor network with a quality factor of  $Q_C$ . This resistor is included by  $R_g$ . All the inductors in the model are on-chip spiral inductors so they have very limited quality factors. The finite quality factors of  $L_g$  and  $L_d$  are also modeled as series resistors and they are included by  $R_g$  and  $R_d$  respectively. The finite quality factor of  $L_s$  together with the source junction contact resistance and the source-substrate resistance are modeled as a parallel resistor so that the DC bias condition is not affected as  $Q_s$  changes.

In this work, we will give design examples to demonstrate the proposed optimization technique using a virtual but realistic CMOS process. The process parameters, together with some process-independent constants, are summarized in Section 1.6. Unless otherwise specified, these values will be assumed throughout the chapter.

Figure 1.3: The dependence of the MOSFET model parameters (a) normalized  $\omega_T$ , (b)  $\alpha$  and (c) b on the bias voltage. The transistor channel lengths are  $L = 0.18 \ \mu m$ ,  $L = 0.24 \ \mu m$  and  $L = 0.5 \ \mu m$ .

#### **1.2.2** The Selection of Design Variables

In the CS LNA shown in Fig. 1.2, there are four explicit independent variables: the bias voltage  $V_{GS}$  (or  $\rho$ ), the external gate-source capacitor  $C_e$ , the transistor size W and the degeneration inductance  $L_s$ . Except  $\rho$ , we do not use  $C_e$ , W and  $L_s$  as design variables directly. Instead, we define three derived variables  $\kappa$ , A and T:

$$\kappa \triangleq 1 + \frac{C_e}{C_{gs}},\tag{1.22}$$

$$A \triangleq 2R_G\omega(C_{gs} + C_e), \tag{1.23}$$

$$T \triangleq g_m \omega L_s. \tag{1.24}$$

Both A and T have physical meanings.  $\frac{1}{A}$  is the quality factor of the input matching network, or equivalently A is the normalized input matching bandwidth. T is the loop gain of the series-series feedback configuration provided by the degeneration inductor.

The benefits of selecting  $\kappa$ , A and T as design variables will be evident in following sections wherein the optimization process can be pursued in steps, and each step can be broken into conditional optimization for a single variable.

#### **1.2.3** Components for Power Matching

In this part, we discuss the selection of matching components  $L_g$ ,  $R_g$ ,  $L_d$  and  $R_d$  according to the requirements of power matching at both ports. The hybrid (H-) parameters of the CS LNA model are

$$H_{11} = R_g + j\omega L_g + \frac{2R_G}{A} \left[ \frac{1}{j} + \frac{(1+j\frac{\omega\kappa}{\omega_T})T}{1+\frac{j}{Q_s} + jbT} \right],$$

(1.25)

$$H_{21} = \frac{\omega_T}{j\omega\kappa} \cdot \frac{\left(1 + b\frac{\omega\kappa}{\omega_T}T\right) + j\frac{1}{Q_s}}{1 + j\left(bT + \frac{1}{Q_s}\right)},\tag{1.26}$$

$$H_{12} = 0, (1.27)$$

$$H_{22} = j \frac{yA}{2R_G\kappa} + \frac{1}{R_d + j\omega L_d}.$$

(1.28)

For simplicity, we have employed a unilateral model. The input impedance and the output admittance are  $Z_{in} = H_{11}$  and  $Y_{out} = H_{22}$ . To satisfy the power matching requirements, they need to be conjugately matched to a real source impedance  $R_G$  and a real load impedance  $R_L$  respectively. That is,  $H_{11} = R_G$  and  $H_{22} = \frac{1}{R_L}$ . Therefore,

the design equations for the matching components can be solved.

$$L_{g} = \frac{2R_{G}}{\omega_{0}A_{0}} \left[ 1 - \frac{T_{0} \left( \frac{\omega_{0}\kappa}{\omega_{T}} - \frac{1}{Q_{s}} - bT_{0} \right)}{1 + \left( bT_{0} + \frac{1}{Q_{s}} \right)^{2}} \right], \qquad (1.29)$$

$$R_{g} = R_{G} - \frac{2R_{G}}{A_{0}} \cdot \frac{T_{0} \left(1 + \frac{\omega_{0\kappa}}{Q_{s}\omega_{T}} + b\frac{\omega_{0\kappa}}{\omega_{T}}T_{0}\right)}{1 + \left(bT_{0} + \frac{1}{Q_{s}}\right)^{2}},$$

(1.30)

$$L_d = \frac{1}{\omega_0} \cdot \frac{1}{\frac{yA_0}{2R_G\kappa} + \frac{2R_G\kappa}{yA_0R_L^2}},$$

(1.31)

$$R_d = \frac{\frac{2R_G\kappa}{yA_0R_L}}{\frac{yA_0}{2R_G\kappa} + \frac{2R_G\kappa}{yA_0R_T^2}}.$$

(1.32)

$\omega_0 = 2\pi f_0$  is the desired operating frequency.  $A_0$  and  $T_0$  are the values of A and T at  $\omega_0$  respectively. This convention will be applied to other variables. For each given variable set  $\{\rho, \kappa, A_0, T_0\}$ , the matching components are uniquely determined.

#### **1.2.4** Design Constraints

In practice, the range of the design variables are subject to various constraints. Fixing the bias  $\rho$  and the capacitance ratio  $\kappa$ , the variable pairs  $\{A_0, T_0\}$  that satisfy all constraints comprise the region of design (ROD) in a 2-dimensional plane. We will introduce several common constraints for CS LNA designs and find the ROD.

#### The $Q_{L_q}, Q_C$ -Constraint

A physical capacitor  $C_{gs}$  has a finite quality factor and so does  $L_g$ . Hence,  $R_g$  which includes the series resistance of  $C_{gs}$  and  $L_g$  cannot be arbitrarily small. We suppose the quality factor  $Q_C$  and  $Q_{L_g}$  are given, so  $R_g$  needs to satisfy  $R_g \ge \frac{1}{Q_C \omega_0 \kappa C_{gs}} + \frac{\omega_0 L_g}{Q_{L_g}}$ . According to (1.23), (1.29) and (1.30), one can derive a lower bound M for  $A_0$ .

$$A_0 \geqslant M \tag{1.33}$$

where

$$M \triangleq \frac{2T_0 \left(1 + \frac{\omega_0 \kappa}{Q_s \omega_T} + b \frac{\omega_0 \kappa}{\omega_T} T_0\right)}{1 + \left(\frac{1}{Q_s} + b T_0\right)^2} + \frac{2}{Q_C} + \frac{2}{Q_{L_g}} \left[1 - \frac{T_0 \left(\frac{\omega_0 \kappa}{\omega_T} - \frac{1}{Q_s} - b T_0\right)}{1 + \left(\frac{1}{Q_s} + b T_0\right)^2}\right].$$

(1.34)

Though the exact value of  $Q_C$ ,  $Q_{L_g}$  and  $Q_s$  are not known until the circuits are finalized, an estimate according to a knowledge of process and rough ranges of component values is usually a good enough starting point.

#### The $Q_{L_d}$ -Constraint

Similarly, a quality factor constraint is also applied to  $L_d$ . For a given  $Q_{L_d}$ ,  $R_d$  satisfies  $R_d \ge \frac{\omega_0 L_d}{Q_{L_d}}$ . From (1.31) and (1.32), we can derive an upper bound

$$A_0 \leqslant \frac{2Q_{L_d}R_G\kappa}{yR_L}.\tag{1.35}$$

#### The $I_D$ -Constraint

According to (1.5), (1.10) and (1.23), the drain current  $I_D$  can be related to  $A_0$  by

$$A_0 = \frac{\kappa I_D}{I_0} \frac{(1 + m\frac{L}{L_o})\rho + 1}{\rho^2}$$

(1.36)

where  $I_0$  is a bias-independent constant

$$I_0 \triangleq \frac{\nu_{sat} m E_{sat}}{2x\omega_0 R_G}.$$

(1.37)

The  $I_D$ -constraint defines an upper bound  $I_{D,\max}$  for the drain current, then  $A_0$  must satisfy

$$A_0 \leqslant \frac{\kappa I_{D,\max}}{I_0} \frac{(1+m\frac{L}{L_o})\rho + 1}{\rho^2}.$$

(1.38)

#### The Gain-Constraint

Gain refers to the power gain in this chapter. The power gain  $G_p$  of a CS LNA satisfying conjugate matching at both ports equals the maximal power gain  $G_{\text{max}} = \frac{|H_{21}|^2}{4\Re\{H_{11}\}\Re\{H_{22}\}}$ .

$$\therefore \ G_p = \frac{R_L \omega_T^2}{4R_G \omega_0^2 \kappa^2} \frac{\left(1 + \frac{\omega_0 \kappa}{\omega_T} bT_0\right)^2 + \frac{1}{Q_s^2}}{1 + \left(bT_0 + \frac{1}{Q_s}\right)^2}.$$

(1.39)

The effect of  $T_0$  can be examined in two extreme cases:

$$G_p|_{T_0=0} = \frac{R_L \omega_T^2}{4R_G \omega_0^2 \kappa^2},$$

(1.40)

$$G_p|_{T_0 \to \infty} = \frac{R_L}{4R_G}.$$

(1.41)

In practice,  $\omega_0 \kappa < \omega_T$  is always true. This means a large value of  $T_0$  results in a power gain degradation. For any power gain  $G_p$  satisfying  $G_p|_{T_0\to\infty} < G_p < G_p|_{T_0=0}$ , we can find a unique corresponding  $T_0$ .

$$T_{0} = \frac{1}{b(G_{p} - \frac{R_{L}}{4R_{G}})} \left\{ \left[ \left( \frac{G_{p}}{Q_{s}} - \frac{R_{L}\omega_{T}}{4R_{G}\omega_{0}\kappa} \right)^{2} + \left(1 + \frac{1}{Q_{s}^{2}}\right) \left(G_{p} - \frac{R_{L}}{4R_{G}}\right) \left(\frac{R_{L}\omega_{T}^{2}}{4R_{G}\omega_{0}^{2}\kappa^{2}} - G_{p} \right) \right]^{\frac{1}{2}} - \left( \frac{G_{p}}{Q_{s}} - \frac{R_{L}\omega_{T}}{4R_{G}\omega_{0}\kappa} \right) \right\}.$$

$$(1.42)$$

And given a lower bound of the power gain  $G_{p,\min}$  (1.42) defines an upper bound for  $T_0$ .

In summary, the ROD of a CS LNA design with all the above constraints can be described as

$$ROD = \{ M \leqslant A_0 \leqslant A_{\max}, \ 0 \leqslant T_0 \leqslant T_{\max} \}$$

$$(1.43)$$

$A_{\text{max}}$  and  $T_{\text{max}}$  are the lowest values of various upper bounds defined above. Designers can update their values if more constraints are considered based on specific application requirements.

#### **1.3** The Noise Optimization Techniques

#### 1.3.1 Noise Factors of CS LNAs

We adopt the concept of noise transfer function (NTF) in our noise analysis. The NTFs are the transfer functions from different internal noise sources,  $n_k$ , to the outputs of the 2-port network. The type of NTFs corresponds to that of the 2-port parameter. Since we use H-parameters to describe a CS LNA, we also use H-NTFs. Now, we are going to derive the connection between H-NTFs and the equivalent input noise voltage  $v_{n,eq}$  and the equivalent input noise current  $i_{n,eq}$ . In general, the 2-port equations with NTFs are

$$\begin{cases} V_1 = H_{11}I_1 + H_{12}V_2 + \sum_k H_{n1k}n_k \\ I_2 = H_{21}I_1 + H_{22}V_2 + \sum_k H_{n2k}n_k \end{cases}$$

(1.44)

On the other hand, the 2-port equations with the equivalent noise voltage and current are

$$\begin{cases} V_1 + v_{n,eq} = H_{11} \left( I_1 + i_{n,eq} \right) + H_{12} V_2 \\ I_2 = H_{21} \left( I_1 + i_{n,eq} \right) + H_{22} V_2 \end{cases}$$

(1.45)

By comparing (1.44) and (1.45), we conclude that

$$i_{n,eq} = U, \tag{1.46}$$

$$v_{n,eq} = H_{11}U - E (1.47)$$

with

$$U \triangleq \sum_{k} \frac{H_{n2k}}{H_{21}} n_k. \tag{1.48}$$

$$E \triangleq \sum_{k} H_{n1k} n_k. \tag{1.49}$$

With all the above information, we can represent the noise factor of the CS LNA in terms of U and E [9],

$$F = 1 + \frac{4R_G^2 \overline{|U|^2} - 4R_G \Re\{\overline{UE^*}\} + \overline{|E|^2}}{4k_B t R_G \Delta f}.$$

(1.50)

We also derive the expression of another noise parameter, the minimum noise factor  $F_{\min}$ . Though only  $F_{opt}$  affects the real performance of an LNA, we would like to see the difference between F and  $F_{\min}$  at the optimal design.

$$F_{\min} = 1 + \frac{\overline{|U|^2}R_G - \Re\{\overline{UE^*}\}}{2k_B t \Delta f} + \frac{1}{2k_B t \Delta f} \left[ \left( \overline{|U|^2}R_G - \Re\{\overline{UE^*}\} + \frac{\overline{|E|^2}}{2R_G} \right)^2 - \left( \Re\{\overline{UE^*}\} - \frac{\overline{|E|^2}}{2R_G} \right)^2 - \Im^2\{\overline{UE^*}\} \right]^{\frac{1}{2}}.$$

(1.51)

F is always higher than  $F_{\min}$  and they are equal if and only if both  $\Re\{\overline{UE^*}\} = \frac{\overline{|E|^2}}{2R_G}$ and  $\Im\{\overline{UE^*}\} = 0$  are satisfied.

#### **1.3.2** Internal Noise Sources

The equivalent circuit in Fig. 1.2 employs a MOSFET noise model from [11]. It includes the channel thermal noise  $i_{ds}$  and the induced gate noise  $i_q$ .

The channel thermal noise constant  $\gamma$  and the induced gate current noise constant  $\delta$  are verified to be independent of operating frequencies, and they are not sensitive to bias conditions for high bias voltages. However, they vary with channel lengths. Short channel effects can result in larger values than their theoretical long channel values [12].

$i_{ds}$  and  $i_g$  are not independent and their correlation coefficient c is studied under different conditions [13]. It is purely imaginary,

$$c = \frac{\overline{i_g \cdot i_{ds}^*}}{\sqrt{|i_g|^2 \cdot |i_{ds}|^2}} = jc_i.$$

(1.52)

$c_i$  is independent of operating frequencies. Also, when biased in the saturation region, it is not very sensitive to bias voltages. Moreover, it decreases when the channel length L decreases.

In our analysis, we consider  $\gamma$ ,  $\delta$  and  $c_i$  as constants. To make our future expressions more compact, we define three variables  $\psi$ ,  $\chi$  and  $\xi$ .

$$\psi \triangleq \frac{\alpha\delta}{5\kappa^2}.$$

(1.53)

$$\chi \triangleq \frac{\alpha\delta}{5\kappa^2} + \frac{\gamma}{\alpha} - 2c_i\sqrt{\frac{\gamma\delta}{5\kappa^2}}.$$

(1.54)

$$\xi \triangleq \frac{\alpha\delta}{5\kappa^2} - c_i \sqrt{\frac{\gamma\delta}{5\kappa^2}}.$$

(1.55)

The thermal noises of the resistors in the model are also considered. As a summary, all internal noise sources in a CS LNA with their power spectra and NTFs are listed in Table 1.1. So the explicit expressions of  $|U|^2$ ,  $|E|^2$  and  $\overline{UE^*}$  can be derived according to (1.48) and (1.49). They are summarized in Section 1.8. And F is now an explicit function of  $A_0$  and  $T_0$ . There are two terms in F that depend on  $A_0$ . One is proportional to  $\frac{1}{A_0}$  and the other is proportional to  $A_0$ . N is defined as the ratio between the coefficients of the two terms. A rigorous definition is

$$N \triangleq \frac{\lim_{A_0 \to 0} A_0 \cdot F}{\lim_{A_0 \to \infty} \frac{F}{A_0}}.$$

(1.56)

| $n_k$     | $\frac{\overline{ n_k ^2}}{4k_B t \Delta f}$          | $H_{n1k}$                                                                                 | $H_{n2k}$                                                                                  |

|-----------|-------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| $v_{R_g}$ | $R_g$                                                 | 1                                                                                         | 0                                                                                          |

| $i_g$     | $\frac{\alpha\delta}{5}\frac{\omega^2 C_{gs}^2}{g_m}$ | $-\frac{2R_G}{A}\frac{T+\frac{1}{Q_s}+bT-j}{1+j\left(\frac{1}{Q_s}+bT\right)}$            | $-\frac{\omega_T}{j\omega\kappa}\frac{1+j\frac{1}{Q_s}}{1+j\left(\frac{1}{Q_s}+bT\right)}$ |

| $i_{ds}$  | $\frac{\gamma}{\alpha}g_m$                            | $\frac{2R_G}{A} \frac{j\frac{\omega\kappa}{\omega_T}T}{1+j\left(\frac{1}{Q_s}+bT\right)}$ | $\frac{1+j\frac{1}{Q_s}}{1+j\left(\frac{1}{Q_s}+bT\right)}$                                |

| $i_s$     | $\frac{1}{Q_s \omega L_s}$                            | $-\frac{2R_G}{A}\frac{j\frac{\omega\kappa}{\omega_T}T}{1+j\left(\frac{1}{Q_s}+bT\right)}$ | $\frac{jbT}{1+j\left(\frac{1}{Q_s}+bT\right)}$                                             |

| $v_{R_d}$ | $R_d$                                                 | 0                                                                                         | $-rac{1}{R_d+j\omega L_d}$                                                                |