# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

A W-Band SiGe 4x4 Polarimetric Transmit-Receive Phased Array and CMOS THz Multiplier Arrays /

**Permalink** https://escholarship.org/uc/item/6kc0k0zp

**Author** Golcuk, Fatih

Publication Date 2013

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

## A W-Band SiGe 4×4 Polarimetric Transmit-Receive Phased Array and CMOS THz Multiplier Arrays

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Fatih Golcuk

Committee in charge:

Professor Gabriel M. Rebeiz, Chair Professor Peter Asbeck Professor James F. Buckwalter Professor Gert Cauwenberghs Professor William S. Hodgkiss

2013

Copyright Fatih Golcuk, 2013 All rights reserved. The dissertation of Fatih Golcuk is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2013

# DEDICATION

To my parents, Duran and Hatice

### TABLE OF CONTENTS

| Signature Page  | e                                 | ii                                                                                                                         |

|-----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Dedication      |                                   | iv                                                                                                                         |

| Table of Conte  | ents .                            |                                                                                                                            |

| List of Figures | 5                                 | vi                                                                                                                         |

| List of Tables  |                                   |                                                                                                                            |

| Acknowledger    | nents                             | xi                                                                                                                         |

| Vita and Public | cation                            | s                                                                                                                          |

| Abstract of the | e Disse                           | ertation                                                                                                                   |

| Chapter 1       | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | duction                                                                                                                    |

| Chapter 2       |                                   | 100 GHz 4×4 SiGe BiCMOS Polarimetric Transmit-Receive Phasedwith Simultaneous Receive-Beams CapabilitiesIntroductionDesign |

|                 | 2.4<br>2.5                        | Acknowledgement         50                                                                                                 |

| Chapter 3    | A 0.39-0.44 THz 2×4 Amplifier-Quadrupler Array with Peak EIRP of 3-4           |

|--------------|--------------------------------------------------------------------------------|

|              | dBm                                                                            |

|              | 3.1 Introduction                                                               |

|              | 3.2 Design                                                                     |

|              | 3.2.1 Quadrupler                                                               |

|              | 3.2.2 Slot-Ring Antenna                                                        |

|              | 3.2.3 Amplifier/Splitter Distribution Network and 2×4 Antenna                  |

|              | Array                                                                          |

|              | 3.3 Measurements                                                               |

|              | 3.3.1 Standalone Quadrupler                                                    |

|              | 3.3.2 Quadrupler with Integrated W-band Driver                                 |

|              | 3.3.3 2×4 Transmit Array                                                       |

|              | 3.4 Conclusion                                                                 |

|              | 3.5 Acknowledgement                                                            |

| Chapter 4    | A 163-180 GHz $2 \times 2$ Amplifier-Doubler Array with Peak EIRP of +5 dBm 78 |

| -            | 4.1 Introduction                                                               |

|              | 4.2 Design                                                                     |

|              | 4.3 Measurements                                                               |

|              | 4.4 Conclusion                                                                 |

|              | 4.5 Acknowledgement                                                            |

| Chapter 5    | Conclusion                                                                     |

| Bibliography |                                                                                |

### LIST OF FIGURES

| Figure 1.1:  | An 8-element phased array block diagram.                                                        | 2   |

|--------------|-------------------------------------------------------------------------------------------------|-----|

| Figure 1.2:  | Phased array receiver architectures: (a) RF phase shifting, (b) LO phase                        |     |

|              | shifting, (c) IF phase shifting and (d) digital beam forming.                                   | 4   |

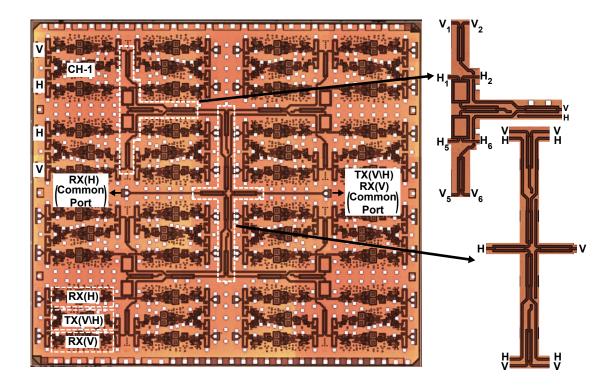

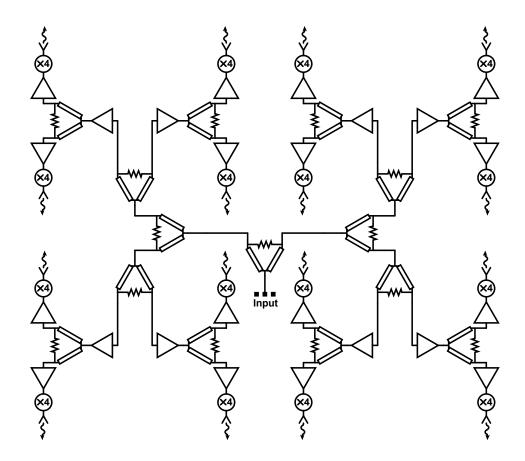

| Figure 2.1:  | Polarimetric transmit-receive 16:1 $4 \times 4$ phased array with simultaneous receive          | e-  |

|              | beams and dual nested Wilkinson combiners                                                       | 10  |

| Figure 2.2:  | T/R unit (single element) block diagram.                                                        | 11  |

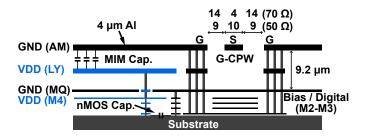

| Figure 2.3:  | IBM8HP metal stack-up with representative 50 $\Omega$ and 70 $\Omega$ G-CPW lines.              | 11  |

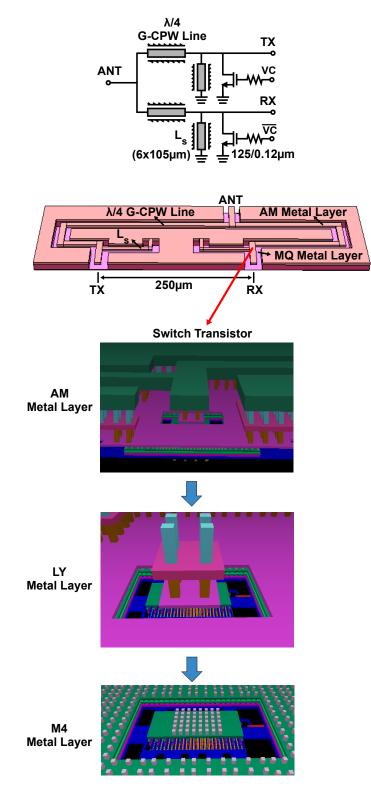

| Figure 2.4:  | SPDT switch schematic and Sonnet layout.                                                        | 12  |

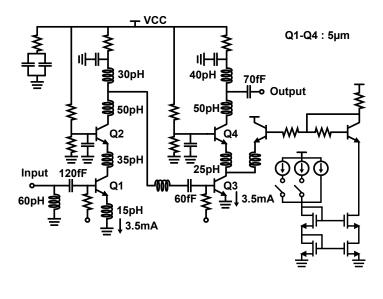

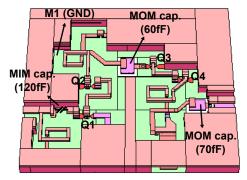

| Figure 2.5:  | LNA with gain control schematic and Sonnet layout.                                              | 13  |

| Figure 2.6:  | Power amplifier with active switch schematic and Sonnet layout                                  | 15  |

| Figure 2.7:  | Phase shifter block diagram.                                                                    | 16  |

| Figure 2.8:  | Input balun schematic, Sonnet layout and simulation results                                     | 17  |

| Figure 2.9:  | I/Q generator schematic, Sonnet layout and simulation results                                   | 17  |

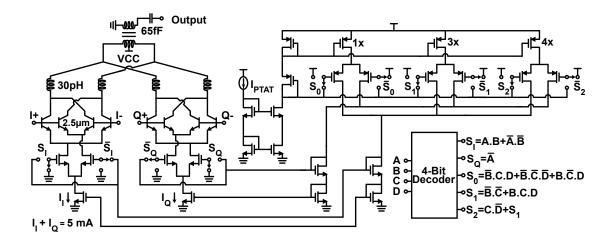

| Figure 2.10: | Vector modulator and DAC (Digital to Analog Converter) schematic                                | 18  |

| Figure 2.11: | Vector modulator Sonnet layout of (a) input matching, (b) transistor inter-                     |     |

|              | connection and (c) output load balun.                                                           | 18  |

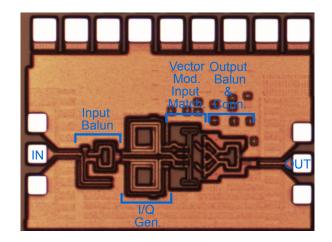

| Figure 2.12: | Phase shifter breakout chip microphotograph $(0.75 \times 0.65 \text{ mm}^2 \text{ including})$ |     |

|              | DC pads)                                                                                        | 19  |

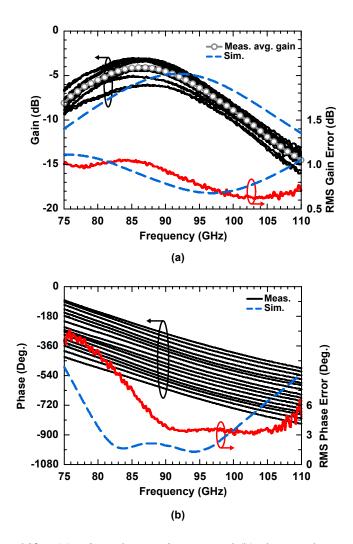

| Figure 2.13: | Phase shifter (a) gain and rms gain error and (b) phase and rms phase error                     |     |

|              | over 16 phase states.                                                                           | 21  |

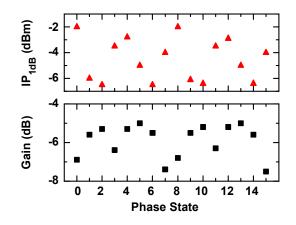

|              | Measured gain and IP <sub>1dB</sub> versus 16 phase states at 94 GHz                            | 22  |

| Figure 2.15: | Measured (a) relative phase versus input power at 94 GHz, (b) rms phase                         |     |

|              | error versus input power at 90, 94 and 100 GHz, (c) a block diagram of                          |     |

|              | current components for phase shifter and (d) simulated $I_I$ and $I_Q$ current                  |     |

|              | versus input power                                                                              | 23  |

| Figure 2.16: | Wilkinson combiner/divider Sonnet layouts and simulated S-parameters.                           |     |

|              | Two different Wilkinson combiners/dividers were used, shown in (a) and                          |     |

|              | (b)                                                                                             | 24  |

| Figure 2.17: | V and H polarization combiner/divider network cross-over Sonnet layouts                         |     |

|              | and simulated S-parameters                                                                      | 25  |

| Figure 2.18: | Parallel G-CPW line Sonnet layout and coupling simulations results for 40                       |     |

|              | $\mu$ m and 58 $\mu$ m center to center spacing                                                 | 25  |

| Figure 2.19: | Simulated insertion loss for the V and H polarization 16:1 Wilkinson com-                       |     |

|              | biner/divider networks.                                                                         | 26  |

| Figure 2.20: | (a) Rx channel block diagram with simulated component values for gain,                          |     |

|              | NF and $IP_{1dB}$ and (b) Tx channel block diagram with simulated component                     | 27  |

| 5. 2.21      | values for gain and $P_{sat}$ .                                                                 | 27  |

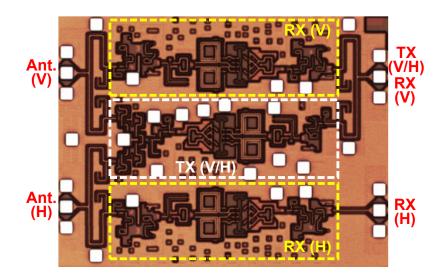

| Figure 2.21: |                                                                                                 | 5.9 |

|              | $mm^2$ ). The chip contains 48 phased-array channels. Note the multitude of                     |     |

|              | ground pads over the entire chip used to equalize the on-chip ground to the                     | 20  |

| Ei           | RDL system-ground.                                                                              | 28  |

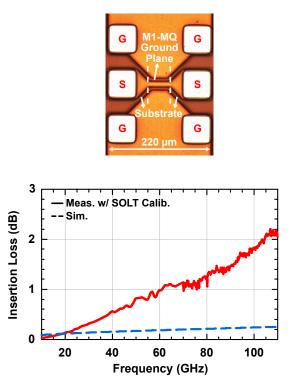

| гigure 2.22: | Measured and simulated THRU pad losses.                                                         | 30  |

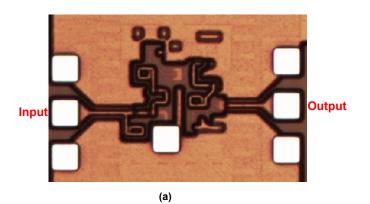

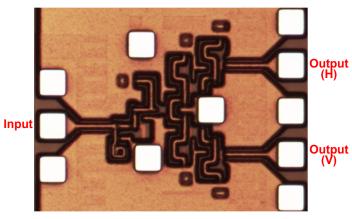

| Figure 2.23: | (a) LNA breakout chip microphotograph $(0.58 \times 0.45 \text{ mm}^2 \text{ not including DC})$ pads), and (b) PA breakout chip microphotograph $(0.65 \times 0.55 \text{ mm}^2 \text{ not including DC})$                                    | 21       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2.24: | cluding DC pads)                                                                                                                                                                                                                               | 31<br>32 |

| Figure 2.25: |                                                                                                                                                                                                                                                | 33       |

| Figure 2.26: | Stand-alone power amplifier: (a) measured and simulated gain, (b) mea-<br>sured output power and gain versus input power at 94 GHz, and (c) mea-<br>sured saturated output power versus DC current at 2 V, 2.2 V and 2.4 V<br>supply voltages. | 35       |

| Figure 2.27: | T/R unit (single element) chip microphotograph $(1.6 \times 1.2 \text{ mm}^2 \text{ not includ-ing DC pads})$ .                                                                                                                                | 36       |

| Figure 2.28: | Measured average gain and phase of both Rx channels on a T/R unit over 16 phase states at maximum gain state.                                                                                                                                  | 37       |

| Figure 2.29: | Measured input and output return losses of Rx(V) channel on a T/R unit over 16 phase states.                                                                                                                                                   | 38       |

| -            | Measured gain of $Rx(V)$ channel on a T/R unit over 8 gain states at $0^{\circ}$ phase state.                                                                                                                                                  | 38       |

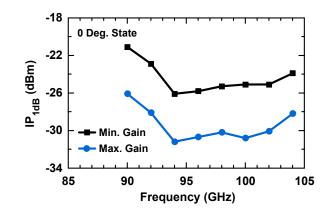

|              | Measured Rx channel IP1dB versus frequency at minimum and maximum gain settings and $0^{\circ}$ phase state.                                                                                                                                   | 40       |

|              | Measured Rx channel NF (LNA, phase shifter and RX amplifier) Measured average gain and phase of $Tx(V)$ and $Tx(H)$ channel on a T/R unit                                                                                                      | 40       |

| Figure 2.34: | over 16 phase states at maximum gain state                                                                                                                                                                                                     | 41       |

| Figure 2.35: | over 16 phase states at maximum gain state                                                                                                                                                                                                     | 42       |

| Figure 2.36: | state                                                                                                                                                                                                                                          | 43       |

| Figure 2.37: | states at 94 GHz                                                                                                                                                                                                                               | 43       |

| Figure 2.38: | <ul> <li>gain state</li></ul>                                                                                                                                                                                                                  | 43       |

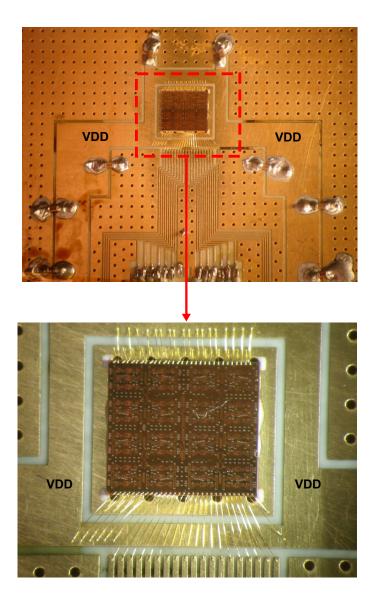

| -            | is toggled) on a T/R unit. The isolation does not vary over the 16 phase states.<br>Bonded a $4\times4$ array chip on a dc biasing board                                                                                                       | 44<br>45 |

| Figure 2.41: | ohmic loss of 16:1 Wilkinson power combiner. (Measured channel numbers<br>for $Rx(V)$ are 1, 5, 6, 7, 9, 10, 11 and 13, and measured channel numbers<br>for $Rx(H)$ are 4, 6, 7, 8, 10, 11, 12 and 16.)                                        | 46       |

|              | are 1, 5, 6, 7, 9, 10, 11 and 13).                                                                                                                                                                                                             | 46       |

| Figure 2.42:                 | Measured (a) gain and output power versus input power for channel-1 and (b) saturated output power of $Tx(V)$ channel on $4 \times 4$ array for 8 channels at $45^{\circ}$ phase state at 94 GHz. (Measured channel numbers are 1, 5, 6, 7, 9, 10, |            |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                              | 45       phase state at 94 GHZ. (Measured channel numbers are 1, 5, 6, 7, 9, 10, 11 and 13)                                                                                                                                                        | 47         |

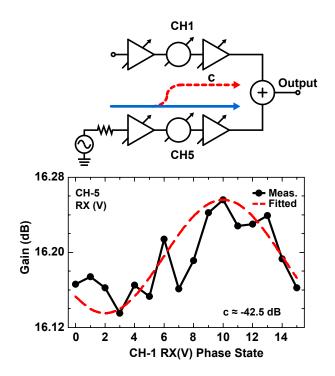

| Figure 2.43:                 | Measured Rx channel coupling at 94 GHz. Rx(V) on CH-5 is measured                                                                                                                                                                                  |            |

|                              | while phase state of $Rx(V)$ on CH-1 is changed                                                                                                                                                                                                    | 48         |

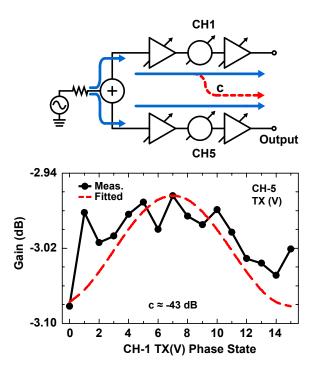

| Figure 2.44:                 | Measured Tx channel coupling at 94 GHz. $Tx(V)$ on CH-5 is measured                                                                                                                                                                                | 4.0        |

|                              | while phase state of $Tx(V)$ on CH-1 is changed.                                                                                                                                                                                                   | 48         |

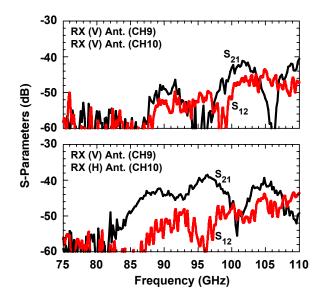

|                              | Rx channel antenna port to Rx channel antenna port coupling                                                                                                                                                                                        | 49         |

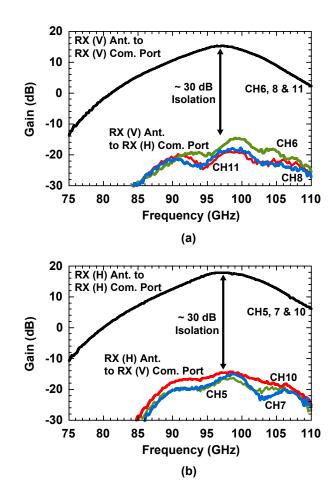

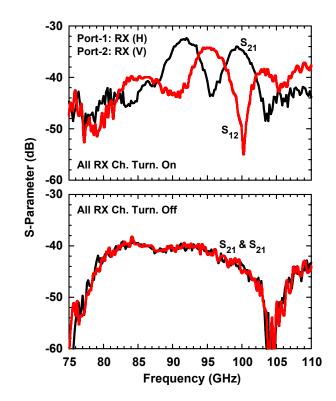

| -                            | Rx channel antenna ports to Rx channel common ports isolation.                                                                                                                                                                                     | 51         |

| Figure 2.47:                 | Rx(H) common port to $Rx(V)$ common port isolation                                                                                                                                                                                                 | 52         |

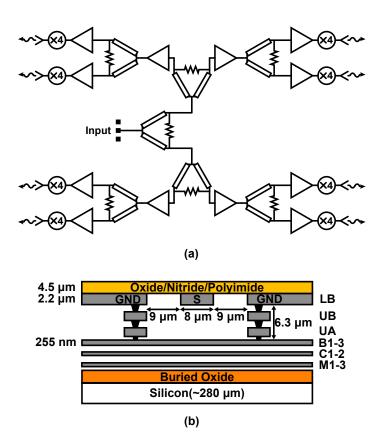

| Figure 3.1:                  | (a) Block diagram of the $2 \times 4$ amplifier-quadrupler array, and (b) 45-nm SOI CMOS process metal stack-up and 50- $\Omega$ G-CPW transmission-line cross                                                                                     |            |

|                              | section                                                                                                                                                                                                                                            | 55         |

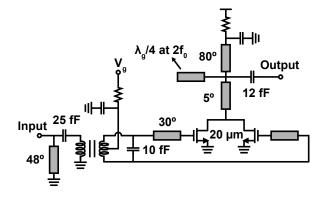

| Figure 3.2:                  | Quadrupler schematic with second harmonic reflector at the output                                                                                                                                                                                  | 57         |

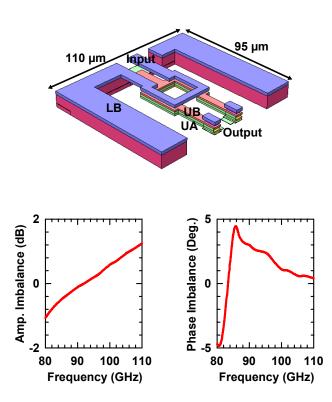

| Figure 3.3:                  | Input balun Sonnet layout, and simulated amplitude and phase imbalance.                                                                                                                                                                            | 57         |

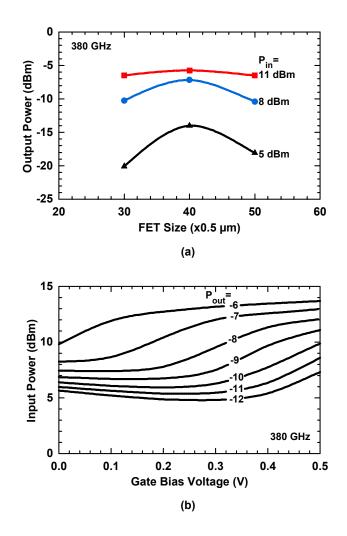

| Figure 3.4:                  | (a) Simulated output power at 380 GHz versus transistor size at 5, 8 and 11                                                                                                                                                                        |            |

|                              | dBm input power and (b) simulated input power versus gate voltage for an                                                                                                                                                                           |            |

|                              | output power range of -6 dBm to -12 dBm at 380 GHz (transistor size is                                                                                                                                                                             | -          |

| <b>D</b> : 0.5               | $40 \times 0.5 \mu$ m).                                                                                                                                                                                                                            | 59         |

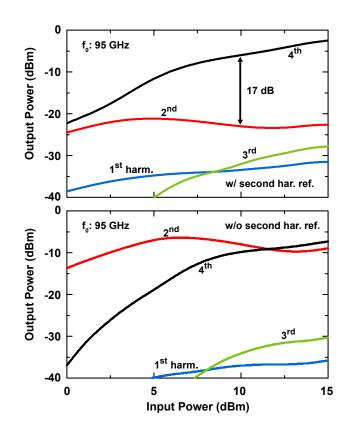

| Figure 3.5:                  | Simulated harmonic levels of quadrupler with and without a second har-                                                                                                                                                                             | <i>(</i> 0 |

| E'                           | monic reflector versus input power at 95 GHz.                                                                                                                                                                                                      | 60         |

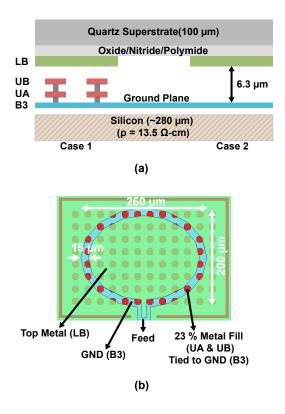

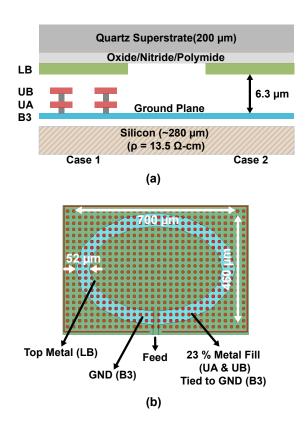

| Figure 3.6:                  | (a) Metal fill cases and (b) on-chip single-ended elliptical slot ring antenna                                                                                                                                                                     | 61         |

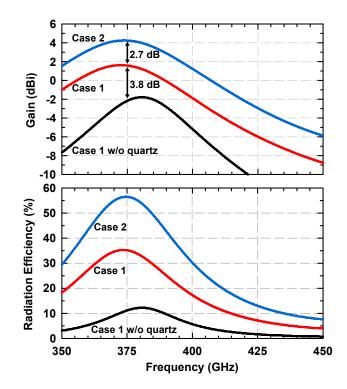

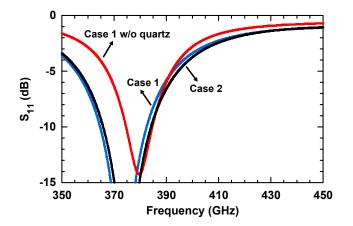

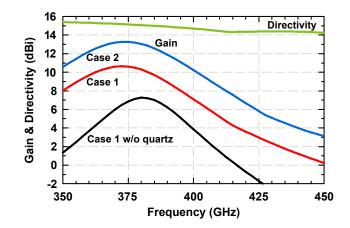

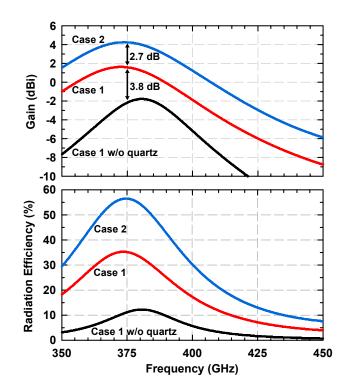

| Eigung 27.                   | with metal-fill underneath the antenna.                                                                                                                                                                                                            | 61<br>62   |

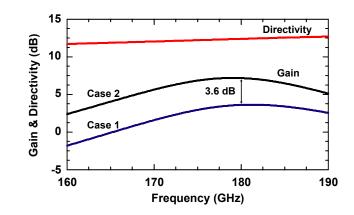

| Figure 3.7:<br>Figure 3.8:   | Simulated elliptical slot-ring antenna gain and efficiency                                                                                                                                                                                         | 62<br>62   |

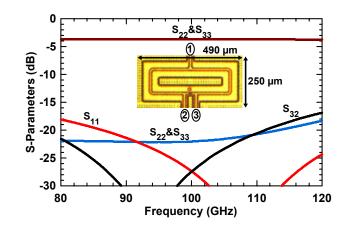

| Figure 3.8:<br>Figure 3.9:   | Simulated S-parameters of the W-band Wilkinson power divider.                                                                                                                                                                                      | 64         |

| Figure 3.9.<br>Figure 3.10:  | Simulated S-parameters of the w-band winkinson power divider. $\ldots$ . Simulated 2×4 antenna array gain and directivity. $\ldots$                                                                                                                | 64         |

| Figure 3.10.<br>Figure 3.11: | Microphotograph of the quadrupler $(0.73 \times 0.55 \text{ mm}^2)$ .                                                                                                                                                                              | 65         |

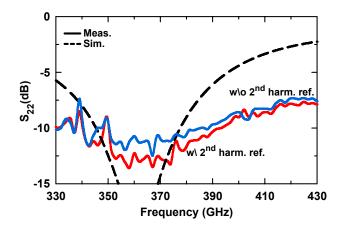

| Figure 3.12:                 | Measured and simulated output return loss.                                                                                                                                                                                                         | 65         |

| Figure 3.12:                 | Measurement setup for quadrupler output power and conversion loss.                                                                                                                                                                                 | 66         |

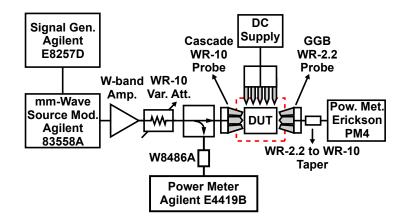

| Figure 3.14:                 |                                                                                                                                                                                                                                                    | 00         |

| 1 iguie 5.1 i.               | of the quadrupler versus input power, (b) peak output power and (c) $2^{nd}$                                                                                                                                                                       |            |

|                              | harmonic output power versus frequency.                                                                                                                                                                                                            | 67         |

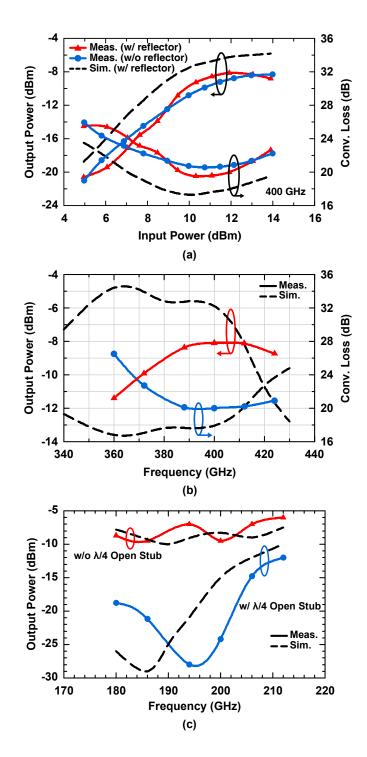

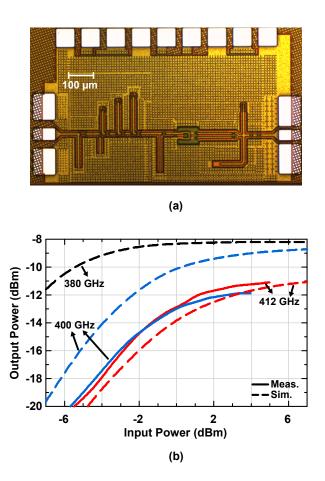

| Figure 3.15:                 |                                                                                                                                                                                                                                                    | 07         |

| 11guie 5.101                 | simulated and measured output power at 380, 400 GHz and 412 GHz of the                                                                                                                                                                             |            |

|                              | amplifier/quadrupler.                                                                                                                                                                                                                              | 69         |

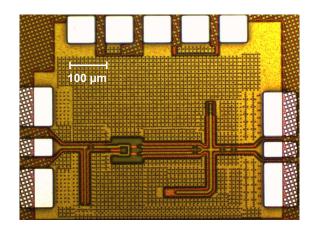

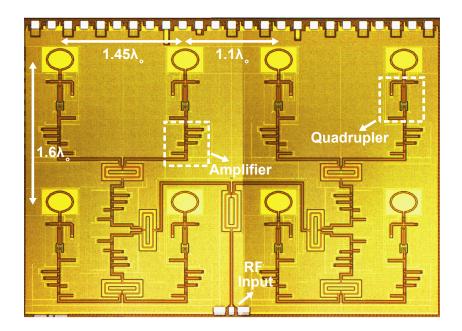

| Figure 3.16:                 | Chip microphotograph of the $2 \times 4$ amplifier-quadrupler array ( $2.7 \times 3.8$ mm <sup>2</sup> ).                                                                                                                                          | 70         |

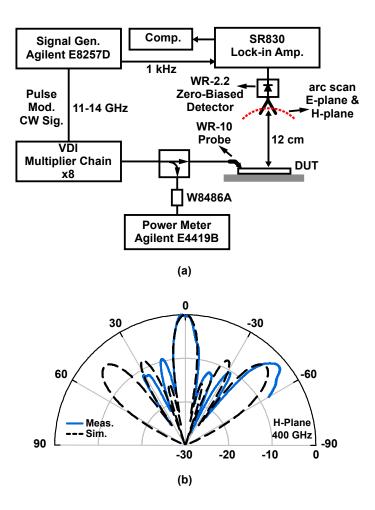

| Figure 3.17:                 |                                                                                                                                                                                                                                                    |            |

|                              | simulated H-plane antenna patterns of the $2 \times 4$ array at 400 GHz                                                                                                                                                                            | 72         |

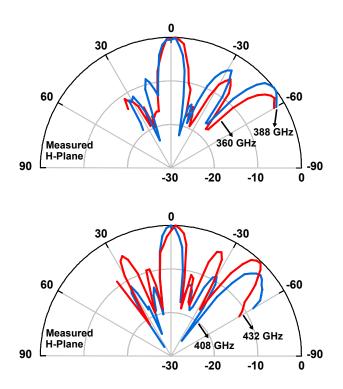

| Figure 3.18:                 | Measured H-plane antenna patterns of the $2 \times 4$ array at 360, 388, 408 and                                                                                                                                                                   |            |

| -                            | 432 GHz                                                                                                                                                                                                                                            | 73         |

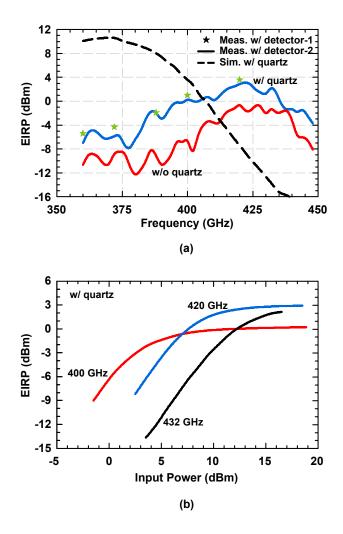

| Figure 3.19:                 |                                                                                                                                                                                                                                                    |            |

|                              | and without a quartz superstrate and (b) measured EIRP at 400, 420 and 432                                                                                                                                                                         |            |

|                              | GHz versus input power                                                                                                                                                                                                                             | 74         |

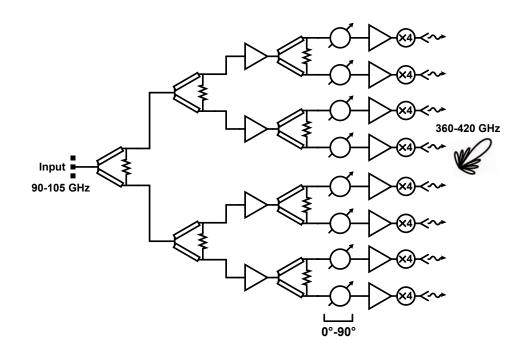

| Figure 3.20: | Block diagram of the $4 \times 4$ amplifier-quadrupler array                                 | 77 |

|--------------|----------------------------------------------------------------------------------------------|----|

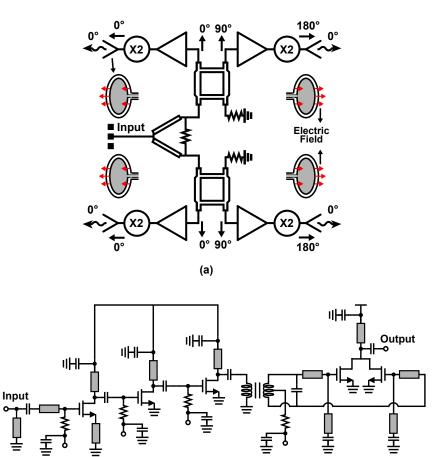

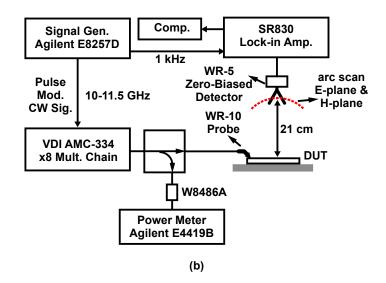

| Figure 4.1:  | (a) Block diagram of the $2 \times 2$ amplifier-doubler array and (b) the amplifier-         |    |

|              | doubler schematic.                                                                           | 79 |

| Figure 4.2:  | Branchline (a) sonnet layout and (b) simulated S-parameters                                  | 80 |

| Figure 4.3:  | (a) Metal-fill cases and (b) on-chip single-ended slot antenna with the metal-               |    |

|              | fill underneath the antenna.                                                                 | 82 |

| Figure 4.4:  | Simulated elliptical slot-ring antenna gain and efficiency                                   | 83 |

| Figure 4.5:  | Simulated $2 \times 2$ antenna array gain and directivity with a quartz superstrate.         | 84 |

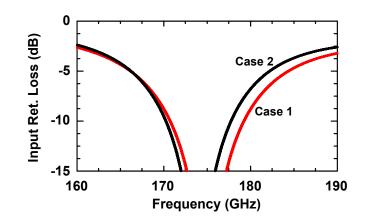

| Figure 4.6:  | Simulated elliptical slot-ring antenna input return loss                                     | 84 |

| Figure 4.7:  | (a) Microphotograph of the $2 \times 2$ amplifier-doubler array (2 x 2.9 mm <sup>2</sup> in- |    |

|              | cluding pads), and (b) Measurement setup for antenna patterns and EIRP.                      | 86 |

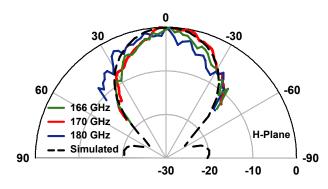

| Figure 4.8:  | Simulated (180 GHz) and measured H-plane patterns with a quartz superstrate.                 | 87 |

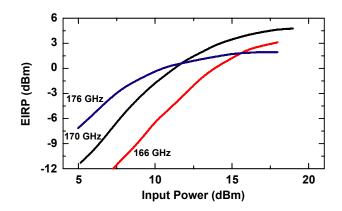

| Figure 4.9:  | Measured EIRP versus input power at 166-176 GHz with a quartz superstrate.                   | 87 |

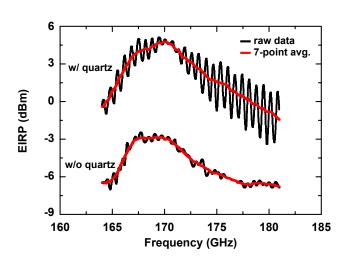

| Figure 4.10: | Measured EIRP versus frequency with and without quartz superstrate. Mea-                     |    |

|              | surements are taken with 200 MHz steps.                                                      | 89 |

| Figure 5.1:  | Polyimide RDL technology (Courtesy of Dr. Jon Hacker, Teledyne Scien-                        |    |

|              | tific, CA)                                                                                   | 93 |

| Figure 5.2:  | 8-element quadrupler based phased array with a low loss W-band distribu-                     |    |

|              | tion network.                                                                                | 93 |

## LIST OF TABLES

| Table 2.1: | Vector Modulator I and Q Path Currents for Phase States                 | 19 |

|------------|-------------------------------------------------------------------------|----|

| Table 2.2: | Performance Summary of 4×4 Transmit-Receive Phased Array                | 53 |

| Table 3.1: | Summary of Antenna-Coupled Transmitters for 2×4 Amplifier-Quadrupler    |    |

|            | Array                                                                   | 76 |

| Table 4.1: | Summary of Antenna-Coupled Transmitters for 2×2 Amplifier-Doubler Array | 90 |

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor, Prof. Gabriel Rebeiz for his guidance and supports through my doctoral studies. He is not just a great technical advisor for his students, also a guidance through their life. In my interviews in Media-Tek Incorporation, Qualcomm Incorporation and Intel Corporation, it was very easy to understand how he is respected by the companies due to his deep technical understanding. It has been a great pleasure and privilege for me to be one of his students. It is very good to know that he will be ready to help me whenever I need.

Next, I would like to thank my dissertation committee members, Prof. Peter Asbeck, Prof. James F. Buckwalter, Prof. Gert Cauwenberghs and Prof. William Hodgkiss for their time, interest, and valuable comments about my research.

There are many people that I would like to acknowledge here for their support and friendship: Mehmet Uzunkol, Ozgur Inac, Berke Cetinoneri, Yusuf Atesal, Tufan Gokirmak, Mehmet Parlak, Woorim Shin, Donghyup Shin, Chirag Patel, Alex Grichener, Sang-Young Kim, Bon-Hyun Ku, Jen Edwards, Kevin Ho, Samet Zihir, Ozan Dogan Gurbuz, Tumay Kanar, Bilgehan Avser, Seyhmus Cacina, Yu-Chin Ou, Yi-Chyun Chiou, Hosein Zareie, Chenhui Niu, Elmer, Yangyang, Ken.

I would also like to thank Tumay Kanar and Bilgehan Avser for being my workout buddies.

I would also like to thank Dr. Fatih Kocer and Dr. Alper Eken, Istanbul, Turkey, who encouraged me to do a Ph.D.

The support and encouragement of my parents, Duran and Hatice Golcuk, was a great contributor in completing my Ph.D. degree. They have done everything to make sure that I get the best education since I was a child, and I always feel their good wishes for me. I can never forget their support, dedication and unending love throughout my life.

The material in this dissertation is based on the following papers which are either published, or have been submitted for publication.

Chapter 2 is based on and mostly a reprint of the following papers:

- F. Golcuk, T. Kanar, and G. M. Rebeiz, "A 90-100 GHz 4×4 SiGe BiCMOS Polarimetric Transmit-Receive Phased Array with Simultaneous Receive-Beams Capabilities," *IEEE Trans. Microwave Theory and Tech.*, vol. 61, no. 8, pp. 3099-3114, Aug. 2013.

- F. Golcuk, T. Kanar, and G. M. Rebeiz, "A 90-100 GHz 4×4 SiGe BiCMOS Po-

larimetric Transmit-Receive Phased Array with Simultaneous Receive-Beams Capabilities," *IEEE Int. Symp. On Phased Array Systems and Technology*, pp. 1-4, Oct. 2013.

Chapter 3 is based on and mostly a reprint of the following papers:

- F. Golcuk, O. D. Gurbuz, and G. M. Rebeiz, "A 0.37-0.43 THz 2×4 Amplifier-Quadrupler Array with Peak EIRP of 3-4 dBm in CMOS 45nm SOI," *IEEE Transactions on Microwave Theory and Techniques*, submitted for publication, June 2013.

- F. Golcuk, A. Fung, and G. M. Rebeiz, "A 0.37-0.43 THz Wideband Quadrupler with 160 μW Peak Output Power in 45 nm CMOS," *IEEE IEEE Int. Microwave Symp.*, pp. 1-4, June 2013.

Chapter 4 is based on and mostly a reprint of the following paper:

F. Golcuk, J. M. Edwards, B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "A 163-180 GHz 2×2 Amplifier-Doubler Array with Peak EIRP of 5 dBm," *IEEE Radio Frequency Integrated Circuit Symp.*, pp. 363-366, June 2013.

The dissertation author was the primary author of the work in these chapters, and coauthors (Prof. Gabriel M. Rebeiz, Dr. Jennifer M. Edwards, Dr. Berke Cetinoneri, Dr. Alperen Y. Atesal, Dr. Andy Fung, Mr. Tumay Kanar, and Mr. Ozan D. Gurbuz) have approved the use of the material for this dissertation.

Fatih Golcuk La Jolla, California Sep., 2013.

#### VITA AND PUBLICATIONS

| 2000 - 2005 | B. S. in Electronics and Communication Engineering, Istanbul Techni-<br>cal University, Istanbul, Turkey                      |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| 2005 - 2008 | M. S. in Electronics Engineering, Istanbul Technical University, Istanbul, Turkey                                             |

| 2010 - 2013 | Ph. D. in Electrical Engineering (Electronic Circuits and Systems), University of California, San Diego, La Jolla, California |

F. Golcuk, O. D. Gurbuz, and G. M. Rebeiz, "A 0.37-0.43 THz 2×4 Amplifier-Quadrupler Array with Peak EIRP of 3-4 dBm in CMOS 45nm SOI," *IEEE Transactions on Microwave Theory and Techniques*, submitted for publication, June 2013.

O. Inac, F. Golcuk, T. Kanar, and G. M. Rebeiz, "A 90-100 GHz phased-array transmit/receive silicon RFIC module with built-in self-test," *IEEE Transactions on Microwave Theory and Techniques*, accepted for publication, August 2013.

F. Golcuk, T. Kanar, and G. M. Rebeiz, "A 90-100 GHz 4×4 SiGe BiCMOS Polarimetric Transmit-Receive Phased Array with Simultaneous Receive-Beams Capabilities," *IEEE Trans. Microwave Theory and Tech.*, vol. 61, no. 8, pp. 3099-3114, August 2013.

F. Golcuk, J. M. Edwards, B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "A 163-180 GHz  $2 \times 2$ Amplifier-Doubler Array with Peak EIRP of 5 dBm," *IEEE Radio Frequency Integrated Circuit Symp.*, pp. 363-366, June 2013.

F. Golcuk, A. Fung, and G. M. Rebeiz, "A 0.37-0.43 THz Wideband Quadrupler with 160  $\mu$ W Peak Output Power in 45 nm CMOS," *IEEE IEEE Int. Microwave Symp.*, pp. 1-4, June 2013.

F. Golcuk, T. Kanar, and G. M. Rebeiz, "A 90-100 GHz 4×4 SiGe BiCMOS Polarimetric Transmit-Receive Phased Array with Simultaneous Receive-Beams Capabilities," *IEEE Int. Symp. On Phased Array Systems and Technology*, pp. 1-4, Oct. 2013.

M. Uzunkol, F. Golcuk, B. Cetinoneri, Y. A. Atesal, O. D. Gurbuz, J. M. Edwards, and G. M. Rebeiz, "Millimeter-wave and terahertz sources and imaging systems based on 45nm CMOS technology," *IEEE Int. Microwave Symp. Dig.*, pp. 1-3, June 2012.

M. Uzunkol, O. D. Gurbuz, F. Golcuk, and G. M. Rebeiz, "A 0.32 THz SiGe 4×4 imaging array using high-efficiency on-chip antennas," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 9, Sep. 2013.

H.-T. Dabag, B. Hanafi, F. Golcuk, A. Agah, J. F. Buckwalter, and P. M. Asbeck, "Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifiers," *IEEE Trans. Microwave Theory and Tech.*, vol. 61, no. 4, pp. 1543-1556, April 2013.

#### ABSTRACT OF THE DISSERTATION

#### A W-Band SiGe 4×4 Polarimetric Transmit-Receive Phased Array and CMOS THz Multiplier Arrays

by

Fatih Golcuk

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2013

Professor Gabriel M. Rebeiz, Chair

The thesis presents a W-band transmit-receive phased array and THz multiplier arrays in SiGe BiCMOS and CMOS technologies. First, a 4×4 transmit/receive SiGe BiCMOS phased array chip in an advanced SiGe technology (IBM8HP) at 90-100 GHz with vertical and horizontal polarization capabilities, 3-bit gain control (9 dB) and 4-bit phase control is presented. The 4×4 phased array fits into a  $1.6 \times 1.5$  mm<sup>2</sup> grid, which is required at 94 GHz for wide scan-angle designs. The chip has simultaneous receive beam capabilities (V and H) and this is accomplished using dual-nested 16:1 Wilkinson combiners/divider with high isolation. The phase shifter is based on a vector-modulator with optimized design between circuit level and electromagnetic simulation and results in < 1 dB and <  $7.5^{\circ}$  rms gain and phase error, respectively, at 85-110 GHz. The behavior of the vector modulator phase distortion versus input power level is investigated and measured, and design guidelines are given for proper operation in a transmit chain.

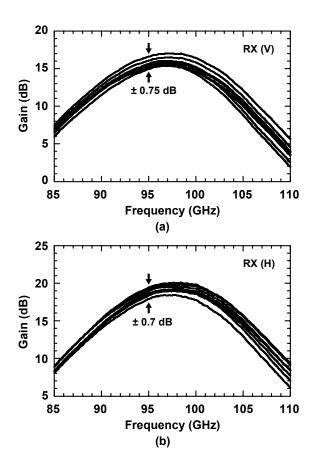

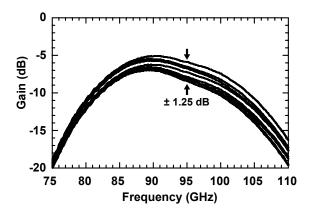

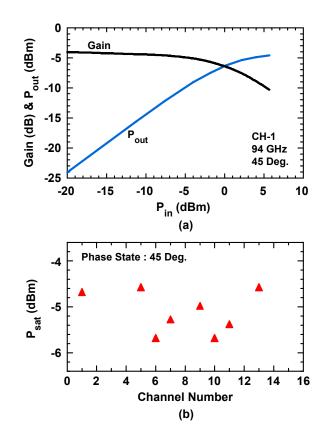

The V and H receive paths result in a gain of 22 dB and 25 dB, respectively, a noise figure of 9-9.5 dB (max. gain) and 11 dB (min. gain) measured without the T/R switch, and an input  $P_{1dB}$  of -31 to -26 dBm over the gain control range. The measured output  $P_{sat}$  is ~-5 dBm per channel, limited by the T/R switch loss. Measurements show  $\pm 0.6$  dB and  $\pm 0.75$  dB variation between the 4×4 array elements in the transmit mode ( $P_{sat}$ ) and receive mode, respectively, and < -40 dB coupling between the different channels on the chip. The chip consumes 1100 mA from a 2 V supply in both the transmit and receive modes. The design can be scaled to > 10,000 elements using polyimide redistribution layers on top of the chip and the application areas are in W-band radars for landing systems.

Next, a CMOS amplifier-multiplier-antenna array capable of generating an EIRP of 3-4 dBm at 420 GHz is presented. The chip is built using a 45nm CMOS SOI (IBM12SOI) process and efficient on-chip antennas are used to extract the power out of the chip. The design is based on a 90-110 GHz distribution network with splitters and amplifiers, and a balanced quadrupler capable of delivering up > 100  $\mu$ W of power at 370-430 GHz. The amplifier-multiplier concept is proven on a 2×4 array, and can be also scaled to any N×M array using additional W-band splitters and amplifiers.

Finally, a  $2 \times 2$  amplifier-multiplier array with on-chip antennas at 163-180 GHz in 45 nm CMOS SOI technology is presented. The measured EIRP is > 2 dBm at 165-175 GHz with a peak value of 5 dBm at 170 GHz meeting the stringiest metal-density rules for antennas. The design is based on a 80-100 GHz distribution network with splitters and amplifiers, and a balanced doubler capable of delivering up > 0.5 mW of power at 170-190 GHz.

# Chapter 1

# Introduction

#### **1.1 Phased Array Systems**

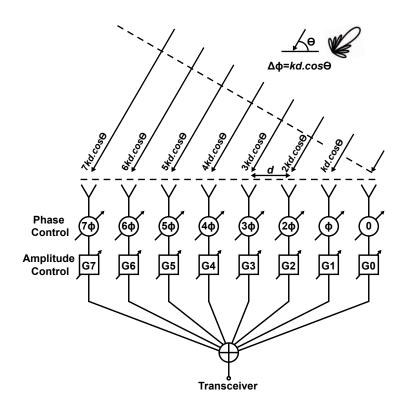

Phased array systems are widely used in radars and communications systems for beam forming and scanning [1-5]. The relative phases of received or transmitted signal are controlled by a phased array systems to steer the effective radiation pattern of an antenna array to a particular direction to construct the signals in desired direction and suppress the signal in undesired direction. The spatial filtering of the phased array increases the spectral efficiency of the receive (transmit) system [6]. The phased array system increases the signal-to-noise ratio (SNR) by combining the signal coherently and noise incoherently from the different elements, results in higher data rate systems [1]. The effective pattern is shaped by controlling the amplitude of the each antenna element and the direction of the beam is controlled by the phase weighting at each antenna element. The beam steering can be done by mechanically or electronically. In mechanically steering array, the antenna reflective surface is rotated mechanically to determine the beam angle. However, the phase and amplitude is weighted electronically in electronically scanned arrays and thus the beam steering and shaping are much faster than mechanical systems [1,7]. Fig. 1.1 shows the conceptual block diagram of the 8-element received phased array. The incoming signal from the desired angle  $\theta$  reaches the each antenna element with a time difference of  $\Delta T$ , which creates  $\Delta \phi$  phase difference between the antenna element, where

$$\Delta T = \frac{d\cos\theta}{c}, \Delta \phi = kd\cos\theta, k = \frac{2\pi}{\lambda}$$

(1.1)

and d is the distance between the elements,  $\lambda$  is the wavelength, and c is the speed of light. Thus, the progressive phase shift,  $\Delta \phi$ , between the antenna elements is required in electronically beam

Figure 1.1: An 8-element phased array block diagram.

steering arrays to receive the signal from desired direction,  $\theta$ . The phase and amplitude difference between the elements are compensated by variable time delay and variable amplifier ( or variable attenuator) to sum the desired signal constructively while adding the signals in the undesired direction de-constructively. Time delays can be employed as phase shifters to compensate the time delay between the elements in narrow band systems since the carried information change slowly in the narrow band applications. Using silicon technologies, both variable phase shifters and gain blocks together with all digital controls can be realised in single chip, and hence it can replace the complex and bulky modules which use III-V technologies.

## **1.2 Phased Array Architectures**

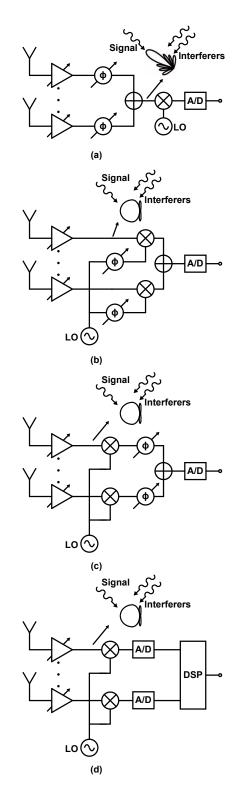

The phase shifting to compensate the time delay between the antenna elements to add them in-phase at the sum port can be done in the RF [8–16], LO [17–19], IF [20] paths or the digital domain [21, 22] of the receiver modules(Fig. 1.2). An RF phase shifter is employed in each element in the RF phase shifting (All-RF) architecture to compensate the time delay

between the elements and the signal is summed in RF domain constructively before the mixer (Fig. 1.2(a)). In the LO phase shifting architecture, each channel requires a mixer and a LO signal with variable phase, an hence results in more complex and power hungry systems (Fig. 1.2(b)). In the IF phase shifting architecture, similar to the LO phase shifting architecture, a mixer at each channel and a LO distribution network are required, but the phase shifters are employed in IF paths (Fig. 1.2)(c)). In the digital beam-forming architecture, the phase of the each element is processed in the digital domain using baseband signal processing techniques (Fig. 1.2)(d)). This architecture can be configured to have multiple beams and polarization. However, it requires high dynamic range A/D converters at each channel, and hence results in a more power consumption system.

Among these architectures, the All-RF architecture is the most commonly used since it requires only one mixer while the other architecture require a mixer at each channel and an LO distribution network. Thus, a more compact phased array and less power consumption can be achieved in the All-RF architecture. The other advantage of this architecture is that the desired signals are summed in RF domain constructively and the interferers are added de-constructively. Thus, the interferers are suppressed before the non-linear mixing and this architecture results in higher signal-to-interferer ratio (SIR). The mixer's linearity and A/D converter's dynamic range are relaxed due to the high SIR. However, disadvantage of the All-RF architecture is the high loss of the RF phase shifter and RF combiner network, but the loss can be compensated using an active phase shifter or using gain blocks in the RF path.

#### **1.3 THz Multiplier Arrays and Wafer Scale Approach**

THz systems have being used for various applications at THz frequencies, such as short distance high data rate communication, radio astronomy, sensor systems, and active and passive imaging [23–38]. The systems at THz frequencies are dominated by III-V technologies. However, advance silicon technologies with high  $f_t$  and  $f_{max}$  can replace III-V technologies at THz frequencies and are becoming popular for THz applications. Signal sources are one of the key building blocks of the communication, active imaging and atmospheric remote sensing systems. Signal can be generated at THz frequencies using injection-locked or N-push oscillator [37, 39, 40] and multipliers [41–43]. Multipliers have better phase noise performance than oscillators which have poor phase noise performance due to operating close to  $f_{max}$  since the source at lower frequencies has low phase noise and can be locked to a low frequency reference using a phase-locked-loop (PLL). Another advantage of the multiplier approach is to have the

**Figure 1.2**: Phased array receiver architectures: (a) RF phase shifting, (b) LO phase shifting, (c) IF phase shifting and (d) digital beam forming.

higher frequency bandwidth than the oscillator approach. The multiplier approach is scalable to large  $N \times M$  arrays using high efficiency on-chip antennas since the distribution network is at lower frequencies and has much less loss. Also, phase shifters can be integrated to scan the beam.

#### **1.4 Thesis Overview**

The thesis presents a 90-100 GHz  $4 \times 4$  SiGe BiCMOS polarimetric transmit-receive phased array with simultaneous receive-beams capabilities and THz multiplier arrays using 45 nm CMOS SOI process.

Chapter 2 presents a 4×4 transmit/receive SiGe BiCMOS phased array chip in an advanced SiGe technology (IBM8HP) at 90-100 GHz with vertical and horizontal polarization capabilities, 3-bit gain control (9 dB) and 4-bit phase control. The 4×4 phased array fits into a  $1.6 \times 1.5$  mm<sup>2</sup> grid, which is required at 94 GHz for wide scan-angle designs. The chip has simultaneous receive beam capabilities (V and H) and this is accomplished using dual-nested 16:1 Wilkinson combiners/divider with high isolation. The phase shifter is based on a vectormodulator with optimized design between circuit level and electromagnetic simulation and results in < 1 dB and  $< 7.5^{\circ}$  rms gain and phase error, respectively, at 85-110 GHz. The behavior of the vector modulator phase distortion versus input power level is investigated and measured, and design guidelines are given for proper operation in a transmit chain. The V and H receive paths result in a gain of 22 dB and 25 dB, respectively, a noise figure of 9-9.5 dB (max. gain) and 11 dB (min. gain) measured without the T/R switch, and an input P<sub>1dB</sub> of -31 to -26 dBm over the gain control range. The measured output  $P_{sat}$  is ~-5 dBm per channel, limited by the T/R switch loss. Measurements show  $\pm 0.6$  dB and  $\pm 0.75$  dB variation between the 4×4 array elements in the transmit mode ( $P_{sat}$ ) and receive mode, respectively, and < -40 dB coupling between the different channels on the chip. The chip consumes 1100 mA from a 2 V supply in both the transmit and receive modes. The design can be scaled to > 10,000 elements using polyimide redistribution layers on top of the chip and the application areas are in W-band radars for landing systems.

Chapter 3 presents a CMOS amplifier-multiplier-antenna array capable of generating an EIRP of 3-4 dBm at 420 GHz. The chip is built using a 45nm CMOS SOI (IBM12SOI) process and efficient on-chip antennas are used to extract the power out of the chip. The design is based on a 90-110 GHz distribution network with splitters and amplifiers, and a balanced quadrupler capable of delivering up > 100  $\mu$ W of power at 370-430 GHz. The amplifier-multiplier concept

is proven on a  $2 \times 4$  array, and can be also scaled to any N×M array using additional W-band splitters and amplifiers.

Chapter 4 presents a  $2\times2$  amplifier-multiplier array with on-chip antennas at 163-180 GHz in 45 nm CMOS SOI technology. The measured EIRP is > 2 dBm at 165-175 GHz with a peak value of 5 dBm at 170 GHz meeting the stringiest metal-density rules for antennas. The design is based on a 80-100 GHz distribution network with splitters and amplifiers, and a balanced doubler capable of delivering up > 0.5 mW of power at 170-190 GHz.

# Chapter 2

# A 90-100 GHz 4×4 SiGe BiCMOS Polarimetric Transmit-Receive Phased Array with Simultaneous Receive-Beams Capabilities

# 2.1 Introduction

SiGe and CMOS RFICs are now the technology of choice for millimeter-wave phased arrays due to their high  $f_t/f_{max}$  and density of integration. Designs with 8-32 elements based on the All-RF architecture have been successfully demonstrated at 45-110 GHz in transmit (Tx), receive (Rx) or transmit/receive (T/R) modes [8–15]. The silicon designs allow the integration of several elements on the same chip, together with the power combining network, up/downconversion blocks, synthesizers, and all the necessary digital control electronics. The silicon designs also result in nearly identical response between the different channels and allow for compact built-in self-test circuitry, which greatly reduces the cost of mm-wave phased array systems [13, 44].

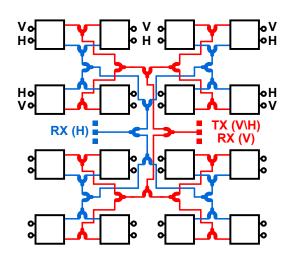

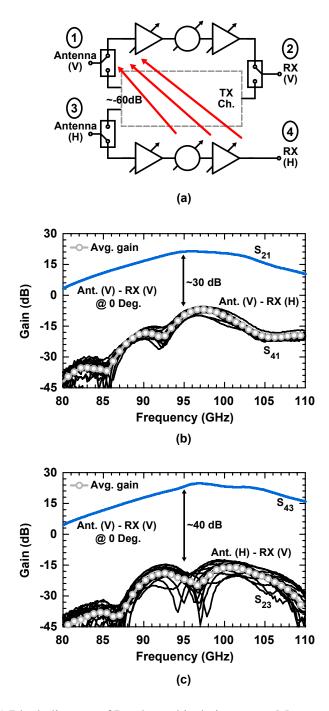

This paper presents the first 90-100 GHz  $4 \times 4$  phased array with full polarimetric capabilities. The chip is designed for a W-band radar system consisting of > 10,000 elements, and requires vertical (V) and horizontal (H) polarization capabilities in both the transmit and receive modes [45]. In this design, the transmit mode is sequentially polarimetric, that is, a single polarization is transmitted at a time (V or H). On the other hand, the receive mode is fully polarimetric and two simultaneous phased-array receivers, one for the vertical and one for the horizontal polarization, are employed. This requires that two nested 16:1 Wilkinson combiner networks be used in the receive mode, each with an equiphase distribution to all the 16-elements for ease of system calibration (Fig. 2.1).

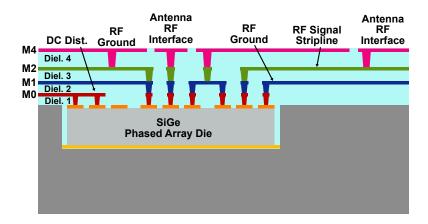

The  $4 \times 4$  phased array chip will be packaged using polyimide layers above the top metal surface (typically called RDL Redistribution Layers or CSP - chip-scale package). These layers contain short RF distribution sections and connect the  $4 \times 4$  outputs of the RFIC to the 94 GHz antennas. They also contain the global RF signal distribution layer, DC feeds and digital control lines, and result in an extremely low RF and DC ground and supply inductance. This technology has been used with success at 45 GHz [46] and 77 GHz [47] and is readily scalable to 94 GHz.

The 4×4 phased array must also fit into an area less than the  $\lambda/2$  spacing at 94 GHz (1.6 mm) for wide scan-angle performance. The size of the RFIC unit cell consisting of a transmit and two receive chains, and the Wilkinson couplers, is  $1.6 \times 1.5 \text{ mm}^2$ , meeting this requirement. Finally, the chip consumes 1100 mA (simulated 950 mA) from a 2 V supply in the receive and transmit modes, which is low enough to allow for large subarrays (256 elements) using the RDL technology.

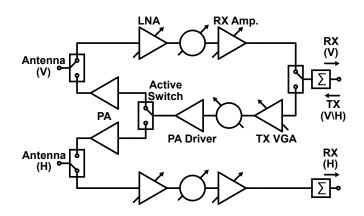

### 2.2 Design

The single-element block diagram with the required polarimetric capabilities is shown in Fig. 2.2. The design is single-ended due to the compact size requirements for each phased array cell, and the low ground inductance (2-5 pH) offered by the chip-scale package. The chip is fabricated in the IBM8HP SiGe BiCMOS process with an  $f_t/f_{max}$  of 200 GHz, 0.12  $\mu$ m CMOS transistors, and 7 metal layers with 2 thick top metals (Fig. 2.3). Grounded coplanar waveguide (G-CPW) transmission lines are used throughout the chip with a simulated loss of 1 dB/mm and 1.2 dB/mm at 90-100 GHz for 50  $\Omega$  and 70  $\Omega$  designs, respectively.

Each element is composed of two receive paths, a power amplifier with an active switch for V and H selection in the transmit path, and CMOS single-pole double-throw (SPDT) switches for T/R control. Also, active phase shifters using vector modulators are employed since passive phase shifters result in high loss at W-band frequencies using 0.12  $\mu$ m CMOS [48,49]. Therefore, each unit element also requires three phase shifters, one in the transmit path and two in the receive paths. Note that the low noise amplifier (LNA) and power amplifier (PA) and switch are single-ended, but the active phase shifter is differential, and therefore, input and output baluns are used around each phase shifter.

All active blocks are designed with 50  $\Omega$  input and output ports so as to allow for indi-

vidual break-out testing of each block, and all transmission-lines components are simulated with Sonnet [50], a full-wave EM program, for added accuracy. A lot of effort was placed on the T/R block to reduce its size and power consumption since it is replicated 16 times in the chip. Therefore, all active circuit blocks are based on cascode designs since it provides the lowest power consumption per gain block, and the highest gain per area.

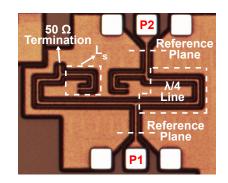

#### 2.2.1 SPDT Switch

Starting from the V or H antenna ports, the SPDT transmit/receive switch is a tuned  $\lambda$ /4-shunt design since it results in lower loss at W-band frequencies than a series-shunt design (Fig. 2.4). This design has been demonstrated before at 90-100 GHz with an insertion loss of 2.3 dB at 94 GHz [32]. Also, the  $\lambda$ /4 section is needed for the physical separation between the (V) and (H) antenna ports. The shunt switching elements are standard CMOS transistors with a W/L=125  $\mu$ m/0.12  $\mu$ m which has deep trench around it to increase the substrate resistance to the ground, and a shunt-stub with an equivalent inductance of 70 pH is used to resonate out the CMOS off-state capacitance when the switch is not activated (in the pass state). The shorted shunt stub also acts as an electrostatic discharge (ESD) protection for the entire channel. The simulated insertion loss is 2.1 dB with an isolation of 25 dB at 90-100 GHz with near-zero power consumption.

#### 2.2.2 LNA and RX Amplifier

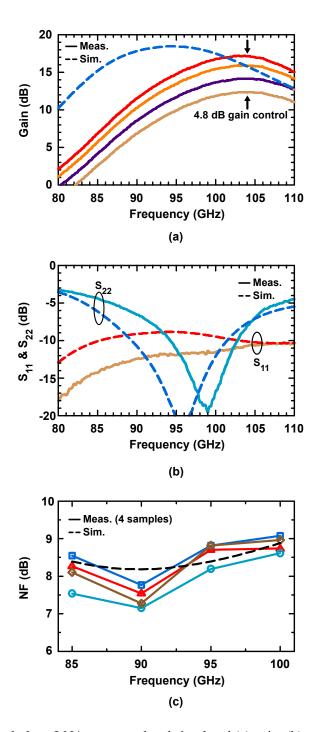

The LNA is a two-stage cascode design biased to get moderate gain with low noise figure at 0.7 mA/ $\mu$ m for the first and second stages (Fig. 2.5). The first stage employs emitter degeneration for wideband input impedance matching, and a complex interstage match is used for maximum gain. Inductances are used between the common-emitter and common-base transistors and at the collector of the common-base transistors to boost the gain of the LNA [51,52]. Also, several ground pads to the RDL system ground surround the LNA for minimum additional ground inductance. The LNA consumes 10 mA from a 2 V supply including all bias and gain control circuits and results in a simulated gain and noise figure (NF) of 18.5 and 8.3 dB, respectively, at 94-95 GHz, a 3-dB bandwidth of 85-104 GHz, and an input P<sub>1dB</sub> of -25 dBm at 94 GHz. The LNA has a 4.5 dB total gain control with 1.5 dB steps using 2-bits digital control. Gain is controlled using a current steering topology in the second stage of the LNA [53].

**Figure 2.1**: Polarimetric transmit-receive  $16:1 4 \times 4$  phased array with simultaneous receivebeams and dual nested Wilkinson combiners.

Figure 2.2: T/R unit (single element) block diagram.

Figure 2.3: IBM8HP metal stack-up with representative 50  $\Omega$  and 70  $\Omega$  G-CPW lines.

Figure 2.4: SPDT switch schematic and Sonnet layout.

Figure 2.5: LNA with gain control schematic and Sonnet layout.

The RX amplifier has the same topology as the LNA but with different component values. It also consumes 10 mA from a 2 V supply and results in 15.5 dB gain with a 3-dB bandwidth of 83-105 GHz. The RX amplifier also uses the same current steering technique, and has 1-bit digital control for a 6 dB gain variation. The total gain control in the Rx path is therefore 10.5 dB using 3-bits.

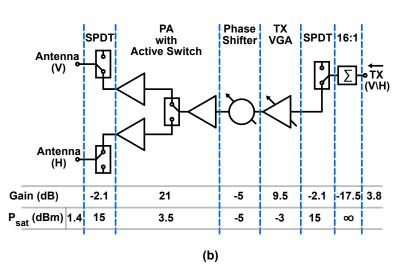

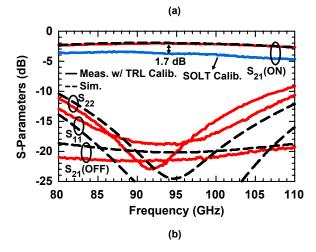

#### 2.2.3 Power Amplifier and Active Switch

The power amplifier is a 3-stage design with the  $2^{nd}$  stage used as a cascode active switch with > 40 dB isolation for V and H polarization control (Fig. 2.6). The input stage employs an emitter inductor for a wideband impedance match, and conjugate matching is employed between all stages for maximum power transfer. The last stage is also a class A design with P<sub>sat</sub> (saturated power) of 3.5 dBm, and a PAE (power added efficiency) of 3% at 94 GHz. All biasing is done at ~1-1.3 mA/ $\mu$ m which corresponds to maximum gain bias. Again, as with the LNA, careful layout is done to minimize parasitic inductance in the interconnects and Sonnet models are used for the MOM (metal-oxide-metal) capacitances and inductors in the Cadence simulations. The simulated gain and NF are 21 dB and 10 dB, respectively, at 94 GHz with a 3-dB gain bandwidth of 80-102 GHz. At P<sub>sat</sub>, the gain drops to 16 dB, and therefore, an input power of -12.5 dBm is required to achieve full saturation. This is still low enough and the preceeding phase shifter can deliver this power level with low phase distortion.

The TX-VGA (transmit variable gain amplifier) on the transmit path is a single-stage cascode amplifier with a current steering topology for gain control (not shown). It consumes 5 mA from a 2 V supply and results in 9.5 dB gain with a 3-dB bandwidth of 81-108 GHz. It also has 5.5 dB gain control with  $\sim$ 0.8-dB steps using a 3-bit digital control. The simulated output saturated power is -4 dBm which is enough to drive the phase shifter.

#### 2.2.4 Phase Shifter

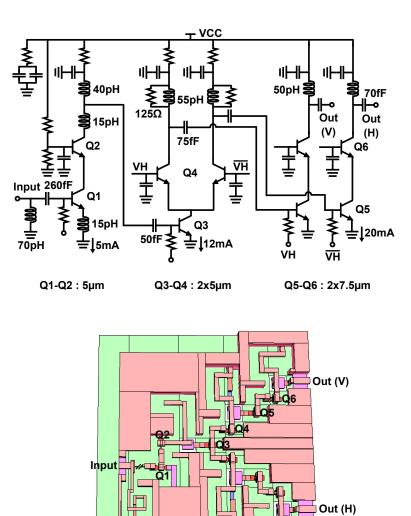

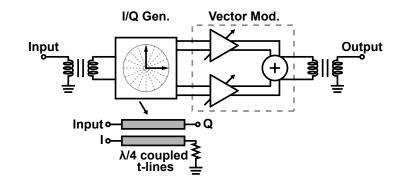

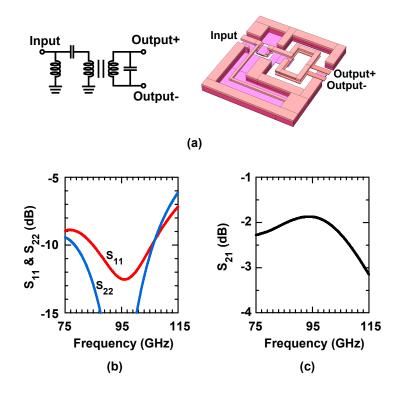

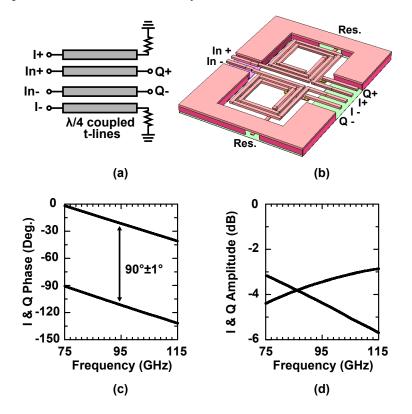

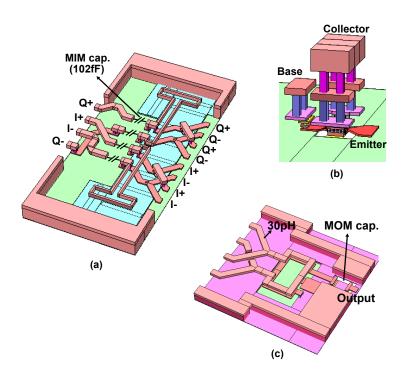

The phase shifter is the hardest component to design due to its interconnect complexity. Fig. 2.7 presents the phase shifter topology, which is based on a vector modulator with input and output baluns. First, the passive 50  $\Omega$  (single-ended) to 100  $\Omega$  (differential) balun is designed using the top two metal layers with an insertion loss of <2 dB at 90-100 GHz, and stub inductors and MOM capacitors are used for input and output matching (Fig. 2.8). This is followed by a differential I/Q network using two 3-dB distributed  $\lambda/4$  couplers that are built using the top two metal layers and in a spiral configuration for compactness (Fig. 2.9) [54, 55]. This network is

īL

Figure 2.6: Power amplifier with active switch schematic and Sonnet layout.

Figure 2.7: Phase shifter block diagram.

simulated using Sonnet and results in  $\sim 1$  dB loss at 94 GHz and a 90°±1° and < 1 dB phase and amplitude difference between the I and Q outputs, respectively.

The I/Q coupler outputs are then attached to the vector modulator consisting of SiGe transistors for the variable gain stages and a 0.12  $\mu$ m CMOS switching network to select the different quadrants for 180° phase shift (Fig. 2.10). The bias currents, I<sub>I</sub> and I<sub>Q</sub>, for the SiGe differential pairs, are controlled using a 4-bit digital-analog-converter (DAC). The output of the I and Q stages are summed together in the current domain and an output balun is used as the inductive load. Also, a differential shunt matching inductor is used at the input for a wideband impedance match (Fig. 2.11). The I<sub>I</sub> and I<sub>Q</sub> currents (and the DAC reference currents) are determined using Cadence simulations for the 0°, 22.5°, 45°, 67.5° and 90° phase settings by using the IBM transistor models and including all the extracted input, output, and interconnect parasitics (using Sonnet) for the I and Q paths, and are tabulated in Table 4.1. The vector modulator results in a simulated gain of -5 dB with rms gain error of 0.7 dB, a noise figure of 16 dB, an input P<sub>1dB</sub> of -2 dBm all at 94 GHz.

Due to the importance of this block, breakout measurements and discussions will be presented in this section. The phase shifter breakout microphotograph is shown in Fig. 2.12. The phase shifter was measured using GSG W-band probes with SOLT calibration to the probe tips. Measurements agree well with simulations with < 1 dB rms gain error and <  $7.5^{\circ}$  rms phase error at 85-110 GHz (Fig. 2.13). At 95 GHz, the results show < 0.8 dB and ~  $3.5^{\circ}$  rms gain and phase error, respectively, stressing the importance of full-wave simulations. Fig. 2.14 presents details of the measured gain and P<sub>1dB</sub> versus 16 phase states at 94 GHz. The gain variation can be equalized using a small-step VGA, which is available in the phased array element if a better rms gain error is required.

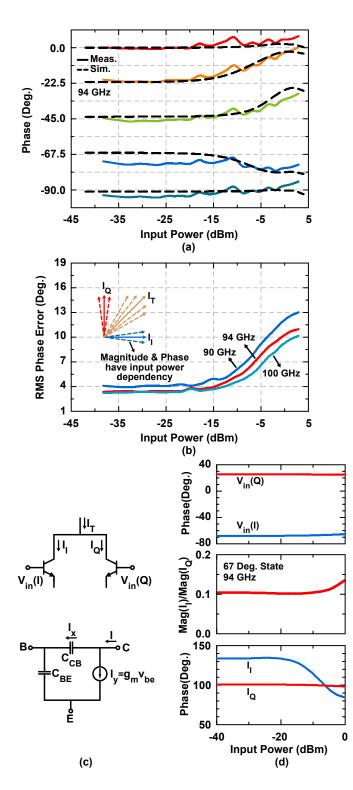

The measured phase versus input power is presented in Fig. 2.15-(a), and is dependent

Figure 2.8: Input balun schematic, Sonnet layout and simulation results.

Figure 2.9: I/Q generator schematic, Sonnet layout and simulation results.

Figure 2.10: Vector modulator and DAC (Digital to Analog Converter) schematic.

**Figure 2.11**: Vector modulator Sonnet layout of (a) input matching, (b) transistor interconnection and (c) output load balun.

**Figure 2.12**: Phase shifter breakout chip microphotograph ( $0.75 \times 0.65 \text{ mm}^2$  including DC pads).

| Phase<br>State<br>(Deg.) | $\mathbf{I}_{I}$ | $\mathbf{I}_Q$ |

|--------------------------|------------------|----------------|

| 0                        | 8x               | 0              |

| 22.5                     | 7x               | 1x             |

| 45                       | 4x               | 4x             |

| 67.5                     | 1x               | 7x             |

| 90                       | 0                | 8x             |

Table 2.1: Vector Modulator I and Q Path Currents for Phase States

x = 0.625 mA

on the input power at  $P_{in} > -10$  dBm. This is explained as follows: The output current in the I and Q paths are composed of two components: a)  $I_x$  due to the collector-base capacitance and b)  $I_y$  due to the transistor  $g_m$  source. Note that these two currents are not at the same phase. Also, the collector-base (CB) capacitance is due to a p-n junction and therefore is dependent on the voltage across the CB junction. As the RF power increased, the voltage across the CB junction increases, and  $I_x$  increases more than  $I_y$ , which results in distortion in the 22°, 45° and 67° bits. Therefore, while the  $P_{1dB}$  values are  $\sim$ -4±2 dBm, the phase shifter should be operated around -10 dBm for low rms phase errors (Fig. 2.15 (b)).

To our knowledge, this phase shifter presents state-of-the-art performance as compared to all published W-band designs [48, 56–58].

#### 2.2.5 Nested Wilkinson Combiners

The 4×4 chip also contains two passive 16:1 Wilkinson combiner/divider networks since one of the distribution layers must be bi-directional (carries the Tx signal and one of the Rx signals). The Wilkinson networks should also be symmetrical with an equiphase distribution to all 16 elements. This was done by nesting the two 16:1 Wilkinson combiners in the 100-200  $\mu$ m space between the 4×4 elements as shown in Fig. 2.1.

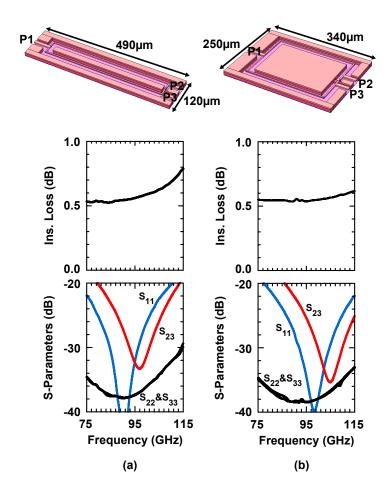

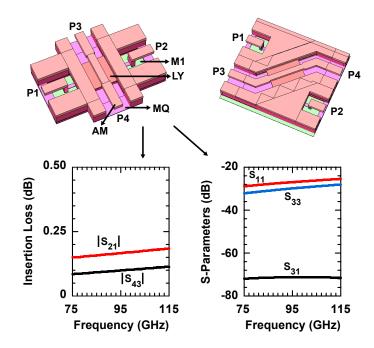

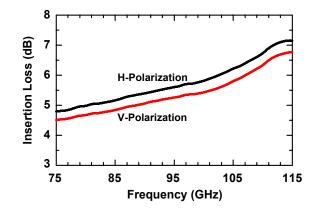

Two different Wilkinson combiners with  $\lambda/4$  70.7  $\Omega$  sections and different geometries are designed for the nested combiners (Fig. 2.16). Sonnet simulations show that both designs have a loss of ~0.55 dB with > 30 dB impedance match and isolation at 95 GHz. The combiner networks also have a large number of cross-overs and this was accomplished by moving the ground plane to the LY layer at the cross-over thus creating a ground plane island (50×50  $\mu$ m<sup>2</sup>) under the top transmission line, and lowering the other transmission line to the MQ layer (below the ground plane). Both transmission-line dimensions are also changed so as maintain a 50  $\Omega$ environment. The simulated cross-over insertion loss using Sonnet is 0.1-0.15 dB at 95 GHz, with an isolation > 70 dB (Fig. 2.17).

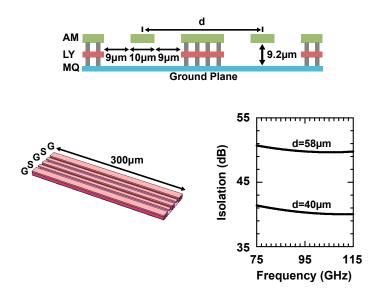

The nested Wilkinson combiners also require transmission-lines which are electrically long and placed parallel to each other due to the narrow spacing between the T/R elements. Therefore, electromagnetic simulation was done in order to determine the minimum distance required for high isolation. A center-to-center spacing of 40-60  $\mu$ m results in an isolation of 40-50 dB at 95 GHz which is sufficient for this application (Fig. 2.18).

Finally, each 16:1 Wilkinson network was simulated including the individual Wilkinson stages, connecting transmission lines and cross-overs. Both networks result in an ohmic loss of

**Figure 2.13**: Phase shifter (a) gain and rms gain error and (b) phase and rms phase error over 16 phase states.

Figure 2.14: Measured gain and  $IP_{1dB}$  versus 16 phase states at 94 GHz.

5-5.5 dB at 95 GHz with a wide band impedance match ( $S_{nn} < -28$  dB at 90-100 GHz) (Fig. 2.19). The V and H networks are individually symmetric from the common port to the 4×4 elements, so there is no phase difference in simulations. The isolation between any two elements is given mostly by the first Wilkinson coupler and is > 30 dB at 95 GHz.

#### 2.2.6 System-Level Simulations

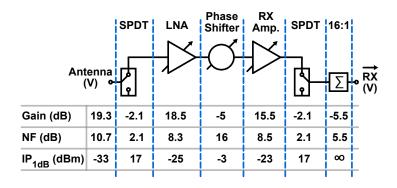

The gain and noise figure of a single receive channel (V or H polarization) is shown in Fig. 2.20 (a). Note that the Wilkinson combiner gain is taken as -5.5 dB since the 12 dB combining gain will be accounted for in the antenna-array gain calculations. The line-up results in 19.3 dB gain and 10.7 dB NF at 95 GHz, with an input  $P_{1dB}$  of -33 dBm which is limited by the RX amplifier. On the transmit side, the Wilkinson network is represented by 17.5 dB loss due to the 16:1 power division (12 dB) which is required to feed the 4×4 T/R modules (Fig. 2.20 (b)). The linear gain from the common port to a radiating element port is 3.8 dB, and the output  $P_{sat}$  is 1.4 dBm and is limited by the active switch PA which is followed by the SPDT switch loss. At  $P_{sat}$ , and due to gain compression in the PA, the total network gain is ~-0.5 dB and an input power of 2 dBm is required at the common port in order to saturate all the 4×4 T/R modules.

#### 2.2.7 Chip Power Supply and Control

The entire 4×4 phased array chip is shown in Fig. 2.21 and consumes 1100 mA from a 2 V supply in the Rx and Tx modes. To ensure the same bias current for the same components on the entire chips, a 125  $\mu$ A reference current source is generated at the center of the chip

**Figure 2.15**: Measured (a) relative phase versus input power at 94 GHz, (b) rms phase error versus input power at 90, 94 and 100 GHz, (c) a block diagram of current components for phase shifter and (d) simulated  $I_I$  and  $I_Q$  current versus input power.

**Figure 2.16**: Wilkinson combiner/divider Sonnet layouts and simulated S-parameters. Two different Wilkinson combiners/dividers were used, shown in (a) and (b).

**Figure 2.17**: V and H polarization combiner/divider network cross-over Sonnet layouts and simulated S-parameters.

**Figure 2.18**: Parallel G-CPW line Sonnet layout and coupling simulations results for 40  $\mu$ m and 58  $\mu$ m center to center spacing.

**Figure 2.19**: Simulated insertion loss for the V and H polarization 16:1 Wilkinson combiner/divider networks.

and distributed to the 16 T/R elements using current mirrors. A PTAT circuit is designed as the reference current source to maintain a nearly constant gain for different temperatures (up to 70 °C). M2 and M3 are used for reference current distribution. M1, MQ and AM metal layers are used together for the ground layer to decrease the ground inductance. LY and M4 metal layers are used together as VCC distribution between the elements to decrease the I×R drop. In the front-end components (LNA, Phase shifter, etc.), MIM and MOS capacitances are employed together between the supply and ground as bypass capacitances. A total of 4 nF capacitance is placed between the supply and the ground on the entire chip.

All individual channels have their own registers (D-type latch) for digital controls. A 4-bit address decoder is used to select the T/R unit element. The Rx channels have a total of 8-bit registers for 4-bit phase, 3-bit gain and 1-bit On/Off control. The Tx channels has one additional register for V/H polarization control. All channels can be switched from Rx (Tx) mode to Tx (Rx) mode using a digital level input. All channels can be turned off using a 1-bit reset input. Thus, a total of 16 bits (4-bit phase, 3-bit gain, 1-bit On/Off, 1-bit V/H, 4-bit address, 1-bit address enable and 1-bit reset and 1-bit Rx-Tx mode) parallel digital interface is required to control the 4×4 phased array. The 2 V logic circuits are designed with 0.24  $\mu$ m thick-oxide CMOS transistors, and M2 and M3 are used for the digital control lines with the longest control line is ~10 mm / 1  $\mu$ m with an M1 ground layer. The total delay of the control network including interconnection lines and logic circuits is ~2.5 ns, resulting in ~100 MHz maximum control speed.

All RF pads except the Rx(H) common port have ESD protection using the shunt inductances of the SPDT switches. VCC supply pads are ESD protected using an RC-clamp ESD

(a)

**Figure 2.20**: (a) Rx channel block diagram with simulated component values for gain, NF and  $IP_{1dB}$  and (b) Tx channel block diagram with simulated component values for gain and  $P_{sat}$ .

**Figure 2.21**: Polarimetric transmit-receive  $4 \times 4$  phased-array chip microphotograph ( $6.6 \times 5.9$  mm<sup>2</sup>). The chip contains 48 phased-array channels. Note the multitude of ground pads over the entire chip used to equalize the on-chip ground to the RDL system-ground.

cell and a reverse diode between VCC and ground for positive and negative polarity spikes, respectively [59]. All other I/O pads have a dual-diode to VCC and ground for ESD protection.

### 2.3 Measurements

#### 2.3.1 Individual Breakouts

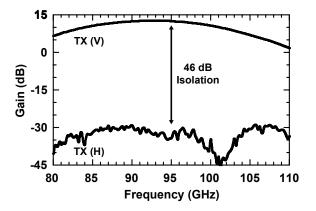

Chip breakouts were available for all individual components and also, for a stand-alone T/R module. All measurements are done using GSG probes and referenced to the probe tips using SOLT calibration, but the SPDT switch break-out is measured using both SOLT and TRL calibration standards. There is a significant difference in the measured (1.6 dB) and simulated (0.2 dB) thru loss at 94 GHz which is basically composed of two GSG pad (Fig. 2.22). In this measurement,  $S_{11}$  and  $S_{22}$  are < -17 dB up to 100 GHz, and therefore,  $S_{21}$  is a correct indication of the thru loss. This is currently being investigated and could be due to electric fields extending into the silicon substrate since M1 was not used under the GSG signal pads. Due to brevity, the measurements on the individual components are summarized below. 1) Fig. 2.23(a) shows the LNA breakout chip microphotograph. The measured LNA gain was 17.1 dB with 4.8 dB gain control. These values are close to simulations (actually 1.3 dB higher) and the peak shifted to 100-102 GHz instead of 94 GHz, but the input and output GSG pad losses, 1.6 dB of total, was not de-embedded from the measured gain. The measured LNA NF was 8.7 dB (the GSG pad loss, 0.8 dB, was not de-embedded) and agrees with the simulated value of 8.3 dB (Fig. 2.24). 2) The measured SPDT switch S-parameters using TRL calibration show a gain of -2.0 dB at 94 GHz and result in an excellent agreement with simulations (Fig. 2.25). 3) The measured phase shifter was very close to simulations as shown in Section II. 4) Fig. 2.23(b) shows the PA breakout chip microphotograph. The measured PA with the active switch showed a gain of 15.6 dB (instead of 21 dB) at 94 GHz as shown in Fig. 2.26, with an isolation > 40 dB between the (V) and (H) outputs, and a P<sub>sat</sub> of 1 dBm (instead of 3.5 dBm, but the GSG pad loss, 0.8 dB, was not de-embedded from the measured value). To match the simulations with the measurements, the MOM capacitances between the stages are decreased by 12% from the simulated values (by increasing the distance between M3 and M4 metal layers), but the input and output GSG pad losses, 1.6 dB of total, was not de-embedded from the measured gain. This is still in accordance to the IBM8HP design rules for process variation ( $\pm 23\%$ ). In the future, it is preferable to use MIM capacitors which do not suffer from such variation.

Figure 2.22: Measured and simulated THRU pad losses.

(b)

**Figure 2.23**: (a) LNA breakout chip microphotograph ( $0.58 \times 0.45 \text{ mm}^2$  not including DC pads), and (b) PA breakout chip microphotograph ( $0.65 \times 0.55 \text{ mm}^2$  not including DC pads).

**Figure 2.24**: Stand-alone LNA: measured and simulated (a) gain, (b) return losses, and (c) noise figure.

**Figure 2.25**: (a) Stand-alone SPDT switch chip microphotograph, and (b) measured and simulated S-parameters.  $S_{21}$  measurements are done with both SOLT and TRL calibration.

#### 2.3.2 T/R Module Receive

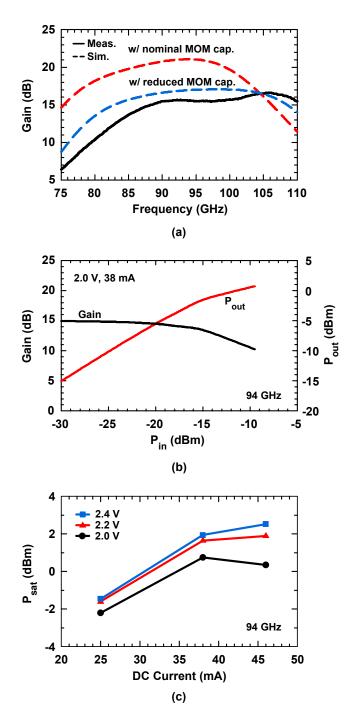

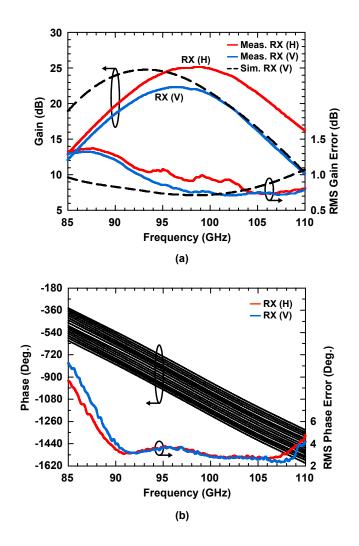

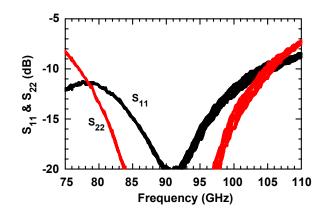

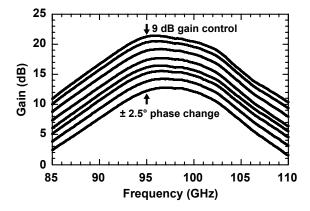

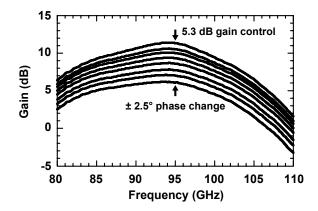

The stand-alone T/R module is measured in both Rx and Tx modes (Fig. 2.27). The measured gain and phase response at maximum gain settings for the V and H polarization paths are shown in Fig. 2.28. Both paths result in a wide band impedance match with a 10 dB return loss up to 105 GHz (Fig. 2.29). Note that, for clarity, the average gain value is presented for the 16 different phase states. As presented in Fig. 2.14, there is a  $\pm 1.2$  dB gain variation over all phase states at 94 GHz, thereby resulting in an rms gain error of ~0.8 dB. The H polarization path has 2-3 dB higher gain at 94 GHz than the V-polarization path due to the absence of an additional SPDT switch at the Wilkinson port (see Fig. 2.2). The measured phase error  $< 4^{\circ}$  at 90-100 GHz. Note that both V and H polarization result in essentially identical phase shifter response. The measured gain control is 9 dB with a  $\pm 2.5^{\circ}$  phase error and agrees with simulations (Fig. 2.30). The measured P<sub>1dB</sub> is -31 dBm to -26 dBm at maximum and minimum gain settings and agrees well with simulations (Fig. 2.31).

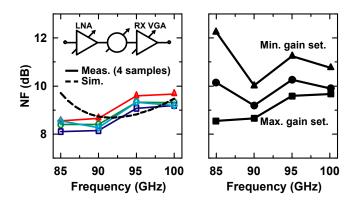

The receive path noise figure was also measured without the switches (LNA, PS, RX amplifier) for 4 different samples, and resulted in 9-9.5 dB NF (the GSG pad loss, 0.8 dB, was not de-embedded) at 95 GHz which is close to the simulated value of 8.7 dB (Fig. 2.32). The noise figure increases to  $\sim 11$  dB at the minimum gain setting also in agreement with simulations.

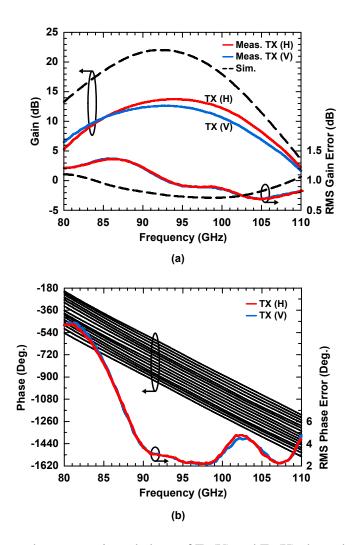

#### 2.3.3 T/R Module Transmit

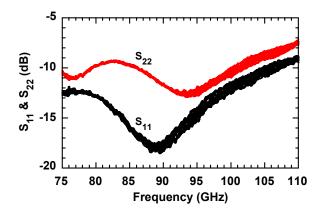

The measured S-parameters of the Tx paths are shown in Fig. 2.33 for the V and H polarization paths for 16 different phase states at maximum gain setting, with a peak gain of 13 dB at 95 GHz, and are within  $\pm 0.5$  dB of each other (this is the calibration accuracy at W-band). Note that there is an ~8.5 dB difference between the simulated and measured response and this is attributed to the increased pad loss and the reduced measured PA/active-switch gain (~4 dB gain difference). Again, the average gain over 16 phase states is presented and there is a  $\pm 2$  dB gain variation versus all phase settings. The measured Tx channel phase response is also very similar to the individual phase shifter (see Fig. 2.13) and of course, is identical for the V and H paths since they pass by the same phase shifter. The measured S<sub>11</sub> and S<sub>22</sub> show a -10 dB response up to 100 GHz (Fig. 2.34).

The measured gain control is 5.3 dB, which agrees well with simulations, over 8 steps with very low phase error since only the gain of the TX-VGA is adjusted (Fig. 2.35). This means that the TX-VGA can correct for the rms gain error in the transmit phase shifter.

**Figure 2.26**: Stand-alone power amplifier: (a) measured and simulated gain, (b) measured output power and gain versus input power at 94 GHz, and (c) measured saturated output power versus DC current at 2 V, 2.2 V and 2.4 V supply voltages.

**Figure 2.27**: T/R unit (single element) chip microphotograph  $(1.6 \times 1.2 \text{ mm}^2 \text{ not including DC pads})$ .

**Figure 2.28**: Measured average gain and phase of both Rx channels on a T/R unit over 16 phase states at maximum gain state.

Figure 2.29: Measured input and output return losses of Rx(V) channel on a T/R unit over 16 phase states.

Figure 2.30: Measured gain of Rx(V) channel on a T/R unit over 8 gain states at  $0^{\circ}$  phase state.

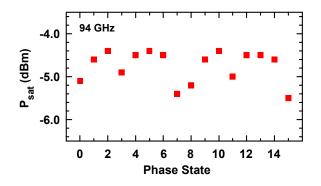

The measured output  $P_{sat}$  is -5±0.5 dBm for the transmit element versus different phase states for both V and H paths (Fig. 2.36). This is lower than simulations due to the reduced power amplifier  $P_{sat}$  and the increased loss of the GSG pad (0.8 dB).

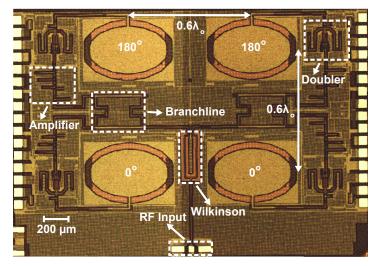

#### 2.3.4 Isolation in the T/R Module